AUGUST/SEPTEMBER 2018

# Solic Siaic TECHNOLOGY

Insights for Electronics Manufacturing

How to Improve Yield Ramp During Development P. 18

Automotive Defect Sensitivity Requirements P. 24

**The Rebirth of the Semiconductor Industry** P. 27

3D Xpoint and e-MRAM Memories Headed for Volumes R14

> Extension MEDIA

www.solid-state.com

## When precise contact matters.

## **Contact Intelligence technology senses and reacts to enable autonomous semiconductor test.**

FormFactor's Contact Intelligence combines smart hardware design, innovative software algorithms and years of experience to create a technology that provides benefits across DC, RF and silicon photonics applications.

Contact Intelligence ensures accurate contact and faster time-to-data with less operator intervention. **Visit www.formfactor.com/go/ci.**

## Solid State TECHNOLOGY

AUGUST/SEPTEMBER 2018 VOL. 61 NO. 6

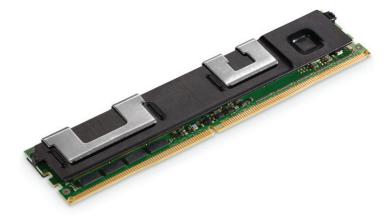

Caption: 3D XPoint is a storage class memory (SCM) based on phase-change that fits in between fast DRAM and non-volatile NAND. Source: Intel

## FEATURES

|     | MEMORY   Emerging memo             |

|-----|------------------------------------|

|     | Two emerging memory types – 3D     |

| 14) | David Lammers, Contributing Editor |

|     |                                    |

**MEMORY** | Emerging memory types headed for volumes Two emerging memory types – 3D Xpoint and e-MRAM -- are now coming to the market.

**DESIGN** | Layout schema generation: Improving yield ramp during technology development Layout schema generation generates random, realistic, DRC-clean layout patterns of the new design technology for use in test vehicles.

Wael Elmanhawy and Joe Kwan, Mentor Graphics, Beaverton, OR

#### PROCESS WATCH | Automotive defect sensitivity requirements

This article is the third in a series on process control strategies for automotive semiconductor devices. David W. Price, Douglas G. Sutherland, Jay Rathert, John Mccormack and Barry Saville, KLA-Tencor, Milpitas, CA

#### VACUUM | Solving the burden of Bourdon tubes

Mini diaphragm gauges offer a new alternative to Bourdon tubes. Brian Sullivan, Valin Corporation, San Jose, CA

## COLUMNS

- **2** Editorial The cobbler's children getting shoes? *Pete Singer, Editor-in-Chief*

- **12 Packaging** Chiplet tech discussed at DARPA ERI kickoff *Phil Garrou, Contributing Editor*

- **13 Semiconductors** Integrated 5G chip directions *Ed Korczynski, Sr. Technical Editor*

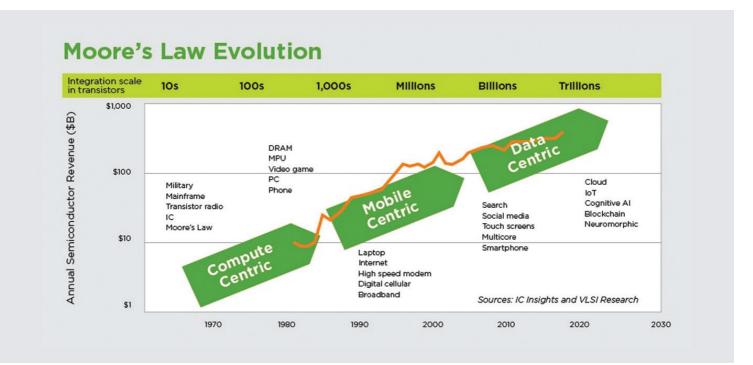

- **30** Industry Forum The rebirth of the semiconductor industry *Ajit Manocha, President and CEO of SEMI*

## DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 29 Ad Index

COVER

## editorial

## The cobbler's children getting shoes?

There's an old proverb that the shoemaker's children always go barefoot, indicating how some professionals don't apply their skills for themselves. Until lately, that has seemed the case with the semiconductor manufacturing industry which has been good at collecting massive amounts of data, but no so good at analyzing that data and using it to improve efficiency, boost yield and reduce costs. In short, the industry could be making better use of the technology it has developed.

That's now changing, thanks to a worldwide focus on Industry 4.0 – more commonly known as "smart manufacturing" in the U.S. – which represents a new approach to automation and data exchange in manufacturing technologies. It includes cyber-physical systems, the Internet of things, cloud computing, cognitive computing and the use of artificial intelligence/deep learning.

At SEMICON West this year, these trends will be showcased in a new Smart Manufacturing Pavilion where you'll be able to see - and experience - data-sharing breakthroughs that are creating smarter manufacturing processes, increasing yields and profits, and spurring innovation across the industry. Each machine along the Pavilion's multi-step line is displayed, virtually or with actual equipment on the floor - from design and materials through front-end patterning, to packaging and test to final board and system assembly.

In preparation for the show, I had the opportunity to talk to Mike Plisinski, CEO of Rudolph Technologies, the

sponsor of the Smart Pavilion about smart manufacturing. He said in the past "the industry got very good at collecting a lot of data. We sensors on all kinds of tools and equipment and we'd a track it with the idea of being able to do predictive maintenance or predictive analytics. That I think had minimal success," he said.

What's different now? "With the industry consolidating and the supply chains and products getting more complex that's created the need to go beyond what existed. What was inhibiting that in the past was really the ability to align this huge volume of data," he said. The next evolution is driven by the need to improve the processes. "As we've gone down into sub-20 manometer, the interactions between the process steps are more complex, there's more interaction, so understanding that interaction requires aligning digital threads and data streams." If a process chamber changed temperature by 0.1°C, for example, what impact did it have on lithography process by x, y, z CD control. That's the level of detail that's required. "That that has been a significant challenge and that's one of the areas that we've focused on over the last four, five years -- to provide that kind of data alignment across the systems,: Plisinski said.

Every company is different, of course, and some have been managing this more effectively than others, but the cobbler's children are finally getting new shoes.

-Pete Singer, Editor-in-Chief

## **Solid State** TECHNOLOGY.

Pete Singer, Editor-in-Chief Ph: 978.470.1806,

psinger@extensionmedia.com Shannon Davis, Editor, Digital Media Ph: 603 547 5309

sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor, edk@extensionmedia.com

Dave Lammers, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor Vivek Bakshi, Contributing Editor CREATIVE/PRODUCTION/ONLINE Marjorie Sharp, Production Traffic Coordinator

Nicky Jacobson, Senior Graphic Designer Slava Dotsenko, Senior Web Developer

MARKETING/CIRCULATION

Jenna Johnson, jjohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

**Clair Bright**, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2018 by Extension Media LLC. All rights reserved. Printed in the U.S.

AUGUST/SEPTEMBER 2018 VOL. 61 NO. 6 • Solid State Technology ©2018 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmaii: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for airmail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343, (8 am – 5 pm, PST).

MEDIA

Extension

1786 18th Street San Francisco, CA 94107

Yield Engineering Systems, Inc.

EcoClean

13

Revolutionary Productivity for Your Advanced Technologies!

Advanced Packaging, MEMS, LED, MicroLED, Power Devices and Sensors...

## **YES-ÉcoClean**

Automated Plasma Resist Strip/ Descum System (up to 200mm wafers)

- 2x faster, ½ the capital cost, and smaller footprint of comparative products

- Front-end and back-end processing with low cost ownership

- No defects or damage due to ICP Downstream Plasma

- Eco-friendly "Green" process

- Flexible System from Descum to Strip

100 to 100,000 Å/min

## Yield Engineering Systems, Inc.

Call: +1 925-373-8353 (worldwide) or 1-888-YES-3637 (US toll free) www.yieldengineering.com

# Online@www.solid-state.com

## **Web Exclusives**

## Top 10 semiconductor industry innovations

Over the past three decades, most of the world's innovations have centered largely on business models and involved iterative advances of existing technologies, with none matching the global impact of the top 10 semiconductor industry discoveries and advances, Dr. Morris Chang, founder of TSMC and the IC foundry model, said at SEMICON Taiwan 2018.

https://bit.ly/2xhzKaT

## CEA-Leti at SEMICON West 2018

Pete Singer, Solid State Technology's Editor-in-Chief, talked with Leti's CEO at SEMICON West 2018 about this year's Leti Innovation Days.

https://bit.ly/2Mxsltl

## Next on-chip: Human organs

Many new innovations were discussed at imec's U.S. International Technology Forum (ITF) at the Grand Hyatt in San Francisco, including quantum computing, artificial intelligence, sub-3nm logic, memory computing, solid-state batteries, EUV, RF and photonics, but perhaps the most interesting was new technology that enables human cells, tissues and organs to be grown and analyzed on-chip.

https://bit.ly/2PsckYV

## Subfab data growing in importance

The importance of data gathered and analysed in the subfab – the place where vacuum pumps, abatements systems and other supporting equipment operates – is growing. Increasingly, manufacturers are finding that these systems have a direct impact on yield, safety, cost-of-ownership and ultimately capacity and cycle time.

https://bit.ly/2o4v6sE

### 2018 EUVL Workshop Update

The 2018 EUVL Workshop was held last June at CXRO, LBL in Berkeley, jointly organized by EUV Litho, Inc. and CXRO.

https://bit.ly/2BGFXCZ

### Insights from the Leading Edge: Will Apple get caught in the trade war?

Why has the California-based company (Apple) enjoyed remarkable success in China, while some Chinese companies have experienced big losses amid a growing trade conflict with Washington? https://bit.ly/2MvhNQS

## Ruthenium nanolayers are ferromagnetic at RT

Researchers from Intel Corporation and the University of Minnesota and the University of Wisconsin have shown that strained atom-scale films of pure ruthenium (Ru) metal exhibit ferromagnetism at room temperature, openning up the possibility of using the material to build novel magnetic random access memory (MRAM) devices.

https://bit.ly/2MsM1UH

#### Gartner identifies five emerging technology trends that will blur the lines between human and machine

The 35 must-watch technologies represented on the Gartner Inc. Hype Cycle for Emerging Technologies, 2018 revealed five distinct emerging technology trends that will blur the lines between humans and machines. Emerging technologies, such as artificial intelligence (AI), play a critical role in enabling companies to be ubiquitous, always available, and connected to business ecosystems to survive in the near future. https://bit.ly/2PybBoU

## SEMICON<sup>®</sup> EUROPA

**Co-located with electronica** 2018

# SEMICONDUCTORS DRIVE SMART

## 13-16 Nov 2018, Messe München, Munich, Germany

This year SEMICON Europa will be the strongest single event for electronics manufacturing in Europe and is broadening the range of attendees across the electronics supply chain. The event covers the areas of Materials, Semiconductors, Frontend and Back-end Manufacturing, Advanced Packaging, MEMS/Sensors, Power and Flexible Electronics, and Automotive. **We connect the breadth of the entire electronics supply chain** by including applications such as the Internet of Things, Artificial Intelligence, Machine Learning, and other adjacent markets.

## **CONFERENCES:**

Automotive Forum 22<sup>nd</sup> Fab Management Forum 2018 FLEX Europe - Be Flexible Advanced Packaging Conference Strategic Materials Conference

## EXHIBITION AND FREE PROGRAMS:

Showfloor (Hall A4) TechARENA TechLOUNGE Talent & Leadership in the Digital Economy

## EXECUTIVE NETWORKING EVENTS:

Executive Keynote Opening SEMI Networking Night

## **KEY FACTS**

More than ...

35% visitors represent engineering job functions

70% involved in purchasing decisions

## Vu

33% are executives and senior managers

8,700 visitors from 85 countries registered in 2017

## INCREASE YOUR EXPOSURE!

Contact us to **become a sponsor!** SEMI Europe Sales: Denada Hodaj, dhodaj@semi.org

To **reserve your booth** contact SEMI Europe Tradeshow Operations: SEMICONEuropa@semi.org

Please send news articles to sdavis@extensionmedia.com

## worldnews

**EUROPE - Murata** announced investments in MEMS sensor manufacturing in Finland.

ASIA - Toshiba announced nextgeneration superjunction power MOSFETs.

**USA** - **Cabot Microelectronics** to acquire KMG Chemicals.

*EUROPE* - Soitec (Euronext Paris), a designer and manufacturer of semiconductor materials, and **MBDA** announce the joint acquisition of Dolphin Integration.

USA - pSemi Corporation (formerly Peregrine Semiconductor), a Murata company focused on semiconductor integration, introduced the world's first monolithic, silicon-on-insulator (SOI) Wi-Fi front-end module.

ASIA - TowerJazz announced details of its China Technical Global Symposium (TGS) event in Shanghai on August 22, 2018.

USA - Synopsys, Inc. and IBM announced a collaboration to apply design technology co-optimization (DTCO) to the pathfinding of new semiconductor process technologies for the 3-nanometer (nm) process node and beyond.

ASIA - Samsung Electronics started mass production of the industry's first 4-bit consumer SSD.

USA - Entegris, Inc. released the next generation EUV 1010 Reticle Pod for high-volume IC manufacturing using extreme ultraviolet (EUV) lithography.

USA - Leti and CMP announced the integrated-circuit industry's first multi-project-wafer (MPW) process for fabricating emerging non-volatile memory OxRAM devices on a 200mm foundry base-wafer platform.

# news

## Worldwide semiconductor revenue hit record \$120.8B in Q2 2018

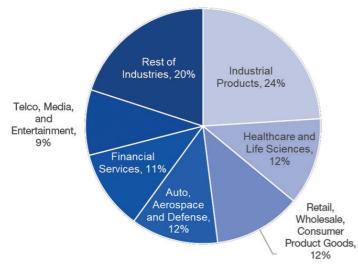

Global semiconductor industry revenue grew 4.4 percent, quarter over quarter, in the second quarter of 2018, reaching a record \$120.8 billion. Semiconductor growth occurred in all application markets and world regions, according to IHS Markit (Nasdaq: INFO).

"The explosive growth in enterprise and storage drove the market to new heights in the second quarter," said Ron Ellwanger, senior analyst and component landscape tool manager, IHS Markit. "This growth contributed to record application revenue in data processing and wired communication markets as well as in the microcomponent and memory categories."

Due to the ongoing growth in the enterprise and storage markets, sequential microcomponent sales grew 6.5 percent in the second quarter, while memory semiconductor revenue increased 6.4 percent. "Broadcom Limited experienced exceptional growth in its wired communication division, due to increased cloud and data-center demand," Ellwanger said. Memory component revenue continued to rise in the second quarter, compared to the previous quarter, reaching \$42.0 billion dollars. "This is the ninth consecutive quarter of rising revenue from memory components, and growth in the second quarter of 2018 was driven by higher density in enterprise and storage," Ellwanger said. "This latest uptick comes at a time of softening prices for NAND flash memory. However, more attractive pricing for NAND memory is pushing SSD demand and revenue higher."

### Semiconductor market share

Samsung Electronics continued to lead the overall semiconductor industry in the second quarter with 15.9 percent of the market, followed by Intel at 13.9 percent and SK Hynix at 7.9 percent. Quarter-overquarter market shares were relatively flat, with no change in the top-three ranking. SK Hynix achieved the highest growth rate and record quarterly sales among the top three companies, recording 16.4 percent growth in the second quarter.  $\diamondsuit$

#### Top 10 semiconductor supplier growth rates by revenue

| Q2-18<br>Rank | Company Name          | Q2-17<br>Revenue(\$) | Q1-18<br>Revenue(\$) | Q2-18<br>Revenue(\$) | YoY Grwoth | QoQ Growth |

|---------------|-----------------------|----------------------|----------------------|----------------------|------------|------------|

| 1             | Samsung Electronics   | 14,388               | 18,607               | 19,233               | 33.7%      | 3.4%       |

| 2             | Intel                 | 14,568               | 15,745               | 16,737               | 14.9%      | 6.3%       |

| 3             | SK Hynix              | 5,884                | 8,152                | 9,488                | 61.3%      | 16.4%      |

| 4             | Micron Technology     | 5,352                | 7,194                | 7,438                | 39.0%      | 3.4%       |

| 5             | Broadcom Limited      | 4,186                | 4,768                | 4,488                | 7.2%       | -5.9%      |

| 6             | Qualcomm              | 4,011                | 4,001                | 4,134                | 3.1%       | 3.3%       |

| 7             | Texas Instruments     | 3,575                | 3,697                | 3,905                | 9.2%       | 5.6%       |

| 8             | nVidia                | 1,966                | 2,660                | 2,826                | 43.7%      | 6.2%       |

| 9             | Toshiba Memory Corp.* | 2,015**              | 2,766                | 2,780                | 38.0%      | 0.5%       |

| 10            | Infineon Technologies | 2,057                | 2,256                | 2,273                | 10.5%      | 0.8%       |

|               | Top 10 Companies      | 58,002               | 69,846               | 73,302               | 26.4%      | 4.9%       |

|               | All Others            | 43,192               | 45,899               | 47,536               | 10.1%      | 3.6%       |

|               | Total Semiconductor   | 101,194              | 115,745              | 120,838              | 19.4%      | 4.4%       |

\*Toshiba Memory Corp new customer Q2 2018.

\*\*Q2 2017 revenue derived from Toshiba Semiconductor memory revenue.

Source: Competitive Landscaping Tool Intelligence Service, Q2 2018 © IHS Markit, 2018.

2019 MRS SPRING MEETING & EXHIBIT April 22–26, 2019 | Phoenix, Arizona

# CALL FOR PAPERS

**Abstract Submission Opens** September 28, 2018

Abstract Submission Closes October 31, 2018

## Spring Meeting registrations include MRS Membership July 1, 2019 – June 30, 2020

ES04

#### **BROADER IMPACT**

High Impact Practice—Increasing Ethnic and Gender Diversification BI01 in Engineering Education

#### CHARACTERIZATION, PROCESSING AND THEORY

- CP01 Advances in In Situ Experimentation Techniques Enabling Novel and Extreme Materials/Nanocomposite Design

- CP02 Design and In Situ TEM Characterization of Self-Assembling Colloidal Nanosystems CP03 Advances in In Situ Techniques for Diagnostics and Synthetic Design

- of Energy Materials

- CP04 Interfacial Science and Engineering-Mechanics, Thermodynamics, Kinetics and Chemistry

- CP05 Materials Evolution in Dry Friction—Microstructural, Chemical and Environmental Effects

- CP06 Smart Materials for Multifunctional Devices and Interfaces

- CP07 From Mechanical Metamaterials to Programmable Materials

- CP08 Additive Manufacturing of Metals

- CP09 Mathematical Aspects of Materials Science—Modeling, Analysis and Computations

#### **ELECTRONICS AND PHOTONICS**

#### Soft Organic and Bimolecular Electronics

- EP01 Liquid Crystalline Properties, Self-Assembly and Molecular Order

- in Organic Semiconductors FP02 Photonic Materials and Devices for Biointerfaces

- EP03 Materials Strategies and Device Fabrication for Biofriendly Electronics

- EP04 Soft and Stretchable Electronics—From Fundamentals to Applications

- EP05 Engineered Functional Multicellular Circuits, Devices and Systems

- EP06 Organic Electronics—Materials and Devices

#### Semiconductor Devices, Interconnects, Plasmonic and Thermoelectric Materials

- EP07 Next-Generation Interconnects-Materials, Processes and Integration EP08 Phase-Change Materials for Memories, Photonics, Neuromorphic

- and Emerging Application Devices and Materials to Extend the CMOS Roadmap for Logic FP09 and Memory Applications

- EP10 Heterovalent Integration of Semiconductors and Applications to Optical Devices

- EP11 Hybrid Materials and Devices for Enhanced Light-Matter Interactions

- EP12 Emerging Materials for Plasmonics, Metamaterials and Metasurfaces

- FP13 Thermoelectrics—Materials Methods and Devices

### www.mrs.org/spring2019

#### **Meeting Chairs**

Yuping Bao The University of Alabama

Bruce Dunn University of California, Los Angeles Subodh Mhaisalkar Nanyang Technological University

Ruth Schwaiger Karlsruhe Institute of Technology-

Institute for Applied Materials

Subhash L. Shinde University of Notre Dame

#### **Don't Miss These Future MRS Meetings!**

#### 2019 MRS Fall Meeting & Exhibit

December 1-6, 2019, Boston, Massachusetts

2020 MRS Spring Meeting & Exhibit April 13-17, 2020, Phoenix, Arizona

#### **ENERGY AND SUSTAINABILITY**

#### Energy Storage

- ES01 Organic Materials in Electrochemical Energy Storage

- ES02 Next-Generation Intercalation Batteries

- Electrochemical Energy Materials Under Extreme Conditions ES03

#### Solid-State Electrochemical Energy Storage Catalysis, Alternative Energy and Fuels

- ES05

- Cooperative Catalysis for Energy and Environmental Applications Atomic-Level Understanding of Materials in Fuel Cells and Electrolyzers ES06

- New Carbon for Energy-Materials, Chemistry and Applications ES07

- Materials Challenges in Surfaces and Coatings for Solar Thermal Technologies ES08

- Rational Designed Hierarchical Nanostructures for Photocatalytic System FS10

- Advanced Low Temperature Water-Splitting for Renewable Hydrogen Production ES11

- via Electrochemical and Photoelectrochemical Processes ES12

- Redox-Active Oxides for Creating Renewable and Sustainable Energy Carriers Water-Energy Materials and Sustainability

- FS09 Advanced Materials for the Water-Energy Nexus

- Materials Selection and Design-A Tool to Enable Sustainable Materials **FS13** Development and a Reduced Materials Footprint

- ES14 Materials Circular Economy for Urban Sustainability Photovoltaics and Energy Harvesting

- **FS15** Fundamental Understanding of the Multifaceted Optoelectronic Properties of Halide Perovskites

- ES16 Perovskite Photovoltaics and Optoelectronics

- ES17 Perovskite-Based Light-Emission and Frontier Phenomena-Single Crystals, Thin Films and Nanocrystals

- **FS18** Frontiers in Organic Photovoltaics

- ES19 Excitonic Materials and Quantum Dots for Energy Conversion

- ES20 Thin-Film Chalcogenide Semiconductor Photovoltaics

- FS21 Nanogenerators and Piezotronics

#### QUANTUM AND NANOMATERIALS

- QN01 2D Layered Materials Beyond Graphene—Theory, Discovery and Design

- QN02 Defects, Electronic and Magnetic Properties in Advanced 2D Materials **Beyond Graphene**

- QN03 2D Materials—Tunable Physical Properties, Heterostructures and Device Applications

- QN04 Nanoscale Heat Transport—Fundamentals

- Emerging Thermal Materials-From Nanoscale to Multiscale Thermal Transport, QN05 Energy Conversion, Storage and Thermal Management

- QN06 Emerging Materials for Quantum Information

- QN07 Emergent Phenomena in Oxide Quantum Materials

- QN08 Colloidal Nanoparticles-From Synthesis to Applications

#### SOFT MATERIALS AND BIOMATERIALS

- SM01 Materials for Biological and Medical Applications

- SM02 Progress in Supramolecular Nanotheranostics

- SM03 Growing Next-Generation Materials with Synthetic Biology

- SM04 Translational Materials in Medicine—Prosthetics, Sensors and Smart Scaffolds

- SM05 Supramolecular Biomaterials for Regenerative Medicine and Drug Delivery

- SM06 Nano- and Microgels

- SM07 Bioinspired Materials—From Basic Discovery to Biomimicry

### MATERIALS RESEARCH SOCIETY®

506 Keystone Drive • Warrendale, PA 15086-7573 Tel 724.779.3003 • Fax 724.779.8313 • info@mrs.org • www.mrs.org

## **NEWS**cont

## New material could improve efficiency of computer processing and memory

A team of researchers led by the University of Minnesota has developed a new material that could potentially improve the efficiency of computer processing and memory. The researchers have filed a patent on the material with support from the Semiconductor Research Corporation, and people in the semiconductor industry have already requested samples of the material.

The findings are published in Nature Materials, a peer-reviewed scientific journal published by Nature Publishing Group.

"We used a quantum material that has attracted a lot of attention by the semiconductor industry in the past few years, but created it in unique way that resulted in a material with new physical and spin-electronic properties that could greatly improve computing and memory efficiency," said lead researcher Jian-Ping Wang, a University of Minnesota Distinguished McKnight Professor and Robert F. Hartmann Chair in electrical engineering.

The new material is in a class of materials called "topological insulators," which have been studied recently by physics and materials research communities and the semiconductor industry because of their unique spin-electronic transport and magnetic properties. Topological insulators are usually created using a single crystal growth process. Another common fabrication technique uses a process called Molecular Beam Epitaxy in which crystals are grown in a thin film. Both of these techniques cannot be easily scaled up for use in the semiconductor industry.

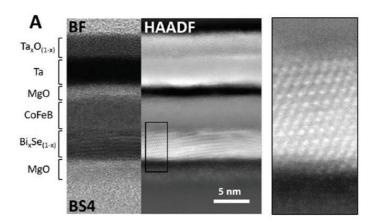

In this study, researchers started with bismuth selenide  $(Bi_2Se_3)$ , a compound of bismuth and selenium. They then used a thin film deposition technique called "sputtering," which is driven by the momentum exchange between the ions and atoms in the target materials due to collisions. While the sputtering technique is common in the semiconductor industry, this is the first time it has been used to create a topological insulator material that could be scaled up for semiconductor and magnetic industry applications.

However, the fact that the sputtering technique worked was not the most surprising part of the experiment. The nano-sized grains of less than 6 nanometers in the sputtered topological insulator layer created new physical properties for the material that changed the behavior of the electrons in the material. After testing the new material, the researchers found it to be 18 times more efficient in computing processing and memory compared to current materials.

"As the size of the grains decreased, we experienced what we call 'quantum confinement' in which the electrons in the material act differently giving us more control over the electron behavior," said study co-author Tony Low, a University of Minnesota assistant professor of electrical and computer engineering.

Researchers studied the material using the University of Minnesota's unique high-resolution transmission electron microscopy (TEM), a microscopy technique in which a beam of electrons is transmitted through a specimen to form an image.

"Using our advanced aberration-corrected scanning TEM we managed to identify those nano-sized grains and their interfaces in the film," said Andre Mkhoyan, a University of Minnesota associate professor of chemical engineering and materials science and electron microscopy expert.

Researchers say this is only the beginning and that this discovery could open the door to more advances in the semiconductor industry as well as related industries, such as magnetic random access memory (MRAM) technology.

"With the new physics of these materials could come many new applications," said Mahendra DC (Dangi Chhetri), first author of the paper and a physics Ph.D. student in Professor Wang's lab.

Wang agrees that this cutting-edge research could make a big impact.

"Using the sputtering process to fabricate a quantum material like a bismuth-selenide-based topological insulator is against the intuitive instincts of all researchers in the field and actually is not supported by any existing theory," Wang said. "Four years ago, with a strong support from Semiconductor Research Corporation and the Defense Advanced Research Projects Agency, we started with a big idea to search for a practical pathway to grow and apply the topological insulator material for future computing and memory devices. Our surprising experimental discovery led to a new theory for topological insulator materials.

"Research is all about being patient and collaborating with team members. This time there was a big pay off," Wang said.

## Size of semiconductor acquisitions may have hit limit

The demise of Qualcomm's pending \$44 billion purchase of NXP Semiconductors in late July along with growing regulatory reviews of chip merger agreements, efforts by countries to protect domestic technology, and the escalation of global trade friction all suggest semiconductor acquisitions are hitting a ceiling in the size of doable deals. It is becoming less likely that semiconductor acquisitions over \$40 billion can be completed or even attempted in the current geopolitical environment and brewing battles over global trade.

### **Biggest Semiconductor Acquisition Announcements**

| Ranking | Acquisition-Buyer (Year Announced)                   | Price (\$B) |

|---------|------------------------------------------------------|-------------|

| 1       | NXP by Qualcomm (struck in 2016 and raised in 2018)* | \$44.0      |

| 2       | Broadcom by Avago (2015)                             | \$37.0      |

| 3       | ARM by SoftBank (2016)                               | \$32.0      |

| 4       | SanDisk by Western Digital (2015)                    | \$19.0      |

| 5       | Toshiba Memory by Bain Capital-Led Consortium (2017) | \$18.0      |

| 6       | Freescale by U.S Investment Companies (2006)         | \$17.6      |

| 7       | Altera by Intel (2015)                               | \$16.7      |

| 8       | Linear Technology by Analog Devices (2016)           | \$14.8      |

| 9       | Freescale by NXP (2015)                              | \$11.8      |

| 10      | Burr Brown by Texas Instruments (2000)               | \$7.6       |

\*Canceled in late July 2018 after failing to win clearance from China. Source: Companies, IC Insights

IC Insights believes a combination of factors—including the growing high dollar value of major chip merger agreements, complexities in combining large businesses together, and greater scrutiny of governments protecting their domestic base of suppliers—will stifle ever-larger mega-transactions in the semiconductor industry in the foreseeable future. Figure 1 ranks the 10 largest semiconductor merger and acquisition announcements and underscores the growth in size of these M&A transactions. Eight of the 10 largest announcements occurred in the last three years with only the biggest deal (Qualcomm buying NXP) failing to be completed.

It is important to note that IC Insights' M&A list only covers semiconductor suppliers, chipmakers, and providers of integrated circuit intellectual property (IP) and excludes acquisitions of software and system-level businesses by IC companies (such as Intel's \$15.3 billion purchase of Mobileye, an Israelibased developer of digital imaging technology for autonomous vehicles, in August 2017). This M&A list also excludes transactions involving semiconductor capital equipment suppliers, material producers, chip packaging and testing companies, and design automation software firms.

Qualcomm's \$44 billion cash purchase of NXP would have been the largest semiconductor acquisition ever if it was completed, but the deal—originally announced in October 2016 at nearly \$39 billion and raised to \$44 billion in February 2018—was canceled in the last week of July because China had not cleared the transaction. China was the last country needed for an approval of the merger, and it was believed to be close to clearing the purchase in 2Q18, but growing threats of

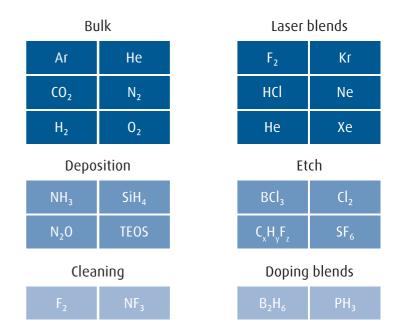

## Local partner. Global expertise.

Providing a complete portfolio of gases for every display process using local production and global supply chains

### Giving our display partners a competitive edge

- → High-efficiency SPECTRA-N<sup>™</sup> nitrogen generators

- → Local production of bulk gases

- → New N<sub>2</sub>O production investments in Mainland China, South Korea, and Taiwan

- $\rightarrow$  Multiple sources of He, NH<sub>3</sub>, NF<sub>3</sub>, and SiH<sub>4</sub>

- → Robust global supply chains of etchants

- → Precision blending for dopant and laser mixtures

www.linde.com/electronics electronicsinfo@linde.com

www.solid-state.com

tariffs in a brewing trade war with the U.S. and moves to block Chinese acquisitions of American IC companies caused China to taken no action on the \$44 billion acquisition in time for a deadline set by Qualcomm and NXP. U.S.-based Qualcomm canceled the acquisition on July 26 and guickly paid NXP in the Netherlands a \$2 billion breakup fee so the two companies could move on separately.

Prior to Qualcomm's failed \$44 billion offer for NXP, the largest semiconductor acquisition was Avago Technologies' \$37 billion cash and stock purchase of Broadcom in early 2016. Avago renamed itself Broadcom Limited after the purchase and launched a failed \$121 billion hostile takeover bid for Qualcomm at the end of 2017. It lowered the unsolicited bid to \$117 billion in February 2018 after Qualcomm raised its offer for NXP to \$44 billion. In March 2018, U.S. President Donald Trump blocked Broadcom's \$117 billion takeover bid for Qualcomm after concerns were raised in the U.S. government about the potential loss of cellular technology leadership to Chinese companies, if the hostile acquisition was completed. After the presidential order, Broadcom executives said the company was considering other acquisition targets, with cash, that would be smaller and more focused.

The global semiconductor industry has been reshaped by a historic wave of mergers and acquisitions during the past three years, with about 100 M&A agreements being reached between 2015 and the middle of 2018 with the combined value of these transactions being more than \$245 billion, based on data collected by IC Insights and contained within its Strategic Reviews database subscription service and in The 2018 McClean Report on the IC Industry. A record-high \$107.3 billion in semiconductor acquisition agreements were announced in 2015. The second highest total for semiconductor M&A agreements was then reached in 2016 at \$99.8 billion. Semiconductor acquisition announcements reached a total value of \$28.3 billion in 2017, which was twice the industry's annual average of about \$12.6 billion in the first half of this decade but significantly less than 2015 and 2016, when M&A was sweeping through the chip industry at historic levels. In the first six months of 2018, semiconductor acquisition announcements had a total value of about \$9.6 billion, based on IC Insights' running tally of announced M&A deals.

## Seven top 15 semi suppliers of the first half of 2018 register ≥20% gains

IC Insights released its August Update to the 2018 McClean Report earlier this month. This Update included a discussion of the top-25 semiconductor suppliers in 1H18 (the top-15 1H18 semiconductor suppliers are covered in this research bulletin) and Part 1 of an extensive analysis of the IC foundry market and its suppliers.

The top-15 worldwide semiconductor (IC and O-S-D-optoelectronic, sensor, and discrete) sales ranking for 1H18 is shown in Figure 1. It includes seven suppliers headquartered in the U.S., three in Europe, two each in South Korea and Taiwan, and one in Japan. After announcing in early April 2018 that it had successfully moved its headquarters location from Singapore to the U.S. IC Insights now classifies Broadcom as a U.S. company.

and four fabless companies. If TSMC were excluded from the top-15 ranking, U.S.-based Apple would have been ranked in the 15th position. Apple is an anomaly in the top company ranking with regards to major semiconductor suppliers. The company designs and uses its processors only in its own products-there are no sales of the company's MPUs to other system makers. IC Insights estimates that Apple's custom ARM-based SoC processors and other custom devices had a "sales value" of \$3.5 billion in 1H18.

IC Insights includes foundries in the top-15 semiconductor supplier ranking since it has always viewed the ranking as a top supplier list, not a marketshare ranking, and realizes that in some cases the semiconductor sales are double counted. With many of our clients being vendors to the semiconductor industry (supplying equipment, chemicals, gases, etc.), excluding large IC manufacturers like the foundries would leave

As shown, all but four of the top 15 companies had double-digit year-over-year growth in 1H18. Moreover, seven companies

had  $\geq 20\%$  growth, including the five big memory suppliers (Samsung, SK Hynix, Micron, Toshiba/ Toshiba Memory, and Western Digital/ SanDisk) as well as Nvidia and ST.

The top-15 ranking includes one pureplay foundry (TSMC)

| 1H18 | 2017 | Company                | Headquarters | 1Q18   | 1Q18      | 1Q18     | 2Q18   | 2Q18      | 2Q18            | 2Q18/1Q18 | 1H18     | 1H17     | 1H18/1H17 |

|------|------|------------------------|--------------|--------|-----------|----------|--------|-----------|-----------------|-----------|----------|----------|-----------|

| Rank | Rank | company                | neauquarters | Tot IC | Tot O-S-D | Tot Semi | Tot IC | Tot O-S-D | <b>Tot Semi</b> | % Change  | Tot Semi | Tot Semi | % Change  |

| 1    | 1    | Samsung                | South Korea  | 18,491 | 910       | 19,401   | 19,434 | 950       | 20,384          | 5%        | 39,785   | 29,181   | 36%       |

| 2    | 2    | Intel                  | U.S.         | 15,832 | 0         | 15,832   | 16,753 | 0         | 16,753          | 6%        | 32,585   | 28,839   | 13%       |

| 3    | 4    | SK Hynix               | South Korea  | 8,016  | 125       | 8,141    | 9,421  | 192       | 9,613           | 18%       | 17,754   | 11,393   | 56%       |

| 4    | 3    | TSMC (1)               | Taiwan       | 8,473  | 0         | 8,473    | 7,839  | 0         | 7,839           | -7%       | 16,312   | 14,601   | 12%       |

| 5    | 5    | Micron                 | U.S.         | 7,486  | 0         | 7,486    | 7,920  | 0         | 7,920           | 6%        | 15,406   | 10,653   | 45%       |

| 6    | 6    | Broadcom Ltd. (2)      | U.S.         | 4,125  | 434       | 4,559    | 4,150  | 435       | 4,585           | 1%        | 9,144    | 8,404    | 9%        |

| 7    | 7    | Qualcomm (2)           | U.S.         | 3,897  | 0         | 3,897    | 4,087  | 0         | 4,087           | 5%        | 7,984    | 7,728    | 3%        |

| 8    | 9    | Toshiba/Toshiba Memory | Japan        | 3,517  | 310       | 3,827    | 3,575  | 315       | 3,890           | 2%        | 7,717    | 6,159    | 25%       |

| 9    | 8    | ті                     | U.S.         | 3,339  | 227       | 3,566    | 3,535  | 245       | 3,780           | 6%        | 7,346    | 6,595    | 11%       |

| 10   | 10   | Nvidia (2)             | U.S.         | 3,108  | 0         | 3,108    | 3,135  | 0         | 3,135           | 1%        | 6,243    | 4,083    | 53%       |

| 11   | 15   | WD/SanDisk             | U.S.         | 2,350  | 0         | 2,350    | 2,375  | 0         | 2,375           | 1%        | 4,725    | 3,715    | 27%       |

| 12   | 13   | Infineon               | Europe       | 1,360  | 907       | 2,267    | 1,388  | 926       | 2,314           | 2%        | 4,581    | 3,896    | 18%       |

| 13   | 11   | NXP                    | Europe       | 2,017  | 252       | 2,269    | 2,035  | 255       | 2,290           | 1%        | 4,559    | 4,413    | 3%        |

| 14   |      | ST                     | Europe       | 1,696  | 518       | 2,214    | 1,724  | 526       | 2,250           | 2%        | 4,464    | 3,732    | 20%       |

| 15   | 16   | MediaTek (2)           | Taiwan       | 1,696  | 0         | 1,696    | 2,032  | 0         | 2,032           | 20%       | 3,728    | 3,726    | 0%        |

| _    | -    | Top-15 Total           |              | 85,403 | 3,683     | 89,086   | 89,403 | 3,844     | 93,247          | 4.7%      | 182,333  | 147,118  | 24%       |

#### 1H18 Top-15 Semiconductor Sales Leaders (SM, Including Foundries)

\*Custom devices for internal use

significant "holes" in the list of top semiconductor suppliers. Foundries and fabless companies are identified in the Figure. In the April Update to The McClean Report, marketshare rankings of IC suppliers by product type were presented and foundries were excluded from these listings.

Overall, the top-15 list shown in **Figure 1** is provided as a guideline to identify which companies are the leading semiconductor suppliers, whether they are IDMs, fabless companies, or foundries.

In May 2018, Toshiba completed the \$18.0 billion sale of its memory IC business to the Bain Capital-led consortium. Toshiba then repurchased a 40.2% share of the business. The Bain consortium goes by the name of BCPE Pangea and the group owns 49.9% of Toshiba Memory Corporation (TMC). Hoya Corp. owns the remaining 9.9% of TMC's shares. The new owners have plans for an IPO within three years. Bain has said it plans to support the business in pursing M&A targets, including potentially large deals. As a result of the sale of Toshiba's memory business, the 2018 sales results shown in **Figure 1** include the combined sales of the remaining semiconductor products at Toshiba (e.g., Discrete devices and System LSIs) and the new Toshiba Memory's NAND flash sales. The estimated breakdown of these sales in 2018 is shown below:

Toshiba System LSI: \$468M Toshiba Discrete: \$315M Toshiba Memory Corporation: \$3,107M

#### Total Toshiba/Toshiba Memory Corporation 2Q18 Sales: \$3,890M

In total, the top-15 semiconductor companies' sales surged by 24% in 1H18 compared to 1H17, four points higher than the total worldwide semiconductor industry 1H18/1H17 increase of 20%. Amazingly, the Big 3 memory suppliers—Samsung, SK Hynix, and Micron, each registered greater than 35% year-over-year growth in 1H18. Fourteen of the top-15 companies had sales of at least \$4.0 billion in 1H18, three companies more than in 1H17. As shown, it took just over \$3.7 billion in sales just to make it into the 1H18 top-15 semiconductor supplier list.

Intel was the number one ranked semiconductor supplier in 1Q17 but lost its lead spot to Samsung in 2Q17 as well as in the full-year 2017 ranking, a position it had held since 1993. With the continuation of the strong surge in the DRAM and NAND flash markets over the past year, Samsung went from having only 1% more total semiconductor sales than Intel in 1H17 to having 22% more semiconductor sales than Intel in 1H18!

It is interesting to note that memory devices are forecast to represent 84% of Samsung's semiconductor sales in 2018, up three points from 81% in 2017 and up 13 points from 71% just two years earlier in 2016. Moreover, the company's non-memory sales in 2018 are expected to be only \$13.5 billion, up 8% from 2017's non-memory sales level of \$12.5 billion. In contrast, Samsung's memory sales are forecast to be up 31% this year and reach \$70.0 billion.

## **LEAK DETECTION SOLUTIONS**

Mobile leak detectors ASM 390 and ASM 392 optimized for rapid pump down and short response times on large test objects

- High maneuverability and compact design

- Superior leak testing performances

- High roughing capacity (35 m<sup>3</sup>/h) for fast evacuation

- Fully Semi S2 compliant

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com · www.pfeiffer-vacuum.com

# Chiplet tech discussed at DARPA ERI kickoff

PHIL GARROU, Contributing Editor

With "Moore's Law", which has guided the electronics industry for more than 50 years, being challenged on both technical and economic grounds, the defense department (DARPA) is putting \$1.5 billion into projects that could "radically alter how electronics are made".

Investments will support R&D in the areas of Architectures, Design, and Materials and Integration. It is hoped that investments in these three thrust areas will lead the next wave of U.S. semiconductor advancement.

DARPA kicked off the initiative and revealed some of the winning proposals July 23-25 in San Francisco.

**Architectures:** The goal of the *Software Defined Hardware* (*SDH*) program is to build runtime-reconfigurable hardware and software that enables near application-specific integrated circuit (ASIC) performance without sacrificing programmability for data-intensive algorithms. Intel, NVIDIA, Qualcomm, Systems & Technology Research, Georgia Tech, Stanford Univ, U Michigan, U of Washington and Princeton Univ were selected for the SDH program.

The goal of the *Domain-specific System on Chip (DSSoC)* program is to develop a heterogeneous SoC comprised of many cores that mix general-purpose processors, special-purpose processors, hardware accelerators, memory, and input/output (I/O). IBM, Oak Ridge National Labs, Arizona St Univ and Stanford Univ were chosen for the DSSoC program.

**Design:** The goal of the *Posh Open Source Hardware (POSH)* program is to create an open source SoC design and verification ecosystem that will enable the cost-effective design of ultra-complex SoCs. Univ of California, San Diego, Northrop Grumman, Cadence, Xilinx, Synopsys, Univ of Southern California, Princeton Univ and Sandia National Labs were selected for the POSH program.

**Materials & Integration:** The overall goal of the *Three Dimensional Monolithic System-on-a-Chip (3DSoC)* program is to develop 3D monolithic technology that will enable > 50X improvement in SoC digital performance at power. 3DSoC aims to drive research in process, design tools, and new compute

## Packaging

architectures utilizing U.S. fabrication capabilities. Georgia Tech, Stanford Univ, MIT and Skywater Technology Foundry were chosen for the 3DSoC program. The goal of the *Foundations Required for Novel Compute* (*FRANC*) program is to define the foundations required for assessing and establishing the proof of principle for beyond von Neumann compute architectures. HRL, Applied Materials, Ferric, UCLA, Univ of Minnesota and Univ of Illinois at Urbana-Champaign have been chosen for the FRANC program.

Also, *Common Heterogeneous Integration and Intellectual Property (IP) Reuse Strategies (CHIPS)* has now been included under the ERI umbrella. The CHIPS program envisions an ecosystem of discrete modular, reusable IP blocks that can be assembled into a system using existing and emerging integration technologies. The program will develop the design tools and integration standards required to demonstrate modular integrated circuit (IC) designs that leverage the best of DoD and commercial designs and technologies.

Instead of building complex SoC on silicon the CHIPS concept sees future systems where each function is made separately (chiplets) and are then connected together on a larger slice of silicon by high-bandwidth interconnects. One of the challenges will be getting these chiplets to communicate properly and do so at a speed and energy cost that's close to what they'd be if the system were all one piece of silicon. Interconnects using the standard will have to be capable of handling a lot of data without using much energy. It is estimated that it will have to cost less than 1 pico-joule to move a bit and be capable of moving 1 terabit per millimeter.

At the ERI kick-off, Intel CTO Mike Mayberry, who is VP and managing director of Intel Labs and holds responsibility for Intel's global research efforts in computing and communications, revealed that Intel will provide their Advanced Interface Bus (AIB) technology, to program participants, royalty-free to help link chiplets together. AIB is a standard communications interface made for connecting different dies (chiplets) in the same package. Intel already uses AIB in 2.5-D packages such as the company's Stratix 10 FPGA.

DARPAs Andreas Olofsson, manager of DARPA's CHIPS program, reitterated the need for a standard communications interface. "We need a plug-and-play standard," he said. "Once we have that standard, you can imagine vendors offering a ,number of chiplets for sale." The CHIPS program community is in the process of accepting the Intel AIB technology for this purpose.  $\triangleleft$

# Integrated 5G chip directions

ED KORCZYNSKI, Sr. Technical Editor

To fulfill the promise of the Internet of Things (IoT), the world needs low-cost high-bandwidth radio-frequency (RF) chips for 5th-generation (5G) internet technology. Despite standards not being completely defined yet it is clear that 5G hardware will have to be more complex than 4G kit, because it will have to provide a total solution that is ultra-reliable with at least 10 Gb/second bandwidth. A significant challenge remains in developing new high-speed transistor technologies for RF communications with low power to allow IoT "edge" devices to operate reliably off of batteries.

At the most recent Imec Technology Forum in Antwerp, Belgium, Nadine Collaert, Distinguished MTS of imec, discussed recent research results from the consortium's High-Speed Analog and RF Program. In addition to working on core transistor fabrication technology R&D, imec has also been working on system-technology co-integration (STCO) and design-technology co-integration (DTCO) for RF applications.

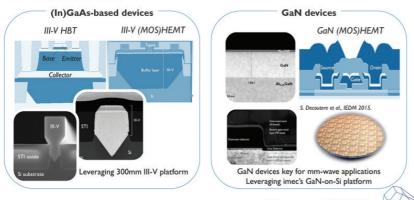

Comparing the system specifications needed for mobile handsets to those for base-stations, transmitter power consumption should be 10x lower, while the receiver power consumption needs to be 2x lower. Today using silicon CMOS transistors, four power amplifiers alone consume 65% of a transmitter chip's power. Heterogeneous Bipolar Transistors (HBT) and High Electron Mobility Transistors (HEMT) built using compound semiconductors such as gallium-arsenide (GaAs), gallium-nitride (GaN), or indium-phosphide (InP) provide excellent RF device results. However, compared to making CMOS chips on silicon, HBT and HEMT manufacturing on compound semiconductor substrates is inherently expensive and difficult.

#### TWO MAIN TRACKS

**FIGURE 1.** III-V on Silicon and GaN-on-Silicon RF device cross-sections, showing work on both Heterogeneous Bipolar Transistors (HBT) and High Electron Mobility Transistors (HEMT) for 5G applications. (Source: imec)

Heterogeneous Bipolar Transistors (HBT) and High Electron Mobility Transistors (HEMT) both rely upon the precise epitaxial growth of semiconductor layers, and such growth is easier when the underlying substrate material has similar atomic arrangement. While it is much more difficult to grow epi-layers of compound semiconductors on silicon wafers, imec does R&D using 300-mm diameter silicon substrates with a goal of maintaining device quality while lowering production costs. **FIGURE 1** shows cross-sections of the two "tracks" of III-V and GaN transistor materials being explored by imec for future RF chips.

Imec's High-Speed Analog/RF Program objectives include the following:

- High-speed III-V RF devices using low-cost, highvolume silicon-compatible processes and modules,

- Co-optimization with advance silicon CMOS to reduce form factor and enable power-efficient systems with higher performance, and

- Technology-circuit design co-optimization to enable complex RF-FEM modules with heterogeneous integration.

5G technology deployment will start with speeds below 6GHz, because technologies in that range have already been proven and the costs are known. However, after five years the frequency will change to the "mm-wave" range with the first wavelength band at ~28GHz. GaN material with a wide bandgap and high charge-density has been a base-station technology, and it could be an ideal material for low-power mm-wave RF devices for future handsets.

This R&D leverages the III-V on silicon capability that has been developed by imec for CMOS:Photonic integration. RF transistors could be stacked over CMOS transistors using either wafer- or die-stacking, or both could be monolithically co-integrated on one silicon chip. Work on monolithic integration of GaN-on-Silicon is happening now, and could also be used for photonics where faster transistors can improve the performance of optical links. ◆

## Semiconductors

# Emerging memory types headed for volumes

DAVID LAMMERS, Contributing Editor

Two emerging memory types – 3D Xpoint and e-MRAM -- are now coming to the market.

fter decades of R&D, two emerging memory types – the phase change memory-based 3D Xpoint, co-developed by Intel and Micron, and the embedded spin-torque transfer magnetic RAM (e-MRAM) from several foundries – are now coming to the market. One point of interest is that neither memory type relies on the charge-based SRAM and DRAM memory technologies that increasingly face difficult scaling challenges. Another is that both have inherent performance advantages that could extend their uses for decades to come.

3D XPoint is a storage class memory (SCM) based on phasechange that fits in between fast DRAM and non-volatile NAND; it is currently available in both SSDs and sampling in a DIMM form factor. David Kanter, an analyst at Real World Technologies (San Francisco) said the Optane SSDs are selling now but the DIMMs are shaping up to be "an early 2019 story" in terms of real adoption. "People are very excited about the DIMMs, including customers, software developers, the whole computer ecosystem. There is a lot of software development going on that is required to take advantage of it, and a lot of system companies are saying they can't wait. They are telling Intel 'give me the hardware.'"

"Intel is taking the long view" when it comes to 3D XPoint (the individual devices) and Optane (the SSDs and DIMMs), Kanter said. "This is a new technology and it is not a trivial thing to bring it to the market. It is a testament to Intel that they are taking their time to properly develop the ecosystem."

However, Kanter said there is not enough public information about 3D XPoint DIMMs, including performance, price, power consumption, and other metrics. Companies that sell enterprise database systems, such as IBM, Microsoft, Oracle, SAP, and others, are willing to pay high prices for a storage-class memory solution that will improve their performance. The Optane DIMMs, according to Intel, are well-suited to "large-capacity in-memory database solutions." According to the Intel Web site, Optane DC persistent memory (**FIGURE 1**) "is sampling today and will ship for revenue to select customers later this year, with broad availability in 2019." It can be placed on a DDR4 module alongside DRAM, and matched up with next-generation Xeon processors. Intel is offering developers remote access to systems equipped with Optane memory for software development and testing.

Speaking at the Symposium on VLSI Technology in Honolulu, Gary Tressler, a distinguished engineer at IBM Systems, said "the reliability of 3D NAND impacts the enterprise," and predicted that the Optane storage class memory will serve to improve enterprise-class systems in terms of reliability and performance.

The DRAM scaling picture is not particularly bright. Tressler said "it could be four years before we go beyond the 16-gigabit size in terms of DRAM density." DRAM companies are eking out scaling improvements of 1nm increments," an indication of the physical limitations facing the established DRAM makers.

Al Fazio, a senior fellow at Intel who participated in the memory-related evening panel at the VLSI symposia, and said that the early adopters of the Optane technology have seen significant benefits: one IT manager told Fazio that

## Storage/Memory Gap solutions (2/3): SCM

|              | Storage<br>typ | : "M"                            |                                  |  |  |

|--------------|----------------|----------------------------------|----------------------------------|--|--|

|              |                | S-SCM                            | M-SCM                            |  |  |

| Protoco      | bl             | Storage*                         | Memory                           |  |  |

| Interface    |                | Asynchronous                     | Synchronous                      |  |  |

| Latency (us) |                | 3-20                             | 0.1-1.0                          |  |  |

| Endurance    |                | 10 <sup>8</sup> -10 <sup>9</sup> | 10 <sup>8</sup> -10 <sup>9</sup> |  |  |

| Retention    |                | ~years                           | Weeks-months                     |  |  |

| Examp        | les            | Fast NAND,<br>Optane ®*          | 3D-XPOINT<br>DIMM                |  |  |

\*Note: although the Optane product is packaged as a block device, the component has a native 16B access

**FIGURE 2.** The drawback to phase change memories, such as 3D XPoint, is the relatively high write-energy-per-bit. Source: Chris Petti, Western Digital, short course presentation at 2018 Symposium on VLSI Circuits.

by adding a layer of Optane SSD-based memory he was able to rebuild a database in seconds versus 17 minutes previously. Fazio said he takes particular pride in the fact that, because of Optane, some doctors are now able to immediately read the results of magnetic resonance imaging (MRI) tests.

"An MRI now takes two minutes instead of 40 minutes to render," Fazio said, adding that a second-generation of 3D Xpoint is being developed which he said draws upon "materials improvements" to enhance performance.

Chris Petti, a senior director of advanced technology at Western Digital, said DRAM pricing has been "flat for the last five to seven years," making it more expensive to simply add more DRAM to overcome the latency gap between DRAM and flash. "DRAM is not scaling so there are a lot of opportunities for a new technology" such as Optane or the fast NAND technologies, he said. Samsung is working on a single-bit-per-cell form of Fast NAND.

In a Monday short course on emerging memory technologies at the Symposium on VLSI Circuits, Petti said the drawback to phase change memories (PCMs), such as 3D XPoint, is the relatively high write-energy-per-bit (**FIGURE 2**), which he estimated at 460 pJ/bit, compared with 250 pJ/bit for standard NAND (based on product spec sheets). In terms of cost, latency, and endurance, Petti judged the PCM memories to be in the "acceptable" range. While the price is five to six times the price-per-bit of standard NAND, Petti noted that the speed improves "because PCM (phase change memory) is inherently faster than charge storage." Phase-change materials, such as  $Ge_2Sb_2Te_5$ , change between two different atomic structures, each of which has a different electronic state. A crystalline structure allows electrons to flow while an amorphous structure blocks the flow. The two states are changed by heating the PCM bit electrically.

Philip Wong, a Stanford University professor, said the available literature on PCM materials shows that they can be extremely fast; the latencies at the SSD and DIMM levels are largely governed by "protocols." In 2016, a team of Stanford researchers said the fundamental properties of phasechange materials could be as much as a thousand times faster than DRAM.

In a keynote speech at the VLSI symposia, Scott DeBoer, executive vice president of technology development at Micron (Boise, Idaho), said "clearly the most successful

conaxtechnologies.com/etchdefender SM<sup>a</sup> and EPSILON<sup>a</sup> are registered trademarks of ASM<sup>a</sup> International. Neither Conax Technolog por its products are atfiliated with, approved by or sponsored by ASM<sup>a</sup> International. of the emerging memories is 3D XPoint, where the technology performance has been proven and volume production is underway. 3D XPoint performance and density are midway between DRAM and NAND, which offers opportunities to greatly enhance system-level performance by augmenting existing memory technologies or even directly replacing them in some applications."

Currently, the 3D XPoint products are made at a fab in Lehigh, Utah. The initial technology stores 128Gb per die across two stacked memory layers. Future generations can either add more memory layers or use lithographic pitch scaling to increase die capacity, according to Micron.

DeBoer noted that "significant system-level enablement is required to exploit the full value of 3D XPoint memory, and this ongoing effort will take time to fully mature."

## eMRAM race begins by major foundries

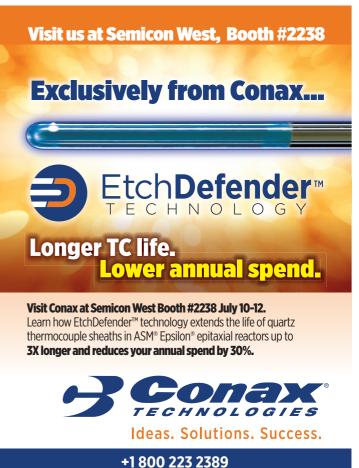

Magnetic RAM technology has been under serious development for three decades, resolving significant hurdles along the way with breakthroughs in MgO magnetic materials and device architecture. Everspin Technology has been shipping discrete MRAM devices for nearly a decade, and the three major foundries are readying embedded MRAM for SoCs, automotive ICs, and other

**FIGURE 3.** MRAM performance is largely controlled by the quality of the PVD-deposited layers in the MTJ (SAF is synthetic antiferromagnetic). Source: Lin Xue, et al, Applied Materials presentation at 2018 Symposium on VLSI Technology. products. The initial target is to replace NOR-type flash on devices, largely due to the large charge pumps required to program NOR devices which add multiple mask layers.

GlobalFoundries, which manufactures the Everspin discrete devices, has qualified eMRAM for its 22nm FD-SOI process, called 22FDX. TSMC also has eMRAM plans.

At the Symposium on VLSI Technology, Samsung Foundry (Giheung, Korea) senior manager Yong Kyu Lee described an embedded STT-MRAM in a 28-nm FDSOI logic process, aimed at high-speed industrial MCU and IoT applications. Interestingly, Lee said compared with the bulk (non-SOI) 28-nm process, the FD-SOI technology "has superior RF performance, low power, and better analog characteristics than 28-nm bulk and 14-nm FinFET CMOS." Lee indicated that the FD-SOI-based eMRAM would be production-ready later this year.

Samsung ported its STT perpendicular-MTJ (magnetic tunnel junction) eMRAM technology from its 28-nm bulk to its FD-SOI CMOS process. The company offers the eMRAM as a module, complementing an RF module. The "merged embedded STT MRAM and RF-CMOS process is compatible to the existing logic process, enabling reuse of IP," he said.

Looking forward to the day when MRAM could complement or replace SRAM, Lee said "even though we have not included data in this paper, our MTJ shows a potential for storage working memory due to high endurance (>1E10) and fast writing (<30ns).

## Beyond embedded to last level cache

As foundries and their customers gain confidence in eMRAM's retention, power consumption, and reliability, it will begin to replace NOR flash at the 40-nm, 28-nm, and smaller nodes. However, future engineering improvements are needed to tackle the SRAM-replacement.

SRAM scaling is proving increasingly difficult, both in terms of the minimum voltages required and the size of the six-transistor-based bits. MRAM researchers are in hot pursuit of the ability to use replace some of the SRAM on processors with Last Level Cache (LLC) iterations of magnetic memory. These LLC MRAMs would be fabricated at the 7nm, 5nm, or beyond nodes.

Mahendra Pakala, senior director of memory and materials at the Applied Materials Advanced Product Technology Development group, said for eMRAM the main challenges now are achieving high yields with less shorting between the magnetic tunnel junctions (MTJs). 'The big foundries have been working through those problems, and embedded MRAM is getting closer to reality, ramping up sometime this year," he said.

For LLC applications, STT-MRAM has approached SRAM and DRAM performance levels for small sample sizes. At the VLSI symposium, researchers from Applied Materials, Qualcomm, Samsung, and TDK-Headway, all presented work on SRAM cache-type MRAM devices with high performance, tight pitches, and relatively low write currents. Applied's VLSI symposium presentation was by Lin Xue, who said the LLC-type MRAM performance is largely controlled by the quality of the PVD-deposited layers in the MTJ (**FIGURE 3**), while yields are governed by the ability to etch the MTJ pillars efficiently. Etching is extremely challenging for the tight pitches required for SRAM replacement, since the tight-pitch MTJ pillars must be etched without redepositing material on the sidewalls.

Deposition is also difficult. The MTJ structures contain multiple stacks of cobalt and platinum, and the thickness of the multilayers must be reduced to meet the 7nm node requirements. Any roughness in the interfaces creates secondary effects which reduce perpendicular magnetic anisotropy (PMA). "The performance is coming from the interface, essentially. If you don't make the interface sharp, you don't end up with the expected improvement in PMA," Pakala said.

Applied has optimized a PVD process for deposition of the 15-plus layers of many different materials required for the magnetic tunnel junctions. Pakala said the PVD technology can sputter more than 10 different materials. The Endura-based system uses a multi-cathode approach, enabling each chamber to have up to five targets. With a system of seven chambers, companies can deposit the required variety of materials and, if desired, increase throughput by doubling up on the targets.

The system would include a metrology capability, and because the materials are easily oxidized, the entire system operates at vacuum levels beyond the normal 10E-8 Torr level. For MRAM deposition, operating at 10 to minus 9 or even 10 to minus 10 Torr levels may be required.

"When we start talking about the 7 and 5 nanometer nodes for SRAM cache replacement, the cell size and distances between the bits becomes very small, less than 100 nm from one MTJ to another. When we get to such small distances, there are etching issues, mainly redepositing on the sidewalls. The challenge is: How do we etch at reduced pitch without shorting?" Pakala said.

"Integrated thermal treatment and metrology to measure the thicknesses, all of which has to be done at extremely low vacuum, are major requirements," he said. "At this point it is not a question of the basic physics. For MRAM, it is, as they say, 'just engineering' from here on out," he said. ◆

Layout schema generation: Improving yield ramp during technology development

WAEL ELMANHAWY and JOE KWAN, Mentor Graphics, Beaverton, OR

DESIGN

Layout schema generation generates random, realistic, DRC-clean layout patterns of the new design technology for use in test vehicles

redicting and improving yield in the early stages of technology development is one of the main reasons we create test macros on test masks. Identifying potential manufacturing failures during the early technology development phase lets design teams implement upstream corrective actions and/or process changes that reduce the time it takes to achieve the desired manufacturing yield in production. However, while conventional yield ramp techniques for a new technology node rely on using designs from previous technology nodes as a starting point to identify patterns for design of experiment (DoE) creation, what do you do in the case of a new design technology, such as multipatterning, that did not exist in previous nodes? The human designer's experience isn't applicable, since there isn't any knowledge about similar issues from previous designs. Neither is there any prior test data from which designers can draw feedback to create new test structures, or identify process or design style optimizations that can improve yield more quickly.

An innovative new technology, layout schema generation (LSG), enables design teams to generate additional macros to add to test structures without relying on past designs for input. These macros are based on the generation and random placement of unit patterns that can construct more meaningful larger patterns. Specifications governing the relationships between those unit patterns can be adjusted to generate layout clips that look like realistic designs. Those layout clips can then be used in design of experiment (DoE) trials to predict yield, and identify potential design and process optimizations that will help improve yield. By using this new LSG process, designers can significantly reduce the time it takes to achieve the desired yield for designs that include new design techniques.

### Issues affecting yield

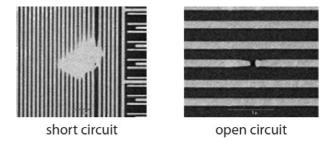

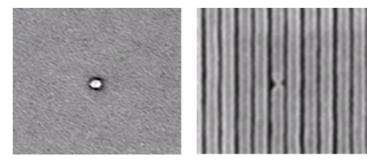

Wafer yield is typically reduced by three categories of defects. The first category comprises random defects, which occur due to the existence of contamination particles in the different process chambers. A conducting particle can short out two or more neighboring wires, or create a leakage path. A non-conducting particle or a void can open up a wire or a via, or create high resistive paths. **FIGURE 1** shows scanning electron microscope (SEM) images of these two types of random defects.

**FIGURE 1.** Random defects caused by contamination particles.

The second category contains systematic defects, which occur due to an imperfect physical layout architecture, or the impact of non-optimized optical process recipes and/ or equipment. Systematic defects are typically the biggest source of yield detraction [1], but a majority of them can be eliminated through design-technology co-optimization (DTCO), in which the design and process sides communicate more freely to achieve faster rates of improvement.

The third category, which we're not addressing in this article, includes parametric defects (such as a lack of uniformity in the doping process) that may affect the reliability of devices.

## Sensors MIDWEST OCTOBER 16-17

Donald E. Stephens Convention Center ROSEMONT, IL

1,600+ ATTENDEES LOOKING FOR SENSOR SOLUTIONS

65+ EXHIBITORS SHOWCASING LEADING TECHNOLOGIES

45+ KNOWLEDGEABLE SPEAKERS AND EXPERTS

30+ TECHNICAL SESSIONS COVERING THE LATEST INDUSTRY TRENDS

2 FULL DAYS OF ESSENTIAL EDUCATION

1 EVENT YOU CAN'T AFFORD TO MISS!

Register Now! www.sensorsmidwest.com

sensors

# THE EVENT FOR SENSORS DESIGN & INDUSTRIAL IOT

INDUSTRY SPONSOR

MEDIA

sensors

ONI INF

QUESTEX

## Layout schema generation

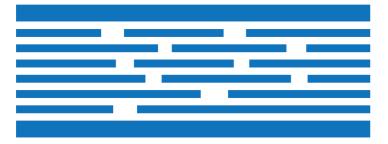

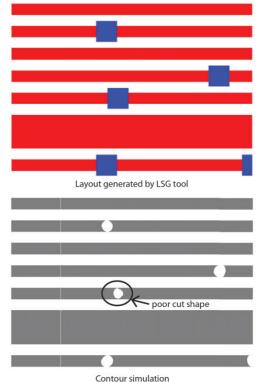

To demonstrate the use and applicability of the LSG process, let's look at designs that use the self-aligned multi-patterning (SAMP) process. Multi-patterning (MP) technology with ArF 193i lithography is currently the preferred choice over extreme ultraviolet (EUV) lithography for advanced technology nodes from 20 nm on down. At 7 nm and 5 nm nodes, the SAMP process appears to be one of the most effective MP techniques in terms of achieving a small pitch of printed lines on the wafer, but its yield is in question. Of course, before being deployed in production, it must be thoroughly tested on test vehicles. However, without any previous SAMP designs, design of an appropriate test vehicle is challenging. In addition to the lack of historical test data, the unidirectional nature of the SAMP design complicates the design of the conventional serpentine and comb test shapes, which contain bidirectional components.

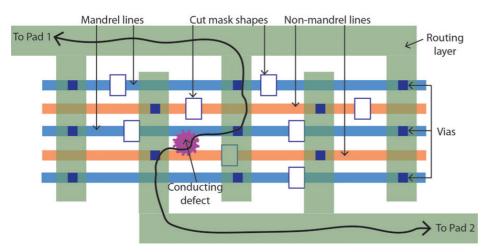

## Self-aligned multi-patterning process

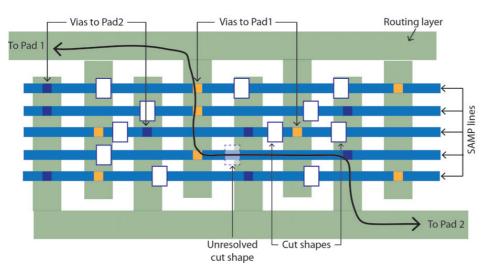

In the SAMP process [3], the first mask is known as the mandrel mask. Sacrificial mandrel shapes are printed with a relaxed pitch, and then used to develop sidewalls. The sidewalls are at half the mandrel's pitch. Depending on the tone, target shapes may exist in the spaces between the sidewalls. The target shapes can be reused as sacrificial mandrel shapes to form another generation of sidewalls. Wafer shapes that don't have corresponding mask shapes are called non-mandrel shapes. This process can be repeated to achieve SAMP layouts with a reduced pitch. The SAMP process (**FIGURE 2**) restricts the designs to be almost unidirectional. Generated parallel lines will be cut later by a cut mask at the desired line ends to form the correct connectivity.

## Sidewalls developed Sacrificial Mandrel Etched Sidewalls developed Sidewalls developed Sidewalls Etched K/4 Sidewalls Etched Sidewalls Etched

FIGURE 2. Basic schematic of SAMP process.

## **Test vehicles**

A test vehicle is typically a subset of the masks for a design, designed specifically to induce potential systematic failures or lithographic hotspots on the layer under test. It may also contain some test structures specially designed for the detection of random defects. The main components in a test vehicle for any new node are serpentine and comb shapes (to capture random defects), and preliminary standard cell designs (with many variations, to assess their quality). Other structures are typically added based on experience derived from production chips of previous nodes.

In a new node, all test structures on the test vehicle are vital for process training and characterization. Feedback from the test process is used for design style optimization. For example, when "bad" layout geometries are discovered after manufacturing, they can be captured as patterns, assigned low scores, and stored in a design for manufacturing (DFM) pattern library [2]. The designer can then use DFM analysis to find the worst patterns in a given layout, and modify or eliminate them. Such early DTCO provides a faster yield ramp for new nodes. Even in mature nodes, test structures are used on production wafers to identify additional opportunities for process refinement and optimization, which will have a positive impact on future yield.

One of the obstacles in test vehicle design is that it depends mainly on human designer's experience and memory. Although experienced designers have seen multiple design styles in older nodes, the design shapes they are familiar with are limited to those styles. It typically takes a long time to design new test structures that cover new shapes, especially for a new process. The

LSG solution adds more macros (generated in a random fashion) to the standard test structures strategy to speed up new shape yield analysis.

## Random test pattern generation

The key component of the LSG solution is a method for the random generation of realistic design-like layouts, without design rule violations. The LSG process uses a Monte Carlo method to apply randomness in the generation of layout clips by inserting basic unit patterns in a grid. These unit patterns represent simple rectangular and square

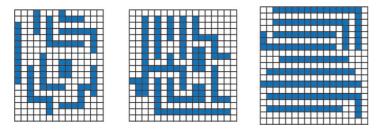

**FIGURE 3.** Realistic DRC-clean clips generated by a layout schema generation process.

polygons, as well as a unit pattern for inserting spaces in the design. Unit pattern sizes depend on the technology pitch value. During the generation of the layouts, known design rules are applied as constraints for unit pattern insertion. Once the rules are configured, an arbitrary size of layout clips can be generated (**FIGURE 3**).

To begin, the SAMP design rules are converted to a format readable by an automated LSG tool like the Calibre® LSG tool from Mentor, a Siemens Business. Once the rules are configured, the Calibre LSG process can automatically generate an arbitrarily wide area of realistic DRC-clean SAMP patterns. The area is only limited by the floorplan of the designated macro of SAMP test structures. Test patterns can be also generated with power rails to mimic the layouts of standard cells. **FIGURE 4** shows a sample clip of the generated output layout. To be ready for the experiments, the SAMP design is decomposed into the appropriate mandrel and cut masks, according to the decomposition rules. This operation also distinguishes between mandrel and non-mandrel shapes.

FIGURE 4. SAMP clip generated by automated LSG process.

## **Design of Experiment**

In the design phase of the test vehicle, the generated SAMP patterns are added to the typical contents of regular test patterns. The random SAMP patterns are electrically meaningless, unless they are connected to other layers to set up the required experiment. The DoE determines the way the connections are made from the patterns up to the testing pads, to detect different fail modes. Fail modes include short circuits due to lithographic bridging or conducting particles, and open circuits due to lithographic pinching, non-conducting particles, voids, or open vias.