plan Now May 2012 Las Vegas

## **Insights for Electronics Manufacturing**

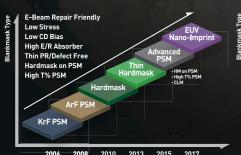

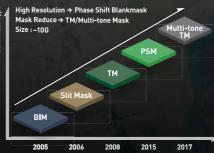

Big Changes in Mask Manufacturing

P. 18

Understanding ALD, MLD and SAMs

P. 22

Outlook for 2018 P. 25

# **3D X-ray Microscopy for FA of Micro-bumps** P12

www.solid-state.com

# The World's Best Blank Mask

# **Beyond Limits**

S&S Tech is a leading supplier in the Blank Mask market for both Semiconductor and Flat Panel Display business segments. Through dedicated services and high quality products, we have been recognized worldwide by major leading-edge customers in the semiconductor and display industry. With dedicated and highly qualified staff supported by extensive R&D investments, S&S Tech is striving forward to become the pioneer in future mask technology.

#### Semiconductor Blankmask

#### **Flat Panel Display Blankmask**

#### Headquarter

42, Hosandong-ro, Dalseo-gu, Daegu, Korea T +82 53 589 1600 F +82 53 585 7170

Taiwan Office

Rm. C, 18F.-6, No.27, Guanxin Rd., East Dist., Hsinchu City 30072, Taiwan

T+886 3 577 8518

F+886 3 577 8618

**US Office** 7873 Lakewood Drive, Austin Texas USA, 78750 T+1 512 496 6036

#### www.snstech.co.kr

# **Solid State TECHNOLOGY**

JANUARY/FEBRUARY 2018 VOL. 61 NO. 1

X-ray imaging is widely employed for nondestructive FA inspection because it can explore interior structures of chips and packages.

#### FEATURES

#### **INSPECTION** | High-res 3D X-ray microscopy for non-destructive failure analysis of chip-to-chip microbump interconnects in stacked die packages

Chip-to-chip interconnects require new defect localization techniques and failure analysis flows Syahirah Md Zulkifli, Bernice Zee and Wen Qiu, Advanced Micro Devices, Singapore; and Allen Gu, ZEISS Semiconductor Manufacturing Technology Process Control Solutions, Pleasanton, CA

**LITHOGRAPHY** | 2018: Big changes in mask manufacturing and what it means for mask models Changes are driving the need for more detailed and more accurate modeling for mask manufacturing. *Ryan Pearman, D2S, Inc., San Jose, CA*

#### **DEPOSITION** Understanding ALD, MLD and SAMs as they enter the fab

As the world of advanced manufacturing enters the sub-nanometer scale era, it is clear that ALD, MLD and SAM represent viable options for delivering the required few-atoms-thick layers required with uniformity, conformality, and purity. *Barry Arkles, Jonathan Goff, Gelest Inc., Morrisville PA, and Alain E. Kaloyeros, SUNY Polytechnic Institute, Albany, NY*

#### BUSINESS Executive viewpoints: 2018 outlook

Each year, Solid State Technology turns to industry leaders to hear viewpoints on the technological and economic outlook for the upcoming year. Read through these expert opinions on what to expect in 2018.

#### COLUMNS

- 2 Editorial Join us at The ConFab 2018, Pete Singer, Editor-in-Chief

- **10 Packaging** Advances in packaging polymers *Phil Garrou, Contributing Editor*

- **11 Semiconductors** Logic densities advance at IEDM 2017, *Pete Singer, Editor-in-Chief*

- **31 Industry Forum** Work to do to keep the good times rolling, *Ajit Manocha, President and CEO of SEMI*

#### DEPARTMENTS

- **3** Web Exclusives

- 4 News

- 30 Ad Index

COVER

## editorial

# Join Us at The ConFab 2018

The ConFab 2018, to be held May 20-23 at The Cosmopolitan of Las Vegas, is a conference and networking event designed to inform and connect leading semiconductor executives from all parts of the supply chain. Now in its 14th year, it is produced by Solid State Technology magazine, the semiconductor industry's oldest and most respected business publication.

The goal of The ConFab this year is to show how today's semiconductor manufacturers and their suppliers can they best position themselves to take advantage of the tremendous growth the industry is expecting to see in the near future, propelled by a wide array of new applications, including artificial intelligence, virtual and augmented reality, automotive, 5G, the IoT, cloud computing and healthcare.

Here's a quick look at the agenda as it stands now.

After a welcome reception on Sunday evening, we'll kick things off on Monday with a talk by IBM's Rama Divakaruni on "How A.I. is Driving the New Semiconductor Era." Although A.I. (and associated deep learning and machine learning) is now in its infancy, it will likely to have a major impact on how semiconductors will be designed and manufactured in the future. A.I. will demand dramatic enhancement in computational performance and efficiency, which in turn will drive fundamental changes in algorithms, systems and chip design. Devices and materials will also change.

Following Rama's talk, we'll hear from John M. Martinis, Google who heads up Google's Quantum A.I. Lab. The lab is particularly interested in applying quantum computing to artificial intelligence and machine learning.

After the keynote talks, we'll hear from a number of industry visionaries, including John Hu, Director of Advanced Technology for Nvidia, Dan Armbrust, Founder and Director of

Silicon Catalyst, and Tom Sonderman, President of Sky Water Technology Foundry. On Monday afternoon, invited industry experts, such as Bill Von Novak of Qualcomm will drill down into the applications most critical to semiconductor industry growth, including automotive, networking, healthcare and the IoT.

On Tuesday, the talks will focus on manufacturing trends and challenges with mainstream semiconductor manufacturing the focus of the morning session and advanced packaging the focus in the afternoon. George Gomba, VP of technology research at GlobalFoundries, will provide an update on EUV lithography, followed by Koukou Suu, of Ulvac, a leading expert on materials for phase change memories. Howard Witham, Vice President of Texas Operations, Qorvo, will provide some insights in using artificial intelligence and automation in semiconductor manufacturing.

The advanced packaging session on Tuesday afternoon is organized and sponsored by IEEE CPMT, notably Li Li, Distinguished Engineer, Cisco and William Chen, Fellow, ASE. The semiconductor industry is increased relying on advanced packaging to deliver far more integrated, complex and advanced solutions for different market segments.

On Wednesday, we'll hear from leading analysts, including Len Jenelik, Senior Director, Semiconductor Manufacturing at IHS Markit, and Jim Feldhan, President of Semico, on market trends and the expected business climate moving forward.

You can register and keep up-to-date by visiting www.theconfab. com. For sponsorship inquiries, contact Kerry Hoffman at khoffman@extensionmedia.com. For those interested in attending as a guest or qualifying as a VIP, contact Sally Bixby at sbixby@extensionmedia.com.

-Pete Singer, Editor-in-Chief

## Solid State TECHNOLOGY.

Pete Singer, Editor-in-Chief Ph: 978.470.1806, psinger@extensionmedia.com

Shanon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor, edk@extensionmedia.com

Dave Lammers, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor Vivek Bakshi, Contributing Editor CREATIVE/PRODUCTION/ONLINE Marjorie Sharp, Production Traffic Coordinator

Nicky Jacobson, Senior Graphic Designer

Simone Bradley, Graphic Designer Slava Dotsenko, Senior Web Developer

MARKETING/CIRCULATION Jenna Johnson, jjohnson@extensionmedia.com

#### **CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

JANUARY/FEBRUARY 2018 VOL. 61 NO. 1 • Solid State Technology ©2018 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmaii: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: *Solid State Technology, 1786* 18th Street, San Francisco, CA 94107-2343, (8 am – 5 pm, PST). Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2018 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

# Online@www.solid-state.com

#### **Web Exclusives**

#### Talent pipeline key to enabling industry growth: Takeaways from SEMI Member Forum

Electronic manufacturing is becoming cool to today's youth. STEM skills are hot in the global job market – though the number of females pursuing a STEM education continues to lag. Work-based learning is key to mastering new technologies. And the electronics industry needs a global talent pipeline more than ever.

#### http://bit.ly/2mMSPgL

# New speakers for The ConFab 2018

The ConFab staff is presently lining up speakers and VIPs for our 2018 Agenda/Program and networking event, which will be held May 20-23 at The Cosmopolitan of Las Vegas. Many different topics have been considered for the talks and keynote addresses, as there are many new drivers and technologies for the semiconductor industry to be considered.

http://bit.ly/2Do9jpd

#### Revision to SEMI E142: Specification for substrate mapping

As dynamic back-end related technologies such as TSV (Through-Silicon Vias), InFO (Integrated Fan Out), etc., enable electronic devices to downsize with higher performance, the importance of back-end processing is greater than ever. Due to this, more and more customers are requesting "quality control" by tracing raw materials to assembly and packaging companies and the need for a standard is clear.

http://bit.ly/2FJLxCg

#### Insights from the Leading Edge: Broadcom continues consolidation

On November 6, Broadcom announced its intention to buy its rival, Qualcomm, for ~ \$130B, including debt. If successful, it would be the largest deal in the history of the technology acquisitions.

http://bit.ly/2DiYyVh

## IEDM 2017: Intel's 10nm platform process

IEDM this year was its usual mixture of academic exotica and industrial pragmatica (to use a very broad-brush description), but the committee chose to keep us all waiting until the Wednesday morning before we got to the CMOS platform papers. Of course, the talk we were all anticipating was Intel's Chris Auth on "A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects".

http://bit.ly/2DDtVHG

#### Insights from the Leading Edge: IWPLC Part 3

Tanja Braun of IZM Fraunhoffer discussed "Fanout and Panel level technology for Advanced LED Packaging."

http://bit.ly/2mLnQ50

## **Surprising changes to semiconductor equipment market share in 2017**

Through three quarters of calendar year 2017, market shares of top semiconductor equipment manufacturers indicate large gains by Tokyo Electron and Lam Research, according to the report "Global Semiconductor Equipment: Markets, Market Shares, Market Forecasts," recently published by The Information Network, a New Tripoli-based market research company.

http://bit.ly/2re3vKa

#### Luc Van den hove to receives SEMI Sales and Marketing Excellence Award

SEMI today announced that Luc Van den hove, president and CEO of imec, has been selected as the 2018 recipient of the SEMI Sales and Marketing Excellence Award, inspired by Bob Graham. He was honored for outstanding achievement in semiconductor equipment and materials marketing during ceremonies at ISS 2018 on January 17 in Half Moon Bay, California.

http://bit.ly/2mEjvzD

Please send news articles to sdavis@extensionmedia.com

#### worldnews

**EUROPE: Picosun Oy** announced a partnership with **STMicroelectronics S.r.I.** to develop the next generation

300mm production solutions for advanced power electronics. USA: Boston Semi Equipment announced that it has received

announced that it has received a multisystem order for its Zeus gravity feed systems for handling pressure MEMS devices.

**ASIA: UMC** filed a patent infringement lawsuit against **Micron**.

USA: ON Semiconductor and ConvenientPower Systems announced a strategic collaboration in automotive wireless charging.

**EUROPE:** The **SEMI European 3D Summit** will make its Dresden, Germany, debut 22-24 January, 2018, featuring a broader scope of 3D topics driving innovation and business opportunities in the 3D market.

USA: Arrow Electronics, Inc. announced the successful completion of its acquisition of elnfochips, one of the world's largest design and managed services companies.

**EUROPE: STMicroelectronics** and **USound** deliver first advanced MEMS silicon micro-speakers.

USA: Micron and Intel announced an update to their successful NAND joint development partnership that has helped the companies develop and deliver industry-leading NAND technologies to market.

ASIA: UMC announced availability of 40nm SST embedded flash process.

**USA: Nordson Corporation** acquired **Sonoscan**.

ASIA: Samsung Electronics announced that it has begun mass producing the industry's first 2nd-generation of 10-nanometer class (1y-nm), 8-gigabit (Gb) DDR4 DRAM.

USA: Intersil to start operations as Renesas Electronics America in January 2018.

# **hender and the second second**

# Worldwide semiconductor revenue grew 22.2% in 2017; Samsung takes over No. 1 position

Worldwide semiconductor revenue totalled \$419.7 billion in 2017, a 22.2 percent increase from 2016, according to preliminary results by Gartner, Inc. Undersupply helped drive 64 percent revenue growth in the memory market, which accounted for 31 percent of total semiconductor revenue in 2017.

"The largest memory supplier, Samsung Electronics, gained the most market share and took the No. 1 position from Intel — the first time Intel has been toppled since 1992," said Andrew Norwood, research vice president at Gartner. "Memory accounted for more than two-thirds of all semiconductor revenue growth in 2017, and became the largest semiconductor category."

The key driver behind the booming memory revenue was higher prices due to a supply shortage. NAND flash prices increased year over year for the first time ever, up 17 percent, while DRAM prices rose 44 percent.

Equipment companies could not absorb these price increases so passed them onto consumers, making everything from PCs to smartphones more expensive in 2017.

Other major memory vendors, including SK Hynix and Micron Technology, also performed strongly in 2017 and rose in the rankings (**see Table 1**).

| Second-placed Intel grew its revenue 6.7      |

|-----------------------------------------------|

| percent in 2017, driven by 6 percent growth   |

| in data center processor revenue due to       |

| demand from cloud and communications          |

| service providers. Intel's PC processor       |

| revenue grew more slowly at 1.9 percent,      |

| but average PC prices are on the rise again   |

| after years of decline following the market's |

| shift from traditional desktops toward        |

| two-in-one and ultramobile devices.           |

|                                               |

The current rankings may not last long, however, "Samsung's lead is literally built on sand, in the form of memory silicon," said Mr. Norwood. "Memory pricing will weaken in 2018, initially for NAND flash and then DRAM in 2019 as China increases its memory production capacity. We then expect Samsung to lose a lot of the revenue gains it has made."

2017 was a relatively quiet year for mergers and acquisitions. Qualcomm's acquisition of NXP was one big deal that was expected to close in 2017, but did not. Qualcomm still plans to complete the deal in 2018, but this has now been complicated by Broadcom's attempted takeover of Qualcomm.

"The combined revenues of Broadcom, Qualcomm and NXP were \$41.2 billion in 2017 — a total beaten only by Samsung and Intel," said Mr. Norwood. "If Broadcom can finalize this double acquisition and Samsung's

| 2017<br>Bank | 2016<br>Rank | Vendor              | 2017<br>Revenue | 2017 Market<br>Share (%) | 2016<br>Revenue | 2016-2017<br>Growth (%) |

|--------------|--------------|---------------------|-----------------|--------------------------|-----------------|-------------------------|

| 1            | 2            | Samsung Electronics | 61,215          | 14.6                     | 40,104          | 52.6                    |

| 2            | 1            | Intel               | 57,712          | 13.8                     | 54,091          | 6.7                     |

| 3            | 4            | SK Hynix            | 26,309          | 6.3                      | 14,700          | 79.0                    |

| 4            | 6            | Micron Technology   | 23,062          | 5.5                      | 12,950          | 78.1                    |

| 5            | 3            | Qualcomm            | 17,063          | 4.1                      | 15,415          | 10.7                    |

| 6            | 5            | Broadcom            | 15,490          | 3.7                      | 13,223          | 17.1                    |

| 7            | 7            | Texas Instruments   | 13,806          | 3.3                      | 11,901          | 16.0                    |

| 8            | 8            | Toshiba             | 12,813          | 3.1                      | 9,918           | 29.2                    |

| 9            | 17           | Western Digital     | 9,181           | 2.2                      | 4,170           | 120.2                   |

| 10           | 9            | NXP                 | 8,651           | 2.1                      | 9,306           | -7.0                    |

|              |              | Others              | 174,418         | 41.6                     | 157,736         | 10.6                    |

|              |              | Total Market        | 419,720         | 100.0                    | 343,514         | 22.2                    |

TABLE 1. Source: Gartner (January 2018)

memory revenue falls as forecast, then Samsung could slip to third place during the next memory downturn in 2019."  $\diamondsuit$

MARCH 14–16, 2018 SNIEC, SHANGHAI, CHINA

# 跨界全球 · 心芯相联 CONNECT · COLLABORATE · INNOVATE

For the past 30 years, SEMICON China has witnessed the robust growth of China's semiconductor industry and is the premier place to connect with the companies, people, products, and information shaping the future of design and manufacturing of microelectronics—all at SEMICON China and FPD China 2018!

- The entire semiconductor industry ecosystem, including device manufacturing, equipment, materials, assembly and test services, design, and more.

- The premier platform for exploring and discussing cutting-edge technologies with engineers, executives, and experts from around the world.

- Connect and engage suppliers, partners, and customers.

- Expand your business opportunities with industry leaders.

Contact SEMI China

Tel: +86.21.6027.8500 E

E-mail: semichina@semi.org

www.semiconchina.org

# **NEWS**cont

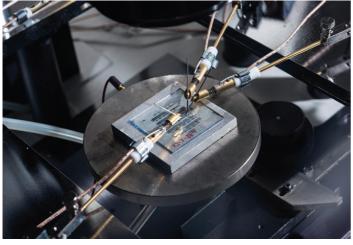

#### Nanostructured gate dielectric boosts stability of organic thin-film transistors

A nanostructured gate dielectric may have addressed the most significant obstacle to expanding the use of organic semiconductors for thin-film transistors. The structure, composed of a fluoropolymer layer followed by a nanolaminate made from two metal oxide materials, serves as gate dielectric and simultaneously protects the organic semiconductor – which had previously been vulnerable to damage from the ambient environment – and enables the transistors to operate with unprecedented stability.

**FIGURE 1.** Image shows organic-thin film transistors with a nanostructured gate dielectric under continuous testing on a probe station. (Credit: Rob Felt, Georgia Tech)

The new structure gives thin-film transistors stability comparable to those made with inorganic materials, allowing them to operate in ambient conditions – even underwater. Organic thin-film transistors can be made inexpensively at low temperature on a variety of flexible substrates using techniques such as inkjet printing, potentially opening new applications that take advantage of simple, additive fabrication processes.

"We have now proven a geometry that yields lifetime performance that for the first time establish that organic circuits can be as stable as devices produced with conventional inorganic technologies," said Bernard Kippelen, the Joseph M. Pettit professor in Georgia Tech's School of Electrical and Computer Engineering (ECE) and director of Georgia Tech's Center for Organic Photonics and Electronics (COPE). "This could be the tipping point for organic thin-film transistors, addressing long-standing concerns about the stability of organic-based printable devices."

The research was reported January 12 in the journal Science Advances. The research is the culmination of 15 years of development within COPE and was supported by sponsors including the Office of Naval Research, the Air Force Office of Scientific Research, and the National Nuclear Security Administration.

Transistors comprise three electrodes. The source and drain electrodes pass current to create the "on" state, but only when a voltage is applied to the gate electrode, which is separated from the organic semiconductor material by a thin dielectric layer. A unique aspect of the architecture developed at Georgia Tech is that this dielectric layer uses two components, a fluoropolymer and a metal-oxide layer.

"When we first developed this architecture, this metal oxide layer was aluminum oxide, which is susceptible to damage from humidity," said Canek Fuentes-Hernandez, a senior research scientist and coauthor of the paper. "Working in collaboration with Georgia Tech Professor Samuel Graham, we developed complex nanolaminate barriers which could be produced at temperatures below 110 degrees Celsius and that when used as gate dielectric, enabled transistors to sustain being immersed in water near its boiling point."

The new Georgia Tech architecture uses alternating layers of aluminum oxide and hafnium oxide – five layers of one, then five layers of the other, repeated 30 times atop the fluoropolymer – to make the dielectric. The oxide layers are produced with atomic layer deposition (ALD). The nanolaminate, which ends up being about 50 nanometers thick, is virtually immune to the effects of humidity.

"While we knew this architecture yielded good barrier properties, we were blown away by how stably transistors operated with the new architecture," said Fuentes-Hernandez. "The performance of these transistors remained virtually unchanged even when we operated them for hundreds of hours and at elevated temperatures of 75 degrees Celsius. This was by far the most stable organic-based transistor we had ever fabricated."

For the laboratory demonstration, the researchers used a glass substrate, but many other flexible materials – including polymers and even paper – could also be used.

In the lab, the researchers used standard ALD growth techniques to produce the nanolaminate. But newer processes referred to as spatial ALD – utilizing multiple heads with nozzles delivering the precursors – could accelerate production and allow the devices to be scaled up in size. "ALD has now reached a level of maturity at which it has become a scalable industrial process, and we think this will allow a new phase in the development of organic thin-film transistors," Kippelen said. An obvious application is for the transistors that control pixels in organic light-emitting displays (OLEDs) used in such devices as the iPhone X and Samsung phones. These pixels are now controlled by transistors fabricated with conventional inorganic semiconductors, but with the additional stability provided by the new nanolaminate, they could perhaps be made with printable organic thin-film transistors instead.

Internet of things (IoT) devices could also benefit from fabrication enabled by the new technology, allowing production with inkjet printers and other low-cost printing and coating processes. The nanolaminate technique could also allow development of inexpensive paper-based devices, such as smart tickets, that would use antennas, displays and memory fabricated on paper through low-cost processes.

But the most dramatic applications could be in very large flexible displays that could be rolled up when not in use.

"We will get better image quality, larger size and better resolution," Kippelen said. "As these screens become larger, the rigid form factor of conventional displays will be a limitation. Low processing temperature carbon-based technology will allow the screen to be rolled up, making it easy to carry around and less susceptible to damage. For their demonstration, Kippelen's team – which also includes Xiaojia Jia, Cheng-Yin Wang and Youngrak Park – used a model organic semiconductor. The material has well-known properties, but with carrier mobility values of 1.6 cm2/Vs isn't the fastest available. As a next step, they researchers would like to test their process on newer organic semiconductors that provide higher charge mobility. They also plan to continue testing the nanolaminate under different bending conditions, across longer time periods, and in other device platforms such as photodetectors.

Though the carbon-based electronics are expanding their device capabilities, traditional materials like silicon have nothing to fear.

"When it comes to high speeds, crystalline materials like silicon or gallium nitride will certainly have a bright and very long future," said Kippelen. "But for many future printed applications, a combination of the latest organic semiconductor with higher charge mobility and the nanostructured gate dielectric will provide a very powerful device technology."

# ing of Fan-Out Wafer Level Packaging

888-YES-3637

www.yieldengineering.com

## Vacuum Polymer Cure Oven

#### Automated. Flexible. Comprehensive.

- Shorter process time

- No trapped solvent/oxygen

- No outgassing at metallization

Cleaner Process. Cleaner Maintenance.

Yield Engineering Systems, Inc.

# **news**cont.

#### Industry enters the age of WOW

By Christian G. Dieseldorff, Industry Research & Statistics Group, SEMI, Milpitas, California

The semiconductor industry has been there before, with large increases in investments followed by dramatic downturns. While the most dramatic downturns, 2001 and 2009, were due to, in a large part, acro-economic factors, the industry has typically observed one to two years of increased investment spending followed by a down period. This time around, the industry will achieve a "WOW" with three consecutive years of fab investment growth, a pattern not observed since the mid-1990s.

Why are things different this time? A diverse array of technology drivers promise more robust long-term growth, such as Mobile applications, Internet of Things (IoT), Automotive & Robotics, Industrial, Augmented Reality & Virtual Reality (AR&VR), Artificial Intelligence (AI), and 5G networking. Each of these new technologies inspires a big "WOW" as the industry embarks on the beginning of a promising journey of growth.

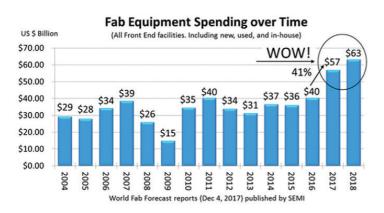

Driven by these technologies, on average the semiconductor revenue CAGR from 2016 to 2021 is forecasted to be 6 percent (in comparison to the previous 2011-2016 CAGR of 2.3 percent). For the first time in the industry's history, semiconductor revenues will exceed the US\$400 billion revenue milestone in 2017. Demand for chips is high, pricing is strong for memory, and the competition is fierce. All of this is spurring increased fab investments, with many companies investing at previously unseen levels for new fab construction and fab equipment. See **Figure 1**.

The World Fab Forecast report, published on December 4, 2017, by SEMI, is modeling that fab equipment spending in 2017 will total US\$57 billion or 41 percent year-over-year (YoY) growth. In 2018, spending is expected to shoot up another 11 percent at US\$63 billion. The two spending jumps in 2017 and 2018 are contributing to the "WOW" factor and to two consecutive years of record fab investments. Following historic large investments, some slowdown is expected for 2019.

FIGURE 1.

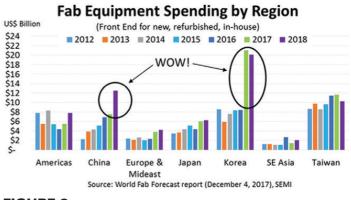

Many companies, such as Intel, Micron, Toshiba (and Western Digital), and GLOBALFOUNDRIES, have increased fab investments in 2017 and 2018; however, the strong increases we see in both years are not caused by these companies but by one company and primarily one region. See **Figure 2**.

FIGURE 2.

The first jump – a Big WOW – in 2017 is the surge of investments in Korea, due mainly to Samsung. Samsung is expected to increase its fab equipment spending by 128 percent in 2017 from US\$8 billion to US\$18 billion. No single company has invested so much in a single year in its fabs and much of its spending is in Korea. SK Hynix also increased fab equipment spending, by about 70 percent, to US\$5.5 billion, its largest spending level in its history. While the bulk of Samsung's and SK Hynix's spending remains in Korea, some will also go to China, and in the case of Samsung to the United States. Both Samsung and SK Hynix are expected to maintain high levels of investments for 2018.

The second jump – another WOW – is investment growth for 2018 in China. China is expected to begin equipping the many fabs that were constructed in 2017. In the past, non-Chinese companies made the majority of the fab investments in China but for the first time in 2018, Chinese-owned companies will approach parity, spending nearly as much on fab equipment as non-Chinese device manufacturers.

Between 2013 and 2017, fab equipment spending in China by Chinese-owned companies typically ranged between US\$1.5 billion to US\$2.5 Billion per year, while non-Chinese companies invested between US\$2.5 billion to US\$5 billion per year. In 2018, Chinese-owned companies are expected to invest about US\$5.8 billion, while non-Chinese will invest US\$6.7 billion. Many new companies such as Yangtze Memory Technology, Fujian Jin Hua, Hua Li, and Hefei Chang Xin Memory are investing heavily in the region.

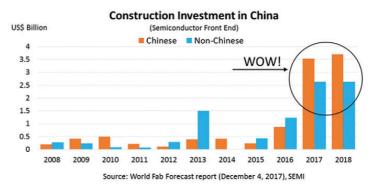

#### New fabs being built

Historic highs in equipment spending in 2017 and 2018 reflect growing demand. This spending follows unprecedented growth in construction spending for new fabs also detailed in SEMI's World Fab Forecast report. Construction spending will reach all-time highs with China construction spending taking the lead: US\$6 billion in 2017 and US\$6.6 billion in 2018, shattering another record – no region has ever spent more than US\$6 billion in a single year for construction. More new fabs mean another wave of spending on equipping fabs in the next few years. See **Figure 3**.

Considering all of these "WOW" factors, there is good reason to feel positive about the semiconductor industry. Even with a slowdown, the industry has and will continue to enjoy a positive outlook for long-term growth. In the meantime, hold on tight and enjoy the "WOW."

#### FIGURE 3.

More details are available in SEMI's just-published World Fab Forecast, December 4, 2017, edition which covers quarterly data (spending, capacity, technology nodes, wafer sizes, and product types) per fab until end of 2018.

# Advances in packaging polymers

Presentations that described new polymer dielectric advancements were a highlight of last year's IWLPC (International Wafer Level Packaging Conference), held in October in San Jose.

Matsukawa of HD Micro described their "Low temp curable PI/PBO for Wafer Level Packaging."

For next generation advanced packaging technologies, the most important requirements for dielectric materials are low temperature curability, high lithographic performance, high chemical resistance, and low warpage. He reported on new low temperature (<200°C) curable PI and PBO.

Conventional photosensitive PIs and PBOs have required curing temperatures greater than 300°C to complete cyclization as well as advance polymerization. To formulate low temperature curable materials, they re-designed the polymer backbone in order to enhance cyclization and changed the cross-linker to form a strong network structure even when cured <200°C.

Generally positive tone photo-definable materials are composed of a PBO precursor, a photo acid generator, crosslinker etc. Regarding the new positive tone PBO, a suitable photo acid generator and cross-linker combination was selected to increase the resolution while also improving the adhesion to Cu, which has been a significant problem for past generation products.

Araki of Toray discussed their "Novel Low Temp curable positive tone photo dielectric material with high elongation for panel processing".

Dielectric materials for redistribution layers (RDL) are one of the most important materials for fan out panel level processing (FOPLP). Toray introduces a low-temperature curable positive-tone photosensitive dielectric material with the high elongation property for fabricating RDL on FOPLP. The high elongation property was achieved by the introduction of flexible molecular skeleton in the base polymer backbone to increase the entanglement of each polymer chain. Cured films showed elongation up to 80%. This positive-tone photosensitive material offers fine pattern (3  $\mu$ m trench and 5  $\mu$ m line and space) with good sensitivity (300 mJ/cm<sup>2</sup> (i-line)) and shows high chemical resistance toward resist strippers.

# Packaging

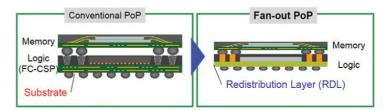

Fukuhara of Hitachi Chemical described their "Photo-sensitive Insulation Film for Encapsulation and Embedding." Conventional PoP with flip chips mounted on BGA like substrates is shown in Figure 1 compared to a fan out PoP.

In order to make a high density connection between upper and

PHIL GARROU, Contributing Editor

lower packages, it is necessary to form fine pitch through holes on the bottom package. These through hole vias can be formed by laser drilling. HC has developed a laminate photo film which allows encapsulation of the die and subsequent photo formation of the required vias through the film.

Onozeki of Hitachi Chemical discussed "Wafer Level Packaging Materials and Processes" where he examined the influences of the material properties of temp bond adhesives (TBA) and epoxy mold cmpds (EMC) on the warpage of FO-WLP during the fabrication process by both of the experiments and finite element analysis.

For TBA, it was found that "the deformation of TBA results in relatively free shrinkage of EMC on the support, and Young's modulus of TBA influences on the warpage most significantly. The small Young's modulus TBA suppressed the warpage regardless of the support materials". As for the EMC, "...the low Young's modulus, low CTE and low Tg are effective to reduce the warpage after post mold curing. The warpage after grinding EMC was smaller than those after post mold cure and there was no big difference in the influence of the mechanical properties." As for FO-WLP structure, the wide die pitch, thin EMC and thick die are effective to reduce warpage. Especially, the wide die pitch contributes to reduce the warpage. 4 layers re-distribution layer with line and space of 2 and 2 µm was successfully fabricated. The layers were interconnected with small diameter filled Cu vias of 5 µm. The vias were formed in the photosensitive dielectric material. A bias HAST test revealed that this material had enough insulation reliability.

Okamoto from JSR discussed "Fine Pitch Plating Resist for High Density FOWLP." For the next generation of high density FO-WLP, RDLs as low as 2  $\mu$ m are reportedly required to support more I/O's and multiple RDL layers.

# Logic densities advance at IEDM 2017

The 63rd International Electron Devices Meeting brought an optimistic slant to transistor density scaling. While some critics have declared the death of Moore's Law, there was little evidence of that -- on the density front at least -- at the IEDM.

And an Intel engineering manager gave a presentation at IEDM that took a somewhat optimistic view of EUV lithography readiness, auguring further patterning improvements, starting with contacts and vias.

GlobalFoundries, which is skipping the 10nm node, presented its 7nm logic technology, expected to move into manufacturing in mid-2018. John Pellerin, vice president of global R&D, said the foundry has worked closely with its two lead customers, AMD and IBM, to define a high-performance-computing 7nm logic technology that achieves a 2.8X improvement of routed logic density compared with its 14nm technology.

Pellerin said the current 7nm process of record (POR) delivers "the right mix of performance, power, and area (PPA)," adding that GlobalFoundries plans to bring in EUV patterning at an undefined later point in the 7+ generation for further improvements.

Chris Auth, director of advanced transistor development at Intel Corp., described a 10nm logic technology that sharply increased the transistor density compared with the 14nm generation, partly due to a contact-over-active-gate (COAG) architecture. The 10nm ring oscillator performance was improved by 20 percent compared with the comparable 14nm test vehicle.

Auth said the COAG approach was a key contributor to Intel's ability to increase its transistor density by 2.7 times over the company's previous generation, to 100 million transistors per square millimeter of silicon. While the traditional approach puts the contact via over the isolation area, COAG places the contact via directly over the gate. Auth said while the approach does require a second etch stop layer and other process complexities, it contributes "a sizable 10 percent reduction in area." Elimination of the dummy gate for cell boundary isolation, and the use of cobalt at three layers also contributed.

While there has been much hand wringing in the industry over the costs involved with multi-level patterning, Auth didn't

### Semiconductors

appear phased by it. Intel used a self-aligned quad patterning (SAQP) scheme

to create fins with a tight pitch. The SAQP approach required two sacrificial layers, with lithography defining

DAVE LAMMERS Contributing Editor

the first large pattern and four additional steps to remove the spacers and create the final lines and spaces. The Intel 10 nm fins are 46nm in height.

The SAQP approach starts by exposing a 130nm line, depositing the two spacers, halving the pattern to 68nm, and again to 34nm. "It is a grating and cut process similar to what we showed at 22nm, except it is SAQP instead of SADP," using patterning to form a grating of fins, and cutting the ends of the fins with a cut mask.

"There were no additional lithography steps required. The result was fins that are tighter, straighter, and taller, with better drive current and matching" than Intel's 14nm-generation fins. Intel continued to use self-aligned double patterning (SADP) for M 2-5, and for gate patterning.

GlobalFoundries -- which has been in production for 18 months with the 14nm process used by AMD, IBM, and others -- plans to ramp its 7nm logic generation starting in mid-2018. The 7nm high-density SRAM cell measures .0269  $\mu$ m2, slightly smaller than TSMC's published 7nm cell, while Intel reported a .0312  $\mu$ m2 cell size for its 10nm process.

GlobalFoundries chief technology officer Gary Patton said "all of us are in the same zip code" when it comes to SRAM density. What is increasingly important is how the standard cells are designed to minimize the track height and thereby deliver the best logic cell technology to designers, Patton said.

Britt Turkot, senior principal engineer at Intel, discussed the readiness of EUV lithography at an IEDM session, giving a cautiously bullish report. With any multi-patterning solution for leading-edge silicon, including etch and CMP steps, placement error is the biggest challenge. With quad patterning, Turkot said multiple masks are involved, creating "compounded alignment errors."

EUV has its own challenges, including significant secondary ions from the EUV photons. The key challenge for much of the decade, source power, seems to be partially resolved. "We are confident that the 250 Watts of source power needed for volume manufacturing will be ready once the field tools are upgraded," she said.  $\triangleleft$

**INSPECTION**

# High-res 3D X-ray microscopy for non-destructive failure analysis of chip-to-chip micro-bump interconnects in stacked die packages

SYAHIRAH MD ZULKIFLI, BERNICE ZEE AND WEN QIU, Advanced Micro Devices, Singapore;

ALLEN GU, ZEISS, Pleasanton, CA

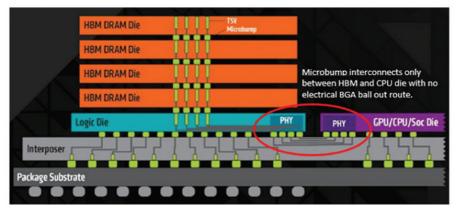

D integration and packaging has challenged failure analysis (FA) techniques and workflows due to the high complexity of multichip architectures, the large variety of materials, and small form factors in highly miniaturized devices [1]. The drive toward die stacking with High Bandwidth Memory (HBM) allows the ability to move higher bandwidth closer to the CPU and offers an opportunity to significantly expand memory capacity and maximize local DRAM storage for high throughput in the data center. However, the integration of HBM results in more complex electrical communications, due to the emerging use of a physical layer (PHY) design to connect the chip and subsystems. FIGURE **1** shows the schematic of a 2.5D stacked die package designed so that some HBM µbumps are electrically connected to the main CPU through a PHY connection. In general, the HBM and CPU signal length needs to be minimized to reduce drive strength requirements

**FIGURE 1.** Schematic of HBM  $\mu$ bump interconnect between the HBM and CPU die.

and power consumption at the PHY.

This requirement poses new challenges in FA fault isolation. A traditional FA workflow using electrical fault isolation (EFI) techniques to isolate the defect becomes less effective for chip-to-chip interconnects because there are no BGA balls for electrically probing the  $\mu$ bumps at the PHY. As a result, new defect localization techniques and FA flows must be investigated.

#### **XRM theory**

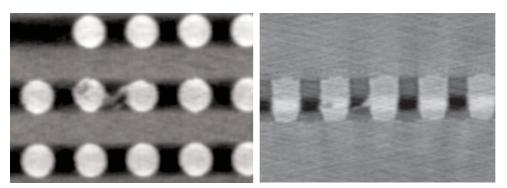

X-ray imaging is widely employed for non-destructive FA inspection because it can explore interior structures of chips and packages, such as solder balls, silver paste and lead frames. Thus, many morphological failures, such as solder-ball crack/burn-out and bumping failure inside IC packages, can be imaged and analyzed through X-ray tools. In 2D X-ray inspection,

> an X-ray irradiates samples and a 2D detector utilizes the projection shadow to construct 2D images. This technique, however, is not adequate for revealing true 3D structures since it projects 3D structures onto a 2D plane. As a result, important information, such as internal faulty regions of electronic packages, may remain hidden. This disadvantage can be overcome by using 3D X-ray microscopic technology, derived from the original computed tomography (CT) technique. In a 3D imaging system, a series of 2D X-ray images are captured at different angles while a sample rotates.

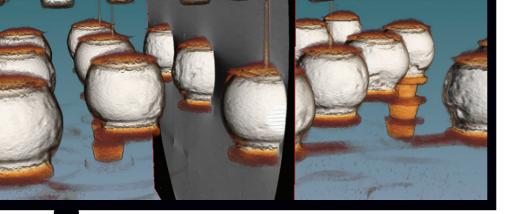

These 2D images are used to reconstruct 3D X-ray tomographic slices using mathematic models and algorithms. The spatial resolution of the imaging technique can be improved through the integration of an optical microscopy system. This improved technology is called 3D X-ray microscopy (XRM) [2]. **FIGURE 2** shows an example 3D XRM image for a stacked die. The image clearly shows the internal structures - including the TSV, C4 bumps and µbump of the electronic components - without physically damaging or altering the sample. The high resolution and quality shown here are essential to inspect small structural defects inside electronic devices. With its non-destructive nature, 3D XRM has been useful for non-destructive FA for IC packaging devices.

#### Failure analysis approach

The purpose of an FA workflow is to have a sequence of analytical techniques that can help to effectively and quickly isolate the failure and determine the root cause. Typical FA workflows for flip-chip devices encounters a defect, inhomogeneity or a boundary inside the material. The transducer transforms the reflected sound pulses into electromagnetic pulses, which are displayed as pixels with defined grey values thereby creating an image [3]. However, stacked die composed of a combination of multiple thin layers may complicate C-SAM analysis. This is because the thin layers have smaller spacing between the adjacent interface, and shorter delay times for ultrasound traveling from one interface to another. Therefore, failures between the die and die attach may not be easily detected, and false readings may even be expected.

TDR is an electrical fault isolation tool that enables failure localization through electrical signal data. The TDR signal carries the impedance load information of electrical circuitry; hence, the reflected signals show the discontinuity location that has caused the mismatch of impedance. In-depth theory on TDR is further discussed in Chin et al [4]. However, TDR can only estimate where the failure lies, whether it is in

**FIGURE 2.** 3D XRM images showing the interior structures of a CPU stacked die.

consist of non-destructive techniques such as C-Mode scanning acoustic microscopy (C-SAM) and time domain reflectometry (TDR) to isolate the failure, followed by destructive physical failure analysis (PFA). However, there are limitations to each of these techniques when posed with the failure analysis of a more complex stacked die package.

C-SAM allows the inspection of abnormal bumps, delamination and any mechanical failure. A focused soundwave is directed from a transducer to a small point on a target object and is reflected when it

Conaxtechnologies.com/etchdefender ASM<sup>\*</sup> and EPSILON<sup>\*</sup> are registered trademarks of ASM<sup>\*</sup> International. Neither Conax Technologi nor its products are affiliated with, approved by or sponsored by ASM<sup>\*</sup> International. the substrate, die or interposer region. To pin point the exact location within the area of failure is difficult, due to limitations in separating the various small structures through the TDR signal. Additionally, some of the pulse power is reflected for every impedance change, posing challenges regarding unique defect isolation and signal complexity - especially for stacked die [5]. In cases where the failure pins reside in the HBM µbump region, no BGA ball out is available to probe and send an electrical pulse through.

Physical Failure Analysis (PFA) is a destructive method to find and image the failure once non-destructive fault isolation is complete. PFA can be done both mechanically and by focused ion beam (FIB). For stacked dies, FIB is predominantly used to image smaller interconnect structures such as TSVs and µbumps. However, the drawback is that the success of documenting the failure through PFA is largely dependent on how well the non-destructive FA techniques can isolate the failure region. Without good clear fault isolation direction, the failure region might be destroyed or missed during the PFA process, and thus no root cause can be derived.

The integration of XRM into the FA flow can help to overcome the limitations of the various analysis techniques to isolate the failure. It is a great advantage to image small structures and failures with the high spatial resolution and contrast provided by XRM and without destroying the sample. For failures in stacked die, XRM can be integrated into the FA flow for further fault isolation with high accuracy. The visualization of defects and failed material prior to destructive analysis increases FA success rates. However, the trade-off for imaging small defects at high resolution is time. For stacked die failures, C-SAM and TDR can first be performed to isolate the region of failure. With a known smaller region of interest to focus on, the time taken for XRM to visualize the area at high resolution is significantly reduced.

In cases where failures are identified in the HBM  $\mu$ bump, XRM is an effective technique to isolate the failure through 3D defect visualization. With the failure region isolated, XRM can then act as a guide to perform further PFA. Following are three case studies where XRM was used to image HBM packages with stacked dies.

#### **Case studies**

In the first case study, we explore the application of XRM as the primary means of defect visualization where other non-destructive testing and FA techniques

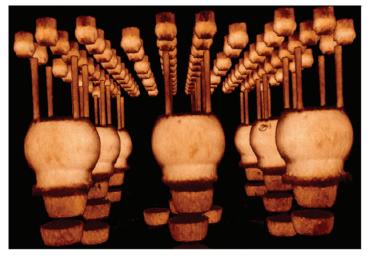

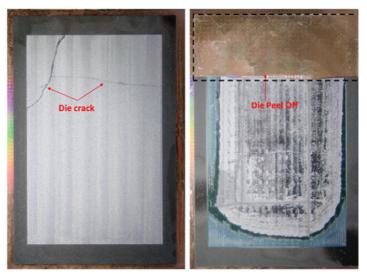

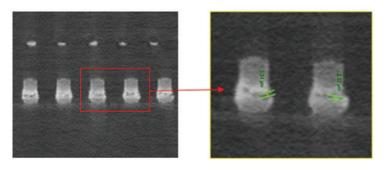

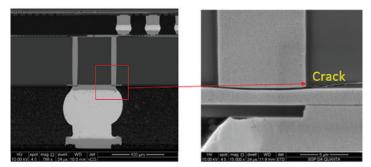

are not possible. An open failure was reported for non-underfilled stacked die packages during a chip package interaction (CPI) study. The suspected open location was within the µbump joints at the HBM stack/ interposer interface. The initial approach exposed the bottom-most die of the HBM stack, followed by FIB cross-sectioning at the specified location. Performing the destructive approach to visualize the integrity of µbump joints in non-underfilled stack die packages was virtually impossible due to the fragility of silicon. The absence of underfill (UF) means that the HBM does not properly adhere to the interposer and is susceptible to peel off. In addition, there was no medium to release shear stresses experienced by the µbump joints upon bending stresses, which could not be absorbed by the package. As seen in **FIGURE 3**, parallel lapping of the HBM stack without UF caused die crack and peeling.

**FIGURE 3.** HBM dies were damaged during PFA sample preparation.

Consequently, to avoid aggravating the damage on the sample, 3D XRM was performed to inspect and visualize the suspected location using a  $0.7\mu$ m/voxel and 4X objective without any sample preparation. **FIGURE 4** shows an example virtual slice where the micro-cracks throughout the row of  $\mu$ bump joints are visualized. The micro-cracks are measured a few microns wide. It is worth noting that the micro-cracks were visible with a short scan time of 1.5 hrs.

With the critical defect information in 3D, PFA was performed on a sample that was underfilled to facilitate ease of sample preparation. SEM images in **FIGURE 5** validated the existence of  $\mu$ bump microcracks observed by 3D XRM inspection.

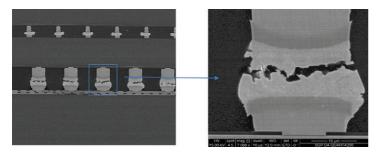

As no defect was observed, XRM was then applied to the corresponding XPU PHY  $\mu$ bump. Contrary to the anticipated  $\mu$ bump open, a short was observed between two  $\mu$ bumps as shown in **FIGURES 6a and**

The  $\mu$ bump short resulted from a solder extrusion bridging two adjacent  $\mu$ bumps. If 3D XRM had not been performed, a blind physical cross-section likely would have been performed on the initially suspected open region. As a

result, the actual failure region may have been missed

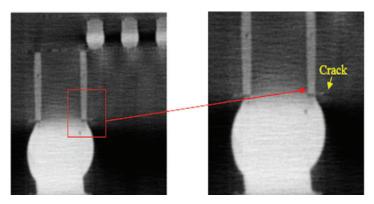

In the final case study, an open failure was reported at a signal pin of a stack die package. As per the traditional FA flow, C-SAM and TDR techniques were applied to isolate the fault. C-SAM results showed an anomaly, and TDR suggested an open in the substrate as demonstrated in

To verify the observations made by C-SAM and TDR

**FIGURE 4.** 3D X-ray microscopy image and measurement of cracked µbump in the non-underfilled HBM packages.

**FIGURE 5.** SEM images show similar cracks in the µbumps visualized by XRM.

In the second case study, the 3D XRM technique was applied to a stacked die package with a failure at a specific HBM/XPU physical interface (PHY) µbump connection. This µbump connection provides specific communication between the HBM stack and XPU die, and there is no package BGA ball out to enable electrical probing. Accordingly, it was not possible to verify if the failure type was an open or short. In addition, there was no means to determine if the failure was

at the HBM or XPU die. Since defects from previous lots were open failures at the PHY  $\mu$ bump of the HBM, 3D XRM was performed at the suspected HBM open region using a 0.85 $\mu$ m/voxel and 4X objective.

non-destructive techniques, 3D XRM was performed using a  $0.80\mu$ m/voxel and 4X objective at the region of

FIGURE 7a and 7b respectively.

bump

**FIGURE 7.** Zoomed in C-SAM image shows anomaly at a C4 bump (a), and TDR shows an open in the substrate (b).

interest.

**6b**.

and/or destroyed.

**FIGURE 6.** 3D X-ray microscopy slice image of (a) solder extrusion from top view and (b) side view.

**FIGURE 8** revealed a crack between the failure C4 bump and associated TSV. A physical cross-section was performed and the passivation cracks between the TSV and interposer backside redistribution layer (RDL) was observed as shown in **FIGURE 9**.

In this case, 3D XRM provided 3D information for the FA engineer to focus on. Without the visual

knowledge on the defect's nature and location, the defect would have been missed during PFA.

**FIGURE 8.** 3D X-ray microscopy slice image of a fine crack between C4 bump and TSV.

FIGURE 9. SEM images show the cracks between TSV and RDL.

#### **Summary and conclusions**

3D integration and packaging have brought about new challenges for effective defect localization, especially when traditional electrical fault isolation is not possible. 3D XRM enables 3D tomographic imaging of internal structures in chips, interconnects and packages, providing 3D structural information of failure areas without the need to destroy the sample. 3D XRM is a vital and powerful tool that helps failure analysis engineers to overcome FA challenges for novel 3D stacked-die packages.

#### Acknowledgement

This article is based on a paper that was presented at the 24th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA 2017).

#### References

- F. Altmann and M. Petzold, "Innovative Failure Analysis Techniques for 3-D Packaging Developments," IEEE Design & Test, Vol. 33, No. 3, pp. 46-55, June 2016.

- C. Y. Liu, P. S. Kuo, C. H. Chu, A. Gu and J. Yoon, "High resolution 3D X-ray microscopy for streamlined failure analysis workflow," 2016 IEEE 23rd International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 2016, pp. 216-219.

- M. Yazdan Mehr et al., "An overview of scanning acoustic microscope, a reliable method for non-destructive failure analysis of microelectronic components," 2015 16th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, Budapest, 2015, pp. 1-4.

- J. M. Chin et al., "Fault isolation in semiconductor product, process, physical and package failure analysis: Importance and overview," Microelectronics Reliability, Vol. 51, Issue 9, pp. 1440-8, Nov. 2011.

- W. Yuan et al., "Packaging Failure Isolation with Time-Domain Reflectometry (TDR) for Advanced BGA Packages," 2007 8th International Conference on Electronic Packaging Technology, Shanghai, 2007, pp. 1-5.

MAGAZINE

WEBSITE

NEWSLETTERS

LIVE EVENTS

# Solid State TECHNOLOGY.

www.Solid-State.com

ADVANCED PACKAGING

MEMS

LEDS

Subscribe today: www.solid-state.com/subscribe

LITHOGRAPHY

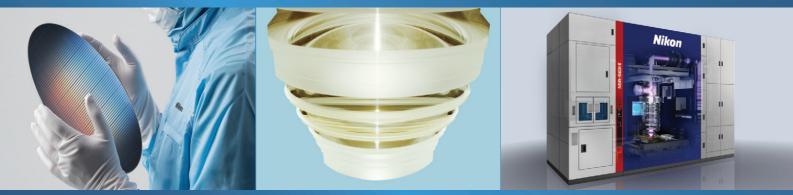

# 2018: Big changes in mask manufacturing and what it means for mask models

#### RYAN PEARMAN, D2S, Inc., San Jose, CA

here are big changes on the horizon for semiconductor mask manufacturing, including the imminent first production use of multi-beam mask writers, and the preparation of all phases of semiconductor manufacturing for the introduction of extreme ultra-violet (EUV) lithography within the next few years. These changes, along with the increasing use of multiple patterning and inverselithography technology (ILT) with 193i lithography, are driving the need for more detailed and more accurate modeling for mask manufacturing.

## New solutions bring new mask modeling challenges

Both EUV and multi-beam mask writing provide solutions to many long-standing challenges for the semiconductor industry. However, they both create new challenges for mask modeling as well. Parameters once considered of negligible impact must be added to mask models targeted for use with EUV and/or multi-beam mask writers. In particular, the correct treatment of dose profiles has emerged as a critical component for mask models targeting these new technologies. This is in addition to scattering effects, such as the well-known EUV mid-range scatter, that must be included in mask models to accurately predict the final mask results. Gaussian models, which form the basis for most traditional mask models, will not be sufficient as many of these new parameters are more properly represented with arbitrary point-spread functions (PSFs).

The most obvious – and most desperately needed – benefit of EUV lithography is greater accuracy due to its enhanced resolution. However, this benefit comes along with a mask-making challenge: wafer-printing defects due to mask errors will appear more readily because of this enhanced resolution. Therefore, the introduction of EUV will require the mean-to-target (MTT) variability on photomasks to become smaller. From a mask manufacturability perspective, all sources of printing errors, systematic and random, must be improved. This means that mask models must also be more accurate, not only in predicting measurements, but also in predicting variability.

A well-known challenge for EUV mask modeling is the EUV mid-range scatter effect. The more complex topology of EUV masks leads to broader scattering effects. In addition to "classical" forward- and backscatter effects, which dominate 193i lithography, there is a mid-range (1 $\mu$ m) scatter that now requires modeling. This phenomenon is non-Gaussian in nature, so cannot be simulated accurately with simple Gaussian ("1G") models. In combination with better treatment of resist effects, a PSF-based model is a much better representation of the critical lithography process.

The eagerly anticipated introduction of EUV will demand a lower-sensitivity resist to be used for EUV masks due to the smaller size of EUV features. This is one of the reasons why multi-beam mask writers have emerged as the replacement for variable shaped beam (VSB) tools for the next generation of mask writers. Slower resists require higher currents, and VSB tools today are limited thermally in ways the massively parallel multi-beam tools are not. In addition to thermal effects, VSB mask writers are runtime-limited by shot count; we are already approaching the practical limit for many advanced masks. Shot count is only expected to grow in the future as pitches shrink and complex small features become prevalent in EUV masks - and even in 193i masks due to increased use of ILT to improve process windows for 193i lithography.

RYAN PEARMAN is Chief Scientist, TrueModel at D2S, Inc., San Jose, CA

**FIGURE 1.** ILT target shape (left), fractured for conventional VSB (center), and rasterized for multi-beam mask writing. The multi-beam rasterization enables more faithful representation of the target shape, without impact on write-time.

In contrast to VSB mask writers, which use shaped apertures to project the shapes (usually rectangles) created by optical-proximity correction (OPC) onto the mask, multi-beam mask writers rasterize the desired mask shapes into a field of pixels, each of which are written by one of hundreds of thousands of individual beamlets (**FIGURE 1**). This enables multi-beam mask writers to write masks in constant time, no matter how complicated the mask shapes. Each of these beamlets can be turned on and off independently to create the desired eBeam input, which enables the fine resolution of smaller shapes. However, it also means that the dose profiles for the multi-beam writers are far more complex, leading to the need for more advanced, separable dose and shape modeling.

Since the beamlets of a multi-beam tool are smaller than the primary length-scale of the dose blur, a key second advantage of multi-beam writers emerges: the patterns written are intrinsically curvilinear. In contrast, VSB mask writers can only print features with limited shapes – principally rectangular and 45-degree diagonals, although some tools enable circular patterns. The critical process-window enhancements for ILT also rely on curvilinear mask shapes, so a synergy appears: better treatment of curved edges at the mask writing step will lead to better wafer yield.

#### Dose and shape: New requirements for multibeam and EUV mask models

Multi-beam mask writers, EUV masks, and even the proliferation of ILT will require mask models to change substantially. Until very recently, curvilinear mask features have been ignored when characterizing masks, and models, when used, have assumed simplicity. Primary electron blur ("forward scattering"), including chemically amplified resist (CAR) effects, historically have been assumed to be a set of Gaussians, with length scales between 15nm and 300nm. All other effects of the mask making processes – long-range electron scattering ("backscatter" and "fogging"), electron charging, development, and plasma-etching effects – have either been assumed to be constant regardless of mask shape or the dose applied, or have been accounted for approximately by inline corrections in the exposure tool.

To meet the challenges posed by both EUV and multibeam writing – especially since they are likely to be employed together – mask models will need to treat dose and shape separately, and to explicitly account for the various scattering, fogging, etch, and charging effects (**FIGURE 2**).

**FIGURE 2.** Simple (standard) mask model (a) versus complex (separable) mask model (b). (Images courtesy: Cliff Henderson, Lithoguru.com). Slides presented at Photomask Japan 2017[1].

When masks were written entirely at nominal dose, dose-based effects could be handled together with shape-based effects as a single term. Several years ago, overlapping shots were introduced by D2S for VSB tools to both improve margins and reduce shot-count for complex mask shapes. At this time, it became clear that dose modulation (including overlapping shots) required specific modeling. Some effects (like etch) varied only with respect to the resist contour shapes, while other print bias effects were based on differences in exposure slope near the contour edge. For all the complexity of VSB overlapping shots, all identical patterns were guaranteed to print in the same way. Today, with multi-beam writers, there are significant translational differences in features due to dose-profile changes as they align differently with the multi-beam pixel grid.

We discussed earlier that multi-beam tools print curvilinear shapes. We should point out that even Manhattan designs become corner-rounded on the actual masks at line ends, corners, and jogs. Why? Physics is almost never Manhattan, and treating it as such will be inaccurate, as in the case of etching effects computed in the presence of Manhattan jogs. We need to embrace the fact that all printed mask shapes will be curvilinear and ensure that any shape-based simulation is able to predict effects at all angles, not just 0 and 90.

## Increasing mask requirements drive the need for mask model accuracy

As we continue to move forward to more advanced processes with ever-smaller feature sizes, the requirement for better accuracy increases. There is quite literally less room for any defects. This increased emphasis on accuracy and precision is what drives the adoption of new technologies such as EUV and multibeam mask writing; it drives the increased need for better model performance as well.

We have already discussed several model parameters that will need to be re-evaluated and handled differently in order to achieve greater accuracy. Accuracy also requires a more rigorous approach to the calibration and validation of models with test chips that isolate specific physics effects with specific test structures. For example, masks that include complex shapes require 2D validation. Today's VSB mask writers are Manhattan (1D) writing instruments, so models built using these tools are by definition 1D-centric. Inaccuracies in 1D models are exacerbated when tested against a 2D validation. Physics-based models are far more likely to extrapolate to 2D shapes, and are better for ILT.

As features shrink, the accuracy of individual shapes on the mask is impacted increasingly by their proximity to other shapes. The context for each shape on the mask becomes as important as the shape itself. The solution is to model each shape within the context of its surroundings. This is driving the need for simulation-based modeling and mask-correction methodologies.

# GPU acceleration: Making simulation-based mask modeling practical

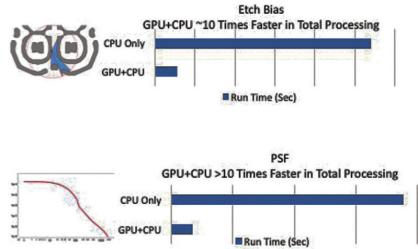

Historically, simulation-based processing of mask models resulted in unacceptably long simulation runtimes. The most common approach until recently has been to use model-based or rules-based methodologies that, while providing less accuracy, result in faster runtimes. The advent of GPU-accelerated mask simulation has changed this picture. GPU acceleration is particularly suited to "single instruction, multiple data" (SIMD) computing, which makes it a very good fit for simulation of physical phenomena, and enables fullreticle mask simulation within reasonable runtimes.

An additional advantage of GPU acceleration is the ability to employ PSFs without runtime impact (**FIGURE 3**). As we've already discussed, PSFs are a natural choice for the mask-exposure model, including EUV mask mid-range scattering effects, forward-scattering details, and modeling back-scattering by construction. Using PSFs, any dose effect of any type can be exactly modeled during simulation-based processing.

GPU acceleration opens the door for simulation-based correction of a multitude of complex mask effects based on physics-based models, affording practical simulation runtimes for these more complex models.

**FIGURE 3.** The runtimes for etch-bias and PSF examples on a CPU-only computing platform, versus an accelerated CPU + GPU platform. Runtimes with CPU + GPU are 10 times faster.

LITHOGRAPHY

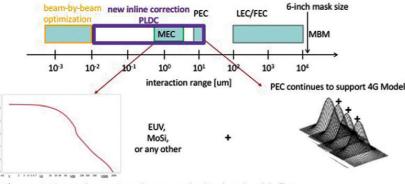

## PLDC: New mask models at work in multi-beam mask writers

As with any big changes to the semiconductor manufacturing process, the industry has been preparing for EUV and multi-beam mask writing for several years. These preparations have required various members of the supply chain to work together to deploy effective solutions. One example of this collaboration in the mask-modeling realm is the introduction by NuFlare Technology of pixellevel dose correction (PLDC) in its MBM-1000 multibeam mask writer. At the 2017 SPIE Photomask Japan conference, NuFlare and D2S jointly presented a paper [2] detailing the mask modeling – and GPU acceleration – used in this new inline mask correction.

PLDC manipulates the dose of pixels to perform shortrange (effects in the 10nm scale to  $3-5\mu$ m scale) linearity correction while improving the overall printability of the mask. In addition to the traditional four-Gaussian (4G) PEC model, PLDC combines for the first time an inline 10nm-100nm short-range linearity correction with a 1 $\mu$ m scale mid-range linearity correction (**FIGURE 4**). This mid-range correction is particularly useful for EUV mid-range scatter correction.

Any PSF for up to 1~5 um scale range is used to express the dose-based model effects PSF = Point Spread Function expressed as distance-value pairs

**FIGURE 4.** PLDC in the context of other correction mechanisms in MBM-1000.

The dose-based effects portion of the D2S mask model, TrueModel, are expressed as a PSF for an interaction range up to  $3-5\mu$ m, and with a 4G PEC model for interaction range up to 40-50 $\mu$ m. Being able to express any arbitrary PSF as the correction model allows smoothing of "shoulders" that are often present on multiple Gaussian models, and allows proper modeling of effects that are not fundamentally Gaussian in nature (such as the EUV mid-range scatter). This ability to model physical effects and correct for them inline with mask writing results in more accurate masks, including for smaller EUV shapes and for curvilinear ILT mask shapes. PLDC is simulation-based, so it has the ability to be very accurate regardless of targeted shape, regardless of mask type (e.g., positive, negative EUV, ArF, NIL master) with the right set of mask modeling parameters.

GPU acceleration enables fast computing of PSF convolutions for all dose-based effects up to  $3-5\mu m$  range, performed inline in the MBM-1000, which helps to maintain turnaround time in the mask shop.

#### Conclusions

Mask models need some significant adaptations to meet the coming challenges. The new EUV/multi-beam mask writer era will require mask models to be more detailed and more accurate. More complex dose profiles and more complex electron scattering require PSFs be added to the industry-standard Gaussian models. More rigorous mask models with specific dose and specific shape effects are now needed. Simulation-based mask processing, made practical by GPU acceleration, is necessary to take contextbased mask effects into account.

> The good news is that the mask industry has been preparing for these changes for several years and stands ready with solutions to the challenges posed by these new technologies. Big changes are coming to the mask world, and mask models will be ready.

#### References

1. Pearman, Ryan, et al, "EUV modeling in the multi-beam mask writer era," SPIE Photomask Japan, 2017.

"GPU-accelerated inline linearity correction: pixel-level dose correction (PLDC) for the MBM-1000," Zable, Matsumoto, et al, SPIE Photomask Japan, 2017. DEPOSITION

# Understanding ALD, MLD and SAMs as they enter the fab

**BARRY ARKLES, JONATHAN GOFF,** Gelest Inc., Morrisville PA; **ALAIN E. KALOYEROS,** SUNY Polytechnic Institute, Albany, NY

As the world of advanced manufacturing enters the sub-nanometer scale era, it is clear that ALD, MLD and SAM represent viable options for delivering the required few-atoms-thick layers required with uniformity, conformality, and purity.

evice and system technologies across several industries are on the verge of entering the sub-nanometer scale regime. This regime requires processing techniques that enable exceptional atomic level control of the thickness, uniformity, and morphology of the exceedingly thin (as thin as a few atomic layers) film structures required to form such devices and systems.[1]

In this context, atomic layer deposition (ALD) has emerged as one of the most viable contenders to deliver these requirements. This is evidenced by the flurry of research and development activities that explore the applicability of ALD to a variety of material systems,[2,3] as well as the limited introduction of ALD TaN in full-scale manufacturing of nanoscale integrated circuitry (IC) structures.[4] Both the success and inherent limitations of ALD associated with repeated dual-atom interactions have stimulated great interest in additional self-limiting deposition processes, particularly Molecular Layer Deposition (MLD) and Self-Assembled Monolayers (SAM). MLD and SAM are being explored both as replacements and extensions of ALD as well as surface modification techniques prior to ALD.[5]

ALD is a thin film growth technique in which a substrate is exposed to alternate pulses of source precursors, with intermediate purge steps typically consisting of an inert gas to evacuate any remaining precursor after reaction with the substrate surface. ALD differs from chemical vapor deposition (CVD) in that the evacuation steps ensure that the different precursors are never present in the reaction zone at the same time. Instead, the precursor doses are applied as successive, non-overlapping gaseous injections. Each does is followed by an inert gas purge that serves to remove both byproducts and unreacted precursor from the reaction zone.

The fundamental premise of ALD is based on selflimiting surface reactions, wherein each individual precursor-substrate interaction is instantaneously terminated once all surface reactive sites have been depleted through exposure to the precursor. For the growth of binary materials, each ALD cycle consists of two precursor and two purge pulses, with the thickness of the resulting binary layer per cycle (typically about a monolayer) being determined by the precursor-surface reaction mode. The low growth rates associated with each ALD cycle enable precise control of ultimate film thickness via the application of repeated ALD cycles. Concurrently, the self-limiting ALD reaction mechanisms allow excellent conformality in ultra-high-aspectratio nanoscale structures and geometries.[6]

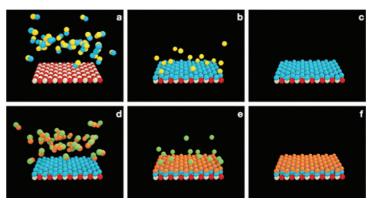

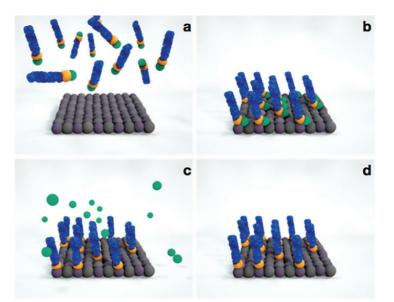

A depiction of an individual ALD cycle is shown in **FIGURE 1**. In Fig. 1(a), a first precursor A is introduced in the reaction zone above the substrate surface.

FIGURE 1. Schematic Depiction of an ALD Cycle of a Binary Film.

Precursor A then adsorbs intact or reacts (partially) with the substrate surface to form a first monolayer, as shown in Fig. 1(b), with any excess precursor and potential byproducts being evacuated from the reaction zone through a subsequent purge step. In Fig. 1(d), a second precursor Y is injected into the reaction zone and is made to react with the first monolayer to form a binary atomic layer on the substrate surface, as displayed in Fig. 1(e). Again, all excess precursors and reaction byproducts are flushed out with a second purge step 1(f). The entire process is performed repeatedly to achieve the targeted binary film thickness.

In some applications, a direct or remote plasma is used as an intermediate treatment step between the two precursor-surface interactions. This treatment has been reported to increase the probability of surface adsorption by boosting the number of active surface sites and lowering the reaction activation energy. As a result, such treatment has led to increased growth rates and reduce processing temperatures.[7]

A number of benefits have been cited for the use of ALD, including high purity films, absence of particle contamination and pin-holes, precise control of thickness at the atomic level, excellent thickness uniformity and step coverage in complex via and trench topographies, and the ability to grow an extensive array of binary material systems. However, issues with surface roughness and large surface grain morphology have also been reported. Another limitation of ALD is the fact that it is primarily restricted to single or binary material systems. Finally, extremely slow growth rates continue to be a challenge, which could potentially restrict ALD's applicability to exceptionally ultrathin films and coatings.

These concerns have spurred a renewed interest in other molecular level processing technologies that share the self-limiting surface reaction characteristics of ALD. Chief among them are MLD and SAM. MLD refers principally to ALD-like processes that also involve successive precursor-surface reactions in which the various precursors never cross paths in the reaction zone. [8] However, while ALD is employed to grow inorganic material systems, MLD is mainly used to deposit organic molecular films. It should be noted that this definition of MLD, although the most common, is not yet universally accepted. An alternative characterization refers to MLD as a process for the growth of organic molecular components that may contain inorganic fragments, yet it does not exhibit the self-limiting growth features of ALD or its uniformity of film thickness and step coverage.[2]

A depiction illustrating a typical MLD cycle, according to the most common definition, is shown in **FIGURE 2**. In Fig. 2(a), a precursor is introduced in the reaction zone above the substrate surface. Precursor C adsorbs to the substrate surface and is confined by physisorption (Fig. 2(b)). The precursor then undergoes a quick chemisorption reaction with a significant number of active surface sites, leading to the self-limiting formation of molecular attachments in specific assemblies or regularly recurring structures, as displayed in Fig. 2(c). These structures form at significantly lower process temperatures compared to traditional deposition techniques.

**FIGURE 2.** Schematic Depiction of an MLD Cycle for Ultrathin Film Formation.

To date, MLD has been successfully applied to grow exceptionally thin films for applications as organic, inorganic, and hybrid organic-inorganic dielectrics and polymers for IC applications; [1,9] nanoprobes for in-vitro imaging and interrogation of biological cells; [10] photoluminescent devices; [7] and lithium-ion battery electrodes.[11]

SAM is a deposition technique that involves the spontaneous adherence of organized organic structures on a substrate surface. Such adherence takes place through adsorption from the vapor or liquid phase through relatively weak interactions with the substrate surface. Initially, the structures are adsorbed on the surface by physisorption through, for instance, van der Waals forces or polar interactions. Subsequently, the selfassembled monolayers become slowly confined by a chemisorption process, as depicted in **FIGURE 3**.

**FIGURE 3.** Schematic Depiction of SAM Formation of a Monolayer-thick Film.