OCTOBER 2018

# Solid State TECHNOLOGY

**Insights for Electronics Manufacturing**

**Emerging Memories for the Zettabyte Era** P. 14

Al Chips: Challenges and Opportunities P. 18

New Thinking Required for Machine Learning P. 23

## Perfecting Yield with Proactive Optimization PID

## Park NX-Wafer

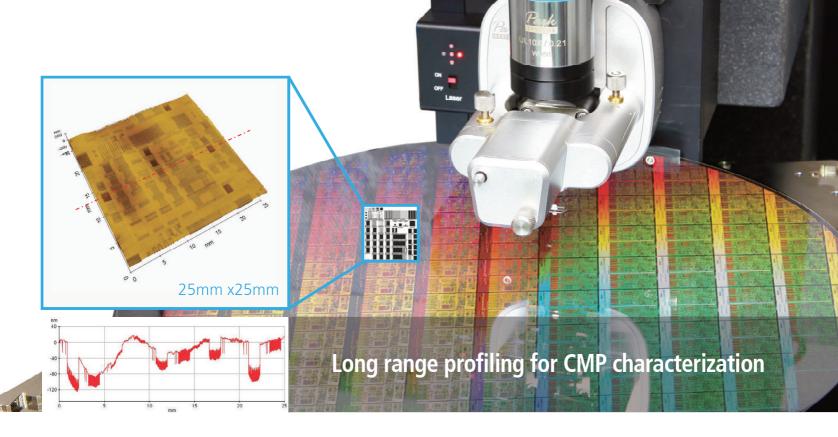

Low Noise, High Throughput Atomic Force Microscope with Automatic Defect Review & Atomic Force Profiler

• Low noise atomic force profiler for more accurate CMP profile measurements

ICON EUROPA

November 13-16, 2018 - Munich / Germany

- Sub-angstrom surface roughness measurements

- Fully automated AFM solution for defect imaging and analysis

- Capable of scanning 300 mm wafers

- Can improve defect review productivity by up to 1000%

- Percentile or Histogram based auto-analysis

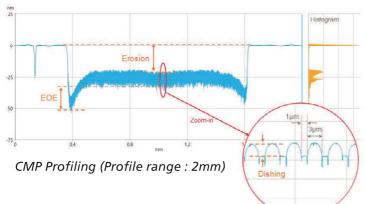

- Erosion, EOE(Edge-Over-Erosion) and Dishing

www.parksystems.com inquiry@parksystems.com

## Solid State TECHNOLOGY

#### OCTOBER 2018 VOL. 61 NO. 7

Caption: Proactive yield perfection (PYP) is a comprehensive systems-level approach to perfecting yield through detailed surveillance and sophisticated modeling. Source: Rudolph Technologies

## FEATURES

## YIELD | Perfecting yield with proactive optimization throughout the process and across the supply chain

Increasingly dispersed and complex supply chains require a proactive, integrated, systems-level approach to optimizing yields.

Prasad Bachiraju, Rudolph Technologies, Inc., Wilmington, Mass.

#### MEMORY | Emerging memories for the zettabyte era

The scaling of traditional memories such as SRAM, DRAM and Flash is no longer following the data growth rate, especially in terms of energy and speed. *Gouri Sankar Kar and Arnaud Furnemont, imec, Leuven, Belgium*

#### ARTIFICIAL INTELLIGENCE | AI chips: Challenges and opportunities

To get to the next level in performance/Watt, innovations being researched at the AI chip level include low precision, analog and resistive computing. *Pete Singer, Editor-in-Chief*

#### ARTIFICIAL INTELLIGENCE | New thinking required for machine learning

Speakers argue the semiconductor community thus far has not been doing enough to enable machine intelligence. Dave Lammers, Contributing Editor

## **MATERIALS** | There's still plenty of room at the bottom: Isotopically pure materials for when every atom counts

When different isotopes of atoms have significantly different properties, the ability to create isotopically pure materials becomes essential.

Dr. Paul Stockman, Linde Electronics, Taipei, Taiwan

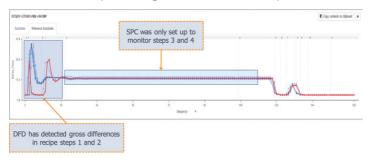

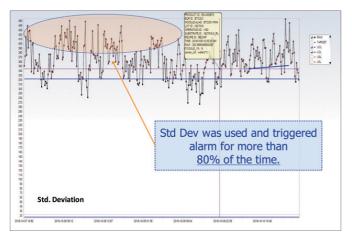

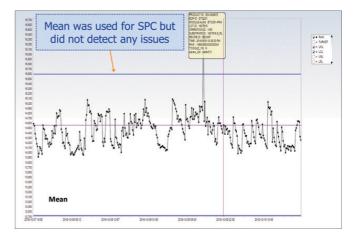

## **YIELD OPTIMIZATION** | Dynamic Fault Detection: Utilizing AI and IoT to revolutionize manufacturing

A new approach in Fault Detection and Classification (FDC) allows engineers to uncover issues more thoroughly and accurately by taking advantage of full sensor traces. *Tom Ho and Stewart Chalmers, BisTEL, Santa Clara, CA*

## COLUMNS

- 2 Editorial A new era of growth Pete Singer, Editor-in-Chief

- 8 Packaging Samsung at ECTC: Emphasis on warpage control *Phil Garrou, Contributing Editor*

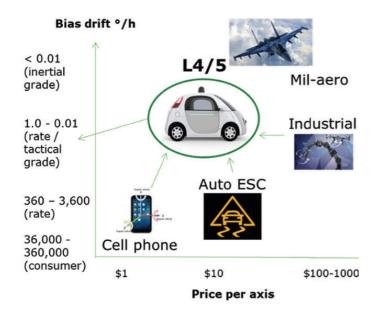

- **31** Industry Forum Sensors in the new age of the car Richard Dixon, Senior Principal Analyst, Sensors, IHS Markit

## DEPARTMENTS

- 4 Web Exclusives

- **5** News

- 30 Ad Index

COVER

## editorial

## A new era of growth

The semiconductor industry is in a new era of growth, driven by a diverse array of applications and new computing architectures.

Just one indicator of the growth: Total wafer shipments in 2018 year are expected to eclipse the all-time market high set in 2017 and continue to reach record levels through 2021, according to SEMI's recent semiconductor industry annual silicon shipment forecast.

Much of this growth will come from the need for better connectivity and more intelligent data analysis using artificial intelligence (AI). AI represents a market opportunity \$2 trillion of on top of the existing \$1.5-2B information technology industry. According to IBM's John E. Kelly, "This is the era that's going to power our semiconductor industry forward. The number of opportunities is enormous." See AI chips: Challenges and opportunities on pg. 23.

Making AI semiconductor engines will require a wildly innovative range of new materials, equipment, and design methodologies. Moore's Law seems to be slowing, so chips designed for AI and more traditional applications will likely include advanced packaging/heterogeneous integration (think chip stacking), and silicon photonics.

In addition to AI chips from traditional IC companies such as Intel, IBM and Qualcomm, more than 45 start-ups are working to develop new AI chips, with VC investments of more than \$1.5B -- at least five of them have raised more than \$100 million from investors. Tech giants such as Google, Facebook, Microsoft, Amazon, Baidu and Alibaba are also developing AI chips.

AI will be paired with new computational methods (think non Von Neumman), such as neuromorphic methods that mimic how the brain works, and quantum computing. Faster communication with higher bandwidth will be required. 5G wireless communication is coming, as is improved WiFi, near-field communication, Bluetooth and satellite communication.

Huge opportunities exist in automotive electronics, as autonomous driving moves closer to reality. Again, AI will play a critical role. Virtual reality will be combined with AI to create a truly immersive experience that mankind has never experienced.

Semiconductors and AI will play an increasingly important role in the healthcare industry, as diagnostic tools and patient monitoring.

A good example of how this all will impact the semiconductor industry moving forward can be found in DARPA's Electronics Resurgence Initiative (ERI). ERI calls for innovative new approaches to microsystems materials, designs, and architectures. The President's budget for FY19 includes continued annual investments of \$300 million over the next five years for ERI's research efforts-potentially upwards of \$1.5 billion over the initiative's lifetime.

In one project in the initiative, Applied, Arm and Symetrix will work together to develop a coprorrelated electron switch. "Most of the materials we are studying in the context of this research should, according to classical theories, conduct electrons, but thanks to correlation they can also exhibit insulating properties under certain conditions due to electron-electron interactions that don't happen according to traditional band theory," notes David Thompson of Applied Materials. "Welcome to the weird and wonderful world of quantum matter!" he adds.

-Pete Singer, Editor-in-Chief

## Solid State TECHNOLOGY.

Pete Singer, Editor-in-Chief Ph: 978.470.1806,

psinger@extensionmedia.com **Shannon Davis,** Editor, Digital Media Ph: 603.547.5309

sdavis@extensionmedia.com Ed Korczynski, Senior Technical Editor.

edk@extensionmedia.com

Dave Lammers, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor Vivek Bakshi, Contributing Editor CREATIVE/PRODUCTION/ONLINE Marjorie Sharp, Production Traffic Coordinator

Nicky Jacobson, Senior Graphic Designer Slava Dotsenko, Senior Web Developer

MARKETING/CIRCULATION

Jenna Johnson, iiohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

**Clair Bright**, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2018 by Extension Media LLC. All rights reserved. Printed in the U.S.

OCTOBER 2018 VOL. 61 NO. 7 • Solid State Technology ©2018 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmaii: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343. (8 am – 5 pm, PST). Extension M E D I A

1786 18th Street San Francisco, CA 94107

Co-located with electronica 2018

# SEMICONDUCTORS DRNE SMART

## 13-16 Nov 2018, Messe München, Munich, Germany

This year SEMICON Europa will be the strongest single event for electronics manufacturing in Europe and is broadening the range of attendees across the electronics supply chain. The event covers the areas of Materials, Semiconductors, Frontend and Back-end Manufacturing, Advanced Packaging, MEMS/Sensors, Power and Flexible Electronics, and Automotive. **We connect the breadth of the entire electronics supply chain** by including applications such as the Internet of Things, Artificial Intelligence, Machine Learning, and other adjacent markets.

## **CONFERENCES:**

Automotive Forum 22<sup>nd</sup> Fab Management Forum 2018 FLEX Europe - Be Flexible Advanced Packaging Conference Strategic Materials Conference

## EXHIBITION AND FREE PROGRAMS:

Showfloor (Hall A4) TechARENA TechLOUNGE Talent & Leadership in the Digital Economy

## EXECUTIVE NETWORKING EVENTS:

Executive Keynote Opening SEMI Networking Night

## **KEY FACTS**

More than ...

35% visitors represent engineering job functions

70% involved in purchasing decisions

## Vu

33% are executives and senior managers

8,700 visitors from 85 countries registered in 2017

## INCREASE YOUR EXPOSURE!

Contact us to **become a sponsor!** SEMI Europe Sales: Denada Hodaj, dhodaj@semi.org

To **reserve your booth** contact SEMI Europe Tradeshow Operations: SEMICONEuropa@semi.org

semi

**REGISTER NOW!**

# Online@www.solid-state.com

## **Web Exclusives**

## Automating 200mm semiconductor fabs to meet growing demand

SEMI met with Heinz Martin Esser, managing director at Fabmatics GmbH, to discuss how existing 200mm semiconductor fabs can master the challenges of a 24×7 production under highest cost and quality pressure by implementing intralogistics automation solutions. The two spoke ahead to his presentation at the Fab Management Forum at SEMICON Europa 2018, 13-16, November 2018, in Munich, Germany.

#### https://bit.ly/2yTHO2w

## Insights from the Leading Edge: IC history for the younger generation

The IC industry started out like a poker championship tournament. Hundreds of players, through the years, put up their entry fee to compete ( i.e. paying for their fabs) and the competition began. https://bit.ly/2PjeYj7

## How will graphene, the 2D wonder material, change the semiconductor industry?

Materials innovation has always been vital to the semiconductor industry. In the past, it was high- $\kappa$  gate dielectrics. Today, Cobalt is seen as a replacement for Tungsten in middle-of-line (MOL) contacts. What materials innovation will the future bring? A likely answer is graphene, the wonder material discovered in 2004.

https://bit.ly/2Ply20b

## Power subsystems: Surging on a wave of vacuum processing equipment

Process power and reactive gas subsystems for semiconductor manufacturing equipment have grown at a CAGR of 21% since 2013. The segment growth is considerably above the critical subsystems industry average of 9.5% and is attributable to higher demand for vacuum processing equipment over the period. https://bit.ly/2E9u49U

## IBM's Jeff Welser to Keynote The ConFab 2019

AI was a big focus on The ConFab and 2018 and we will continue that theme in 2019 with a keynote talk by IBM's Jeff Welser. The ConFab 2019 will return to The Cosmopolitan of Las Vegas on May 14-17. In 2018, AI and other leading technologies were discussed by speakers from IBM, Google, Nvidia, HERE Technologies, Silicon Catalyst, TechInsights, Siemens and Qorvo, among many others.

https://bit.ly/2llj6Xj

## Ruthenium nanolayers are ferromagnetic at RT

Researchers from Intel Corporation and the University of Minnesota and the University of Wisconsin have shown that strained atom-scale films of pure ruthenium (Ru) metal exhibit ferromagnetism at room temperature, openning up the possibility of using the material to build novel magnetic random access memory (MRAM) devices. (*From SemiMD.com*) https://bit.ly/2MsM1UH

## SEMI calls for exclusion process for products in new China tariff list

SEMI joined a coalition of business groups in calling for Ambassador Robert Lighthizer, U.S. Trade Representative, to enact an exclusion process for the most recent tranche of tariffs on \$200 billion in goods imported from China. https://bit.ly/2OdCCkD

#### Toshiba Memory and Western Digital celebrate the opening of Fab 6 and Memory R&D Center at Yokkaichi, Japan

Toshiba Memory Corporation and Western Digital Corporation (NASDAQ:WDC) yesterday celebrated the opening of a new semiconductor fabrication facility, Fab 6, and the Memory R&D Center, at Yokkaichi operations in Mie Prefecture, Japan.

https://bit.ly/2yl5xsd

Please send news articles to sdavis@extensionmedia.com

## worldnews

**EUROPE** - Leti and EFI launched a project to improve reliability and speed of low-cost electronic devices for autos.

*ASIA* - MagnaChip will host Foundry Technology Symposium in Shenzhen, China in November 2018.

USA - GLOBALFOUNDRIES extended FinFET offering with new features to enable tomorrow's intelligent systems.

**EUROPE - STMicroelectronics** and **Leti** announced their cooperation to industrialize GaN (Gallium Nitride)-on-Silicon technologies for power switching devices.

**USA - Lam Research** named its 2018 Supplier Excellence Award recipients.

ASIA - Air Products announced it has been awarded by Samsung Electronics additional gaseous nitrogen and hydrogen supply to its semiconductor fab in Giheung, South Korea.

USA - Imagination and GLOBALFOUNDRIES announced a collaboration to deliver ultra-low-power connectivity solutions for IoT applications.

ASIA - Amkor opened a new semiconductor package manufacturing and test plant in Taiwan.

USA - SUNY Poly professor was awarded \$500,000 National Science Foundation grant to develop next-generation memory technology.

USA - Keysight Technologies' 3D planar electromagnetic simulator certified for GLOBALFOUNDRIES 22FDX process technology.

# news

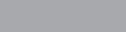

## New fabs invest over \$220B; 2019 to mark all-time spending high

Global fab equipment spending will increase 14 percent this year to US\$62.8 billion and is expected to rise 7.5 percent, to US\$67.5 billion, in 2019, marking the fourth consecutive year of spending growth and the highest investment year for fab equipment in the history of the industry, according to the latest World Fab Forecast Report published by SEMI. Investments in new fab construction are also nearing a record with a fourth consecutive year of growth predicted and capital outlays next year approaching US\$17 billion.

Investments for fab technology and product upgrades, as well as for additional capacity, will grow as the emergence of numerous new fabs significantly increases equipment demand, the forecast shows. The World Fab Forecast Report currently tracks 78 new fabs and lines that have or will start construction between 2017 to 2020 (with various probabilities) and will eventually require more US\$220 billion in fab equipment (Figure 1). Construction spending for these fabs and lines is expected to reach US\$53 billion during this period.

Korea is projected to lead other regions in fab equipment investments with US\$63 billion, US\$1 billion more than second-place China. Taiwan is expected to claim the third spot at US\$40 billon, followed by Japan at US\$22 billion and the Americas at US\$15 billion. Europe and Southeast Asia will share sixth

**FIGURE 1.** Shows the investment potential of new fabs and lines starting construction between 2017 and 2020.

place, with investments totaling US\$8 billion each. Fully 60 percent of these fabs will serve the Memory sector (the lion's share will be 3D NAND), and a third will go to Foundry.

Of the 78 fab construction projects starting construction between 2017 and 2020, 59 began construction in the first two years (2017 and 2018), while 19 are expected to begin in the last two years (2019 and 2020) of the tracking period.

Equipping a new fab typically takes one to one and a half years, though some fabs take two years and others longer, depending on various factors as such the company, fab size, product type and region. Approximately half of the projected US\$220 billion will be spent from 2017 and 2020, with less than 10 percent invested in 2017 and 2018, nearly 40 percent in 2019 and 2020, and the rest after 2020.

While the US\$220 billion estimate is based on current insights of known and announced fab plans, total spending could exceed this level as many companies continue to announce plans for new fabs. Since the last quarterly publication of the report published last quarter, 18 new records – all new fabs – have been added to the forecast. Up-todate and detailed analysis, with a bottomsup approach, is available by subscribing to SEMI's World Fab Forecast Report.

> Since its June 1 publication, more than 340 updates have been made to the World Fab Forecast. The report now includes more than 1,200 records of current and future front-end semiconductor facilities from high-volume production to research and development. The report covers data and predictions through 2019, including milestones, detailed investments by quarter, product types, technology nodes and capacities down to fab and project level.

## **nev/S**cont.

## DRAM market braces for slower growth

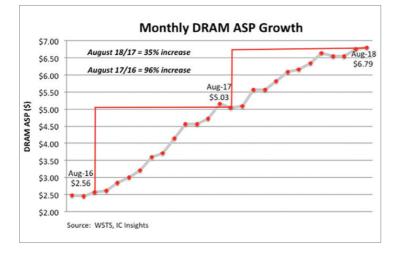

In its September Update to The 2018 McClean Report, IC Insights discloses that over the past two years, DRAM manufacturers have been operating their memory fabs at nearly full capacity, which has resulted in steadily increasing DRAM prices and sizable profits for suppliers along the way. Figure 1 shows that the DRAM average selling price (ASP) reached \$6.79 in August 2018, a 165% increase from two years earlier in August of 2016. Although the DRAM ASP growth rate has slowed this year compared to last, it has remained on a solid upward trajectory through the first eight months of 2018.

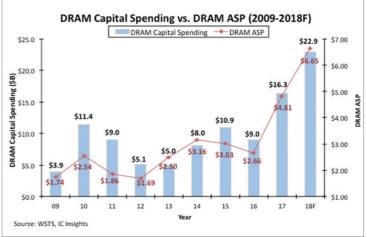

The DRAM market is known for being very cyclical and after experiencing strong gains for two years, historical precedence now strongly suggests that the DRAM ASP (and market) will soon begin trending downward. One indicator suggesting that the DRAM ASP is on the verge of decline is back-to-back years of huge increases in DRAM capital spending to expand or add new fab capacity (Figure 2). DRAM capital spending jumped 81% to \$16.3 billion in 2017 and is expected to climb another 40% to \$22.9 billion this year. Capex spending at these levels would normally lead to an overwhelming flood of new capacity and a subsequent rapid decline in prices.

However, what is slightly different this time around is that big productivity gains normally associated with significant spending upgrades are much less at the sub-20nm process node now being used by the top DRAM suppliers as compared to the gains seen in previous generations.

At its Analyst Day event held earlier this year, Micron presented figures showing that manufacturing DRAM at the sub-20nm node required a 35% increase in the number of mask levels, a 110% increase in the number of non-lithography steps per critical mask level, and 80% more cleanroom

space per wafer out since more equipment—each piece with a larger footprint than its previous generation—is required to fabricate  $\leq 20$ nm devices. Bit volume increases that previously averaged around 50% following the transition to a smaller technology node, are a fraction of that amount at the  $\leq 20$ nm node. The net result is suppliers must invest much more money for a smaller increase in bit volume output. So, the recent uptick in capital spending, while extraordinary, may not result in a similar amount of excess capacity, as has been the case in the past.

As seen in Figure 2, the DRAM ASP is forecast to rise 38% in 2018 to \$6.65, but IC Insights forecasts that DRAM market growth will cool as additional capacity is brought online and supply constraints begin to ease. (It is worth mentioning that Samsung and SK Hynix in 3Q18 reportedly deferred some of their expansion plans in light of expected softening in customer demand.)

Of course, a wildcard in the DRAM market is the role and impact that the startup Chinese companies will have over the next few years. It is estimated that China accounts for approximately 40% of the DRAM market and approximately 35% of the flash memory market.

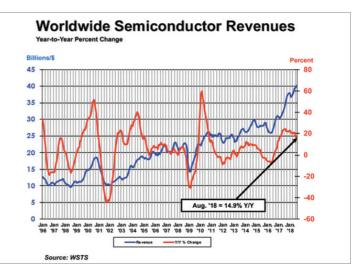

At least two Chinese IC suppliers, Innotron and JHICC, are set to participate in this year's DRAM market. Although China's capacity and manufacturing processes will not initially rival those from Samsung, SK Hynix, or Micron, it will be interesting to see how well the country's startup companies perform and whether they will exist to serve China's national interests only or if they will expand to serve global needs. The Semiconductor Industry Association (SIA), representing U.S. leadership in semiconductor manufacturing, design, and research, announced worldwide sales of semiconductors reached \$40.16 billion for the month of August 2018, an increase of 14.9 percent compared to the August 2017 total of \$34.96 billion. Global sales in August 2018 were 1.7 percent higher than the July 2018 total of \$39.49 billion. All monthly sales numbers are compiled by the World Semiconductor Trade Statistics (WSTS) organization and represent a threemonth moving average.

"Global semiconductor sales continued to bound upward in August, easily outperforming sales from last August and narrowly surpassing last month's total," said John Neuffer, president and CEO, Semiconductor Industry Association. "While year-to-year growth has moderated somewhat in recent months, sales remain strong across every major semiconductor product category and regional market, with the China and Americas markets standing out with the largest year-year growth."

Regionally, sales increased compared to August 2017 in China (27.3 percent), the Americas (15.0 percent), Europe (9.5 percent), Japan (8.4 percent), and Asia Pacific/All Other (4.7 percent). Sales were up compared to last month in China (2.1

percent), the Americas (3.6 percent), and Asia Pacific/All Other (1.3 percent), and decreased slightly inJapan (-0.1 percent), and Europe (-1.4 percent).

For comprehensive monthly semiconductor sales data and detailed WSTS Forecasts, consider purchasing the WSTS Subscription Package. For detailed data on the global and U.S. semiconductor industry and market, consider purchasing the 2018 SIA Databook.

## Samsung at ECTC: Emphasis on warpage control

At the 2018 ECTC, Samsung presented several papers on their advanced packaging activities. In one paper, Samsung teamed with SUNY Binghamton to discuss "design Guidelines of 2.5D Package with Emphasis on Warpage Control and Thermal Management." A 2.5D Package is composed of many material sets and in general its size is larger than conventional single chip packages. The CTE of substrate is a well-known factor to control warpage in a single die packages. However, the existence of another layer (interposer) makes the problem more complicated. Optimization of the material sets, which include lid, EMC, chip, Interposer and geometric factors, are essential. From their modeling studies it is clear that substrate CTE is more influential than other criteria.

Area ratio of lid attach, lid thickness, EMC CTE and substrate CTE are major factors influencing for warpage. For thermal management, EMC coverage on top of the chip, (cooling) fan speed, and conductivity of TIM are the major factors that affect thermal resistance.

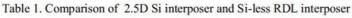

In their presentation on "Low Cost Si-less RDL Interposer Pkg for High Performance Computing Applications" In this presentation a concept for a Si-less redistribution layer is descried for server/HPC applications and warpage behavior, electrical performance and reliability of the RDL interposer package were evaluated.

Si-less RDL interposer

Wafer level

< 2~5 µm

Middle

Low (1x)

Panel level

2µm target

Low

High (~3.5x)

Low cost and large size packages

with wider L/S

Packaging

Test

L/S

Cost

Productivity

Application

2.5D Si interposer

< 1 µm

High

Low (1x)

High-end packages

with fine L/S

PHIL GARROU. Contributing Editor

Si-interposer have attracted attention for high end sever products due to high electrical performance at low power consumption. The key barrier of Si-interposer adoption, utilizing TSV, is high manufacturing cost for large interposer sizes. They suggest a Si-less redistribution layer (RDL) interposer platform for high performance applications as a low cost package solution.

The Table compares 2.5D Si interposer technology to wafer level and panel level RDL interposers.

The fabrication process flow of RDL interposer package is classified into six main steps as summarized in the fig below. RDL formation, multi-chip bonding on RDL, encapsulation, chip exposure, solder ball attachment, and interposer assembly on PCB. The most challenging aspect of the assembly is reportedly the warpage control of interposer packages, due to the large size and multichips.

Samsung clams that the RDL interposer package has the advantage of lower manufacturing cost over Si-interposer by replacing TSV with RDL. Their results showed that RDL interposer warpage is more controllable than Si-interposer at room and high temperature by the optimization of design, process condition and material selection. Their test structure, a RDL interposer package whose size is larger than 3000mm2 included four HBMs and one ASIC chip, was successfully fabricated and they determined that the electrical loss of RDL interposer was lower than Si interposer case. Mechanical simulation showed RDL interposer reduced joint stress by 34% compared to Si interposer. They predict that RDL interposer tech will become one of the most promising solutions for low cost and large size packages in the near future if "....fine patterning technology is developed below L/S 2/2μm." ↔

## The ConFab 2019 **Distinguished Opening Keynote**

## Dr. Jeffrey Welser, Vice President, IBM Research – Almaden

## May 14-17, 2019 at The Cosmopolitan of Las Vegas theconfab.com

Owned & Produced by: Extension

MEDIA

Presented by:

# Perfecting yield with proactive optimization throughout the process and across the supply chain

PRASAD BACHIRAJU, Rudolph Technologies, Inc., Wilmington, Mass.

Increasingly dispersed and complex supply chains require a proactive, integrated, systems-level approach to optimizing yields.

fter decades of R&D, two emerging memory types – the phase change memory-based 3D Xpoint, co-developed by Intel and Micron, and the embedded spin-torque transfer magnetic RAM (e-MRAM) from several foundries – are now coming to the market. One point of interest is that neither memory type relies on the charge-based SRAM and DRAM memory technologies that increasingly face difficult scaling challenges. Another is that both have inherent performance advantages that could extend their uses for decades to come.

As IC manufacturers adopt advanced packaging processes and heterogeneous, multi-chip integration schemes to feed ever-greater consumer demand for more computing power in smaller and smaller spaces, their supply chains have become increasingly complex. A fab-wide view of the process, not so long ago the holy grail of yield management systems, now seems quaintly inadequate. Critical processes that affect finished product yields now occur in different facilities running diverse processes at locations spread around the world. A packaged electronics module may combine microprocessors, memory, MEMS sensors and RF communications, all from different fabs and each with its own particular history. Optimizing yields from such a complicated supply chain requires access to individual component genealogy that includes detailed knowledge of process events, equipment malfunctions and operational parameters, and much more. The latest generation of yield optimization systems consolidates this data - tool deep and supply-chain wide - in a monolithic database, providing end-to-end, die-level traceability, from bare wafer to final module test. Specialized algorithms, designed for "big data" but based on intimate knowledge of semiconductor manufacturing processes, can find hidden correlations among parameters, events and conditions that guide engineers to the root causes of yield losses and ultimately deliver increased fab productivity, higher process yields, and more reliable products.

## **Proactive Yield Perfection**

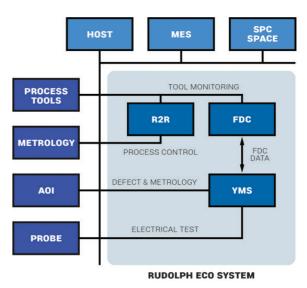

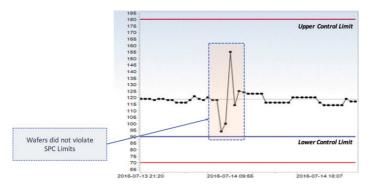

Proactive yield perfection (PYP) is a comprehensive systems-level approach to perfecting yield through detailed surveillance and sophisticated modeling that identifies actual or potential root causes of excursions and establishes monitoring mechanisms to anticipate and proactively address problems before they result in yield loss. PYP is a logical extension of long-standing yield management practices that comprehends the dispersal and growing complexity of the manufacturing process and combines information from conventional defect detection, yield analysis, automated process control, and fault detection and classification techniques. It addresses

FIGURE 1. The PYP ecosystem

two major obstacles identified within the industry: providing access to data across the fab and supply chain and integrating that data into device-level genealogy. PYP's ability to correct small problems early is increas-

ingly valuable in a complex supply chain where each step represents a considerable additional investment and a flawed finished module results in the costly loss of multiple component devices.

PYP collects data in a single database that integrates vital product parameter data from every die at each step in the process with performance and condition data from all tools, factories and providers in the supply chain. It provides unprecedented visibility of the entire manufacturing process from design, through wafer fab, test, assembly and packaging. Consolidating the data in a single, internally consistent database eliminates the considerable time often consumed in simply locating and aligning data stored in disparate databases at multiple facilities, and allows analytical routines to find correlations among widely separated observations that are otherwise invisible (FIGURE 1).

Genealogy incorporates traditional device-level traceability of every die, but also provides access to all information available from sensors on the tool (temperature, pressure), process events (e.g. lot-tolot changes and queue times), equipment events (e.g. alarms and preventive maintenance), changes in process configurations (e.g. specifications and recipes), and any other event or condition captured in the database for sophisticated analysis. Ready access

to device genealogy allows analysts to trace back from failed devices to find commonalities that identify root causes, and trace forward from causes and events to find other device at risk of failure.

## **Only from Conax Technologies**

EtchDefender<sup>™</sup> technology extends the life of quartz thermocouple sheaths in ASM<sup>®</sup> EPSILON<sup>®</sup> epitaxial reactors up to **3X longer and reduces your annual spend by 30%.**

+18002232389

conaxtechnologies.com/ss

ASM<sup>®</sup> and EPSILON<sup>®</sup> are registered trademarks of ASM<sup>®</sup> International. Neither Conax Technologies nor its products are affiliated with, approved by or sponsored by ASM<sup>®</sup> International.

**FIGURE 2.** Numerous locations worldwide feed information into a single big-data cluster where multiple software solutions operate on the pre-aligned and internally consistent data set.

## **Mobile communications**

YIELD

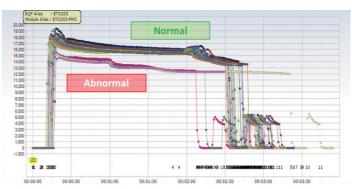

A leading global supplier of mobile communications products has implemented the full PYP suite across their supply chain (**FIGURE 2**), which includes three separately located front-end fabs, a fabless design facility, oursourced manufacturing (foundries), and outsourced assembly and test (OSAT). Finished modules integrate data processing, data storage, RF communications, power management, analog sensing, and other functions using multiple die and components fabricated at various facilities around the world. The PYP suite comprises fault detection and classification, yield management, defect detection and classification, and run-to-run automated process control, including configurable dashboard displays that provide

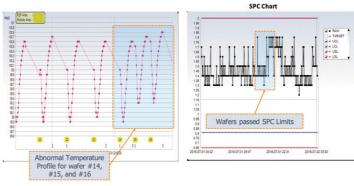

**FIGURE 4.** A potential loss of hundreds of thousands of dollars due to final test on panel (left) was traced back to over a thousand wafers. Through yield analysis, an SPR pattern signaled wafers with edge defect clusters (center). Finally, the root cause is understood through MES analysis (right).

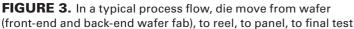

interactive drill-down reports and scheduled userdefinable reports. The process flow includes front-end wafer-based processing, with singulated die then transferred to tape and subsequently to rectangular panels for back-end processing (**FIGURE 3**).

In one instance (**FIGURE 4**), panel mounted die were failing in back-end processing, causing yield losses valued at hundreds of thousands of dollars. The failed die were traced back to over a thousand wafers, and analysis of those wafers, using spatial pattern recognition, revealed defect clusters near the wafer edges. Further analysis of

integrated MES (wafer process history) data traced the clusters to a defective tool that leaked etching solution onto wafers. Engineers are currently evaluating sensor data from the tool in an effort to identify a signal that will permit proactive intervention to prevent similar losses in the future.

In another case, failed die on panels in the back-end showed a characteristic "strip" signature (**FIGURE 5**). Tracing the die backward revealed a front-end a process issue with the failing die all originating from locations near the center of the wafer.

A final example from this manufacturer occurred in the back-end where die containing various filter technologies fabricated on a wafers of different sizes are combined on a panel substrate (**FIGURE 6**). In this case, the customer

**FIGURE 5.** The bad die (red strips) on the panel (left) were traced back the centers of the original wafers.

**FIGURE 5.** A single panel contains different filter components from multiple (differently-sized) wafers. Dielevel traceability allows engineers to relate final test results to inspection and metrology data collected during wafer processing. Die can be traced back to their individual location on the original wafer, permitting associations with location-specific data such as defect patterns discovered by SPR.

gained additional insights regarding the origin of the die being assembled and was able to evaluate how shifts in performance parameters impacted the final module product. This resulted in better matching of parts in the pre-assembly process and a tighter distribution of performance parameters in the outgoing modules.

## **Automotive electronics**

A leading global supplier of electronic systems to the automotive market manufactures finished modules containing multiple ICs from various suppliers and facilities. Highest reliability with component failure rates at parts-per-billion levels is an absolute requirement because the health and safety of millions of drivers may be jeopardized by a defective product. Limiting these risks, and the associated financial liability, through fast rootcause analysis of in-house test failures and field returns and rapid identification of process drift or step function changes are critical needs. Tuning the process to improve yields while preserving critical reliability is an equally important economic concern.

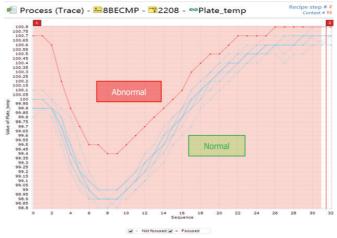

The final product is a multi-chip module containing microelectromechanical system (MEMS)-based sensors from one supplier and application-specific integrated circuits (ASIC) from another. These component parts are functionally tested prior to being send to an assembly facility where they are attached to a common carrier and packaged in a sealed module, which is then retested to verify functionality of the completed assembly. PYP

software collects data across the entire supply chain. Devices from a single wafer lot are ultimately split and mixed among many modules. Using a commonality analysis, engineers can quickly identify die that share a similar risk and track them to their ultimate dispositions in finished modules. The tracking is not limited to wafer level. For instance, it might be used to find only those die located on the straight-line extension of a known crack or within at-risk regions identified by spatial pattern recognition (SPR). Such information is critical in issuing a recall of at-risk parts.

In this case, die that were known-good at wafer test were failing after assembly. Tracing back to wafer level the customer determined that all affected modules were assembled within a short time period of one another. Further investigation found that the packaging process was affecting peak-to-peak voltage at final test. The customer was not able to modify the assembly process, but they were able to eliminate the final test losses by tuning wafer probe specifications to eliminate die at risk for damage in the assembly operation. Die-level traceability across the supply chain, which allowed engineers to quickly and easily compare data sets on the same dies from wafer probe and final test, was key to achieving this solution.

## Conclusion

Increasingly dispersed and complex supply chains require a proactive, integrated, systems-level approach to optimizing yields. PYP's ability to integrate data – sensordeep and supply chain-wide – in a monolithic database streamlines analysis and finds relationships that are otherwise invisible. Die-level genealogy allows engineers to trace die histories backward to find root causes of failures and forward to identify other die similarly at-risk. The value of PYP-based solutions is multiplied by the substantial investments made at each step of the process and the high cost and potential financial liability associated with failed, multi-chip modules.

PRASAD BACHIRAJU is Director, Customer Solutions, Rudolph Technologies, Inc., Wilmington, Mass. ◆

## **Delivering Real-world Solutions**

Nikon combines a strong history of engineering expertise with superior scanner technology and innovative alignment solutions to deliver exceptional manufacturing performance and productivity—now and for the future.

Nikon. Delivering Real-world Solutions.

See Nikon at SEMICON Europa 2018 - Visit booth A4706 to learn about the latest lithography solutions.

www.nikonprecision.com

# Emerging memories for the zettabyte era

GOURI SANKAR KAR and ARNAUD FURNEMONT, imec, Leuven, Belgium

The scaling of traditional memories such as SRAM, DRAM and Flash is no longer following the data growth rate, especially in terms of energy and speed.

Every day, even every second, we produce massive amounts of data. With an estimated annual data growth rate of 1.2 to 1.4x (source: IDC's Data Age 2025 study, March 2017), the amount of digital data produced in the world will soon exceed 100 zettabyte. To grasp the meaning of this number - we would need to fill a soccer field with terabyte solid state drives (SSDs) stacked 28 meter high if we would want to store all this data. The data are partly generated through well-known applications such as Amazon, YouTube, Facebook or Netflix. But emerging IoT applications will make a significant contribution as well. Examples are the autonomous car (accounting for 4,000GB of data per day), the smart building (>275GB per day, per building) and the smart city (>1000TB per day, per city). Huge amounts of bandwidth are required to transport all this data – from the application to an edge node, then to a base station, and then to a data center – a challenge that is tackled by 5G and optical fiber technologies. Throughout this data flow, stringent requirements will be imposed on memory and storage - in terms of density, bandwidth, cost and energy.

## Clever data mining, and reduced energy consumption

At some point in the flow of data transport, the generated data will need to be analyzed and converted into knowledge and wisdom by means of machine learning techniques. The exact point at which this will happen, will significantly impact the requirements on memory and storage. For example, if machine learning can be applied just after data generation, it can help relax the requirements. If, on the other hand, data is turned into wisdom later in the process, more raw data will need to be stored throughout the whole process.

The zettabyte era will also challenge the power that is consumed by the growing amount of data centers, for

processing, transporting and storing all the data. If we don't optimize the energy consumption for these operations, data centers worldwide may use almost 8000 terawatt-hours by 2030 (source: https://www. labs.hpe.com/next-next/energy). That's about the amount of electricity consumed by Europe, Africa and part of Asia today. In recent years, several technologies have been introduced in the data centers to address power and performance issues for storage, including, for example, the wide deployment of solid state drives since 2014, and the introduction of the first emerging memory technologies in 2017. But to be prepared for the zettabyte era, we will have to introduce novel non-volatile memories with unprecedented density and speed, and improved power consumption.

## The slowdown of today's memory roadmap

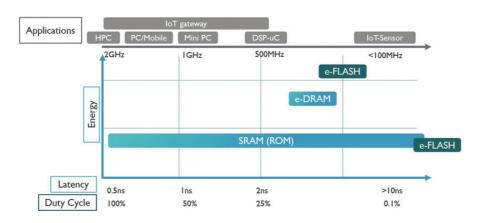

Let's have a closer look at today's memory landscape (**FIGURE 1**). Close to the central processing unit (CPU), fast, volatile embedded static random access memories (SRAMs) are the dominant memories. Also on chip are the higher cache memories, mostly made in SRAM or embedded dynamic random access memory (DRAM) technologies. Off-chip, further away from the CPU, you will mainly find DRAM chips for the working memory, non-volatile Flash NAND memory chips for storage, and tapes for long-term archival applications. In general, memories located further away from the CPU are cheaper, slower, denser and less volatile.

For half a century, Moore's Law has driven cost improvement of memory technologies, and this has translated into a continuous increase of the memory density. However, despite large improvements in memory density, only storage density (Flash NAND devices and tapes) has truly kept pace with the data growth rate. With the transition from NAND to 3D-NAND devices, density improvement for this storage class is however expected to slow down as well, and go below the data growth rate soon. Unlike in logic development – which has always been driven by improvements in cost and device physics – improving the power/performing benefits for memory has barely been taken care of. As a result, energy reduction and speed improvement are far from following up the data growth rate, for both memory and storage devices (**FIGURE 2**).

**FIGURE 1.** Application and performance space of the existing conventional memories (HPC = high performance computing; DSP = digital signal processing; ROM = read only memory; duty cycle = the proportion of time during which the memory device is operated).

|                  | ENERGY REDUCTION FOR A<br>GIVEN THROUGHPUT | DENSITY IMPROVEMENT                     | SPEED (AT DEVICE LEVEL)                     |

|------------------|--------------------------------------------|-----------------------------------------|---------------------------------------------|

| CACHE (SRAM)     | 1.12x                                      | 1.15x                                   | l.lx                                        |

| MEMORY (DRAM)    | I.IX<br>Cs reduction,Vdd reduction         | I.2X → I.1X<br>Slow down with C scaling | Ix                                          |

| STORAGE (FLASH)  | IX                                         | 1.4X → 1.2X<br>3D log trend cannot last | Ix<br>performance increase from 2D to<br>3D |

| ARCHIVAL (TAPES) | I.Ix                                       | 1.4X<br>Doubling at each LTO node       | I.Ix                                        |

**FIGURE 2.** Growth rates for the main memory roadmaps; (red) only storage density has kept pace with the data growth rate.

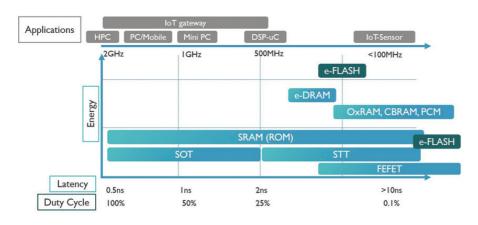

**FIGURE 3.** Memory research landscape at imec – application and performance space.

## **Emerging technologies to the rescue?**

To meet the memory requirements of the zettabyte era (i.e., improved density and speed, and reduced energy consumption), imec is exploring multiple emerging memory options, for standalone as well as for embedded applications (**FIGURE 3**). Options range from MRAM technologies for cache level applications, new ways for improving DRAM devices, emerging storage class

memories to fill the gap between DRAM and NAND technologies, solutions for improving 3D-NAND storage devices, and a revolutionary solution for archival type of applications. Below, we review their status and challenges, and investigate whether these emerging memory roadmaps can cope with the zettabyte world.

## MRAM technologies for embedded cache level applications

Spin transfer torque MRAM (STT-MRAM) technology has emerged as a candidate technology for replacing L3 cache embedded SRAM memories. It offers non-volatility, high density, high speed and low switching current. The core element of an STT-MRAM device is a magnetic tunnel junction in which a thin dielectric layer is sandwiched between a magnetic fixed layer and a magnetic free layer. Writing of the memory cell is performed by switching the magnetization for the free magnetic layer, by means of a current that is injected perpendicular into the magnetic tunnel junction.

Because of this geometry, the read and write operations are performed through the same path, and this challenges the reliability of the device. These reliability issues in combination with increased energy at sub-ns switching speeds make STT-MRAM memories unsuitable for replacing the faster L1/L2 cache SRAM memories.

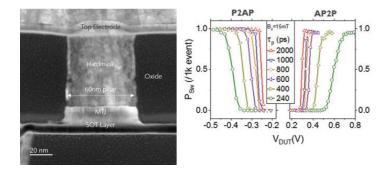

An MRAM variant, the spin orbit torque MRAM (SOT-MRAM), can overcome these issues. In these devices, switching the free magnetic layer is done by injecting an in-plane current in an adjacent SOT layer, as such de-coupling the read and write path and improving the device endurance and stability. Imec recently demonstrated the

**FIGURE 4.** (Left) SOT-MRAM device, and (right) SOT switching distribution as a function of pulse voltage for various pulse lengths.

ability to fabricate state-of-the-art SOT-MRAM devices on 300mm wafers using CMOS compatible processes (**FIGURE 4**). The devices exhibited an unlimited endurance (>5x1010), fast switching speed (240ps), and power consumption as low as 300pJ. We also explore ways for further reducing energy consumption, by bringing down switching current and demonstrating field-free switching.

## An imec view on DRAM scaling

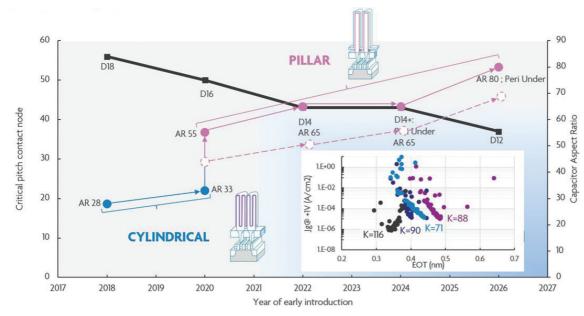

DRAM is structurally a very simple type of memory. A DRAM memory cell consists of one transistor and one capacitor, that can be either charged or discharged. Traditionally, double-sided cylindrical capacitor structures have been used, with a dielectric material contained inside as well as outside the capacitor structure. However, when spacing becomes smaller, we need to increase the aspect ratio of these structures - since a certain amount of capacitor area is needed to maintain the memory's performance. For very large aspect ratios, these DRAM structures are fabricated at the limits of mechanical stability. The industry may therefore transition to a new capacitor architecture: the high-aspect ratio one-pillar architecture, with the dielectric film now only on the outside (FIGURE 5). This change may make it possible to use thicker films of higher-k dielectrics, which in turn will allow reducing the aspect ratio of the one-pillar structure and improving leakage. A new dielectric with these specifications is currently under development at imec.

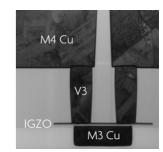

Further down the road, we are investigating if we can place the peripherical logic directly under the array of capacitors and transistors. This logic circuitry controls how data is moved to and from the memory chip, and typically consumes considerable area. Today, the transistor of the DRAM memory cell is however built on silicon. To be able to move the peri logic underneath the DRAM array, we need to replace this transistor with a non-Si transistor that is back-end compatible. At imec, we are moving towards a thin-film indium gallium zinc oxide (IGZO)-based transistor (**FIGURE 6**). This architecture is expected to give us one generation of Moore's law scaling. In addition, it will enable ultimate 3D DRAM integration as well.

#### **Emerging memory and selector concepts** for storage class memory

Storage class memory has been introduced to fill the gap between DRAM and NAND Flash memories in terms of latency, density, cost and performance. This new memory class should allow massive amounts of data to be accessed in a very short time. Most probably, more than one novel memory technology will be required to span the entire gap. The imec team explores several emerging technologies for storage class memory, including various crosspoint-based architectures for the memory element, such as phase-change-RAM (PC-RAM), vacancy-modulated conductive oxide (VMCO), conductive bridging RAM (CB-RAM) and oxide RAM (OxRAM). When it comes to high-density applications, all these memory elements require two-terminal selector elements that connect serially with each of the memory elements. These selector elements suppress the sneak currents that run through the unselected cells in the cross-point array during memory operation. Imec is developing GeSe-based ovonic threshold switching (OTS) selector devices that fulfill the requirements imposed by high-density storage class memories, including high thermal and electrical stability, high current density and low off-state current.

Close to the DRAM side of the DRAM-NAND gap, highdensity, high-speed MRAM offers an interesting, scalable alternative for the memory element. As this technology requires a selector as well, imec is working on a diodebased selector for this type of device. And finally, closer to the NAND Flash side, a ferroelectric memory based on hafnium-oxide (HfO) has gained interest. Compared to NAND-Flash, this emerging memory can operate at lower voltages and is much faster (with speeds down to 100ns). The easy cell structure can be fabricated with CMOS compatible processes and can be built in a 3D architecture.

## 3D NAND... and beyond?

Since its introduction several years ago, 3D NAND has become a mainstream storage technology because of its ability to significantly increase bit density. This is enabled by transitioning from 3 bits per cell to 4 bits per cell. And, instead of traditional x-y scaling in a horizontal plane, 3D NAND scales in the z direction by stacking multiple layers of NAND gates vertically. Today, stacking over 60 layers has become possible. However, increasing the numbers of layers challenges the deposition and etch

FIGURE 6. Novel oxide semiconductor based DRAM cell transistor.

**FIGURE 5.** An imec view on the DRAM scaling roadmap; inset: impact of the one-pillar capacitor architecture

processes. Also, the more layers that are stacked, the more stress evolves inside the layers, and this can cause a collapse of the 3D NAND pattern – a challenge that is tackled by imec. Imec also investigates alternative channel materials and processes – such as a silicon macaroni channel – that can overcome the limitations of the traditionally used poly-Si channels.

Despite all these advances, the density improvement of 3D NAND is expected to slow down and go below data growth rate soon. Therefore, the search for an emerging memory technology that is faster and cheaper than 3D NAND is ongoing. So far, there are no good candidates out there that can beat the 3D NAND density, especially because of the outstanding capability of 3D NAND Flash technology to integrate 3-4 bits per cell.

## DNA storage: the holy grail of archival storage?

Imagine that we could store all data of the world in a container the size of a car, and store them for a very long time? That is exactly what DNA storage promises. DNA can be kept stable for millions of years – today, it is still possible to extract DNA from the woolly mammoth – guaranteeing long term retention. DNA as a medium for storage is also extremely dense and compact. Writing can be performed by encoding binary data onto strands of DNA through the process of DNA synthesis. The DNA strand can be built up with the base pairs representing a specific letter sequence, through a series of deprotection and protection reactions. As from the read side, there is an enormous technology push to sequence DNA faster and faster and at lower cost. Progress in DNA sequencing has been amazing, even outpacing Moore's law. But researchers still have a long way to go before reasonable targets (1Gb/s) can be reached. To realize this, faster fluidics, faster chemical reactions and much higher parallelism are needed than what's possible today. At imec, we work towards faster write/read operation, and towards making DNA storage a cost-effective solution for long-term storage.

## Towards a sustainable zettabyte era

It has become clear that the classical memory roadmap cannot handle the zettabyte world in terms of energy, density, speed and cost. As shown above, imec is working on several emerging memory and storage technologies that can largely improve on density, system performance, and, partly, speed. However, energy consumption remains the biggest challenge towards a truly sustainable zettabyte era. And this highlights the need to continue collaborating with academia and industry on reduced energy consumption for memory technologies.

Talking about sustainability brings another aspect of the zettabyte era to mind: recycling. To be able to process and store all the data, massive amounts of devices will be produced. The advent of emerging technologies will also bring in new materials, which today are hardly recycled. To enable a truly sustainable zettabyte era, the semiconductor industry should therefore also find ways to improve the recyclability of all these materials.

GOURI SANKAR KAR is distinguished member technical staff emerging memories, and ARNAUD FURNEMONT is memory director at imec, Leuven, Belgium. MATERIALS

# There's still plenty of room at the bottom: Isotopically pure materials for when every atom counts

DR. PAUL STOCKMAN, Head of Market Development, Linde Electronics, Taipei, Taiwan

When different isotopes of atoms have significantly different properties, the ability to create isotopically pure materials becomes essential.

early 60 years after Richard Feynman delivered his celebrated talk, which became the foundation for nanotechnology [1], many of the milestones he envisioned have been achieved and surpassed. In particular, he discussed computing devices with wires 10 to 100 atoms in width. Today we are reaching the smaller end of that range for high-volume FinFET and 10nm class DRAM chips, and device manufacturers are confidently laying the roadmaps for generations of conductors with single atom scales.

While device shrinkage has continued apace, it has not been without consequences. As chip circuit dimensions dip into the atomic range, bulk semiconductor properties which allowed for relatively simple scaling are breaking down and atomic-level physics are beginning to dominate.

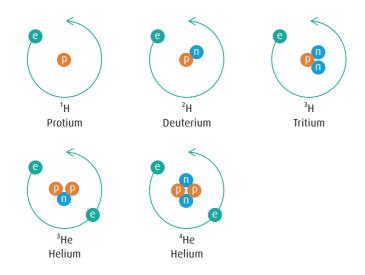

**FIGURE 1.** The stable isotopes of hydrogen and helium. The number of protons determines the element, and the number of neutrons determines the isotope. The superscript number is the sum of the protons and the neutrons.

At this scale, every atom counts. And when different isotopes of the needed atoms have significantly different properties, the ability to create isotopically pure materials (IPMs) becomes essential.

In this paper, we begin by discussing several examples of IPMs used in current high-volume electronics manufacturing: the physics at play and the materials selected. With the near future in focus, we then look at coming applications which may also require IPMs. Finally, we look at the current supply of IPM precursors, and how this needs to be developed in the future.

## What is an isotope?

Isotopes are atoms of a particular element which have the same number of protons in their nucleus, but different numbers of neutrons (**FIGURE 1**). The number of protons determines which element the atom is: hydrogen has one proton, helium has two protons, and so on in the ordering used for the periodic table.

Different isotopes of the same element all have nearly exact chemical behavior – that is how they form and break molecular bonds in chemical reactions – but sometimes exhibit significantly different physical behavior. It is these differences in physical behavior which become important when electronics are made on the atomic scale.

For the purposes of engineering semiconductors, it is important to consider two different classes of isotopes.

• **Radioactive:** The nuclei of these of these isotopes are unstable, break apart into different and lighter elements, and often emit radiation in the form of alpha particles or light. The rate at which this

happens can be quite fast – much less than a nanosecond – to longer than a billion years for half of the material to undergo decay. It is this type of isotope which was first historically observed and which we often first learn about. The element uranium has five different isotopes which naturally occur on earth, but all of these are radioactive.

• **Stable:** All other isotopes are termed stable. This means that they have not been observed to break apart, even once, when looking at bulk quantities of material with many billions of atoms. We do have evidence that some of these isotopes, termed primordial, are indeed stable over the span of knowable time, as we have evidence that they have formed and not decayed since the formation of the universe.

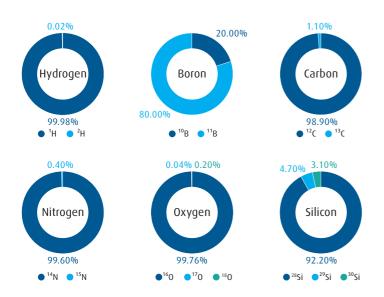

For the use of IPMs to engineer semiconductors, only stable isotopes are considered. Even for radioactive isotopes which decay slowly, the fact that current logic and memory chips have more than a billion transistors means that one or more circuits have the likelihood to be corrupted over the useful lifetime of the chip. In **FIGURE 2**, we show some common elements used in semiconductor manufacturing with their stable isotopes and naturally occurring abundances.

## **Current applications**

There are already several electronics applications for IPMs, which have been used in high volume for more than a decade.

**FIGURE 2.** The natural abundance of stable isotopes for elements most relevant for electronics devices.

**Deuterium** ( $D_2 = {}^2H_2$ ): Deuterium (D) is the second stable isotope of hydrogen, with one proton and one neutron. As a material, it is most commonly used in electronics manufacturing as the IPM precursor gas  $D_2$ . Chemically, deuterium can be substituted directly for any reaction using normally abundant hydrogen. Deuterium is made by the electrolysis of  $D_2O$ , often called heavy water, which has been already enriched in the deuterium isotope.

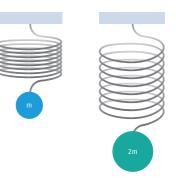

Important physical property – mass: For most elements, the difference in mass among their isotopes is only a few percent. However, for the lightest element hydrogen, there is a two-fold difference in mass. The chemical bond between a hydrogen atom and a heavier bulk material can be roughly approximated by the simple classical mechanics example of a weight at the end of the spring. When the weight is doubled, the force on the spring is also doubled (FIGURE 3).

**FIGURE 3.** According to Hooke's Law, a spring will stretch twice as far when attached to a mass twice the original. When the balls and springs are bonds to naturally abundant hydrogen <sup>1</sup>H and deuterium <sup>2</sup>H, they vibrate at different frequencies.

At the atomic level, quantum mechanics applies, and only certain amounts of energy, or quanta, can excite the spring. When deuterium  ${}^{2}$ H is substituted for the much more abundant  ${}^{1}$ H, the amount of energy which can excite the spring changes by almost 50%.

**Long-distance optical fibers:** Optical fibers, like semiconductors, rely on silicon oxide as a primary material. The fiber acts as a waveguide to contain and transmit bursts of near-infrared lasers along the length of the fiber. The surface of the silicon oxide fiber is covered with hydroxide (oxygen-hydrogen), which is formed during the manufacture of the fiber. Unfortunately, the hydroxide chemical bonds absorb small amounts of the laser light with every single reflection against the surface, which in turn diminishes the signal. By substituting deuterium <sup>2</sup>H for normally abundant hydrogen <sup>1</sup>H on the surface hydroxide, the hydroxide molecular spring no longer absorbs light at the frequencies used for communication.

**Hot carrier effect between gate and channel:** As transistor sizes decrease, the local electric fields inside transistors increase. When the local field is high enough, it can generate free electrons with high kinetic energy,

known as hot carriers. Gate oxides are often annealed in hydrogen to reduce the deleterious effects of these hot carriers. But the hydride bonds themselves can become points of failure because the hot carriers have just the right amount of energy to excite and even break the hydride bonds. Just like in the optical fiber application, substituting deuterium <sup>2</sup>H for naturally abundant <sup>1</sup>H changes the energy of the bond and protects it against hot carrier damage. The lifetimes of the devices are extended by a factor of 50 to 100.

**11-Boron trifluoride** (<sup>11</sup>**BF**<sub>3</sub>): Boron has two naturally occurring stable isotopes <sup>10</sup>B at 20% and <sup>11</sup>B at 80%. Boron is used in electronics manufacturing as a dopant for silicon to modify its semiconducting properties, and is most commonly supplied as the gases boron trifluoride (BF<sub>3</sub>) or diborane (B<sub>2</sub>H<sub>6</sub>). <sup>11</sup>BF<sub>3</sub> is produced by the distillation of naturally abundant BF<sub>3</sub>, and can be converted to other boron compounds like B<sub>2</sub>H<sub>6</sub>.

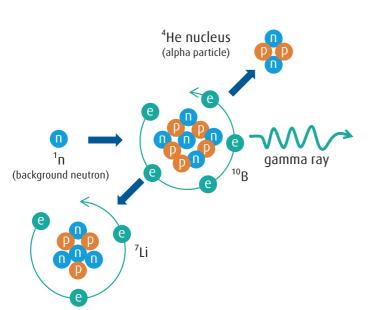

Important physical property - neutron capture:

The earth is continuously bombarded by high-energy cosmic radiation, which is produced primarily by events distant from our solar system. We are shielded from most of this radiation because it reacts with the molecules in our outer atmosphere. A by-product of this shielding mechanism are neutrons which constantly shower the earth's surface, but are not strong enough to pose any biological risk, usually passing through most materials without reaction. However, the nucleus of the <sup>10</sup>B atom is more than 1 million times likely to react with background neutrons versus other isotopes,

including <sup>11</sup>B. This results in splitting the <sup>10</sup>B atom into a <sup>7</sup>Li (lithium) atom and an alpha particle (helium nucleus) (**FIGURE 4**).

The smallest semiconductor gates now contain fewer than 100 dopant boron atoms. If even one of these is transmuted into a lithium atom, it can change the gate voltage and therefore the function of the transistor. Furthermore, the energetic alpha particle can cause additional damage. By using  $BF_3$  which is depleted of <sup>10</sup>B below 0.1%, semiconductor manufacturers can greatly reduce the risk for component failure.

Initially, IPMs  $\rm D_2$  and  $^{11}\rm BF_3$  were used for making chips with the most critical value, like high performance computing processors, or remote operating environments like satellites and space vehicles. Now, as chip dimensions shrink to single nanometers and transistors multiply into the billions, these IPMs are increasingly being adopted into more high volume manufacturing processes.

## **Developing and future applications**

As devices continue to scale to atomic dimensions and new device structures are developed to continue the progression of electronics advance, IPMs will play a greater role in a future where every atom counts. We present in this section a few of the nearest and most promising applications.

**FIGURE 4.** <sup>10</sup>B neutron capture. When a <sup>10</sup>B atom captures a background neutron, it breaks into a smaller <sup>7</sup>Li atom and emits alpha and gamma radiation.

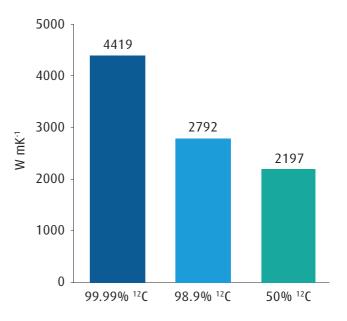

**FIGURE 5.** Thermal conductivity of graphene for different concentrations of <sup>12</sup>C content. 99.99% <sup>12</sup>C is achievable using commercial grade <sup>12</sup>CH<sub>4</sub> methane; 98.6% <sup>12</sup>C is the value of naturally abundant carbon on earth; 50% <sup>12</sup>C is an artificial mixture to demonstrate the trend. Source: Thermal conductivity of isotopically modified graphene. S Chen et al., Nature Materials volume 11, pages 203–207 (2012).

Important physical property – thermal conductivity:

Thermal conductivity is the property of materials to transfer heat, which is especially important in semiconductor chips where localized transistor temperatures can exceed 150 C and can affect the chip performance. Materials like carbon (either diamond or graphene) and copper have relatively high thermal conductivity; silicon and silicon nitride medium and oxides like silicon oxide and aluminum oxide are much lower. However, with all of the other design constraints and requirements, semiconductor engineers seldom choose materials to optimize thermal conductivity.

When viewed in classical mechanics, thermal conductivity is like a large set of balls and springs. In an atomically pure material like diamond or silicon, all the springs are the same, and all the balls are nearly the same – the differences being the different masses of the naturally occurring isotopes. When IPMs are used to make the material, all the balls are now exactly the same, there is less disorder, and heat is transferred through the matrix of balls and springs more efficiently. This has been demonstrated in graphene to improve the thermal conductivity at room temperature by 60% [**FIGURE 5**], and other studies have shown a similar magnitude improvement in silicon.

**Silicon epilayers:** Epitaxially grown silicon is often the starting substrate for CMOS manufacturing. This may be especially beneficial for HD-SOI applications where trade-offs of substrate cost vs processing cost and device performance are already part of the value equation.

**Sub 3nm 2D graphene FETs:** Graphene is a muchdiscussed material being considered for sub-3nm devices as the successor technology for logic circuits after the FinFET era. Isotopically pure graphene could reduce localized heating at the source.

**Important physical property – nuclear spin**: Each atomic nucleus has a quantum mechanical property associated with it called nuclear spin. Because it is a quantum mechanical property, nuclear spin is measured in discrete amounts, and in this case half-integer numbers. Nuclear spin is determined by the number of protons and neutrons. Since different isotopes have different numbers of neutrons, they also have different nuclear spin. An atomically and isotopically pure material will have atoms with all the same spin.

**Qubits and quantum computing:** Much research has been published recently about quantum computing as the successor to transistor-based processors. IBM and Intel, among others, have made demonstration devices, albeit not large enough for practical applications yet. The most promising near-term realization of quantum computing uses qubits – atomic two-state components—which store and transmit information via electron spin, which is a property analogous to nuclear spin, and can be affected by nuclear spin. Many of these early devices have been made with isotopically pure diamond (carbon) or silicon matrices to avoid disorder from having multiple values of nuclear spin in these devices.

**12-Methane** (<sup>12</sup>**CH**<sub>4</sub>): Carbon is predominantly <sup>12</sup>C, with about 1.1% <sup>13</sup>C in natural abundance. A large demand already exists for <sup>13</sup>C chemicals, primarily used as markers in studying chemical and biological reactions. <sup>13</sup>C is produced primarily by the distillation of carbon monoxide (CO), and then chemically converted to other carbon-containing precursors like methane (CH<sub>4</sub>). At the same time <sup>13</sup>C is produced, a large amount of <sup>13</sup>C-depleted <sup>12</sup>CO is produced, which serves as a less expensive feedstock for applications which require IPMs made from carbon.

**28-Silane** (<sup>28</sup>SiH<sub>4</sub>) and other silicon precursors: There are no such large applications driving the production of isotopically pure silicon precursors yet. Currently, research quantities of silicon tetrafluoride (SiF<sub>4</sub>) are produced primarily by using gas centrifuges, and then converted into silicon precursors like silicon tetrachloride (SiCl<sub>4</sub>), trichlorosilane (SiHCl<sub>3</sub>), dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>), and silane (SiH<sub>4</sub>). Distillation of one or more of these materials would be a less expensive option for larger-scale production.

Other IPM precursors already exist for oxygen and nitrogen compounds, and are relatively inexpensive because they are also by-products from the production of chemical markers for less abundant isotopes. Aluminum and phosphorous only have one stable isotope, and so all compounds produced with these are isotopically pure in these elements.

## **Production methods**

Production of IPMs is challenging because of the limited differences in physical and chemical properties normally used to separate and purify materials, and because of the low concentration of some of the desired isotopes. A number of creative approaches have been applied, and often the methods are repeated to obtain the desired enrichment and purity of the IPM. We give a description here of the two methods used today in the production of IPMs relevant to the electronics industry. Importantly, all of these require gas-phase starting materials in order to enhance the physical differences that do exist among the isotopes.

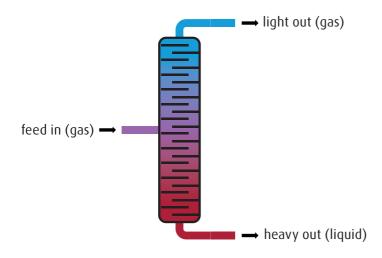

**FIGURE 6.** Isotope separation. Distillation. Gas is fed into the middle of the distillation column. By the process of condensation and boiling on many plates, the lighter isotope is separated as a gas leaving the top of the column, and the heavier isotope leaves as a liquid at the bottom.

**Distillation:** The more familiar of the two is distillation, which relies on differing boiling points of materials to separate them into lower boiling point fractions called *lights* (which often are lighter in mass) and higher boiling point fractions which are called *heavies*. Because the boiling point differences are a fraction of a degree, very long distillation columns are used. Distillation is best used with lighter compounds, and is the preferred method for producing  $D_2O$ , <sup>11</sup>BF<sub>3</sub>, <sup>12</sup>CO/<sup>13</sup>CO, and isotopes of nitrogen and oxygen (**FIGURE 6**).

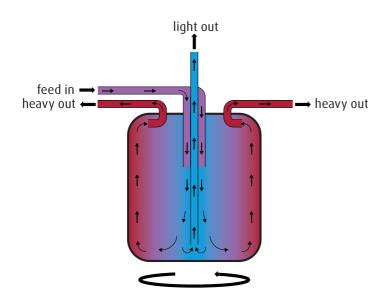

**FIGURE 7.** In this isotope separation centrifuge, gas is fed into the center of the centrifuge, which is spinning at a very high rate of 100,000 rpm. The heavier isotope is thrown to the sides, while the lighter isotope remains in the center.

**Centrifuge:** After a number of other methods were tried, gas centrifuges were the method ultimately chosen to scale the separation of the <sup>235</sup>U uranium isotope in uranium hexafluoride (UF<sub>6</sub>) gas used for the first atomic devices during the Manhattan Project, and remains the preferred method of obtaining this useful isotope and other isotopes of heavier elements. The gas is spun at very high speeds – around 100,000 rpm – and the higher mass isotopes tend toward the outer regions of the centrifuge. Many gas centrifuges are linked in arrays to achieve the desired level of enrichment. Currently, useful quantities of <sup>28</sup>SiF<sub>4</sub> and <sup>30</sup>SiF<sub>4</sub> are are produced with this method (**FIGURE 7**).

### Conclusion

In the hundred-year anniversary of Richard Feynman's birth, we are still finding plenty of room at the bottom. But as we go further down, we must look more carefully at what is there. Increasingly, we are seeing that individual atoms hold the properties that are important today and which will support the developments of a not-too-distant tomorrow. IPMs are an important part of creating that reality.

Linde Electronics is the leader in the production of IPMs which are important to electronics today, and holds the technology to produce the IPMs which will support the development of tomorrow's devices. Linde has made recent investments for the production of deuterium ( $D_2$ ) and  ${}^{11}BF_3$  to satisfy global electronics demand, and has a long history in the production, purification, and chemical synthesis of stable isotopes relevant to semiconductor manufacturing.

Dr. PAUL STOCKMAN is Head of Market Development, Linde Electronics, Taipei, Taiwan.

## Reference

Feynman, Richard P. (1960) There's Plenty of Room at the Bottom. Engineering and Science, 23 (5). pp. 22-36. ◆

# AI chips: Challenges and opportunities

PETE SINGER, Editor-in-Chief

To get to the next level in performance/Watt, innovations being researched at the AI chip level include low precision, analog and resistive computing.

he exploding use of Artificial Intelligence (AI) is ushering in a new era for semiconductor devices that will bring many new opportunities but also many challenges. Speaking at the AI Design Forum hosted by Applied Materials and SEMI during SEMICON West in July, Dr. John E. Kelly, III, Senior Vice President, Cognitive Solutions and IBM Research, talked about how AI will dramatically change the world. "This is an era of computing which is at a scale that will dwarf the previous era, in ways that will change all of our businesses and all of our industries, and all of our lives," he said. "This is the era that's going to power our semiconductor industry forward. The number of opportunities is enormous."

Also speaking at the event, Gary Dickerson, CEO of Applied Materials, said AI "needs innovation in the edge and in the cloud, in generating data on the edge, storing the data, and processing that data to unlock the value. At the same time Moore's Law is slowing." This creates the "perfect opportunity," he said.

Ajit Manocha, President and CEO of SEMI, calls it a "rebirth" of the semiconductor industry. "Artificial Intelligence is changing everything – and bringing semiconductors back into the deserved spotlight," he notes in a recent article. "AI's potential market of hundreds of zettabytes and trillions of dollars relies on new semiconductor architectures and compute platforms. Making these AI semiconductor engines will require a wildly innovative range of new materials, equipment, and design methodologies."

"Hardware is becoming sexy again," said Dickerson. "In the last 18 months there's been more money going into chip start ups than the previous 18 years." In addition to AI chips from traditional IC companies such as Intel and Qualcomm, more than 45 start-ups are working to develop new AI chips, with VC investments of more than \$1.5B — at least five of them have raised more than \$100 million from investors. Tech giants such as Google, Facebook, Microsoft, Amazon, Baidu and Alibaba are also developing AI chips.

Dickerson said having the winning AI chip 12 months ahead of anyone else could be a \$100 billion opportunity. "What we're driving inside of Applied Materials is speed and time to market. What is one month worth? What is one minute worth?"

IBM's Kelly said there's \$2 trillion of decision support opportunity for artificial intelligence on top of the existing \$1.5-2 billion information technology industry. "Literally every industry in the world is going to be impacted and transformed by this," he said.

## Al needed to analyze unstructured data

Speaking at an Applied Materials event late last year during the International Electron Devices Meeting, Dr. Jeff Welser, Vice President and Director of IBM Research's – Almaden lab, said the explosion in AI is being driven by the need to process vast amounts of unstructured data, noting that in just two days, we now generate as much data as was generated in total through 2003. "Somewhere around 2020, the estimate is maybe 50 zettabytes of data being produced. That's 21 zeros," he said.

Welser — who will be delivering the keynote talk at The ConFab 2019 in May — noted that 80% of all data is unstructured and growing 15 times the rate of structured data. "If you look at the growth, it's really in a whole different type of data. Voice data, social media data, which includes a lot of images, videos, audio and text, but very unstructured text," he said. And then there's data from IoT-connected sensors.

Custom hardware for AI is not new. "Even as early as the '90s, they were starting to play around with ASICS and FPGAs, trying to find ways to do this better," Welser said. Google's Tensor Processing Unit (TPU), introduced in 2016, for example, is a custom ASIC chip built specifically for machine learning applications, allowing the chip to be more tolerant of reduced computational precision, which means it requires fewer transistors per operation.