# Sold States TECHNOLOGY Insights for Electronics Manufacturing

Deep Learning Could Boost Yields, Increase Revenues

**P.** 20

First EUV Solution for 5nm

P. 24

Discovery of New PVD Chalcogenide Materials

P. 27

# FD-SOI Goes Mainstream PIZ

# HEIDENHAIN

## You're precisely where you should be

Engineers aren't like everyone else. Methodical yet wildly imaginative. Grounded in reality but endlessly optimistic. You see the world though a unique lens—and that's a beautiful thing. For decades, HEIDENHAIN has worked hand-in-hand with engineers like you toward unimaginable precision measurement and motion control innovations—reinvesting our profits into R&D to make it happen. Because your wildest design dreams call for the most disciplined commitment.

Visit HEIDENHAIN.us/imagine to learn more

# **Solid State TECHNOLOGY**

#### APRIL/MAY 2017 VOL. 60 NO. 3

FD-SOI is increasingly the de facto technology for many applications including entry-level application processors for smartphones, system-on-chip (SoC) devices for autonomous driving and IoT, and all mmWave applications such as 5G transceivers and radar systems for automotive electronics.

#### FEATURES

SILICON ON INSULATOR | FD-SOI: How a pioneering technology entered mainstream markets

With its unique characteristics, FD-SOI is generating increasingly strong interest from major players in the semiconductor ecosystem for a very wide range of markets. Manuel Sellier, Soitec, Bernin (Grenoble), France

**BIG DATA** | Deep learning could boost yields, increase revenues Deep learning is "a shiny new hammer" that chip industry may figure out how to use. *Dave Lammers, Contributing Editor*

**LITHOGRAPHY** | First EUV lithography high-volume manufacturing solution for N5 BEOL Immersion-based self-aligned quadruple patterning is combined with EUV lithography block patterning to achieve metal layers with pitches as small as 32nm. Joost Bekaert and Ming Mao, imec, Leuven, Belgium

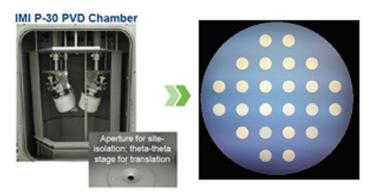

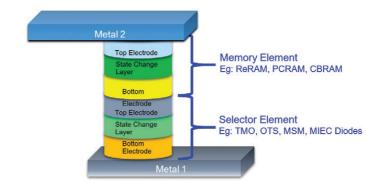

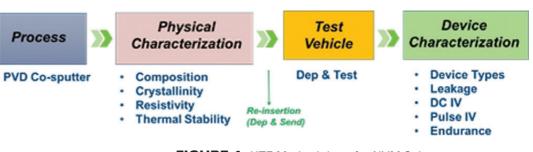

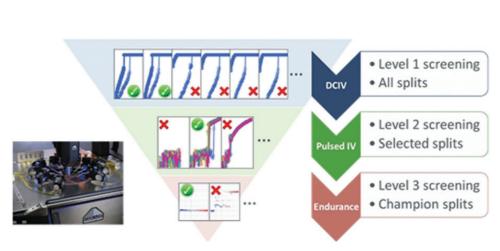

**MATERIALS** | Discovery of new PVD chalcogenide materials for memory applications A case study is presented based on the use of high throughput experimentation (HTE) for the discovery of new memory materials.

Larry Chen, Mark Clark, Charlene Chen, Susan Cheng and Milind Weling, IMI, Inc., San Jose, CA

#### COLUMNS

- 2 Editorial The ConFab preview Pete Singer, Editor-in-Chief

- **10 Packaging** New business models emerging, *Phil Garrou, Contributing Editor*

- **11 Semiconductors** Silicon photonics advances, *Ed Korczynski, Sr. Technical Editor*

- **32** Industry Forum MRAM lowers system power Barry Hoberman, CEO, Spin Transfer Technologies

#### DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 31 Ad Index

COVER

## editorial

# The ConFab Preview

The agenda is set for The ConFab, to be held May 14-17, 2017 in San Diego at the iconic Hotel del Coronado. While reviewing the abstracts for just the Monday morning session, it struck me how well our speakers will cover the complex opportunities and challenges facing the semiconductor industry.

In the opening keynote, for example, Hans Stork, Senior Vice President and Chief Technical Officer, ON Semiconductor we will discuss the challenge to realize high signal to noise ratio in small (read inexpensive) and efficient form factors, using examples of image sensors and power conversion in automotive applications. "It seems that at last, after many decades of exponential progress in logic and memory technologies, the "real world" devices of power handling and sensor functions are jointly enabling another wave of electronics progress in autonomously operating and interacting Things," he said.

Next, Subramani Kengeri, Vice President of CMOS Platforms Business Unit, GLOBALFOUNDRIES, will describe how the rapid growth of applications in the consumer, auto and mobile space coupled with the emergence of the Internet of Things (IoT) is driving the need for differentiated design and technology solutions. "While die-cost scaling is slowing down and power density is emerging as a major challenge, fabless semiconductor companies are hungry for innovation using application optimized technology solutions. Specifically, emerging SoC innovations are driving the need for low-power, performance, cost, and time-to-volume that solves the issues of voltage scaling and integration of "userexperience" functions," he notes. Islam Salama, a Director with Intel Corporation responsible for packaging substrate Pathfinding of the high-density interconnect across all Intel products, looks at it from a connectivity perspective. "The pervasive nature of computing drives a need for connecting billions of people and tens of billions of devices/things via cloud computing. Such connectivity effect will generate tremendous amounts of data and would require a revolutionary change in the technology infrastructures being used to transmit, store and analyze data," he said.

Next-generation electronics will require several new packaging solutions, he adds. Smaller form factors, lower power consumption, flexible designs, increased memory performance, and-more than ever, a closely managed silicon package, co-optimization and architectural innovations. Heterogeneous integration through package with technologies such as system in package (SIP), on package integration (OPI) and fan-out (WLFO and PLFO) are poised to change the packaging industry and play a disruptive role in enabling next generation devices.

Heterogeneous Integration is also the focus of a talk by Bill Bottoms, Chairman and CEO, Third Millennium Test Solutions. Bill will report on the collaboration in the making of the HIR Roadmap to address disruptive changes in the global IT network, the explosive growth coming for IoT sensors and the multi-sensor fusion and data analytics that extract "awareness" from the expanding data.

I'm very much looking forward to these and many other talks this year, and the exciting panel discussions and networking events we have planned.

-Pete Singer, Editor-in-Chief

## Solid State TECHNOLOGY.

Pete Singer, Editor-in-Chief Ph: 978.470.1806, psinger@extensionmedia.com

Shanon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor, edk@extensionmedia.com

Dave Lammers, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

CREATIVE/PRODUCTION/ONLINE LS Jerrett, Production Traffic Coordinator Nicky Jacobson, Senior Graphic Designer Simone Bradley, Graphic Designer Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION

Jenna Johnson, jjohnson@extensionmedia.com

#### **CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, Business Development msterling@extensionmedia.com

April/May 2017 VOL. 60 NO. 3 • Solid State Technology ©2016 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmaii: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343. (8 am – 5 pm, PST). For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2017 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

# SEMICON® VEST SMART STARTS HERE

# Disrupt or Disrupted? Make the SMART decision.

Uncertainty is racing across the extended microelectronics supply chain. Everything's in flux, but you have a choice: You can embrace disruption and participate in the transformation. Or, let the chips fall where they may. SEMICON West will get you where you need to be. Because this year, *Smart Starts Here*:

- SMART Programs and the Smartest Partners—Learn all about what's driving the industry forward with all-new programming focused on Smart Automotive, Smart Manufacturing, MedTech, IoT, and more. And get in the loop with advanced sessions from IEEE and SAE International.

- **Thought Leaders and Thoughtful Analysis** Hear from Intel, Cisco, NVIDIA, Qualcomm, and others about the latest breakthroughs, and from SEMI/Gartner and Bulls & Bears panelists about business prospects for what's ahead.

- **Ramped Up Experiences and Networking** Let the immersive, VR-driven SMART Journey take you on a hyper-visualized tour of tomorrow's innovations, then head over to the exclusive Summerfest at AT&T Park to catch the All-Star Game with colleagues and customers.

Smart Starts Here at SEMICON West 2017. So you should be here, too.

#### **Register Today – WWW.SEMICONWEST.ORG**

JULY 11-13, 2017 | MOSCONE CENTER | SAN FRANCISCO, CA

# Online@www.solid-state.com

### **Web Exclusives**

#### Lithographic stochastic limits on resolution

The physical and economic limits of Moore's Law are being approached as the commercial IC fab industry continues reducing device features to the atomic-scale. Early signs of such limits are seen when attempting to pattern the smallest possible features using lithography. Stochastic variation in the composition of the photoresist as well as in the number of incident photons combine to destroy determinism for the smallest devices in R&D. The most advanced Extreme Ultra-Violet (EUV) exposure tools from ASML cannot avoid this problem without reducing throughputs, and thereby increasing the cost of manufacturing.

http://bit.ly/2omsIAS

# The ConFab 2017 announces leading semiconductor industry keynotes

The ConFab 2017 is excited to welcome these distinguished Keynote speakers: Hans Stork, Senior Vice President and Chief Technical Officer at ON Semiconductor; Mohan Trivedi, Distinguished Professor of Electrical and Computer Engineering and founding director of the Computer Vision and Robotics Research Laboratory, as well as the Laboratory for Intelligent and Safe Automobiles at the University of California San Diego; Dr. Alissa Fitzgerald, Founder and Managing Member of A.M. Fitzgerald & Associates, and Bill McClean, President of IC Insights. http://bit.ly/2oDQt2b

#### Edge placement error control in multipatterning

SPIE Advanced Lithography remains the technical conference where the leading edge of minimum resolution patterning is explored, even though photolithography is now only part of the story. Leading OEMs continue to impress the industry with more productive ArFi steppers, but the photoresist suppliers and the purveyors of vacuum deposition and etch tools now provide most of the new value-add. Tri-layer-resist (TLR) stacks, specialty hard-masks and anti-reflective coatings (ARC), and complex thin-film depositions and etches all combine to create application-specific lithography solutions tuned to each critical mask. (From SemiMD.com) http://bit.ly/2miYPid

#### Insights from the Leading Edge: IMAPS DPC Part 1: New MIL Qualified Player in FOWLP

The annual IMAPS Device Packaging Workshop was held at its usual location outside Scottsdale, AZ in early March.

http://bit.ly/2oe043k

#### **Further thoughts from the 2017 SPIE AL EUV Lithography conference**

In the previous blog, I listed technology status and would now like to discuss a couple of topics in detail. During last year's SPIE AL conference, the message for EUVL was "Not If, but When." This year the message was "Not If, but When and How Much Volume." It was nice to see the technology that I bet on so long ago coming so far and doing so well.

http://bit.ly/2odTvh4

# How critical area analysis optimizes memory redundancy design

As any design engineer knows, the farther downstream a design goes, the less likely a manufacturing problem can be corrected without a costly and time-consuming redesign. And it doesn't matter if you are a fabless, fab-lite, or independent device manufacturer (IDM) company—reducing a design's sensitivity to manufacturing issues should ideally be handled by the design teams. By identifying and resolving design for manufacturing (DFM) problems while the design is still in its early stages, many manufacturing ramp-up issues can be avoided altogether. (From SemiMD.com) http://bit.ly/2nkuXPe

# EUVL masks may need to be tool-specific

Now we hear that EUVL might require fabs to park work-in-progress (WIP) lots of wafers behind a single critical tool with an idealistic 80% availability on a good day, and lots of downtime bad days. (From SemiMD.com) http://bit.ly/2omgFzb

MCENERY CONVENTION CENTER / SAN JOSE / CALIFORNIA

#### EXHIBIT DATES: JUNE 28-29, 2017

### The sensors industry is moving at lightning fast speed.

Experience this change firsthand at the industry's premier event for sensor technical training. The 2017 Sensors Expo & Conference will feature over three days of **Keynotes, Symposia, Case Studies, Technical Sessions, Hands-on Workshops, Networking Parties, and more.**

- EMERGING TECHNOLOGIES

- ENERGY HARVESTING & POWER

- FLEXIBLE & WEARABLES TECH

- S IOT & WIRELESS

- MEASUREMENT & DETECTION

- MEMS & SENSORS

- NOVEL SENSOR APPLICATIONS

- OPTICAL SENSING & DETECTION

- SENSOR DATA

- SENSORS & EMBEDDED SYSTEMS DESIGN

## <sup>°</sup>Overall, I found the Sensors Expo event a worthwhile and informative event, effectively structured to enable attendees a variety of experiences, from large keynotes, time to explore the exhibition, technical talks and networking time.<sup>°</sup> - LEO KENNY, PLANET SINGULAR

(0)

$\odot$

#### in f 🕑 🗹 🔊 www.sensorsexpo.com

OFFICIAL PUBLICATION:

INDUSTRY SPONSOR:

SENSORS EVENT

REGISTER

and join 6,000+ of your closest colleagues!

Use code EE100 when

registering for \$100 off a Gold or

Main Conference Pass!\*

Sensors

Extension MEDIA

Please send news articles to sdavis@extensionmedia.com

#### worldnews

EUROPE - Soitec and Silicon Genesis Corp. have successfully brought an end to the dispute regarding the importation and sale in the United States of certain SOI wafers.

USA - Intel announced that Omar Ishrak and Greg Smith have been elected to Intel's board of directors.

ASIA - Microsemi announced the planned closure of its manufacturing facility in China.

**USA** - Peregrine Semiconductor announced the acquisition of Arctic Sand Technologies.

#### ASIA - STATS ChipPAC

announced that it has shipped 1.5 billion fan-out wafer level packages (FOWLP), also known in the industry as embedded Wafer Level Ball Grid Array (eWLB).

USA - SEMI announced that it has moved its headquarters office to Milpitas, Calif.

ASIA - Over 60,000 were in attendance at the SEMICON China opening at Shanghai New International Expo Centre (SNIEC).

**EUROPE - EV Group (EVG)** unveiled the IQ Aligner NT-its latest and most advanced automated mask alignment system for highvolume advanced packaging applications.

USA - Kateeva announced that it is expanding its Silicon Valley headquarters, leasing an adjacent building at its Newark campus, adding 75,000 sq. ft. that is zoned for manufacturing and business operations.

ASIA - Soitec began the ramp up to high-volume production of 200mm silicon-on-insulator (SOI) wafers at the manufacturing facility of its Chinese partner Shanghai Simgui Technology Co., Ltd.

EUROPE - Imec announced that their 200mm gallium nitrideon-silicon (GaN-on-Si) e-mode power devices with a pGaN gate architecture showed no degradation after heavy ion and neutron irradiation.

## IC Insights more than doubles its 2017 IC market growth forecast

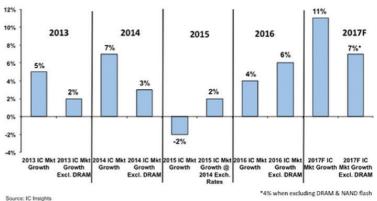

IC Insights has raised its worldwide IC market growth forecast for 2017 to 11%-more than twice its original 5% outlookbased on data shown in the March Update to the 20th anniversary 2017 edition of The McClean Report. The revision was necessary due to a substantial upgrade to the 2017 growth rates forecast for the DRAM and NAND flash memory markets.

39% and NAND flash sales to increase 25% this Moreover, NAND flash ASPs are forecast to year, with upside potential from those forecasts. rebound and jump 22% this year after falling DRAM market growth is expected to be driven by 1% last year. almost entirely by a huge 37% increase in the DRAM average selling price (ASP), as compared

Recent Major Impacts on Worldwide IC Market Growth (\$)

IC Insights currently expects DRAM sales to grow to 2016, when the DRAM ASP dropped by 12%.

Continued on page 9

#### Record spending for fab equipment expected in 2017 and 2018

report, revealing that fab equipment spending is strong product segments are Discretes (with expected to reach an industry all-time record - LED and Power), Logic, MEMS (with MEMS/RF), more than US\$46 billion in 2017. The record is and Analog/Mixed Signal. expected to be broken again in 2018, nearing the \$50 billion mark. These record-busting years are SEMI (www.semi.org) forecasts that China will part of three consecutive years of growth (2016, be third for regional spending in 2017, although 2017 and 2018), which has not occurred since the mid-1990s. The report has been the industry's 1 percent), as many of the new fab projects most trusted data source for 24 years, observing and analyzing spending, capacity, and technol- constructing 14 new fabs in 2017 and these new ogy changes for all front-end facilities worldwide. fabs will be equipping in 2018. China's annual

SEMI's World Fab Forecast report (end of percent (more than \$10 billion), and ranking February 2017) provides updates to 282 facili- in second place for worldwide spending in ties and lines equipping in 2017, 11 of which are expected to spend over \$1 billion each in 2017. In 2018, SEMI's data reflect 270 fabs to equip, with 12 facilities spending over \$1 billion each. The spending is mainly directed towards memory (3D \$10 billion.

SEMI announced updates to its World Fab Forecast NAND and DRAM), Foundry and MPU. Other

China's annual growth is minimal in 2017 (about are in the construction phase. China is busy spending growth rate in 2018 will be over 55 2018. In total for 2017, China is equipping 48 fabs, with equipment spending of \$6.7 billion; looking ahead to 2018, SEMI predicts that 49 fabs to be equipped, with spending of about

## Micron to establish its site for DRAM in Taiwan

Micron Technology, Inc., a developer of advanced semiconductor systems, announced that on March 14 it successfully won the auction for Cando Corporation assets, which will be utilized in establishing a back-end site for Micron Taiwan. Micron has now completed the title acquisition process for the new site.

The acquisition includes the cleanroom and tools that are adjacent to Micron's existing Taichung fab, bringing the company's fabrication and back-end together in one location. The new site will be focused on establishing a centralized back-end operation.

"This marks a significant step in our plan to create a center of excellence for leading-edge DRAM in Taiwan," said Wayne Allan, VP, Global Manufacturing. "Bringing fabrication and back end together, all in one location, builds an efficient support structure for end-to-end manufacturing with quicker cycle times that benefit our business and customers."

The new back-end site is expected to begin production in August, and the new integrated center of excellence is expected to bring greater operational cost efficiency that will benefit Micron's DRAM business on a global scale. These cost efficiencies are part of the overall US\$500 million of ongoing operational enhancement opportunities cited at the company's 2017 analyst conference.

The strategic acquisition, with a winning bid of US\$89.2 million, also highlights Micron's goal to grow its presence in Taiwan – where it is the largest foreign employer and investor – from its current wafer manufacturing function to a broader center of expertise in the global memory industry. The backend site will further enhance the company's strong presence on the island, which already includes 300mm wafer fabrication facilities in Taichung and Taoyuan, as well as sales and technical support offices in Taipei.

The back-end operation will be led by site director Mike Liang, who joined Micron in November 2016 with more than 35 years of experience in the semiconductor industry. Having previously served in leadership roles at Ti-Acer, KYEC and Amkor Taiwan, Liang brings significant expertise in both front-end wafer fabrication and back-end assembly and test manufacturing.  $\blacklozenge$

# **A4 SERIES**

#### Energy efficient dry multi-stage Roots process pumps for all semiconductor applications

- Low energy consumption

- Improved temperature management to optimize the pump according to your process

- Protection of the pump against precursor cracking or condensable deposition

- Corrosion resistant and high particle tolerance

- Extended monitoring functionalities

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com

# **news**cont.

#### **EUV lithography progress emphasized at SPIE Advanced Lithography**

New extreme-ultraviolet (EUV) lithography equipment unveiled by ASML, announcement by Intel of eight EUV programs ready to be rolled out, and introduction by IMEC of the industry's first comprehensive solution for EUVL-enabled high-volume manufacturing systems were among highlights at SPIE Advanced Lithography 2017 in San Jose earlier this month.

Sponsored by SPIE, the international society for optics and photonics, the annual event is the year's primary forum for the industry. Attendance was up this year over last, with nearly 2,300 participating, and ran 26 February through 2 March.

Speakers from ASML, Intel, KLA-Tencor, JSR Corp, IMEC, Samsung, and other organizations emphasized progress being made toward manufacturing computer chips using sub-10nm node lithography, sparking much discussion about when, where, and how — plus the occasional if the next generation of lithography tools will enable highvolume and high-throughput manufacturing at an EUV wavelength of about 13.5nm. Presentation recordings are viewable on the SPIE Newsroom on SPIE.org.

Product System Engineer Mark van de Kerkhof reported on ASML's NXE:3400B EUV scanner, which enables sub-10nmnode lithography — ASML's first scanner that can produce 125 wafers/hour, the throughput rate needed in production fabs.

With ever-smaller feature sizes being designed, mask makers must continuously advance their technologies as EUV sources and other lithography tools advance, noted plenary speaker Frank Abboud, Vice President of Technology and Manufacturing Group at Intel, and General Manager, Intel Mask Operation.

"Almost every module in the mask shop is touched," he said, including blank preparation, fiducial mark patterning, device patterning, black-border patterning, and metrology/ characterization."

Plenary speaker Ben Tsai, Chief Technology Officer and Executive Vice President of Corporate Alliances at KLA-Tencor, spoke on the return on investment of defect detection.

Inspection and metrology can involve 1,000 process steps for an advanced graphics processing unit, each requiring extremely high accuracy, he noted. In such a process model, if each step was 99.5% perfect, fewer than 1% of manufactured devices would work, illustrating the importance of investment in inspection and metrology to identify and resolve essentially all defects.

Starting with a vision of drivers for next-generation computing such as artificial intelligence (AI) and the computational power required, Nobu Koshiba, President and CEO of JSR Corporation, pointed out the extent to which the information explosion trending for years is continuing, with estimated data traffic in 2020 being 7x greater than in 2015.

The growth is stimulating Al advances, as are autonomous driving, precision medicine, genomic science, and cognitive computing, he said.

In a keynote talk, Philippe Leray, IMEC Group Leader of Advanced Metrology, described development of the first comprehensive solution for EUVL enablement in highvolume manufacturing. The approach serves as a basis for industry requirements for power, performance, area and cost, and includes proposals for design rules, masks, photoresists, etching, and metrology and an extensive process variation assessment, Leray said.

Donis Flagello, President, CEO, and COO of Nikon Research Corporation of America (NRCA), was presented with the 2017 Frits Zernike Award for Microlithography.

Semiconductor pioneer Burn Lin (National Tsin Hua University) was honored on the 30th anniversary of the Optical Microlithography conference in recognition of his serving as the first chair of the conference in 1988, and of his outstanding contributions to the lithography community. Lin was the founding editor of the SPIE Journal of Microlithography, Microfabrication, and Microsystems (JM3).

Six new Fellows of SPIE were recognized: Emily Gallagher (IMEC), Yuri Granik (Mentor Graphics), Qinghuang Lin (IBM Thomas J. Watson Research Center), David Pan (University of Texas, Austin), Mark Phillips (Intel Corp.), and James Thackarey (Dow Electronic Materials).

Bruce Smith, Rochester Institute of Technology, served as symposium chair, and Will Conley of Cymer, an ASML company, was symposium co-chair.

SPIE Advanced Lithography included seven conferences on lithographic topics, along with technical courses taught by experts from industry and academia, and a two-day exhibition.  $\triangleleft$

#### IC Insights, continued from page 6

The DRAM market started 2017 the way it ended 2016—with strong gains in DRAM ASP. In April 2016, the DRAM ASP was \$2.41 but rapidly increased to \$3.60 in January 2017, a 49% jump. A pickup in DRAM demand from PC suppliers during the second half of 2016 caused a significant spike in the ASP of PC DRAM. Currently, strengthening ASPs are also evident in the mobile DRAM market segment.

With total DRAM bit volume demand expected to increase by 30% this year and DRAM bit volume production capacity forecast to increase by 20%, IC Insights believes that quarterly DRAM ASPs could still surprise on the upside in 2017. Furthermore, DRAM output is also being slowed, at least temporarily, by the ongoing transition of DRAM production to  $\leq$ 20nm feature sizes by the major DRAM producers this year.

At \$57.3 billion, the DRAM market is forecast to be by far the largest IC product category in 2017, exceeding the expected MPU market for standard PCs and servers (\$47.1 billion) by \$10.2 billion this year. Figure 1 shows that the DRAM market has been both a significant tailwind (i.e., positive influence) and headwind (i.e., negative influence) on total worldwide IC market growth in three out of the past four years.

Spurred by a 12% decline in the DRAM ASP in 2016, the DRAM market slumped 8% last year. The DRAM segment became a headwind to worldwide IC market growth in 2016 instead of the tailwind it had been in 2013 and 2014. As shown, the DRAM market shaved two percentage points off of total IC industry growth last year. In contrast, the DRAM segment is forecast to have a positive impact of four percentage points on total IC market growth this year. It is interesting to note that the total IC market growth rate forecast for 2017, when excluding the DRAM and NAND flash markets, would be only 4%, about one-third of the current worldwide IC market growth rate forecast including these memory devices.

The March Update to the 2017 edition of The McClean Report further describes IC Insights' IC market forecast revision, updates its 2017-2021 semiconductor capital spending forecast, and shows the final 2016 top 10 OSAT company ranking.  $\blacklozenge$

# New business models emerging

Jim Walker, who retired from Gartner and is now consulting as World Level Packaging Concepts, gave a plenary talk at the recent IMAPS Device Packaging Conference in Scottsdale on the state of the semiconductor industry which contained some interesting perspectives on emerging new business models.

While Gartner 2020 projections show wireless and computer will still account for ~ 50% of the overall market activity, automotive, storage and industrial will show significant growth (7-9%) between now and then and account for ~ 30% of the total market (combined).

Gartner expects consolidation to continue "...with semi companies sitting on \$135B in cash and profit margins decreasing there is a need to diversify into new markets" with specifics including:

- IoT related M&A activity will drive consolidation in MCU, analog and sensor technologies.

- Companies will initiate sale of unprofitable divisions and product lines to prepare themselves for M&A (i.e., make themselves more attractive to be acquired).

- China will continue to buy or invest in U.S. and European companies, even as governments impose restrictions.

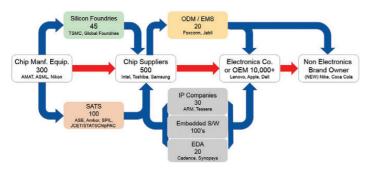

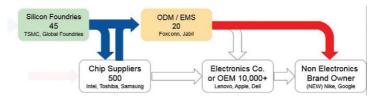

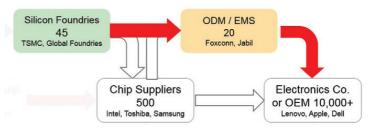

Gartner sees the industries maturation resulting in traditional business models changes. The traditional semiconductor ecosystem is shown in **FIGURE 1**.

FIGURE 1. The semiconductor ecosystem.

Gartner reports that a relatively new problem for some OEMs and Electronics Brands is that they are being bypassed by a direct relationship between the

ODM/EMS company and a nonelectronics brand owner buyer who could be in any industry. This model emerged with Operator

branded handsets, although those were recognizable as say Nokia or Motorola. This (Brand) Direct to ODM/EMS business model is good for chip suppliers but bad for traditional electronics companies (**FIGURE 2**).

PHIL GARROU, Contributing Editor

FIGURE 2. The Brand Direct model.

Another relatively new problem for some chip companies now is that they are being bypassed by a direct relationship between the foundry and the EMS/ ODM company and the OEM -- the OEM Direct model. These could be chips designed by Apple or Facebook (for example) and manufactured by TSMC (**FIGURE 3**).

FIGURE 3. The OEM Direct model.

Walker specifically suggests we keep an eye on Hon Hai/Foxconn which appears to be building strong and broad manufacturing capabilities through acquisitions such as Japan's Sharp (Feb 2016) and a bid on the Toshiba memory business (2017).

Packaging is currently ~17% (\$53B) of the \$265B electronics market. By 2020, 55% of all packaging is expected to be done at OSATS with foundries like TSMC (and maybe others soon) becoming competitors with their own wafer based packaging offerings like InFO. Walker sees a bright future for IoT packaging, but cautions that it is composed of many small to mid-sized applications, not one big one like the smart phone, and thus will require many custom packaging solutions.

# Silicon photonics advances

With rapidly increasing use of "cloud" client:server computing there is motivation to find cost-savings in the cloud hardware, which leads to R&D of improved photonics chips. Silicon photonics chips could reduce hardware costs compared to existing solutions based on indium-phosphide (InP) compound semiconductors, but only with improved devices and integration schemes. Now MIT researchers working within the US AIM Photonics program have shown important new silicon photonics properties. Meanwhile, GlobalFoundries has found a way to allow for automated passive alignment of optical fibers to silicon chips, and makes chips on 300-mm silicon wafers for improved performance at lower cost.

In a recent issue of Nature Photonics, MIT researchers present "Electric field-induced second-order nonlinear optical effects in silicon waveguides." They also report prototypes of two different silicon devices that exploit those nonlinearities: a modulator, which encodes data onto an optical beam, and a frequency doubler, a component vital to the development of lasers that can be precisely tuned to a range of different frequencies.

This work happened within the American Institute for Manufacturing Integrated Photonics (AIM Photonics) program, which brought government, industry, and academia together in R&D of photonics to better position the U.S. relative to global competition. Federal funding of \$110 million was combined with some \$500 million from AIM Photonics' consortium of state and local governments, manufacturing firms, universities, community colleges, and nonprofit organizations across the country. Michael Watts, an associate professor of electrical engineering and computer science at MIT, has led the technological innovation in silicon photonics.

"Now you can build a phase modulator that is not dependent on the free-carrier effect in silicon," says Michael Watts in an online interview. "The benefit there is that the free-carrier effect in silicon always has a phase and amplitude coupling. So whenever you change the carrier concentration, you're changing both the phase and the amplitude of the wave that's passing through it. With second-order nonlinearity, you break that coupling, so you can have a pure phase modulator. That's important for a lot of applications." The frequency doubler uses regions of p- and n-doped silicon arranged in regularly spaced bands perpendicular to an undoped silicon waveguide. The space between bands is tuned to a

ED KORCZYNSKI, Sr. Technical Editor

specific wavelength of light, such that a voltage across them doubles the frequency of the optical signal passing. Frequency doublers can be used as precise on-chip optical clocks and amplifiers, and as terahertz radiation sources for security applications.

At the start of the AIM Photonics program in 2015, MIT researchers had demonstrated light detectors built from efficient ring resonators that they could reduce the energy cost of transmitting a bit of information down to about a picojoule, or one-tenth of what all-electronic chips require. Jagdeep Shah, a researcher at the U.S. Department of Defense's Institute for Defense Analyses who initiated the program that sponsored the work said, "I think that the GlobalFoundries process was an industry-standard 45-nanometer design-rule process."

GlobalFoundries has found a way to automatically align twelve optical fibers to a silicon chip while the fibers are dark. Because the micron-scale fibers must be aligned with nanometer precision, default industry standard has been to expensively align actively lit fibers. Leveraging the company's work for Micro-Electro-Mechanical Sensors (MEMS) customers, GlobalFoundries uses an automated pick-and-place tool to push ribbons of multiple fibers into MEMS groves for the alignment. Ted Letavic, Global Foundries' senior fellow, said the edge coupling process was in production for a telecommunications application. Silicon photonics may find first applications for very high bandwidth, mid- to long-distance transmission (30 meters to 80 kilometers), where spectral efficiency is the key driver according to Letavic.

GobalFoundries has now transferred its monolithic process from 200mm to 300mm-diameter silicon wafers, to achieve both cost-reduction and improved device performance. The 300mm fab lines feature higher-N.A. immersion lithography tools which provide better overlay and line width roughness (LWR). Because the of the extreme sensitivity of optical coupling to the physical geometry of light-guides, improving the patterning fidelity by nanometers can reduce transmission losses by 3X. ◆

#### Semiconductors

www.solid-state.com

# FD-SOI: How a pioneering technology entered mainstream markets

MANUEL SELLIER, Soitec, Bernin (Grenoble), France

With its unique characteristics, FD-SOI is generating increasingly strong interest from major players in the semiconductor ecosystem for a very wide range of markets.

ully depleted silicon-on-insulator or FD-SOI is the only technology bringing together two substantial characteristics of CMOS transistors: 2D planar transistor structure and fully depleted operation. It relies on a unique substrate whose layer thicknesses are controlled at the atomic scale. FD-SOI offers remarkable transistor performance with one of the best power, performance, area and cost tradeoffs (PPAC) among all advanced CMOS technologies. In addition, FD-SOI has numerous other unique advantages including back bias ability, very good transistor matching, near threshold supply capability, ultra-low sensitivity to radiation and very high intrinsic transistor speed, which allows it to handle mmWave frequencies.

All these key features are progressively making FD-SOI a de facto technology for many applications including entrylevel application processors for smartphones, system-onchip (SoC) devices for autonomous driving and IoT, and all mmWave applications such as 5G transceivers and radar systems for automotive electronics.

FD-SOI technology is supported by multiple foundries and IDMs with full technology offerings now available for the 28nm and 22nm nodes and emerging for the 65nm and 12nm nodes. With this global ecosystem in place, FD-SOI is ready for applications development for diversified markets.

There are several striking characteristics of FD-SOI substrates that give this technology unique advantages. This article summarizes the latest advances and the various elements of the global ecosystem that support

widespread implementation of FD-SOI as well as the applications that most benefit from it.

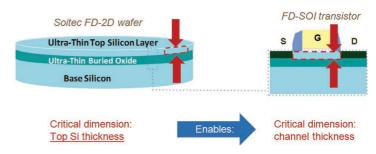

#### The heart of FD-SOI

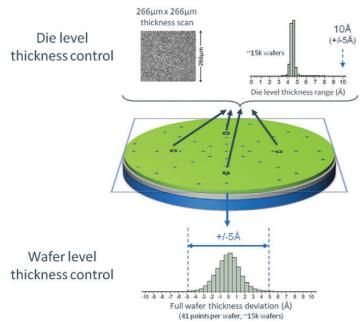

Everything in FD-SOI technology starts with the substrate. The substrate directly defines the transistor architecture, as shown in **FIGURE 1**. To allow the fully depleted operation of transistors, the thickness of the top silicon layer defining the device channel represents a real challenge, with the thickness target typically around 60 Å or 11 atomic layers. Given the consumption of silicon material during device fabrication, a 120 Å incoming top silicon specification is usually required by foundries. Uniformity is another very challenging specification needed to keep transistor variability as low as possible. Uniformity of +/-5 Å or 1 atomic layer is typically considered essential. Buried oxide (BOx) thickness also must be very thin - around 20nm - to maximize electrostatic control in the transistor channel due to the ground plane effect.

**FIGURE 1.** Transistor channel thickness is directly linked to top silicon SOI layer definition.

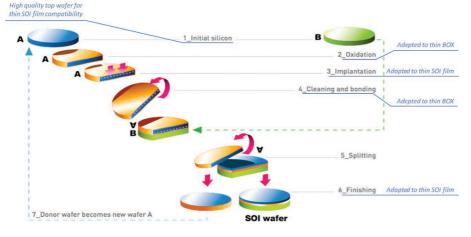

FIGURE 2. Smart Cut process and its adaptation to FD-SOI.

Manufacturing a 300mm piece of crystalline silicon with a thickness specification as low as 11 +/-1 atomic layers is understandably difficult. Ten years ago, it sounded unachievable so people studied other paths to enable fully depleted transistors [1]. But it is now possible.

Fabrication relies on the well-known Smart Cut TM process (**FIGURE 2**). As shown, wafer A first undergoes

an oxidation step followed by high-dose ion implantation, creating a weakened layer just beneath the surface. After careful cleaning steps, wafer A is bonded to wafer B through molecular-bonding technology. Splitting is then induced at the precise location of the weakened zone of wafer A. Finally, the formed SOI wafer is subjected to other smoothing process steps to achieve the targeted thickness specification. It is noteworthy that highquality wafer A can be recycled for further reuse, making Smart Cut the most costeffective solution for SOI manufacturing.

The FD-SOI substrate-manufacturing process is now fully mature. In particular, thickness uniformity is very well controlled at all levels, from transistor to wafer, as shown in **FIGURE 3**. This ensures a very low level of transistor variability.

#### When less is more

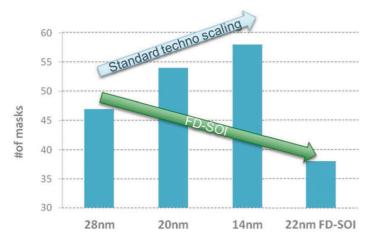

The way of getting more performance out of silicon below 28nm node adds more complexity to the

**FIGURE 3.** FD-SOI thickness is controlled at all levels - from die to wafer.

manufacturing process. Consequently, as illustrated in **FIGURE 4**, the smaller nodes get, the greater number of masks are needed to create chips. This increases manufacturing costs as well as other non-recurring engineering costs including design flow, design verification, mask sets and more.

On the other hand, FD-SOI is a simple technology from a manufacturing standpoint. In fact, it offers more performance while decreasing the manufacturing process complexity. Most of the channel engineering work is actually done directly at the substrate level, making FD-SOI easier to implement than bulk silicon, as major foundries have reported [2] [3].

**FIGURE 4.** Number of masks required per technology node (from [2]).

#### The next level of transistor performance

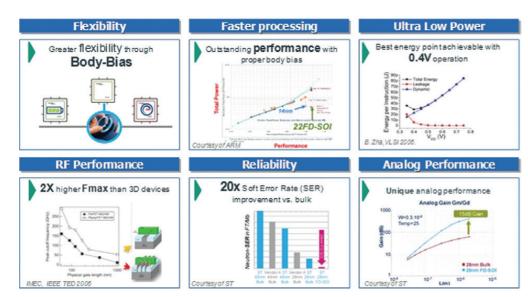

In addition to simpler manufacturing, FD-SOI offers other substantial benefits, as depicted below and summarized in **FIGURE 5**.

1. Better design flexibility through body bias

The thin BOx of FD-SOI not only enhances electrostatic control of the channel, but also makes it possible to completely tune the threshold voltage through back biasing. All the complex Vth adjustment techniques through channel doping can be avoided. Low, mid-range and high Vth can be achieved simply through back-gate polarization. The thin BOx behaves like a real second gate and, most importantly, it can be used dynamically. This means that the same functional block can operate under high or low power, on demand. Back bias potential is huge: selective body bias for critical path improvements [4], process variation compensation [5] and reliability drift compensation [6]. Full back biasing is a very unique feature, only achievable with SOI on thin BOx technology.

2. Power-performance-area-cost tradeoff: Best PPAC of all planar technologies

Thanks to simpler manufacturing, better control of random mismatch, minimizing of junction leakage and capacitances, enhanced electrostatic control through fully depleted transistor operation and the possibility of tuning body bias, FD-SOI technology presents the best powerperformance-area-cost tradeoff (PPAC) among all planar technologies.

#### 3. Ultra-low power through near-threshold supply voltage

Almost all CMOS technologies achieve their best energy efficiency – i.e., the lowest amount of energy per function, regardless of the frequency – at around 0.4 V supply voltage, often referred to as Vdd [7]. At this level of supply voltage, variability management is a real challenge. Thanks to body bias and to its intrinsic low-variability characteristics, FD-SOI can achieve very low supply voltages. More generally, the ability to lower the supply voltage, although not necessarily as low as 0.4 V, is a real challenge in many applications in which power is a greater challenge than performance. Given the fact that dynamic power scales with Vdd<sup>2</sup>, a technology like FD-SOI that is capable of strong power savings through tremendous supply voltage reduction presents a unique advantage.

4. Best RF-CMOS technology with almost 2 times maximum frequency over 3D devices

FIGURE 5. Benefits of using FD-SO [4] [7] [9] [10].

Integrating as many analog/RF functions as possible into a single RF-CMOS silicon platform is becoming an increasingly important issue in many markets for obvious cost and power reasons. However, one limitation of RF-CMOS platforms is the limited ability to increase frequency, especially in the mmWave spectrum (30 GHz and above). This is a bigger issue with 3D devices such as FinFETs, which must carry very strong parasitic capacitances due to their 3D structures [8]. As a result, SiGe-Bipolar platforms are often used for this frequency range. FD-SOI is a planar technology and, as such, it should not suffer from the limitations of 3D devices. Ft/Fmax in the range of 325-350 GHz have been reported [3], allowing full usage of the mmWave spectrum up to 100 GHz and giving FD-SOI RF-CMOS platforms a bright future in many applications.

#### 5. Enhanced reliability

Low sensitivity to high-energy particles is another key characteristic of FD-SOI. High-energy particles can interact with silicon and generate a significant amount of charges capable of flipping transistor logic state, thus increasing the soft errors rate (SER). FD-SOI devices are completely isolated from the substrate due to the BOx layer. This means that any charge generated in the substrate is unlikely to modify the device logic state. In short, FD-SOI is much less sensitive to SER [9]. This has very important consequences for safety-critical devices such as autonomous car systems.

#### 6. Outstanding analog transistor characteristics

Often, analog designers have to make their designs work with more and more degraded transistors as

technology shrinks. Meeting speed, noise, power, leakage and variability requirements is increasingly challenging. By providing a transistor with improved matching, gain and parasitic, FD-SOI can greatly simplify device design [10].Moreover, the back bias has potential for the design of many new analog structures [11].

# FD-SOI's growing use at foundries

Some of the most pioneering work with FD-SOI has been done at

semiconductor foundries around the world.

STMicroelectronics adopted FD-SOI technology in 2012 [12] and started several projects. The company demonstrated an ARM-based application processor for smartphones with 3 GHz+ operating frequency on 28nm FD-SOI

+18002232389

[13]. The technology is now used at STMicroelectronics for many diversified markets [14] [15].

In 2014, Samsung announced the adoption of 28nm FD-SOI technology for its foundry division [15]. Mass production maturity was reached in 2016 [2], and the first product release was announced recently [16] [17].

In 2015, GLOBALFOUNDRIES developed a 22nm FD-SOI technology called 22FDX [18], which it positioned as offering the best performance/cost ratio. This FD-SOI technology platform achieved performance close to 16nm/14nm FinFET at a cost similar to 28nm bulk silicon [19]. The first commercial product was announced in February 2017 by GLOBALFOUNDRIES and Dream Chip Technologies [20]. GLOBALFOUNDRIES' technology is now almost fully qualified, with volume ramp-up expected this year.

In Asia, the Chinese foundry Huali has announced its intention to include 22nm FD-SOI technology in its fab2 plan [21], offering the Chinese market greater access to FD-SOI technology.

In Japan, Renesas' experience with FD-SOI includes work on a very low-power FD-SOI technology called siliconon-thin-BOx (SOTB), which targets low-power MCU markets. This technology has been supported by the LEAP initiative (Low-Power Electronics Association and Project) and is now available in 65nm. Renesas has reported very low-power consumption with this platform, as small as a tenth of that achieved using bulk silicon.

#### **IP/CAD** status and roadmap

The design ecosystem is well established for 28nm FD-SOI with complete libraries and foundation IP and growing at a fast pace for 22nm technology. EDA companies are on board and developing IP ported to FD-SOI.

In September 2016, GLOBALFOUNDRIES announced a new partner program called FDXcelerator<sup>™</sup> to facilitate 22FDX SoC design and reduce time to market for its customers including Synopsys, Cadence, INVECAS, VeriSilicon, CEA-Leti, Dream Chip and Encore Semi [22]. In December 2016, the foundry announced the addition of eight new partners to its growing FDXcelerator program including Advanced Semiconductor Engineering (ASE Group), Amkor Technology, Infosys, Mentor Graphics, Rambus, Sasken, Sonics and Quick-Logic [23].

As for the technology roadmap, FD-SOI is available on a wide range of technology nodes from 65nm to 12nm with visibility down to 7nm. Building on the success of its 22FDX offering, in 2016 GLOBALFOUNDRIES unveiled a new 12nm FD-SOI semiconductor technology called 12FDX [24]. Staying with fully depleted planar processing allows the foundry to take advantage of the low parasitic capacitance, avoid the complex lithography steps required by equivalent 3D transistors, and leverage back biasing to boost transistor performance, especially at low supply voltages. Customer product tape-outs are expected to begin by the end of 2017.

Leti, which pioneered FD-SOI development 15 years ago, worked with GLOBALFOUNDRIES on the 22FDX and 12FDX platforms. The organization recently developed test devices on 10nm FD-SOI technology and produced models for 10nm and 7nm on FD-SOI. Leti strongly believes that FD-SOI can be scaled down to 7nm.

Both Samsung and GLOBALFOUNDRIES plan to have embedded non-volatile memory integrated into their FD-SOI technology platforms by 2018 [2] [3].

# FD-SOI traction in power and analog/RF integration

Thanks to the growing maturity of the FD-SOI ecosystem, there is now a wide range of applications seeing strong differentiation possibilities through FD-SOI. These include single-chip solutions for entry-level mobile communications, general purpose application processors, image signal processors, SoC for set-top boxes, embedded computer vision, microcontrollers, mixed-signal applications such as transceivers, GPS/satellite receivers, wi-fi/ BT combos and mmWave radar systems.

For all these applications, power budget is typically very limited and must be balanced with performance targets. A good example of this can be found in embedded computing applications such as ADAS, where designers must constantly find compromises to achieve the required performance with a very limited power budget, typically around 3 W. For all embedded computing applications, FD-SOI - and its ability to run on very low supply voltages - is gaining momentum as the reference technology.

In addition, RF/analog integration is often key for these applications. Having best-in-class RF-CMOS technology available on the same silicon die as the digital parts is a unique advantage of FD-SOI. It opens up possibilities for single-chip solutions covering a wide range of functions. This is particularly advantageous in entry-level markets such as low-end mobile, where the price pressure is so great that integration must be pushed to its limits, or in mmWave applications including radar and 5G transceivers,

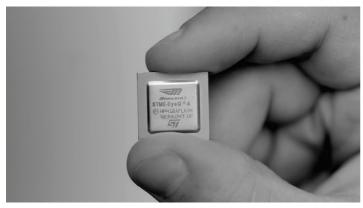

**FIGURE 6.** Huami Amazfit smartwatch with FD-SOI-based GPS inside.

**FIGURE 7.** Mobileye EyeQ4 chip dedicated to ADAS autonomous level3 applications (http://www.mobileye.com/).

where the mmWave RF functions can be integrated on the same die as the computing functions.

#### A new wave of ground-breaking products

The list of FD-SOI-based products is increasing at a very fast pace, with multiple product announcements over the past months.

In September 2016, Huami (a Xiaomi partner company) introduced a new fitness smartwatch that includes a FD-SOI-based global positioning system (GPS) chip demonstrating record energy efficiency (**FIGURE 6**) [25]. The chip allows the watch to reach an unsurpassed battery life of 35 hours with the GPS turned on, which represents two to five times more than today's similar devices. The chip, revealed in February 2016 at the International Solid-State Circuits Conference (ISSCC) in San Francisco [27], dramatically lowers power usage and opens the door for always-on GPS applications in smartwatches, smartphones, drones and a large number of devices for the IoT.

FIGURE 8. i.MX processor roadmap (courtesy of NXP).

Also in 2016, Mobileye posted on its website that its next EyeQ4 product family dedicated to level3 autonomous driving will be based on FD-SOI technology [26] (**FIGURE 7**).

In March 2017, NXP released two general-purpose processor families (i.MX7ULP and i.M8X) [16] [17] based on Samsung's 28FDS FD-SOI technology for ultra-low

+18002232389

power consumption and rich graphics in battery-powered applications (see NXP roadmap **FIGURE 8**). NXP reported a deep-sleep suspended power consumption of 15  $\mu$ W or less for its i.MX7ULP product, 17 times less in comparison to previous low-power bulk devices, while the dynamic power efficiency improved by 50 percent. This high-performance, low-power solution is optimized for customers developing IoT, home control, wearable and other applications that spend a significant amount of time in standby mode with short bursts of performance-intense activity that require exceptional graphics processing.

In March 2017, Eutelsat Communications and STMicroelectronics announced a new-generation SoC for interactive applications that represents a step down in the overall cost of interactive satellite terminals while reducing

**FIGURE 9.** Dream Chip Technologies' first 22nm FD-SOI product dedicated to ADAS (courtesy of Dream Chip)

power consumption [14].

On the 22nm side, Dream Chip announced the industry's first 22nm FD-SOI product for a new ADAS SoC for automotive computer-vision applications [20]. The SoC device (**FIGURE 9**) offers highperformance image acqui-

sition and processing capabilities and supports convolutional neural network (CNN) vision workloads to meet the demand for complex automotive object detection and processing.

The 22nm FD-SOI product portfolio is expected to grow significantly in the coming year as the technology ramps up.

#### Adding fabs to meet overall FD-SOI demand

Faced with the growing interest of FD-SOI, particularly in China, foundries are organizing themselves to build up enough production capacity. In February 2017, GLOBAL-FOUNDRIES announced plans to expand the capacity of its Fab 1 facility in Dresden by 40 percent by 2020. Dresden will continue to be the center for FDX technology development [27].

In China, GLOBALFOUNDRIES and the Chengdu municipality have announced a partnership to build a fab. The partners plan to establish a 300mm fab to support the growth of the Chinese semiconductor market and to meet accelerating global customer demand for 22FDX [27]. The fab will begin producing mainstream process technologies in 2018 and then focus on manufacturing GLOBALFOUNDRIES' commercially available 22FDX process technology, with volume production expected to start in 2019.

With these two announcements, GLOBALFOUNDRIES will have a future production capacity of more than 2 million FD-SOI wafers per year.

Regarding FD-SOI substrate manufacturing capacity, Soitec owns one 300mm fab in France and has another one in Singapore (currently in standby mode) with a combined global capacity of 1.5 million wafers per year (for manufacturing FD-SOI and other emerging SOI products). The company has plans to go beyond that to meet additional customer demand.

#### Conclusion

Growing interest in FD-SOI reflects today's new paradigm for semiconductor technologies. Customers are demanding for more computing capability with drastically reduced power consumption, enabled by enhanced analog/RF integration. With its unique characteristics, FD-SOI is generating increasingly strong interest from major players in the semiconductor ecosystem for a very wide range of markets, especially for embedded computing applications. FD-SOI is now a mainstream technology, which device designers are leveraging for key competitive advantages.

#### **Acknowledgements**

The author would like to warmly thank the Soitec team (Christophe Maleville, Bich-Yen Nguyen, Thomas Piliszczuk, Alexandra Givert, and Camille Dufour) for their valuable contribution and constructive discussions.

#### References

- H. Chenming, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," IEEE Transactions on Electron Devices, p. 2320–2325, December 2000.

- 2. Y. Jeon (SAMSUNG), "The industry's first mass-produced FD-SOI technology for the IoT era, with single design platform benefits," in SOI Industry Consortium workshop, Tokyo, 2016.

- 3. J. Schaeffer (GLOBALFOUNDRIES), "FDX Rising," in GLOBAL-FOUNDRIES Technology Conference, San Jose, 2016.

- 4. W. Abbey (ARM), "Realize the potential of FD-SOI," in SOI Industry Consortium workshop, San Jose, 2016.

- P. Flatresse (ST), "FD-SOI ULV, Body Biasing & Demonstrators," in LETI days FDSOICE Workshop, GRENOBLE, 2015.

- C. Ndiaye (ST), "Performance vs. reliability adaptive body bias scheme in 28nm & 14nm UTBB FD-SOI nodes," Microelectronics Reliability, 2016.

- 7. B. Zha, in VLSI symposium, 2006.

- 8. IMEC, chez VLSI Design, 2010.

- 9. P. Roche (ST), "Technology downscaling worsening radiation effects in bulk: SOI to the rescue," in IEDM, 2013.

- G. Cesana (ST), "Advances in Applications and Ecosystem for the FD-SOI Technology," in LETI days FDSOICE Workshop, GRENOBLE, 2015.

- A. Cathelin (ST), "On the usage of FBB for inverter-based Analog and RF 28nm UTBB FD-SOI circuits : example of a 450MHz Gm-C filter with IIP3> 1dBv over a 0.7-1V power supply," in LETI Days FDSOICE Workshop, GRENOBLE, 2015.

- STMicroelectronics Announces Its 28nm FD-SOI Technology Is Ready for Manufacturing in Its Leading-Edge Crolles Fab, ST Press Release, 2012.

- ST-Ericsson brings PC speeds to mobile devices: First 3Ghz smartphone prototype demo at Mobile World Congress, STE Press Release, February 20, 2013.

- EUTELSAT and STMicroelectronics announce low-cost, low-power, system-on-chip for interactive satellite terminals, EUTELSAT Press Release, March 8, 2017.

- G. Desoli (ST), «A 2.9TOPS/W deep convolutional neural network SoC in FD-SOI 28nm for intelligent embedded systems,» chez International Solid-State Circuits Conference (ISSCC), 2017.

- Samsung and STMicroelectronics Sign Strategic Agreement to Expand 28nm FD-SOI Technology, Samsung/STMicroelectronics Press Release, May 14, 2014.

- NXP Taps into FD-SOI Technology to Enable the Industry's Lowest Power General Purpose Applications Processors, NXP Press Release, March 13, 2017.

- NXP Delivers Increased Safety, Reliability and Scalability to Industrial Applications with New i.MX 8X Processors, NXP Press Release, March 14, 2017.

- GLOBALFOUNDRIES Launches Industry's First 22nm FD-SOI Technology Platform, GLOBALFOUNDRIES Press Release, July 13, 2015.

- S. Jha (GLOBALFOUNDRIES), "The Right Technology at the Right Time," in SOI Industry Consortium workshop, Shanghai, 2015.

- 21. Dream Chip Technologies Presents First 22nm FD-SOI Silicon of New Automotive Driver Assistance SoC, DREAM CHIP Press Release, February 27, 2017.

- 22. R. Merritt, "China Defends Big Chip Bet Inside Huali's \$5.9 billion bet on Fab 2," EETIMES, January 12, 2017.

- 23. GLOBALFOUNDRIES Unveils Ecosystem Partner Program to Accelerate Innovation for Tomorrow's Connected Systems, GLOBALFOUNDRIES Press Release, September 8, 2016.

- 24. GLOBALFOUNDRIES Expands Partner Program to Speed Timeto-Market of FDX<sup>™</sup> Solutions, GLOBALFOUNDRIES Press Release, December 15, 2016.

- 25. GLOBALFOUNDRIES Extends FDX<sup>™</sup> Roadmap with 12nm FD-SOI Technology, GLOBALFOUNDRIES Press Release, September 8, 2016.

- 26. J. Yoshida, «Sony-Inside Huami Watch: Is It Time for FD-SOI?,» October 4, 2016.

- K. Yamamoto (SONY), "A 0.7V 1.5-to-2.3mW GNSS receiver with 2.5-to-3.8dB NF in 28nm FD-SOI," in International Solid-State Circuits Conference (ISSCC), 2016.

- Mobileye, "The Evolution of EyeQ," [Online]. Available: http:// www.mobileye.com/our-technology/evolution-eyeq-chip/. [Accessed 29 March 2017].

- 29. GLOBALFOUNDRIES Expands to Meet Worldwide Customer Demand, GLOBALFOUNDRIES Press Release, February 9, 2017.

Conax introduces Etch**Defender™** coating—the patent-pending solution for extending the life of quartz sheath thermocouples. Etch**Defender™** increases yield and decreases cost of ownership. **Find out more.**

+1 800 223 2389 | conaxtechnologies.com/ss

# Deep learning could boost yields, increase revenues

DAVE LAMMERS, Contributing Editor

**BIG DATA**

Deep learning is "a shiny new hammer" that chip industry may figure out how to use.

hile it is still early days for deep-learning techniques, the semiconductor industry may benefit from the advances in neural networks, according to analysts and industry executives.

First, the design and manufacturing of advanced ICs can become more efficient by deploying neural networks trained to analyze data, though labelling and classifying that data remains a major challenge. Also, demand will be spurred by the inference engines used in smartphones, autos, drones, robots and other systems, while the processors needed to train neural networks will re-energize demand for high-performance systems.

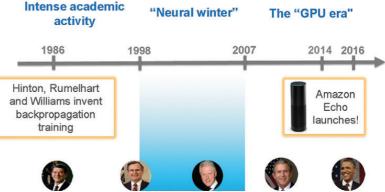

Abel Brown, senior systems architect at Nvidia, said until the 2010-2012 time frame, neural networks "didn't have enough data." Then, a "big bang" occurred when computing power multiplied and very large labelled data sets grew at Amazon, Google, and elsewhere. The trifecta was complete with advances in neural network techniques for image, video, and real-time voice recognition, among others.

During the training process, Brown noted, neural networks "figure out the important parts of the data" and then "converge to a set of significant features and parameters."

Chris Rowen, who recently started Cognite Ventures to advise deep-learning startups, said he is "becoming aware of a lot more interest from the EDA industry" in deep learning techniques, adding that "problems in manufacturing also are very suitable" to the approach.

Chris Rowen, Cognite Ventures

For the semiconductor industry, Rowen said, deeplearning techniques are akin to "a shiny new hammer" that companies are still trying to figure out how to put to good use. But since yield questions are so important, and the causes of defects are often so hard to pinpoint, deep learning is an attractive approach to semiconductor companies.

"When you have masses of data, and you know what the outcome is but have no clear idea of what the causality is, (deep learning) can bring a complex model of causality that is very hard to do with manual methods," said Rowen, an IEEE fellow who earlier was the CEO of Tensilica Inc.

The magic of deep learning, Rowen said, is that the learning process is highly automated and "doesn't require a fab expert to look at the particular defect patterns."

"It really is a rather brute force, naïve method. You don't really know what the constituent patterns are that lead to these particular failures. But if you have enough examples that relate inputs to outputs, to defects or to failures, then you can use deep learning."

Juan Rey, senior director of engineering at Mentor Graphics, said Mentor engineers have started investigating deep-learning techniques which could improve models of the lithography process steps, a complex issue that Rey said "is an area where deep neural networks and machine learning seem to be able to help."

In the lithography process "we need to create an approximate model of what needs to be analyzed. For example,

for photolithography specifically, there is the transition between dark and clear areas, where the slope of intensity for that transition zone plays a very clear role in the physics of the problem being solved. The problem tends to be that the design, the exact formulation, cannot be used in every space, and we are limited

Juan Rey, Mentor Graphics

Mentor Graphics by the computational resources. We need to rely on a few discrete measurements, perhaps a few tens of thousands, maybe more, but it still

is a discrete data set, and we don't know if that is enough to cover all the cases when we model the full chip," he said.

"Where we see an opportunity for deep learning is to try to do an interpretation for that problem, given that an 2017 MRS FALL MEETING & EXHIBIT

November 26–December 1, 2017 | Boston, Massachusetts

#### **Abstract Submission Opens** CALL FOR PAPERS May 15, 2017

#### **BROADER IMPACT**

- RI1 Community College and University Partnerships as Catalysts for Promoting Materials Science Education

- BI2 Materials Innovation for Sustainable Agriculture and Energy

#### **BIOMATERIALS AND SOFT MATERIALS**

- BM1 Multiscale Mechanobiology and Biomechanics-Theory, Experiments, Computations

- Multiphase Fluids for Materials Science— BM2 Droplets, Bubbles and Emulsions

- Biological and Bioinspired Materials for Photonics and Electronics— BM3 From Living Organisms to Devices

- BM4 Biomaterials for Regenerative Engineering

- Polymer Gels in Materials Science-BM5 3D/4D Printing, Fundamentals and Applications

- BM6 2D Nanomaterials in Health Care

- Emerging Materials and Devices for Engineering Biological Function RM7 and Dynamics

- BM8 Materials Design for Neural Interfaces

- BM9 Stretchable Bioelectronics-From Sensor Skins to Implants and Soft Robots

- BM10 Bioinspired Interfacial Materials with Superwettability

- BM11 Modeling, Characterization, Fabrication and Applications of Advanced Biopolymers-Where Form Meets Function

- BM12 Biomolecular Self-Assembly for Materials Design

#### **ELECTRONICS, MAGNETICS AND PHOTONICS**

- EM1 Organic Semiconductors—Surface, Interface, Bulk Doping and Charge Transport

- Multiferroics and Magnetoelectrics FM2

- EM3 Novel Materials and Architectures for Plasmonics-From the Ultraviolet to the Terahertz

- EM4 Wide- and Ultra-Wide-Bandgap Materials and Devices

- EM5 Oxide Interfaces—Lattice and Electronic Defect Interactions

- EM6 Diamond Electronics, Sensors and Biotechnology-Fundamentals to Applications

- EM7 Materials, Devices and Architectures for Neuromorphic Engineering and Brain-Inspired Computing

- Emerging Materials for Quantum Information FM8

- EM9 Electronic and Ionic Dynamics at Solid-Liquid Interfaces

- EM10 Solution-Processed Inorganics for Electronic and Photonic Device Applications

#### **ENERGY AND SUSTAINABILITY**

- ES1 Perovskite Materials and Devices—Progress and Challenges

- ES2 On the Way to Sustainable Solar Fuels-New Concepts, Materials and System Integration

- ES3 Earth Abundant Metal Oxides, Sulphides and Selenides for Energy Systems and Devices

- FS4 Interfaces in Electrochemical Energy Storage

- Materials and Design for Resilient Energy Storage ES5

- Alkali Solid Electrolytes and Solid-State Batteries ES6

- FS7 Chromogenic Materials and Devices

- Advanced Nuclear Materials—Design, Development and Deployment ES8

- ES9 Thermal Energy—Transfer, Conversion and Storage

- ES10 Materials Efficiency to Enable a Circular Materials Economy

- ES11 Silicon for Photovoltaics

NANOMATERIALS

Abstract Submission Deadline

June 15, 2017

- NM1 Carbon Quantum Dots—Emerging Science and Technology

- NM2 Anisotropic Carbon Nanomaterials—Frontiers in Basic and Applied Research NM3 Progress in Developing and Applications of Functional One-Dimensional

- Nanostructures

- Atomically Thin, Layered and 2D Non-Carbon Materials and Systems NM4

- Nanomaterials, Nanoparticles and Nanostructures Produced by Plasmas-NM5 Synthesis, Characterization and Applications

- NM6 Semiconductor Nanocrystals, Plasmonic Nanoparticles and Metal-Hybrid Structures

- NM7 Nanostructure-Based Optical Bioprobes-Advances, Trends and Challenges in Optical and Multimodular Bioimaging and Sensing

- NM8 Defect-Induced Phenomena and New States of Matter at the Nanoscale

#### **PROCESSING AND MANUFACTURING**

- PM1 Explore New Frontiers in Materials Design Using Plasmas-Synthesis, Processing and Characterization

- Advances and Upcoming Research Strategies in Reactive Materials PM2

- Interfaces and Interface Engineering in Inorganic Materials PM3

- PM4 Micro-Assembly Technologies—Fundamentals to Applications

#### THEORY, CHARACTERIZATION AND MODELING

- TC1 Multifunctional and Multifrequency Scanning Probe Microscopy

- TC2 In Situ Studies of Materials Transformations

- тсз Emerging Prospect and Capabilities in Ion Beam Technology and Applications

- TC4 Advanced Atomistic Algorithms in Materials Science

- TC5 Uncertainty Quantification in Multiscale Materials Simulation

- TC6 Mechanical Behavior at the Micro and Nanoscale-Bridging Between Computer Simulations and Experiments

- TC7 Design, Control and Advanced Characterization of Functional Defects in Materials

#### **Meeting Chairs**

Ilke Arslan Pacific Northwest National Laboratory Jason A. Burdick University of Pennsylvania Tao Deng Shanghai Jiao Tong University James B. Hannon IBM T.J. Watson Research Center Sanjay Mathur University of Cologne

www.mrs.org/fall2017

#### 2017 iMatSci Innovator Showcase **CALL FOR EARLY-STAGE STARTUPS**

Submission Site Opens: June 1, 2017 www.mrs.org/imatsci

#### MRS MATERIALS RESEARCH SOCIETY®

506 Keystone Drive · Warrendale, PA 15086-7573 Tel 724.779.3003 · Fax 724.779.8313 info@mrs.org · www.mrs.org

exhaustive analysis is impossible. Using these new types of algorithms, we may be able to move from a problem that is continuous to a problem with a discrete data set."

Mentor seeks to cooperate with academia and with research consortia such as IMEC. "We want to find the right research projects to sponsor between our research teams and academic teams. We hope that we can get better results with these new types of algorithms, and in the longer term with the new hardware that is being developed," Rey said.

Many companies are developing specialized processors to run machine-learning algorithms, including non-Von Neumann, asynchronous architectures, which could offer several orders of magnitude less power consumption. "We are paying a lot of attention to the research, and would like to use some of these chips to solve some of the problems that the industry has, problems that are not very well served right now," Rey said.

While power savings can still be gained with synchronous architectures, Rey said brain-inspired projects such as Qualcomm's Zeroth processor, or the use of memristors being developed at H-P Labs, may be able to deliver significant power savings. "These are all worth paying attention to. It is my feeling that different architectures may be needed to deal with unstructured data. Otherwise, total power consumption is going through the roof. For unstructured data, these types of problem can be dealt with much better with neuromorphic computers."

The use of deep learning techniques is moving beyond the biggest players, such as Google, Amazon (**FIGURE 1**), and the like. Just as various system integrators package the open source modules of the Hadoop data base technology into a more-secure offering, several system integrators are offering workstations packaged with the appropriate deep-learning tools.

Robert Stober, director of systems engineering at Bright Computing, bundles AI software and tools with hardware based on Nvidia or Intel processors. "Our mission statement is to deploy deep learning packages, infrastructure, and clusters, so there is no more digging around for weeks and weeks by your expensive data scientists," Stober said.

Deep learning is driving new the need for new types of processors as well as high-speed interconnects. Tim Miller, senior vice president at One Stop Systems, said that training the neural networks used in deep learning is an ideal task for GPUs because they can perform parallel

#### **History of Deep Learning**

**FIGURE 1.** Deep learning has evolved to play a role in speech recognition used in Amazon's Echo. Source: Amazon

calculations, sharply reducing the training time. However, GPUs often are large and require cooling, which most systems are not equipped to handle.

David Kanter, principal consultant at Real World Technologies, said "as I look at what's driving the industry, it's about convolutional neural networks, and using general-purpose hardware to do this is not the most efficient thing."

However, research efforts focused on using new materials or futuristic architectures may over-complicate the situation for data scientists outside of the research arena. At the International Electron Devices Meeting (IEDM 2017), several research managers discussed using spin torque magnetic (STT-MRAM) technology, or resistive RAMs (ReRAM), to create dense, power-efficient networks of artificial neurons.

While those efforts are worthwhile from a research standpoint, Kanter said "when proving a new technology, you want to minimize the situation, and if you change the software architecture of neural networks, that is asking a lot of programmers, to adopt a different programming method."

While Nvidia, Intel, and others battle it out at the high end for the processors used in training the neural network, the inference engines which use the results of that training must be less expensive and consume far less power.

Kanter said "today, most inference processing is done on general-purpose CPUs. It does not require a GPU. Most people I know say Google does not use a GPU. Since the (inference processing) workload load looks like the processing of DSP algorithms, it can be done with specialpurpose cores from Tensilica (now part of Cadence) or ARC (now part of Synopsys). That is way better than any GPU," Kanter said.

Rowen was asked if the end-node inference engine will blossom into large volumes. "I would emphatically say, yes, powerful inference engines will be widely deployed" in markets such as imaging, voice processing, language recognition, and modeling.

"There will be some opportunity for stand-alone inference engines, but most IEs will be part of a larger system. Inference doesn't necessarily need hundreds of square millimeters of silicon. But it will be a major sub-system, widely deployed in a range of SoC platforms," Rowen said.

Kanter noted that Nvidia has a powerful inference engine processor that has gained traction in the early self-driving cars, and Google has developed an ASIC to process its Tensor deep learning software language.

In many other markets, what is needed are very low power consumption IEs that can be used in security cameras,

voice processors, drones, and many other markets. Nvidia CEO Jen Hsung Huang, in a blog post early this year, said that deep learning will spur demand for billions of devices deployed in drones, portable instruments, intelligent cameras, and autonomous vehicles.

"Someday, billions of intelligent devices will take advantage of deep learning to perform seemingly intelligent tasks," Huang wrote. He envisions a future in which drones will autonomously find an item in a warehouse, for example, while portable medical instruments will use artificial intelligence to diagnose blood samples on-site.

In the long run, that "billions" vision may be correct, Kanter said, adding that the Nvidia CEO, an adept promoter as well as an astute company leader, may be wearing his salesman hat a bit.

"Ten years from now, inference processing will be widespread, and many SoCs will have an inference accelerator on board," Kanter said. ◆

# 15TH ANNUAL MEMS AND SENSORS TECHNOLOGY SYMPOSIUM

## LEADING PERSPECTIVES ACROSS THE SUPPLY CHAIN

# TUESDAY, JUNE 6, 2017 | SAN JOSE, CALIFORNIA

SYMPOSIUM 8:00AM - 5:00PM | EXHIBITS 9:30AM - 6:30PM | RECEPTION 5:00PM - 6:30PM

## **REGISTER TODAY AT MEPTEC.ORG/2017MEMS**

LITHOGRAPHY

# First EUV lithography high-volume manufacturing solution for N5 BEOL

JOOST BEKAERT and MING MAO, imec, Leuven, Belgium

Immersion-based self-aligned quadruple patterning is combined with EUV lithography block patterning to achieve metal layers with pitches as small as 32nm.

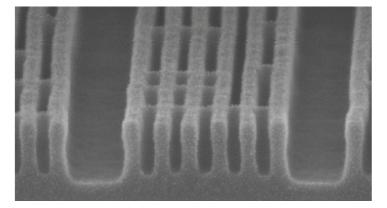

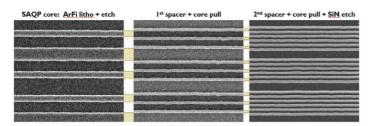

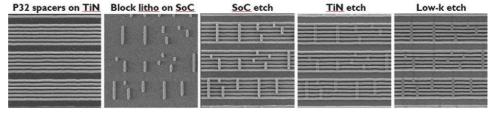

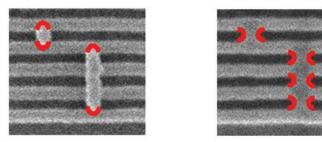

t the 2017 SPIE Advanced Lithography conference, imec – in close collaboration with its suppliers – presented an industry relevant platform for patterning the most advanced back-end-ofline metal layers, conform with the foundry N5 technology node. Imec's solution includes two scenarios for EUV lithography insertion, as well as proposals for design rules, masks, photoresists, etching, metrology and variation assessment. In this article, one of these scenarios is described in more detail. It combines immersion-based self-aligned quadruple patterning with EUV lithography block patterning, to achieve metal layers with pitches as small as 32nm. To assess the platform's suitability for highvolume manufacturing, the uniformity of the layers and their local variability is discussed.

# The patterning of advanced logic back-end-of-line layers

As we move towards more advanced technology nodes, the patterning of critical back-end-of-line (BEOL) metal layers with ever more aggressive pitches (e.g. 32nm) has become very challenging. In these BEOL layers, typically, trenches are created which are then filled with metal in a final metallization step. In order to create a disconnection in the continuous trenches, block layers perpendicular to the trenches are added, resulting in small metal tip-to-tips. In the industry, various options are considered to pattern the most aggressive BEOL layers and blocks. One option is to use immersion lithography in combination with so-called self-aligned quadruple patterning (SAQP) for the metal lines, and triple patterning for the block layers. This option however requires a triple block mask and a triple litho-etch process flow, which adds to the cost and complexity of the proposed solution. Another option is to pattern the BEOL metal layers directly with EUV lithography (EUVL) in one single exposure. Although this direct EUVL integration flow is very simple and cost-effective, pattern fidelity (e.g. the shape of the pattern) and pattern variability, as well as mask making are expected to be extremely challenging, especially for very small tip-to-tips.

One of the alternatives imec is evaluating is a 'hybrid' option, in which immersion-based SAQP of metal lines is combined with a direct EUV print of the block layer – using ASML's NXE:3300 scanner.

#### The imec N7 (iN7) EUV platform