## Solid State TECHNOLOGY

**Insights for Electronics Manufacturing**

Inside the Intel/ Micron 3D FG-NAND

P. 17

CMP Slurry Optimization

P. 20

Ambient Cooling Systems

P. 24

Processes for Next-Gen Biotech Devices PIII

> Extension M F D L A

## CALL FOR PAPERS

**Abstract Submission Opens** September 13, 2016

**Abstract Submission Deadline** October 13, 2016

#### CHARACTERIZATION, THEORY AND MODELING

- CM1 Emergent Material Properties and Phase Transitions Under Pressure

- CM2 Advanced Numerical Algorithms for Metallic Systems at the Mesoscale in Materials Science

- CM3 Computer-Based Modeling and Experiment for the Design of Soft Materials

- CM4 In Situ Electron Microscopy of Dynamic Materials Phenomena

- CM5 Mechanically Coupled Properties, Phenomena and Testing Methods in Small-Scale and Low-Dimensional Systems

- CM6 Dislocation Microstructures and Plasticity

- CM7 Genomic Approaches to Accelerated Materials Innovation

#### **ELECTRONIC DEVICES AND MATERIALS**

- ED1 Silicon-Carbide, Diamond and Related Materials for Quantum Technologies

- ED2 Materials and Devices for Neuromorphic-Engineering and Brain-Inspired Computing

- ED3 Physics, Chemistry and Materials for Beyond Silicon Electronics

- ED4 Luminescent Materials for Photon Upconversion

- **ED5** Photoactive Nanoparticles and Nanostructures

- ED6 Nanostructured Quantum-Confined States for Advanced Optoelectronics

- ED7 Materials and Device Engineering for Beyond the Roadmap Devices in Logic, Memory and Power

- ED8 Development and Integration of Organic and Polymeric Materials for Thin-Film Electronic Devices

- ED9 Advanced Interconnects for Logic and Memory Applications— Materials, Processes and Integration

- ED10 Material Platforms for Plasmonics and Metamaterials— Novel Approaches Towards Practical Applications

- ED11 Phase-Change Materials and Their Applications— Memories, Photonics, Displays and Non-von Neumann Computing

- ED12 Quantum Sensing, Metrology and Devices

- ED13 Novel Photonic, Electronic and Plasmonic Phenomena in Materials

- ED14 Molecular and Colloidal Plasmonics—Synthesis and Applications

#### **ENERGY STORAGE AND CONVERSION**

- ES1 Perovskite Solar Cells—Towards Commercialization

- ES2 High-Capacity Electrode Materials for Rechargeable Energy Storage

- ES3 Materials for Multivalent Electrochemical Energy Storage

- ES4 Nanogenerators and Piezotronics

- ES5 Advances in Materials, Experiments and Modeling for Nuclear Energy

- ES6 Mechanics of Energy Storage and Conversion— Batteries, Thermoelectrics and Fuel Cells

- ES7 (Photo)electrocatalytic Materials and Integrated Assemblies for Solar Fuels Production—Discovery, Characterization and Performance

- ES8 Caloric Materials for Energy-Efficient Applications

- ES9 Surfaces, Coatings and Interfaces in Concentrated Solar Energy Applications

- ES10 Frontiers in Oxide Interface Spintronics—

Magnetoelectrics, Multiferroics and Spin-Orbit Effects

- ES11 Advanced and Highly Efficient Photovoltaic Devices

- ES12 Soft Magnetic Materials for Next-Generation Power Electronics

- ES13 Interfaces and Interphases in Electrochemical Energy Storage and Conversion

- ES14 Thin-Film Chalcogenide Semiconductor Photovoltaics

#### **NANOMATERIALS**

- NM1 Emerging Non-Graphene 2D Materials

- NM2 Nanoscale Heat Transport—From Fundamentals to Devices

- NM3 Aerogels and Aerogel-Inspired Materials

- NM4 Novel Catalytic Materials for Energy and Environment

- NM5 Frontiers in Terahertz Materials and Technology

- NM6 Mechanical Behavior of Nanostructured Composites

- NM7 Semiconductor Nanowires for Energy Applications

- NM8 2D Materials—

- Macroscopic Perfection vs. Emerging Nanoscale Functionality

- NM9 High-Performance Metals and Alloys in Extreme Conditions

- NM10 Micro/Nano Assembling, Manufacturing and Manipulation for Biomolecular and Cellular Applications

#### **Meeting Chairs**

Christopher J. Bettinger Carnegie Mellon University Stefan A. Maier Imperial College London Alfonso H.W. Ngan The University of Hong Kong W. Jud Ready Georgia Institute of Technology Eli A. Sutter University of Nebraska—Lincoln

www.mrs.org/spring2017

#### Don't Miss These Future MRS Meetings!

2017 MRS Fall Meeting & Exhibit

November 26 - December 1, 2017, Boston, Massachusetts

2018 MRS Spring Meeting & Exhibit

<del>April</del> 2 – 6, 2018, Phoenix, Arizona

#### **SOFT MATERIALS AND BIOMATERIALS**

- SM1 Bioelectronics—Materials, Processes and Applications

- SM2 Advanced Multifunctional Fibers and Textiles

- SM3 Advanced Biomaterials for Neural Interfaces

- SM4 A Soft Future—

- From Electronic Skin to Robotics and Energy Harvesting

- SM5 Aqueous Cytomimetic Materials

- SM6 Materials in Immunology—

- From Fundamental Material Design to Translational Applications

- SM7 Emerging Membrane Materials for Sustainable Separations

- SM8 Advanced Polymers

MRS MATERIALS RESEARCH SOCIETY®

Advancing materials. Improving the quality of life

506 Keystone Drive • Warrendale, PA 15086-7573

Tel 724.779.3003 • Fax 724.779.8313

info@mrs.org • www.mrs.org

## **Solid State TECHNOLOGY**®

SEPTEMBER 2016 VOL. 59 NO. 6

NIL, combined with sealing and bonding processes, can enable the production of next-generation biotechnology devices. Source: EVG.

#### FEATURES

#### **BIOTECH** | High-volume processes for next-generation biotechnology devices

Micro- and nanotechnology combined with biotechnology has the potential to revolutionize many areas of healthcare, agriculture and industrial manufacturing, but the availability of fabrication tools is key.

Bernd Dielacher, Martin Eibelhuber and Thomas Uhrmann, EV Group, St. Florian, Austria

#### FLOATING GATE NAND | Deep dive into the Intel/Micron 3D 32L FG-NAND

Key features of the cell structure, design and integration of the Micron 3D 32L FG-NAND device are discussed, and compared with Samsung's 32L and 48L V-NAND device.

Jeongdong Choe, TechInsights, Ottawa, Canada

#### PLANARIZATION | CMP slurry optimization for advanced nodes

As advanced device manufacturers identify needs for new and additional CMP steps, new slurry solutions can deliver exceptional planarization and defectivity within a stable CMP process.

Adam Manzonie, Todd Buley, Jia-Ni Chu and Mike Kulus, CMP Technologies, Dow Electronic Materials, Newark, DE

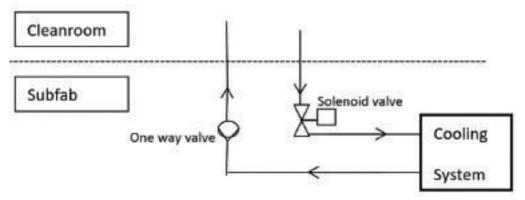

#### **COOLING** Liquid to liquid ambient cooling systems for semiconductor tools

An overview of liquid-to-liquid cooling systems and their operating principles.

Marko Niemann, Regional Sales Director, Laird Engineered Thermal Systems, Cologne, Germany

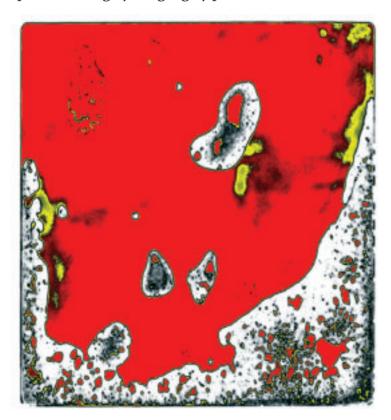

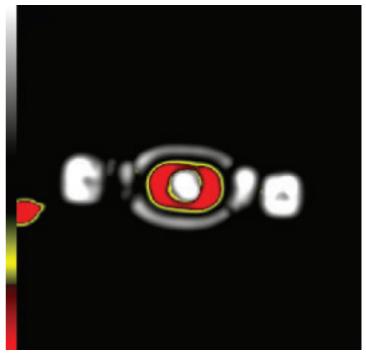

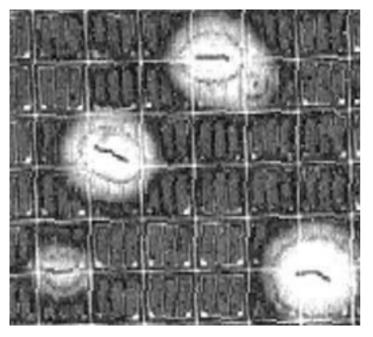

#### **LEDs** Light and sound: LEDs seen acoustically

Many LED failures are the result of voids or other gap-type anomalies that block heat flow from the die. Tom Adams, Sonoscan, Inc., Elk Grove, IL

#### COLUMNS

- **2 Editorial** A changing industry *Pete Singer, Editor-in-Chief*

- **9 Packaging** TSMC's UBM-free fan-in WLCSP, *Phil Garrou, Contributing Editor*

- **Semiconductors** Fab facilities data and defectivity, *Ed Korczynski, Sr. Technical Editor*

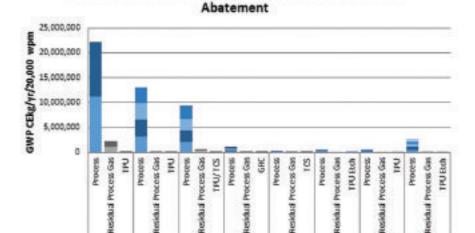

- **32** Industry Forum | Etch abatement needed to meet WSC goals,

Mike Czerniak, Environmental Solutions Business Development Manager, Edwards

#### DEPARTMENTS

- Web Exclusives

- 4 News

- 30 Ad Index

#### editorial

#### A changing industry

The semiconductor industry is changing in some big ways. Demand for PCs and mobile devices - once the main drivers of growth - has slowed. Gains from traditional scaling are harder to come by. Cost per transistor is now increasing. Consolidation is widespread up and down the supply chain, which may slow innovation. ITRS efforts have been abandoned.

Yet, despite this "maturing" of the industry - at least as we know it -opportunities abound. The Internet of Things (IoT) is set to explode, which will result in a demand for "things" such as sensors and actuators, but also cloud computing.

Earlier this year, Brian Krzanich, CEO of Intel, wrote about five core beliefs that he holds to be "undeniably true" for the future:

- The cloud is the most important trend shaping the future of the smart, connected world - and thus Intel's future.

- The many "things" that make up the PC Client business and the Internet of Things are made much more valuable by their connection to the cloud.

- Memory and programmable solutions such as FPGAs will deliver entirely new classes of products for the data center and the Internet of Things.

- 5G will become the key technology for access to the cloud and as we move toward an always-connected world.

- · Moore's Law will continue to progress and Intel will continue to lead in delivering its true economic impact.

While it's true that it's difficult to forecast what the overall impact of the IoT movement will have on the semiconductor industry, or how big it will be. Speaking at The ConFab in June, Tom Caulfield, SVP and GM of Fab 8 at GLOBALFOUNDRIES, said the IoT opportunity represents "magnitudes that are well beyond anything we've done before." A recent McKenzie study estimates \$50-75 billion dollars of additional semiconductor revenue in an industry that today is \$350 billion.

IoT, cloud computing and 5G will result in increased demand for leading edge semiconductor technology, which in turn will create a demand for 7 and 5nm devices and beyond. Perhaps more importantly, there will be tremendous demand for a wider variety of solid state devices, including MEMS, LEDs, power electronics, biomedical devices, thin film batteries and photonics/plasmonics.

There will be a need to integrate these devices for the usual reasons: to improve performance, and reduce cost and size. This will lead to innovative new packaging strategies and better chip-package co-design tools. It will create a demand for new types of manufacturing equipment and materials. New business models and new approaches to collaboration will also be required.

In short, the semiconductor industry is going through some fundamental changes, but the future has never looked brighter. As Caulfield said at The ConFab, "The demand for silicon is going to grow in an incredible way. What we need to do in this industry, is what we've done all along. We've reinvented ourselves every 18 months to 2 years with Moore's Law. Now we have to start reinventing ourselves in how we engage and collaborate together."

-Pete Singer, Editor-in-Chief

### Solid State

Pete Singer, Editor-in-Chief Ph: 978.470.1806. psinger@extensionmedia.com

Shannon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor,

Dave Lammers, Contributing Editor Phil Garrou, Contributing Editor Dick James, Contributing Editor Vivek Bakshi, Contributing Editor

#### CREATIVE/PRODUCTION/ONLINE

LS Jerrett, Production Traffic Coordinator Nicky Jacobson, Senior Graphic Designer Simone Bradley, Graphic Designer

Slava Dotsenko, Senior Web Developer

Jon Franke, Media Coordinator

#### MARKETING/CIRCULATION

iiohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher **Embedded Electronics Media Group** cbright@extensionmedia.com

Melissa Sterling, Vice President, **Business Development** msterling@extensionmedia.com

For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2016 by Extension Media LLC. All rights reserved. Printed in the U.S.

September 2016 VOL. 59 NO. 6 • *Solid State Technology* ©2016 (ISSN 0038-111X) **Subscriptions**: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: *Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343.* (8 am – 5 pm, PST).

San Francisco, CA 94107

#### **Web Exclusives**

#### Kateeva: Enabling OLED success

Kateeva is out to change the way displays are being made, and during Tuesday's Silicon Innovation Forum keynote at SEMICON West 2016, Kateeva President and COO Conor Madigan, PhD, laid out how their YIELDJet inkjet system is making that happen.

http://bit.ly/2aPkTt2

## Packaging and displays drive new litho requirements

Fan-out wafer level packaging (FOWLP) is gaining traction, leading to higher I/Os and larger formats, and new mobile displays are pushing the limits of pixel per inch (PPI) while also moving to larger formats. Both trends are driving new requirements for lithography equipment, including steppers, track systems and photoresists. Both packages and displays are employing new types of materials and thinner substrates as well.

http://bit.ly/2b1TuVG

## Insights from the Leading Edge: IMEC 20m pitch thermo compression copper pillar bonding

Contributing Editor Dr. Phil Garrou continues his look at IEEE ECTC 2016.

http://bit.ly/2aPI07Z

## Flexible medical device manufacturing developments

Medical and health/wellness monitoring devices provide critical information to improve quality-of-life and/or human life-extension. To meet the anticipated product needs of wearable comfort and relative affordability, sensors and signal-processing circuits generally need to be flexible. The SEMICON West 2016 Flexible Electronics Forum provided two days of excellent presentations by industry experts on these topics, and the second day focused on the medical applications of flexible circuits.

http://bit.ly/2aPn7c4

#### IEDM 2016 has "new twists," supplier exhibits for the first time

A bit earlier than usual, the IEDM (International Electron Devices Meeting) press kit is available, and among the announcements are a couple of surprises. The biggest practical change is the addition of an exhibit hall – up to now the conference has been almost religiously anticommercial, to the extent that forums sponsored by Applied Materials, ASM, and Synopsys have had to be held offsite in other hotels.

http://bit.ly/2aWdVV6

#### **Update from EUVL Workshop in Berkeley**

The 2016 EUVL Workshop was held last month at LBL in Berkeley, where we heard the latest news on EUV Lithography R&D development topics.

http://bit.ly/2aWdGta

#### Established technology nodes: The most popular kid at the dance

The Internet of Things (IoT) means many things to many people, but the segment of IoT related to sensors and connectivity is the answer to the longevity question. The functionality we crave, such as smart power management for longer battery life, and Wi-Fi and Bluetooth for more connectivity, are more cost-effective when implemented at established nodes between 40 nm and 180 nm. Consequently, the high consumer demand for these capabilities is driving increased demand for ICs manufactured using these processes. In a nutshell, the nodes that best support radio frequency (RF) and mixed-signal IC designs with low power, low cost and high reliability are seeing a much higher demand than in the past.

http://bit.ly/2bDSg62

#### Power semiconductor market revenues decline

Overall revenue for the power semiconductors market globally dropped slightly in 2015, due primarily to macroeconomic factors and application-specific issues, according to a new report from IHS Markit.

http://bit.ly/2aN0NOe

Please send news articles to sdavis@extensionmedia.com

#### worldnews

#### USA - Lam Research Corp.

introduced an atomic layer deposition process for depositing low-fluorine-content tungsten films.

ASIA - Samco announced that it will open its Malaysia branch office on Aug. 10, 2016 in Petaling Jaya, a suburb of Kuala Lumpur.

**USA** - Cascade Microtech announced the release of a comprehensive low-frequency noise measurement solution for device modeling, characterization and reliability testing with MeasureOne solution partner **Keysight Technologies.**

ASIA - Mouser Electronics, Inc. announced the appointment of Sam Katsuta as Vice President of Mouser Electronics-Japan.

**EUROPE - STMicroelectronics** was named the MEMS Manufacturer of the Year at the MEMS World Summit.

**EUROPE** - **EV Group** introduced the EVG50 automated metrology system.

**ASIA** - GLOBALFOUNDRIES announced that Wallace Pai has been appointed as vice president and general manager of China.

USA - Busch, LLC. announced plans to build a new 44,000 sq. ft. building in Austin, Texas.

ASIA - A\*STAR's Institute of Microelectronics launched two consortia on advanced packaging, the Silicon Photonics Packaging consortium (Phase II) and the MEMS Wafer Level Chip Scale Packaging (WLCSP) consortium.

EUROPE - imec and Synopsys, Inc. announced an interconnect resistivity model to support the screening and selection of alternative interconnect metals and liner-barrier materials at the 7nm node and beyond.

#### What's happening in Japan's semiconductor industry?

By Yoichiro Ando, SEMI Japan

The 2016 global semiconductor market is forecast to decrease by 2.4 percent from the previous year according to the World Semiconductor Trade Statistics (WSTS). SEMI forecasts that the global semiconductor manufacturing equipment market will be effectively flat this year. However, SEMI also forecasts double-digit growth in 2017 with significant new fab construction starts in 2016 and 2017 that will drive later equipment. The forecast foresees the Japan market will shrink through 2017. This article provides insight behind those forecast numbers.

Toshiba's new Fab 2 cleanroom (Source: Toshiba)

#### Overview

Large-scale investments in 300mm wafer lines in Japan are primarily made by three companies: Toshiba (NAND Flash), Sony (image sensors) and Micron Memory Japan (DRAM). The logic players' investments are largely for upgrading and expanding existing capacity; the companies producing power, surface acoustic wave (SAW), and automotive semiconductor devices are actively adding capacity by constructing new fabs and expanding existing fabs. These activities are planned on 200mm or smaller wafers, so the investments are smaller in terms of dollar values. However, they are important to Japan's semiconductor industry in the coming Internet of Things (IoT) age.

#### Toshiba plans a new mega fab

Toshiba continues to expanding its 300 mm NAND fabs in Yokkaichi in 2015 and 2016 including the second phase construction of Fab 5, new Fab 2 for 3D NAND flash memory production, and plan for a new fab (Fab 6).

The new Fab 6 will be dedicated to 3D NAND flash memory production, and is planned to be built in an adjacent area of the current Yokkaichi factory site. Detailed plans of the construction (such as construction period, production capacity, and invest-

> ment to manufacturing instrument used) will be decided in FY 2016 based on market trends. Fab 6 is expected to be built in FY 2017. Production capacity of the fab is projected to be more than 200,000 wafers per month (300mm wafers) at full capacity.

Toshiba and Western Digital announced a plan in July 2016 to invest a total of 1.5 trillion JPY for the next three years in Yokkaichi operations. This investment will be for the construction of

the new fab as well as for updating equipment for existing fabs such as new Fab 2 and Fab 5.

#### Sony expands 300mm capacity

Sony is also actively expanding its 300mm wafer fabs for increased production of complementary metal-oxide-semiconductor (CMOS) image sensors. Sony plans to expand production capacity not only with its existing lines but also to acquire fabs from other companies. Specifically, Sony acquired Tsuruoka factory in Yamagata prefecture in 2014 from Renesas Electronics

Continued on page 7

#### China's final chance to achieve its IC industry ambitions now underway

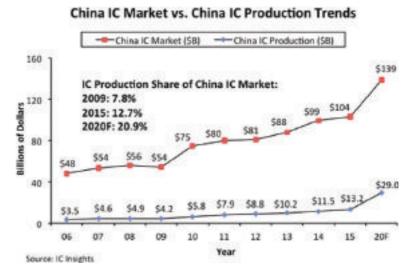

Over the past 20 years, China has become increasingly frustrated over the gap between its IC imports and indigenous IC production (**Figure 1**). It has oftentimes been quoted over the last couple of years that China's imports of semiconductors exceeds that of oil.

In its upcoming Mid-Year Update to The McClean Report 2016 (released at the end of this week), IC Insights examines the "Three-Phase" history of China's attempt at strengthening its position in the IC industry that started in earnest in the late 1990s (**Figure 2**).

In the late 1990s, China began to contemplate ways to grow its indigenous IC industry and assisted in creating Hua Hong NEC, which was founded in 1997 as a joint venture between Shanghai Hua Hong and Japan-based NEC (it merged with Grace in 2011). Then, as part of the country's 10th Five Year Plan (2000-2005), establishing a

Continued on page 8

FIGURE 1.

## International Technology Roadmap for Semiconductors examines next 15 years of chip innovation

The Semiconductor Industry Association (SIA) announced the release of the 2015 International Technology Roadmap for Semiconductors (ITRS), a collaborative report that surveys the technological challenges and opportunities for the semiconductor industry through 2030. The ITRS seeks to identify future technical obstacles and shortfalls, so the industry and research community can collaborate effectively to overcome them and build the next generation of semiconductors – the enabling technology of modern electronics. The current report marks the final installment of the ITRS.

"For a quarter-century, the Roadmap has been an important guidepost for evaluating and advancing semiconductor innovation," said John Neuffer, president and CEO, Semiconductor Industry Association. "The latest and final installment provides key findings about the future of semiconductor technology and serves as a useful bridge to the next wave of semiconductor research initiatives."

Faced with ever-evolving research needs and technology challenges, industry leaders have decided to conclude the ITRS and transition to new ways to advance semiconductor research and bring about

the next generation of semiconductor innovations. While the final ITRS report charts a path for existing technology research, additional research is needed as we transition to an even more connected world, enabled by innovations like the Internet of Things. Some of these technology challenges were outlined in a recent SIA-Semiconductor Research Corporation (SRC) report, "Rebooting the IT Revolution," but work continues to define research gaps and implement new research programs.

The ITRS is sponsored by five regions of the world – Europe, Japan, Korea, Taiwan, and the United States. Through the cooperative efforts of the global chip manufacturers and equipment suppliers, research communities and consortia, the ITRS has identified critical gaps, technical needs, and potential solutions related to semiconductor technology.

"SIA appreciates the hard work, dedication, and expertise of those involved with the ITRS over the years and looks forward to continuing the industry's work to strengthen semiconductor research and maintain the pipeline of semiconductor innovations that fuel the digital economy," Neuffer said. ◆

#### Huge 2H16 spending surge expected from Samsung, TSMC, and Intel

In addition to the monthly Updates, IC Insights' subscription to The McClean Report includes three "subscriber only" webcasts. The first of these webcasts was presented on August 3, 2016 and discussed semiconductor industry capital spending trends, the worldwide economic outlook, the semiconductor industry forecast through 2020, as well as China's failures and successes on its path to increasing its presence in the IC industry.

In total, IC Insights forecasts that semiconductor industry capital spending will increase by only 3% this year after declining by 2% in 2015. However, driven by the top three spenders—Samsung, TSMC, and Intel—capital spending in 2016 is expected to be heavily skewed toward the second half of this year. Figure 1 shows that the combined

2016 Capital Spending Forecast (1H16 vs 2H16)

| 2016F<br>Rank | Company                   | 2015<br>(SM) | 2016F<br>(\$M) | 16/15 %<br>Change | Actual<br>(\$M) | 2H16 Spending<br>Needed to Make<br>Budget (SM) | 2H16/1H16<br>% Change |

|---------------|---------------------------|--------------|----------------|-------------------|-----------------|------------------------------------------------|-----------------------|

| 1             | Samsung                   | 13,010       | 11,000         | -15%              | 3,439           | 7,561                                          | 120%                  |

| 2             | TSMC                      | 8,080        | 10,000         | 24%               | 3,426           | 6,574                                          | 92%                   |

| 3             | Intel                     | 7,326        | 9,500          | 3014              | 3,646           | 6,854                                          | 61%                   |

| -             | Top 3 Total               | 28,425       | 30,500         | 7%                | 10,511          | 19,969                                         | 90%                   |

| _             | Others                    | 36,427       | 36,610         | 1%                | 19,932          | 16,678                                         | -16%                  |

| _             | <b>Total Cap Spending</b> | 64,852       | 67,110         | 3%                | 30,443          | 36,667                                         | 20%                   |

Source IC Insights, Company Reports

2016 outlays for the top three semiconductor industry spenders are forecast to be 90% higher in the second half of this year as compared to the first half.

Combined, the "Big 3" spenders are forecast to represent 45% of the total semiconductor industry outlays this year. An overview of each company's actual 1H16 spending and their 2H16 spending outlook is shown below.

**Samsung** — The company spent only about \$3.4 billion in capital expenditures in 1H16, just 31% of its forecasted \$11.0 billion full-year 2016 budget.

**TSMC** — Its outlays in the first half of 2016 were only \$3.4 billion, leaving \$6.6 billion to be spent in the second half of this year in order to reach its full-year \$10.0 billion budget. This would represent a 2H16/1H16 spending increase of 92%.

Intel — Spent just \$3.6 billion in 1H16. The company needs to spend \$5.9 billion in the second half of this year to reach its current \$9.5 billion spending budget, which would be a 2H16/1H16 increase of 61%.

In contrast to the "Big 3" spenders, capital outlays by the rest of the semiconductor suppliers are forecast to shrink by 16% in the second half of this year as compared to the first half. In total, 2H16 semiconductor industry capital spending is expected to be up 20% over 1H16 outlays, setting up a busy period for the semiconductor equipment suppliers through the end of this year.

Further trends and analysis relating to semiconductor capital spending through 2020 are covered in the 250-plus-page Mid-Year Update to the 2016 edition of The McClean Report. ◆

Japan's semiconductor industry, Continued from page 4

Corporation, and it is now operated as Yamagata Technology Center (TEC) of Sony Semiconductor Manufacturing Corporation, which is a semiconductor production subsidiary of Sony Corporation. In 2015, Sony acquired the 300mm line of the Toshiba Oita factory, for production of CMOS image sensors.

Sony plans to invest 70 billion JPY in FY 2016, and expand image sensor production capacity now 70,000 wafers per month as of first quarter of 2016. The restoration of Kumamoto TEC damaged by the Kumamoto earthquake would make investment in other TECs decrease.

#### Micron and TowerJazz

Micron Technology operates a 300mm fab in Hiroshima (Micron Memory Japan Fab 15). The fab manufactures DRAM with 12nm process technology. Micron invested US\$750 million in 2015 and \$500 million in 2016 for the technology upgrades. The capacity has been flat in these two years.

Panasonic TowerJazz Semiconductor, a Panasonic and TowerJazz joint venture, operates a 300mm foundry fab in Uozu. The company invested \$10 million in 2015 and plans to invest the same amount in 2016 to improve the productivity.

#### Investments in 200mm and smaller wafer lines

Other major semiconductor manufacturers primarily invest in existing fabs and lines for maintenances and productivity improvements. Therefore, investment amount is modest. However, these fabs will be the major source for semiconductor devices of the Internet of Things applications.

- Renesas Electronics Corporation plans upkeep of production capacity of Kumamoto fab (200mm wafer fab) and Naka fab (300mm wafer fab).

- Fujitsu enhances Fab B2 of Mie Fujitsu Semiconductor Limited, which provides foundry services with 300mm wafer lines. Taiwan's major foundry UMC participated in capital of Mie Fujitsu Semiconductor Limited, and assists with 40nm process technology.

- Rohm Co., Ltd. plans to invest more than 10 billion JPY in enhancement of 200mm lines of fab and others in the headquarters.

- Fuji Electric Co., Ltd. continues enhancement of its 200mm wafer lines for IGBT of Yamanashi plant in FY 2016. Fuji Electric further expands its SiC power device production capacity by enhancing 200mm wafer lines at Matsumoto fab.

- Mitsubishi Electric Corporation manufactures power devices at 200mm wafer line of Kumamoto fab. Mitsubishi Electric continues enhancement of power device production capacity.

Shindengen Electric Manufacturing Co., Ltd. is enhancing its power semiconductor module production by adding a new line each for Akita Shindengen Co., Ltd. and Higashine Shindengen Co., Ltd. from FY 2015.

#### **Electronic parts and optoelectronic devices**

The electronic parts companies are emerging as new fab owners in Japan. Their recent activities are summarized below:

- New Japan Radio Co., Ltd. continues enhancement of production capacity of SAW devices and GaAs ICs at its Kawagoe fab in 2016.

- Hamamatsu Photonics K.K. continues enhancement of MEMS fabrication facility (Fab 13) which started operation in March 2014.

- Upkeep of new clean room of Toyota Motor Corporation, which started operation in 2014, is now underway. Currently, this line is used for research and development, and trial production of SiC devices.

- Murata Manufacturing Company, Ltd. is building a new fab for SAW filter production at its headquarter factory in Toyama. The new fab construction will be completed in September 2016. Total investment to the facility is planned to be 12 billion JPY. Then it will be equipped with 200 mm (mostly secondary) equipment.

- Taiyo Yuden Co., Ltd. continues its enhancement plan of Oume fab in FY 2016, which was acquired from Hitachi in 2013 for SAW device production.

- TDK agreed to acquire 125mm wafer lines in Tsuruoka Factory from Renesas Electronics Corporation in November 2015. TDK plans to enhance its production capacity of super miniature electronic components at this plant. Production will start in FY 2016 after replacement of manufacturing equipment to conform to products to be manufactured. Investment will continue in FY 2016 as well for startup of the mass production and maintenance at this plant. ◆

China's final chance, Continued from page 5

strong China-based IC foundry industry became a priority. As a result, pure play foundries SMIC and Grace (now Hua Hong Semiconductor) were both founded in 2000 and XMC was founded in 2006. This effort is categorized by IC Insights as Phase 1 of China's IC industry strategy.

In the early 2000s, to help boost the sales of its indigenous foundries, as well as ride the strong wave of fabless IC supplier growth, the Chinese government began attempts to foster a positive environment for the creation of Chinese fabless companies. It should be noted that eight of the current top 10 Chinese fabless IC suppliers were started between 2001 and 2004 and seven of them were in the top 50 worldwide ranking of fabless IC companies last year. This stage of China's IC industry strategy is labeled by IC Insights as Phase 2.

IC Insights believes that Phase 3 of China's attempt at creating a strong China-based IC industry began in 2014, just before the

start of its 13th Five Year Plan which runs from 2015 through 2020. As discussed in detail in the Mid-Year Update, this Phase is being supported by a huge "war chest" of cash that is intended to be used to purchase IC companies and their associated intellectual property, provide additional funding to China's existing IC producers (e.g., SMIC, Grace, XMC, etc.), and to help establish new IC producers (e.g., Sino King Technology, Fujian Jin Hua, etc.).

In 1Q16, the U.S. Department of Commerce slapped an export ban on U.S. IC suppliers' shipments of ICs to China-based telecom giant ZTE in response to the company allegedly shipping telecommunications equipment to Iran while it was under trade sanctions by the U.S. This ban, if fully enacted, would have a devastating effect on ZTE's telecom equipment sales (including mobile phones). Thus far, the export ban has been postponed until August 30, 2016 pending further investigation by the U.S. Department of Commerce.

#### The Three Phases of China's IC Industry Strategy

| Phase | Approach                                                                                                | Timeframe Initiated      | Successful? |

|-------|---------------------------------------------------------------------------------------------------------|--------------------------|-------------|

| 1     | Build a strong indigenous pure-play foundry industry                                                    | Late 1990s - Early 2000s | No          |

| 2     | Build a strong presence in the fabless IC<br>supplier space                                             | Early 2000s - Mid 2000s  | No          |

| 3     | Build a strong China-based IC<br>supplier/manufacturer base with<br>startups, acquisitions, and mergers | Mid 2010s - Late 2010s   | 7277        |

Source: IC Insights

FIGURE 2.

The situation regarding ZTE and the abrupt announcement earlier this year of export controls on the company by the U.S. government sent shock waves throughout the Chinese government as well as China's electronic system manufacturers. At this point in time, such potentially drastic measures taken by the U.S. government against such a large Chinese electronics company has bolstered the Chinese government's resolve to make China more self-sufficient regarding IC component production, spurring increased emphasis on "Phase Three."

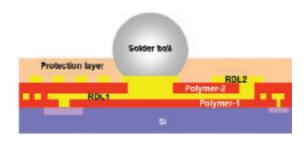

## TSMC's UBM-free fan-in WLCSP

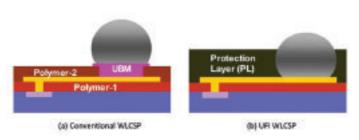

At the 2016 ECTC Conference, TSMC discussed their UFI (UBM-Free Integration) Fan-In WLCSP technology which they claim enables large die fine pitch packages.

Development of low-cost WLCSP for large die with high I/O count is desired for broadening its applications. Reliability issues including solder cracking and high chip warpage are known to be the main challenges for extending the die size of conventional WLCSP to more than  $5x5\ mm2$  with ball pitch smaller than  $350\ \mu m$ .

TSMC has discovered that by controlling the maximum strain location and optimizing materials, chip warpage and the stress between silicon and the PCB can be reduced which improves both component and board-level reliabilities of WLCSP packages. Packages as large as 10.3x10.3 mm2 with both 400 and 350  $\mu m$  ball pitches have been developed.

UBM is used as an interfacial layer between the metal pad of the integrated circuit and the solder ball. The formation of UBM/solder intermetallic compounds (IMC) limits the board level reliability of the package due to the poor mechanical robustness of IMCs. When the die size is increased, stress increases which promotes cracking at the UBM/solder ball interface.

TSMC claims their UFI WLCSP fabrication cost is lower than conventional WLCSPs due to the elimination of the UBM. Removal of the UBM also reduces the thickness of the package by 30%.

Figure 1 compares the structures of a standard WLCSP vs the TSMC UFI WLCSP. In the UFI WLCSP, the solder balls are directly mounted to the Cu RDL followed by the polymeric PL (protection layer which secure the balls.

Very similar removal of UBM and subsequent thickening of the copper pad has been reported before by Amkor in 2010 [1].

#### **Packaging**

PHIL GARROU, Contributing Editor

TSMC simulation results showed the solder joint fatigue life decreases with increasing die sizes for both UFI and the conventional WLCSP. Predicted

solder ball fatigue life was found to increases with decreasing die thickness. The authors suggest that decreasing the die thickness not only reduces the thermal expansion difference between the die and the PCB, but also causes the die to bend more under thermal loading. In addition, simulation results imply that solder joint creep strain for solder mask defined (SMD) structures is 72% higher than for non-solder mask defined (NSMD) structures because of its reduced flexible solder joint height and the constraint of the solder mask. Thus they concluded that it is better to use NSMD type of PCB for UFI WLCSP. The use of NSMD structures to increase reliability has been known since the work of Bell Labs Ejim [2].

The UFI WLCSP passes all component-level tests and exhibited board-level thermal cycle life that is 1.4 and 2.3 times longer than that of the conventional WLCSP in terms of the first failure and the Weibull distribution, respectively. 10mm UFI WLCSP have passed component-level reliability tests such as TCB1000, uHAST96 and HTS1000, and board-level reliability tests of TCG500 and drop tests.

To demonstrate the possibility of higher interconnect density, they fabricated UFI- WLCSP with multiple RDL layers. The package with two RDL layers had die size of 10.3 x 10.3 mm2 and ball pitch of 350  $\mu m$  (Figure 2). Again such structures passed all component level reliability testing.

#### References

- http://imapsource.org/doi/abs/10.4071/2010DPCtha32?journalCode=apap

- 2. TI Ejim et. al., "Reliability performance and failure mode of high I/O thermally enhanced ball grid array packages" Electronics Manufacturing Technology Symposium, 1998, p.323 332.

## Fab facilities data and defectivity

At the 4th annual Entegris Yield Forum held during Semicon West, attendees heard from executives representing the world's leading memory fabs discuss manufacturing challenges Among the excellent presenters was Norm Armour, managing director worldwide facilities and corporate EHSS of Micron. Armour has been responsible for some of the most famous fabs in the world, including the Malta, New York logic fab of GlobalFoundries, and AMD's Fab25 in Austin, Texas. He discussed how facilities systems effect yield and parametric control in the fab.

Just recently, his organization within Micron broke records working with M&W on the new flagship Fab 10X in Singapore—now running 3D-NAND—by going from ground-breaking to first-tool-in in less than 12 months, followed by over 400 tools installed in 3 months. "The devil is in the details across the board, especially for 20nm and below," said Armour. "Fabs are delicate ecosystems." Armour gave a few examples of component-level failures that caused major yield crashes.

Ultra-Pure Water (UPW) is critical for IC fab processes including cleaning, etching, CMP, and immersion lithography, and contamination specs are now at the part-per-billion (ppb) or part-per-trillion (ppt) levels. Use of online monitoring is mandatory to mitigate risk of contamination. International Technology Roadmap for Semiconductors (ITRS) guidelines for UPW quality (minimum acceptable standard) include the following critical parameters:

- Resistivity @ 25C >18.0 Mohm-cm,

- TOC <1.0 ppb.</li>

- Particles/ml < 0.3 @ 0.05 um, and

- Bacteria by culture 1000 ml <1.

In one case associated with a gate cleaning tool, elevated levels of zinc were detected with lots that had passed through one particular tool for a variation on a classic SC1 wet clean. High-purity chemistries were eliminated as sources based on analytical testing, so the root-cause analysis shifted to the UPW system as a possible source. Then statistical analysis could show a positive correlation between UPW supply lines equipped with pressure regulators and the zinc exposure. The pressure regulator vendor confirmed use of zinc-oxide and zinc-stearate as part of the assembly process of the pressure regulator. "It was really a curing agent for an elastomer diaphragm that caused the contamination of multiple lots," said Armour.

#### **Semiconductors**

ED KORCZYNSKI, Sr. Technical Editor

cantly degrade fab yield. It is critical to implement a rigorous component testing and qualification process prior to component installation and widespread use. "Don't take anything for granted," advised Armour. "Things like UPW regulators have a first-order impact upon yield and they need to be characterized carefully, especially during new fab construction and fit up."

Photoresist filtration has always been important to ensure high yield in manufacturing, but it has become ultra-critical for lithography at the 20nm node and below. Dependable filtration is particularly important because industry lacks in-line monitoring technology capable of detecting particles in the range below ~40nm.

Micron tried using filters with 50nm pore diameters for a 20nm node process...and saw excessive yield losses along with extreme yield variability. "We characterized pressure-drop as a function of flow-rate, and looked at various filter performances for both 20nm and 40nm particles," explained Armour. "We implemented a new filter, and lo and behold saw a step function increase in our yields. Defect densities dropped dramatically." Tracking the yields over time showed that the variability was significantly reduced around the higher yield-entitlement level.

Airborne Molecular Contamination (AMC) is 'public enemy number one' in 20nm-node and below fabs around the world. "In one case there were forest fires in Sumatra and the smoke was going into the atmosphere and actually went into our air intakes in a high volume fab in Taiwan thousands of miles away, and we saw a spike in hydrogen-sulfide," confided Armour. "It increased our copper CMP defects, due to copper migration. After we installed higher-quality AMC filters for the make-up air units we saw dramatic improvement in copper defects. So what is most important is that you have real-time on-line monitoring of AMC levels."

Building collaborative relationships with vendors is critical for troubleshooting component issues and improving component quality. "Partnering with suppliers like Entegris is absolutely essential," continued Armour. "On AMCs for example, we have had a very close partnership that developed out of a team working together at our Inotera fab in Taiwan. There are thousands of important technologies that we need to leverage now to guarantee high yields in leading-node fabs."

## High-volume processes for nextgeneration biotechnology devices

DR. BERND DIELACHER, DR. MARTIN EIBELHUBER and DR. THOMAS UHRMANN, EV Group, St. Florian, Austria

ver the past several decades, miniaturization has significantly improved clinical diagnostics, pharmaceutical research and analytical chemistry. Modern biotechnology devices—such as biosensors, fully integrated systems for diagnostics, cell-analysis or drug discovery—are often chip-based and rely on close interaction of biological substances at the micro- and nanoscale. Thus, process technologies that enable the production of surface patterns and integration of fluidic components with small feature sizes are needed (**FIGURE 1**).

Microfluidic channels

Photonic and plasmonic structures

Photonic and plasmonic structures

Turn

Turn

Cells

Bacterie

Optical gratings

Pleamonic structures

Hanostructured surfaces

Hanostructured surfaces

Hanostructured surfaces

100 pm

10 pm

10 nm

1 nm

**FIGURE 1.** Biotechnology devices utilize a variety of structures at the micro- and nanoscale that interact with biological substances.

Today's miniaturized biotechnology devices can be found in numerous applications, including fields related to human health as well as environmental and industrial sciences. For example, chemical sensors and biosensors are commonly used to analyze pH values, levels of electrolytes and blood-gas. Glucose sensors are a prominent example of highly successful commercial devices used for diabetes monitoring, where miniaturization has enhanced the development of implantable chips for continuous glucose

level monitoring inside the human body. Fully integrated systems, including micro- and nanopumps for accurate insulin release, have also been shown. In general, such controlled drug delivery systems offer new opportunities for the treatment of common acute and chronic diseases. Moreover, microneedle arrays, which allow minimally invasive and painless delivery of drugs through the skin, neural electrodes for stimulation or monitoring signals inside the brain, or prosthetic devices such as artificial retinas, have also been developed.

Microfluidics plays a key role in the transport and

manipulation of biological fluids in biotechnology devices. For example, laminar flow behavior can be overserved, which allows a well-defined control of liquids. Capillary forces can enable fluid flow without the need of active pumps. In addition, short distances reduce diffusion times of molecules, which lead to faster biological reactions. Overall, microfluidic devices offer a high degree of parallelization while using extremely-low-volume samples. Microfluidic devices

11

that perform complete tasks or analysis, usually done in a laboratory, are referred to as lab-on-chip (LOC) devices. Other names include bio-chips or micro-Total-Analysis-Systems ( $\mu$ -TAS). These systems are used in applications such as in-vitro diagnostics, high-throughput screening, genomics and drug discovery. LOC devices are also ideally suited for point-of-care testing (POCT), where they provide rapid diagnostics at the patient site.

#### **Nanoimprint lithography**

To successfully commercialize such products in a fast growing market with stringent requirements and high

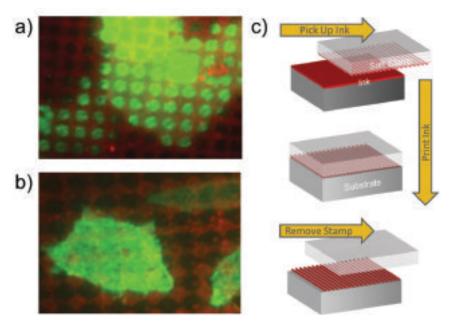

regulatory hurdles, precise and cost-effective microstructuring technologies are essential. Nanoimprint lithography (NIL) has evolved from a niche technology to a powerful high-volume manufacturing method that is able to serve today's needs and overcome the challenges of increasing complexity of microfluidic devices in particular, and biotechnology devices in general. NIL is a patterning technique capable of producing a multitude of different sizes and shapes on a large scale by imprinting either into a biocompatible resist or directly into the bulk material with resolutions down to 20 nm. NIL can be distinguished between three types of imprint technologies: hot-embossing or thermal NIL, UV-NIL, and microcontact printing ( $\mu$ -CP).

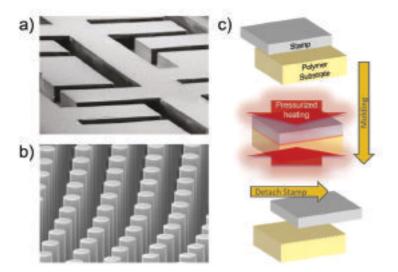

Hot-embossing is a cost-effective and relatively simple process, well suited for the fabrication of polymer microfluidic devices with very high replication accuracy of small features down to 50 nm (FIGURE 2). A polymer sheet or spin-on-polymer is heated above its glass transition temperature, transforming the material into a viscous state. A stamp containing the negative copy of the structures is then pressed into the polymer with sufficient force to conformally mold the polymer. De-embossing is done after cooling the substrate below a certain temperature where the material retains its shape when removing the stamp. During hot-embossing, the structure is transferred by displacement of the viscous material. The process is characterized by short flow paths of the material, moderate flow velocities and imprinting temperatures. Residual stress is therefore low, especially when comparing the process to injection molding, which is an alternative production technique for microfluidics.

Because of the much higher process temperatures and pressures associated with injection molding, final products produced by this process usually experience higher internal residual stress, which easily results in significant deformation, such as warpage and shrinkage. In addition, a surface solidification layer is formed at the interface of the cold mold during the injection of the high-temperature molten polymer. This effect significantly influences the replication accuracy and optical quality. Extensive effort in process development and simulation is therefore often necessary for injection molding to replicate small features in an accurate manner. In contrast, hot-embossing allows precise replication of micro- and nanostructures with less effort and is superior when replicating high-aspect ratio features or when using very-thin substrates. Structures with high-aspect ratios are often needed in microfluidic chips for filtration elements, particle separation or cell sorting.

The ability to use very thin substrates enables the patterning of spin-on-polymer layers on top of other

**FIGURE 2:** a) 200-μm wide microfluidic channels and b) 10-μm pillar arrays with high aspect ratios (7:1) fabricated by hotembossing (Courtesy of National Research Council Canada). c) Schematic drawing of hot-embossing process flow.

materials or even roll-to-roll embossing using polymer foils for very-high-throughput production. Parallel wafer-based batch processing also enables fabrication of typical-sized microfluidic chips with throughputs comparable to or even higher than injection molding or similar techniques. Since master stamps for hot-embossing do not need to withstand the high temperatures and forces required for mold inserts for injection molding, they are less expensive to produce. Therefore, hot-embossing is also a well suited technology for R&D and allows easier design changes in volume-production.

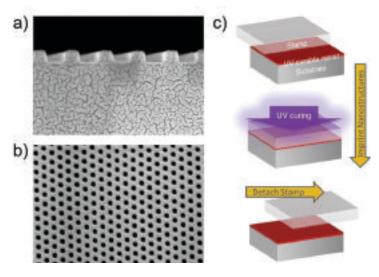

**FIGURE 3:** (a) 100-nm grating with residual layer <10 nm imprinted into 90 nm height resist on silicon substrate and (b) 350-nm photonic crystal fabricated by UV-NIL. c) Schematic drawing of UV-NIL process flow.

UV-NIL refers to a technique where a transparent stamp is pressed into a photo-curable resist and cross-linked by UV-light while still in contact (**FIGURE 3**). In biotechnology applications, the resist is usually coated onto silicon or glass substrates. Unlike hot-embossing, the UV-NIL stamp is brought in contact with the resist using minimum force to conformally join the stamp and substrate. The different mechanisms of curing and stamp attachment account for different advantages and fields of application of the respective technologies.

UV-NIL provides very-high-alignment accuracy, pattern fidelity, and throughput whereas hot-embossing is capable of imprinting higher aspect ratios and larger structures in the upper micron range as well as combinations of microand nanostructures. UV-NIL offers additional opportunities for biotechnology devices where features with ultrahigh precision are needed. Examples include optical-based biosensors that often rely on noble metal nanostructures that influence properties of coupled light upon the binding of molecules onto the nanostructures. Regardless of what

the sensing principle is based on (e.g. localized surface plasmon resonance or photonic band gaps), small changes in shape and size can significantly alter the properties of the sensing element.

In order to produce nanostructures made of metals, either additive or subtractive processes can be used. The former involves the deposition of a metal layer onto the patterned resist followed by a lift-off process, whereas the latter involves the transfer of the pattern into an underlying metal layer by etching processes. In both cases, the small residual layer must first be removed. Having a uniform residual layer is of high importance, especially for subsequent etching processes, and can be easily achieved with current equipment over large areas. Imprinted UV-NIL resists can also be used directly as functional layers. After many years of continuous resist development, a broad portfolio of optimized resist materials is available for various bio-applications. Another interesting aspect, especially for microfluidic devices, is the potential of nanostructures to influence surface properties. For

#### **Cure Ovens for Dielectric Polymers**

## The Equipment You Want For the Results You Need!

#### Superior yields with:

- Excellent thermal, electrical and mechanical properties

- Reliable multi-level interconnections

- Proper cross-linking

- No stress

- No cracking or lifting

- Low cost of ownership/FAST ROI

YES-VertaCure YES-PB Series

www.yieldengineering.com 1.888.YES.3637

13

**FIGURE 4:** Bio-functionalized, micro-patterned array created by micro-contact printing for the detection of protein-protein interactions in live cells. a) Antibody-patterns induce the recruitment of two interacting proteins to micro-patterns, which is detected by fluorescence microscopy. b) Missing interaction of the two candidate proteins leads to homogenous distribution on the functionalized surface. c) Schematic drawing of micro-contact printing process flow. [Images adapted from Schwarzenbacher et al., 2008, Nature Methods; Weghuber et al., 2010, Methods in Enzymology].

example, nanostructures can change the surface behavior from hydrophilic to hydrophobic, which can be used to locally influence the fluid flow.

Hot-embossing / UV-HIL imprinted Substrate Bending

Single Devices Singulation Bonded Substrate

**FIGURE 5:** Large-area parallel processing offers significant advantages in terms of cost and flexibility. Additional processes, such as electrode fabrication or spotting of reagents, can also be efficiently integrated.

While UV-NIL is ideally suited for fabricating very small features, it is not well suited for features larger than several tens of micrometers. In cases where both highly-accurate nanostructures and large microfluidic channels are needed, hot-embossing can be used to imprint the channels on a separate substrate. The two substrates can subsequently be bonded together to produce the final device.

A third NIL option is  $\mu$ -CP, where a pre-inked stamp is used to transfer materials such as biomolecules onto a substrate in a distinct pattern (**FIGURE 4**). Local modification of surface chemistry can, for example, be used to guide the growth of neurons on a chip. On the other hand, it can be used for the precise placement of capture molecules in biosensor

fabrication. This technique is applicable on all common surfaces, such as silicon, glass or polymers with microand nanometer resolution and offers new possibilities for functionalization of biotechnology devices.

Although most current microfluidic devices do not follow the same degree of miniaturization in terms of chip-size compared to the microelectronics industry, large-scale parallel processing has a significant advantage in terms of costs and flexibility (**FIGURE 5**). Alternative fabrication techniques for microfluidic chips, such as injection molding, are principally serial processes and have limitations in up-scaling. Using nanoimprinting, 30 chips of the size of a microscopy slide (25 x 75 mm) can easily fit on a single 300-mm substrate. This format can be considered

a good reference for an average-sized microfluidic chip. In terms of throughput, wafer-based batch processing is able to reach similar or better cycle times per device compared to alternative solutions, such as injection molding. UV-NIL has even been introduced on GEN2 substrates  $(370 \times 470 \text{ mm})$ . In addition, roll-to-roll processing can reach even higher throughput levels but is restricted to the structuring of flexible foils.

#### Wafer bonding

NIL has an additional advantage in terms of postprocessing. Electrode fabrication, surface treatments or spotting of bio-reagents can be efficiently integrated in a large-area batch. The same is true for sealing and

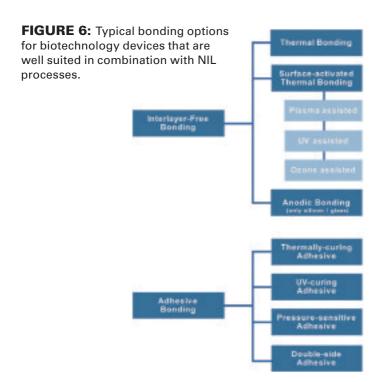

encapsulation, an essential process step for all biotechnology devices. It is usually mandatory to close microfluidic channels, to fabricate a hermetic sealing for protection against environmental influences or even to provide packaging that is compatible for implantation into human bodies. In addition, interconnections to the outer world have to be incorporated, such as holes or fluidic connectors. Electronic connections or assembling the device together with an integrated microelectronic chip is also often necessary. Thus, bonding of different device layers, capping layers or interconnection layers is a key process that can be implemented together with NIL in a cost-effective large-area batch process. NIL has an additional advantage of providing a high surface quality that can significantly improve subsequent bonding of polymer devices. Surface roughness, total-thickness variation as well as warpage are usually lower than in devices fabricated by injection molding. In the following section, several well-suited bonding processes for sealing biotechnology devices are discussed (FIGURE 6).

#### **2016 SEMICONDUCTOR PACKAGING**

# ROADMAP SYMPOSIUM 11.14.2016

MEPTEC INITIATES COLLABORATION WITH HETEROGENEOUS INTEGRATION ROADMAP

MONDAY, NOVEMBER 14, 2016 | SAN JOSE, CALIFORNIA

SYMPOSIUM 8:00AM - 5:00PM | EXHIBITS 9:30AM - 6:30PM | RECEPTION 5:00PM - 6:30PM

REGISTER TODAY AT MEPTEC.ORG/ROADMAPS

A common requirement in biotechnology applications is optical transparency, at least from one side, since most devices rely on optical readouts. Glass is therefore often used as a capping layer for highly complex devices made of silicon. In such cases, anodic bonding can provide a high-quality hermetic seal, where bonding is achieved by high voltage and heat causing inter-diffusion of ions. Another process for joining glass or polymer devices is thermal bonding using high temperatures and pressures. Special attention has to be paid when using this technique for bonding polymer and, in particular, polymer microfluidic devices. Thermal bonding is performed by heating the substrate near or above the glass transition temperature, which softens the material. The additional pressure generates sufficient flow of polymer at the interface to achieve intimate contact and inter-diffusion of polymer chains. Pressure is removed after the substrate is cooled down to a specific value below the glass transition temperature. Un-optimized temperature and pressure can easily lead to deformation of microstructures. Plasma as well as UV and ozone treatment can be used to activate the polymer surface, which allows bonding at reduced temperatures and reduces the risk of deformation. Anodic and thermal bonding are interlayer-free processes and therefore do not introduce any additional material to the device.

Adhesive bonding is another process that found widespread use in sealing or encapsulating bio-technology devices. Many biocompatible adhesives are available today and high bond strength can be expected from this technique. Bonding with adhesives can be used to join many different materials. Often liquid adhesives are used, which can be cured thermally or by exposure to UV light. The latter offers a significant advantage that addresses another important issue in many pharmaceutical or diagnostic devices where bio-molecules have to be incorporated before sealing the device. UV-curing allows bonding at room-temperature whereas higher temperatures usually lead to denaturation or complete destruction of bio-molecules.

Adhesives usually have to be selectively deposited on the substrate, which can be achieved with  $\mu$ -contact printing. Similar to bio-molecule printing, an adhesive can be transferred onto the substrate according to the pattern of the stamp. In contrast, however, an adhesive can be spin

16

coated onto a transfer plate, which is then brought into contact with the substrate. By releasing the transfer plate, the adhesive will remain on the heightened structures. This production process is an elegant solution for microfluidic devices where micro-channels stay free of adhesive without the need for alignment. With these methods the adhesive can be coated as a thin layer (typically on the order of several microns) with very good uniformity over large areas. Commercially available adhesive tapes offer another solution, which can be easily laminated onto the microfluidic chips either in the form of double-sideadhesive tapes or pressure-sensitive-tapes. By using this process, the tape covers the top of microfluidic channels and can alter chemical or physical parameters of the channels, which can then influence the fluidic behavior or biological function of the device. Due to the availability of a variety of different tapes, however, such influences can be addressed and eliminated in many applications.

#### **Summary**

Micro- and nanotechnology combined with biotechnology has the potential to revolutionize many areas of healthcare, agriculture and industrial manufacturing. The market for miniaturized bio-devices is rapidly growing with technologies becoming increasingly complex. For successful translation of these technologies into new products, the availability of fabrication tools is key. Today's NIL equipment offers a well suited solution, where complexity in design does not necessarily add manufacturing cost. Together with sealing and bonding processes that are well aligned with these structuring techniques, limitations of current fabrication methods can be overcome to enable the production for next-generation biotechnology devices.

#### **Further reading**

- T. Glinsner and G. Kreindl, "Nanoimprint Lithography," in Lithography, M. Wang, Ed. InTech, 2010.

- T. Glinsner, T. Veres, G. Kreindl, E. Roy, K. Morton, T. Wieser, C. Thanner, D. Treiblmayr, R. Miller, and P. Lindner, "Fully automated hot embossing processes utilizing high resolution working stamps," Microelectron. Eng., vol. 87, no. 5–8, pp. 1037–1040, May 2010.

- G. Kreindl, T. Glinsner, and R. Miller, "Next-generation lithography: Making a good impression," Nat. Photonics, vol. 4, no. 1, pp. 27–28, Jan. 2010. ◆

SEPTEMBER 2016 SOLID STATE TECHNOLOGY www.solid-state.com

## Deep dive into the Intel/ Micron 3D 32L FG-NAND

**JEONGDONG CHOE**, Ph. D., Senior Technical Fellow at TechInsights, Ottawa, Canada

Key features of the cell structure, design and integration of the Micron 3D 32L FG-NAND device are discussed, and compared with Samsung's 32L and 48L V-NAND device.

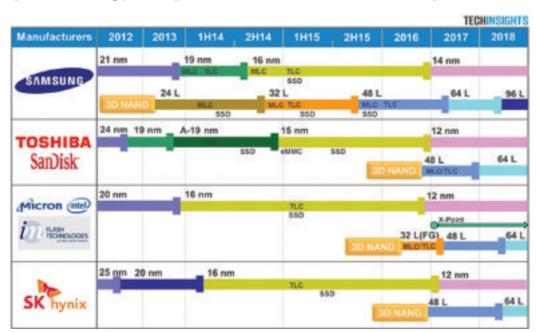

he Intel/Micron 1st generation 3D TLC NAND with FG (floating gate) structure is finally on the market. TechInsights has torn down Micron's Crucial MX300 750 GB 2.5-inch SSD and reverse engineered Micron's 3D FG-NAND. The SSD has eight 3D NAND packages with 6FB22 NW852 package markings on the board, and two NAND dice in each package. We discuss some key features of the cell structure, design and integration of the Micron 3D 32L (32 layers or 32T, 32 Tiers) FG-NAND device, and compare with Samsung's 32L and 48L V-NAND device.

#### Die size and memory density

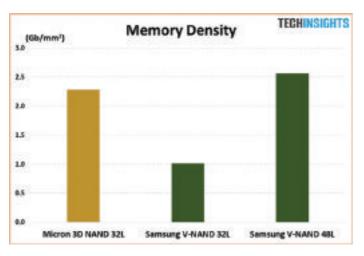

Micron's 32L 3D NAND die size (168.2 mm2) is much larger than Samsung's 32L (84.3 mm2) and 48L (99.8 mm2) 3D V-NAND devices. Micron's 32L 3D NAND memory size is 48 GB/die (384 Gb/die) which is more than 4 times

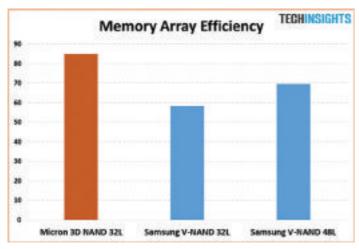

**FIGURE 1.** A comparison of memory density on Intel/Micron 3D 32L NAND, Samsung 3D 32L and 48L NAND.

Samsung 32L V-NAND (85.3Gb/die) and 1.5 times their 48L V-NAND (256 Gb/die). In other words, the memory density for the Intel/Micron 32L 3D NAND is 2.28 Gb/ mm2, while Samsung's 32L V-NAND and 48L V-NAND are 1.01 Gb/mm2 and 2.57 Gb/mm2, respectively. **FIGURES 1** and 2 show comparisons of memory density and memory array efficiency for the Micron 32L, Samsung 32L and 48L 3D NAND memories. Micron's 2.28 Gb/mm2 memory density is the same as their announcement in 2015 at IEEE IEDM. They announced another 3D NAND with 768 Gb/ die TLC (which is 4.29 Gb/mm2) earlier this year at ISSCC 2016. We can find a gap between the two announcements, including memory density difference (2.28 Gb/mm2 and 4.29 Gb/mm2). They might further shrink bitline pitch to 40 nm or expand to 48 layers. Comparing the 32L 3D NAND devices, the memory density on Intel/Micron's 1st generation 3D NAND is more than two times Samsung's 32L 3D NAND. Although Micron jumped into the 3D NAND race two years later than Samsung, Micron beat Samsung's 32L 3D NAND devices and came close to Samsung's 48L ones by using CMOS circuit under the memory array. We're looking forward to seeing their 2nd generation (either a modified 32L or a new 48L) FG-NAND.

#### 3D memory cell architecture

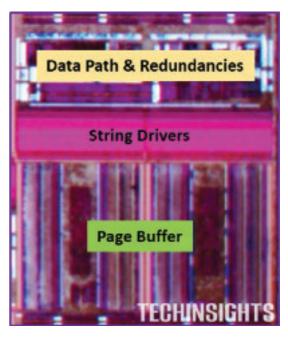

As shown on **FIGURE 3**, the Intel/Micron 1st generation 3D FG-NAND (32L or 32T) has 4 planes with 32 tiles; while Samsung's 3D V-NAND, either 32L (2nd generation) or 48L (3rd generation), has 2 planes without a tile-like floor plan. An innovative technology from Micron is that CMOS decoders and sense-amps are sitting under the 3D FG-NAND memory array for high memory density (2.28 Gb/mm2). Referring to the memory tiles comprised of page buffer (PB), string drivers and CMOS circuits, the area of

17

**JEONGDONG CHOE** has more than 20 years of experience of semiconductor process and device integration including NAND Flash, DRAM, logic and advanced memory devices at Samsung and SK-Hynix. He works at TechInsights as a senior technical fellow focusing on memory/logic products, architecture, roadmap and technology.

**FIGURE 2.** A comparison of memory array efficiency on Intel/Micron 3D 32L NAND, Samsung 3D 32L and 48L NAND.

unit memory tile is 4.12 mm2. The 1 kB page buffer, string drivers and other CMOS circuits on each memory tile have 2.20 mm2, 0.83 mm2 and 1.09 mm2 areas, respectively (**FIGURE 4**). As Micron mentioned at ISSCC 2016, placement of the wordline drivers under the array allows for the wordline lengths to be short.

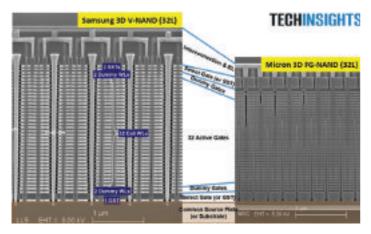

Micron's 32L 3D FG-NAND uses a 4 metal CMOS plus FG-NAND array on common source plate technology. The FG-NAND array has 32 active wordlines, 6 dummy wordlines (3 on the top portion and 3 on the bottom portion), one source-side select gate and one drain-side select gate. All of the wordlines and select gates are on a Si/W-silicide-based common source plate. The NAND array has 40 gates (38 wordlines plus 2 select transistors), which is different from Samsung's 32L V-NAND which has 39 gates (36 wordlines plus 3 select transistors).

Micron's V-NAND uses a vertical Si-channel surrounded by a floating gate (FG) and a control gate (CG), termed a 'gate all around (GAA)' structure. The vertical Si-channel and control gate stacked memory cell structure is the same as Samsung's, however, Micron uses a silicon FG (floating gate) layer instead of Samsung's SiN charge trap

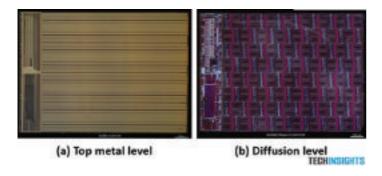

FIGURE 3. Top metal level and Diffusion level of Micron 3D 32L NAND die

FIGURE 4. Memory tile layouts on Micron 3D 32L NAND die.

layer (CTL). The FG layer is far better way to store more electrons than a SiN layer. Micron's 52 nm 32L NAND array vertical cell gate pitch is less than Samsung's 60 nm 32L V-NAND vertical cell gate pitch. Micron's memory cell array (or Si-channel hole) height is 2.21  $\mu m$ , which is 27% lower than that of Samsung 32L (2.9  $\mu m$ ).

Micron's 3D FG-NAND cell architecture has a 'CG/FG first, Channel last' scheme, while Samsung's 3D V-NAND cell integration has a 'Channel first, Gate last' scheme. Micron's process involves first making the control gate/dielectric stack. A recess etch would have been used to form cavities for the polysilicon floating gates (FG) and inter-poly dielectrics. The deposition of the tunnel oxide and polysilicon channel would complete then NAND string. An etch-back processes is applied for both CG and FG structures to recess and isolate the gates.

Micron's 2D 16 nm node planar thin-FG NAND Flash has a select gate with the same structure as the cell, which has a high-k dielectric stack and a thin polysilicon floating gate. To simplify the manufacturing of the 16 nm cell, the source and drain select gates are constructed in a similar manner as the cell. In contrast, Micron's 3D FG-NAND device has a select gate composition that is different from cell gate. Here, the source and drain select devices are single gate oxide transistors.

Placing the select gates and dummy wordlines under and on the memory cell gates looks reasonable from an integration perspective. Intel/Micron and Samsung have the same configuration of dummy wordlines near the select transistors, but Samsung has a SEG (Si epitaxial growth) channel on GST (ground select transistor) structure. Micron uses a single select gate with a thick gate length (thickness) on the drain side, while Samsung has two thin SSTs (string select transistors). **FIGURE 5** shows a comparison of 3D cell gate structure on Samsung and Intel/Micron 32L NAND devices.

**FIGURE 5.** A comparison of 3D cell gate structure on Samsung and Intel/Micron 32L NAND devices.

#### 3D NAND competition and roadmap

When Micron will produce 48L 3D FG-NAND commercial products is an open question. **FIGURE 6** shows a NAND roadmap for the major players of 3D NAND products (Samsung, Micron/Intel, Toshiba/SanDisk and SK-hynix). Samsung has 48L V-NAND SSD products and they are developing 64L for their next generation 3D V-NAND. Samsung has been more focused on 3D V-NAND development including yield improvement and 64L V-NAND

than next generation 2D NAND (1z nm). Intel/Micron have just entered the V-NAND race with their 32L FG-NAND. Once they successfully release 48L and 64L, if in a timely manner, they may gain market share at the expense of Samsung, Toshiba and SK hynix. Toshiba and SanDisk are scheduled to release their 3D BiCS NAND products to compete in the 3D NAND sector soon.

Intel/Micron's 1st generation 3D FG-NAND devices with 32L (or 32T) are quite compatible with Samsung's 32L 3D V-NAND. Samsung and Toshiba use a CTL (charge trap layer), while Micron adopted thin-FG silicon layer as a storage between channel and CG. Although Micron's thin-FG layer contains more electrons than Samsung's CTL SiN layer, the etch-back process used to isolate the FG layers may result in non-uniform FG sizes and coupling ratios. Furthermore, the FG layer is getting smaller and may form nanowire-like or nanodot-like structures on the Si cylinder during the process integration creating performance non-uniformities. Samsung's CTL scheme does not suffer as much from process non-uniformities giving it an advantage. Additionally the CTL does not require isolation between each of the stacked cell gates.

Which is better? Intel/Micron's 32L 3D FG-NAND or Samsung's 32L (or 48L) 3D V-NAND? From the memory cell structure and process integration viewpoints, Samsung looks better than the Intel/Micron design due to the CTL scheme. From the die efficiency and memory density viewpoints, Intel/Micron's CMOS circuit layout under the memory array has an advantage over Samsung's conventional die floor plan. Should Micron scale down the bitline pitch from 80 nm to 40 nm, it would be a memory

density advantage to them. We can discuss further after circuit, device and waveform analyses on Intel/Micron's 3D NAND devices. ◆

19

FIGURE 6. NAND technology roadmap.

## CMP slurry optimization for advanced nodes

ADAM MANZONIE, TODD BULEY, JIA-NI CHU and MIKE KULUS, CMP Technologies, Dow Electronic Materials, Newark, DE

As advanced device manufacturers identify needs for new and additional CMP steps, new slurry solutions can deliver exceptional planarization and defectivity within a stable CMP process.

dvanced logic and memory device nodes demand significantly greater performance from chemical mechanical planarization/polishing (CMP) processes. Due to the fast growing number and increased diversity of non-metal CMP steps, new requirements are emerging, such as enhanced planarization efficiency, near-zero level defectivity and substantial reductions in process cost versus previous device nodes. Highly tunable and dilutable CMP slurries, in conjunction with matched CMP pads and processes are needed to achieve both technical and economic objectives. In advanced front-end-of-line (FEOL) processing, a variety of new CMP steps for different layer combinations, such

as oxide, nitride and polysilicon, need to be polished and each layer requires different rates, selectivities and tight process control.

These varied requirements necessitate new slurry formulations. A new family of dielectric CMP slurries will be examined, which uses state-of-the-art colloidal silica abrasives paired with advanced additives to offer high removal rates, planarization efficiency and exceptionally low defect levels. These newly commercialized slurries are offered to customers in concentrate form to minimize overall cost-of-ownership (CoO). Point-of-use dilution minimizes abrasive

20

concentration without sacrificing CMP performance and process stability.

#### CMP technical trends and challenges

The semiconductor industry continues to see growth in both logic and memory chip demand, driven by expanding applications in segments such as mobile, server, data processing, communications, consumer electronics, industrial and automotive. Scaling and cost reduction to extend Moore's Law continue to drive the needs for new transistor/device architectures and technologies like 3D FinFETs, 3D NANDs and 3D packaging. CMP is a critical enabler to deliver these technologies.

In advanced logic nodes, there are an increased number of CMP layers (e.g., 22-28 layers at 7nm compared to 12 layers

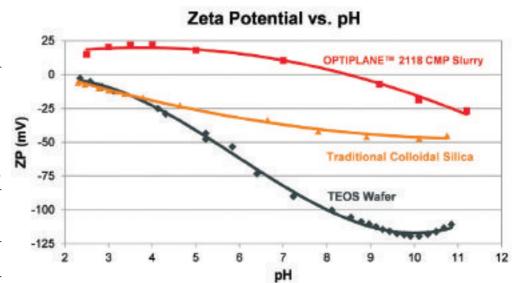

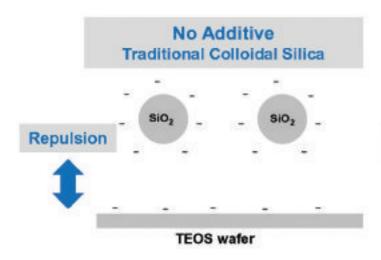

**FIGURE 1.** Zeta potential compared against pH for OPTIPLANE™ 2118 CMP slurry, traditional colloidal silica slurry and a TEOS wafer.

All authors are with CMP Technologies, Dow Electronic Materials. **ADAM MANZONIE** is Global Business Director, Slurry, **TODD BULEY** is Global Slurry Applications Director, **JIA-NI CHU** is Slurry Marketing Manager, and **MIKE KULUS** is Strategic Marketing Director.

SEPTEMBER 2016 SOLID STATE TECHNOLOGY www.solid-state.com

for 45nm). New technologies and material layers have not only offered additional opportunities but also presented new challenges for CMP consumables and tool sets [1].

In addition to low defectivity and reduced cost-of-ownership, key performance drivers such as planarization efficiency (PE), erosion, and dishing must have tight process control with-in-die (WID) and with-in-wafer (WIW) uniformity. New innovations are needed for these emerging requirements.

In advanced logic processes, the Polysilicon Open Polish (POP) requires nitride and oxide removal to then stop on polysilicon [2]. There is a need for a tunable slurry and stable pad life to enable low gate height variation and dishing. Self-Aligned Contacts (SAC) processes require polishing nitride and stopping on oxide; this necessitates use of a highly-selective slurry (nitride: oxide selectivity > 50:1). Multiple buff steps may be needed to generate nitride residual free surfaces, making a tunable slurry a good solution. Polysilicon gate CMP polishes amorphous- or polysilicon and stops in the same film. Gate height variation across the wafer is critical. Managing final thickness requirements through end-pointing is very challenging; preferably, it requires a pad/slurry process with some level of self-stopping and with high planarization efficiency for gate height control and low surface roughness. With shallow trench isolation (STI), since the needle-like structure fins are getting thinner and taller, there is a need for slurry with extremely high selectivity (>100:1 Ox: SiN) to minimize the nitride loss. New flowable CVD (FCVD) films used for gap-fill (e.g., in STI processes) are sensitive to deposition and annealing, and could cause high defectivity (particles) and rate instability.

Advanced memory applications are also incorporating additional CMP process steps (e.g., buff steps may be performed in a one-platen process with hard pads for improved defectivity and global uniformity after an etch step). There are enormous technical challenges to enable further scaling of current DRAM cell size. With the need for additional CMP steps, DRAM processes continue to demand higher removal rates to enable greater throughput and reduce overall CoO.

For advanced nodes, one consistency is that there are additional new CMP steps for both logic and memory (primarily 3D-NAND). Slurries with significant, characterized tunability, enabling low defectivity and a lower CoO, are required for multiple applications.

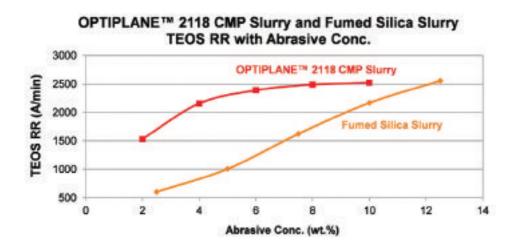

#### **New slurry formulations**

Semiconductor manufacturers rely on strong collab-

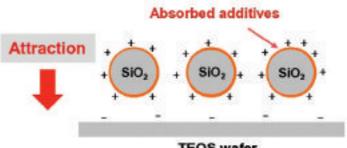

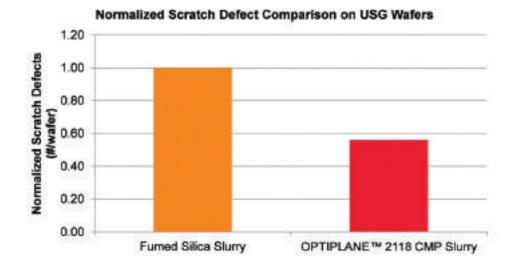

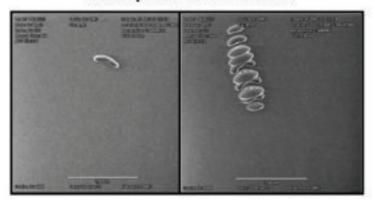

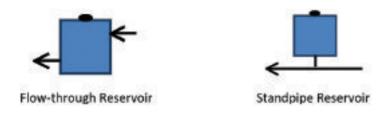

oration with materials suppliers to identify or develop slurries that meet these new specific and stringent requirements. As an example, Dow has recently developed slurry options that address higher oxide removal, lower defectivity and lower cost-of-ownership in both  $\leq 20$ nm DRAM and  $\leq 28$ nm logic applications. For  $\leq 14$ nm logic applications, different process requirements warranted an oxide slurry with high planarization efficiency and step height reduction combined with good polysilicon and nitride removal rates.