NOVEMBER 2012

## SOM SIGNE TECHNOLOGY Insights for Electronics Manufacturing

Improving LED Yield P. 18

**ECHNOLOGY**

The Scare of Overcapacity P. 26

TSMC'S CoWoS p. 28

## IEDM Preview: 20nm and Below R.14

www.solid-state.com

PennWell

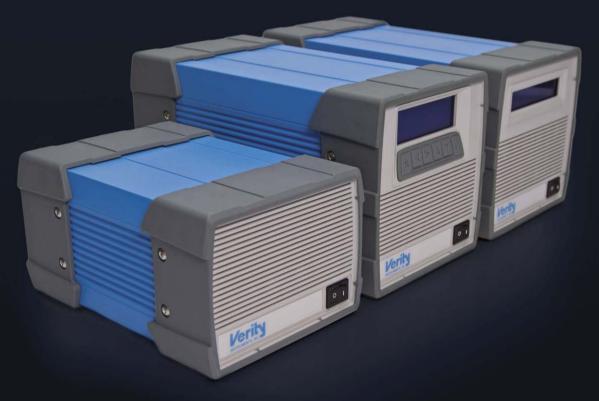

## We've gone the extra mile so you don't go the extra nanometer.

#### THE NEXT GENERATION HAS ARRIVED.

Introducing the latest additions to the Verity family of smart spectrometers featuring the SD1024X, a new industry standard that combines spectrometer and PC in the same space, eliminating the need for a dedicated applications computer. The new SD1024G Series delivers improved capability with industry leading ultra-performance, general purpose, and high resolution model options. Coupled with the compact FL2100 flashlamp module the new series addresses the broadest range of challenging plasma and film thickness/etch depth endpoint control problems. Now, more than ever, the first name in endpoint detection is the last word in performance. **Learn more at www.Verityinst.com**.

Zoom in | Zoom out

For navigation instructions please click here

MEMS

Search Issue

Next Page

SEMICONDUCTORS

LEDS • DIS

DISPLAYS

NOVEMBER 2012

# SOCIAL STREET

PACKAGING

Improving LED Yield P. 18

The Scare of Overcapacity P. 26

TSMC'S CoWoS p. 28

## IEDM Preview: 20nm and Below P.14

www.solid-state.com

Zoom in

Contents

PennWell

### Solid State Equipment LLC

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

ADVANCED PACKAGING SINGLE WAFER WET PROCESSING

#### TSV RESIST STRIP AND CLEAN

As received - post DRIE

After SSEC Cleaning

As received - post DRIE

After SSEC Cleaning

As received - post DRIE

ISIS 3D

#### Si ETCH TO REVEAL Cu TSV

DRY FILM STRIP

FLUX CLEANING

UBM Post Etch

UBM Post Strip

ssecusa.com

© 2012 SOLID STATE EQUIPMENT LLC

ECHNOLOGY

After SSEC Cleaning

dState CHNOLOGY Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

NOVEMBER 2012 VOL. 55 | NO. 9

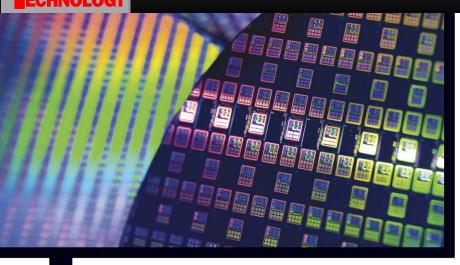

Processed wafers add a near-magical quality to reflected light. Source: TSMC.

#### FEATURES

## As the industry works to perfect 28 and 22nm devices now in volume manufacturing, attention must turn to next-generation 14nm, 10 nm and 7nm technologies presently in development. Those to be presented at IEDM are previewed. *Pete Singer, Editor-in-Chief*

**TRANSISTORS** [IEDM preview: 20nm and below

**LED MANUFACTURING** | Automated data analysis improves yield of MOCVD epitaxial process in LED manufacturing Integration of collection and analysis are vital. *Mike Plisinski, Data Analysis & Review Business Unit, Rudolph Technologies Inc., Tewksbury, MA*

## **EMERGING TECH** | New CMP process holds promise of lower costs, improved efficiencies

Implementing third-generation low-abrasive copper slurry. *Christopher Eric Bannon, Texas Instruments Inc., Dallas, TX*

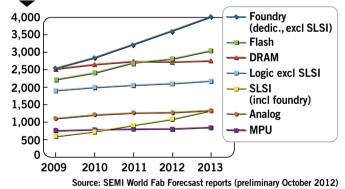

#### FORECAST | The scare of overcapacity

How changes in capex affect fab capacity. *Christian Gregor Dieseldorff, SEMI Industry Research & Statistics, San Jose, CA*

## **PACKAGING** | CoWoS process cuts power, boosts performance, shrinks footprint

A silicon wafer with TSVs is used as a carrier to integrate multiple chips in a single device to reduce power, improve system performance, and reduce form factor. *Jerry Tzou, TSMC, Hsinchu, Taiwan*

#### COLUMNS

- **4** Editorial | Forecast for 2013, Pete Singer, Editor-in-Chief

- **12** Packaging | IMAPS 2012: A Review, Dr. Phil Garrou, Contributing Editor

- **13** MEMS | Semiconductors and Healthcare Converging, Pete Singer, Editor-in-Chief

- **32** Industry Forum | New level of repeatability required for 3D NAND, *Jeff Marks, Lam Research Corp.*

#### DEPARTMENTS

- **2** Web Exclusives

- 6 News

- **30** New Products

- 31 Ad Index

SOLID STATE TECHNOLOGY NOVEMBER 2012

1

## online@<u>www.solid-state.com</u>

#### Web Exclusives

#### EUV Symposium takeaways

Reporting from the International Symposium on Extreme Ultraviolet Lithography, industry analysts and host imec gauge the pace of improvements in EUV lithography and its long march toward production readiness. Bottom line: Progress is still slow and steady, but much improvement is expected in early 2013 with the next generation of tools. <u>http://bit.ly/SPoip9</u>

## European consortia, ASML, supplier network plan for 450mm transition

At SEMICON Europa, European government representatives, consortia, and suppliers discussed programs to support and participate in the 450mm wafer-size transition — including a comprehensive presentation from ASML about its roadmap for 450mm EUV platforms. http://bit.ly/Ve840o

#### **Process Watch:**

2

CHNOLOGY

#### Taming the overlay beast

Experts from KLA-Tencor discuss overlay registration and new capabilities to align to buried layers. <u>http://bit.</u> Iy/PIWxts

#### LED industry shifting production to 6-inch wafers

Driven by market demand and cost-savings goals, the semiconductor industry is progressing toward consensus on building-block standards for automating LED production on 6-in wafers, writes Paula Doe in *SST*'s sister magazine *LEDs Magazine*. <u>http://bit.ly/PKsoOp</u>

#### Moving forward with Moore's Law: Throughput of EUVL scanners

Dr. Vivek Bakshi asks: How much do we need to increase EUV throughput, what must be done to accomplish that, and how quickly can it be achieved? http://bit.ly/SPMoQA

#### Insights from the Leading Edge

Dr. Phil Garrou takes a closer look at some of the 3D and advanced packaging papers presented at the recent 45th Symposium on Microelectronics (IMAPS 2012). <u>http://bit.ly/</u> <u>OdGR08</u>

#### MEMS in medical, quality-of-life

Karen Lightman from the MEMS Industry Group talks with Freescale Semiconductor's Jeannette Wilson about a panel discussion at the MEMS Executive Congress. <u>http://bit.</u> Iy/RNxbmy

#### GlobalFoundries' 14nm finFET "eXtreme Mobility" process

Chipworks' Dick James digs into the technical details of GlobalFoundries' 14nm finFETs, and how they stack up against what Intel and TSMC will be offering. http://bit.ly/QR5OZ0

NOVEMBER 2012 SOLID STATE TECHNOLOGY

ECHNOLOGY

### Omage

## Residual Gas Analyzers ...

### ... starting at \$3750

#### • 100, 200, 300 amu models

- Sensitivity to 5 x 10<sup>-14</sup> Torr

- Better than ½ amu resolution

- Dual ThO<sub>2</sub>Ir filament

- Long-lasting electron multiplier

- 6 decades of dynamic range

Residual Gas Analyzers from SRS are designed to handle the toughest environments from basic research to semiconductor process monitoring. Thousands of SRS RGAs are in use worldwide, and have earned us a reputation for producing quality vacuum instrumentation at reasonable prices.

Our RGAs have greater dynamic range, higher resolution and better linearity than competitive models, and are easier to use. In addition, a dual ThO<sub>2</sub>Ir filament and a unique four channel electron multiplier give SRS RGAs a longer lifetime than other designs.

Simply put, SRS RGAs offer better performance and value than any other system.

1.0 1

0110

1.0×10

SRS Stanford Research Systems

ECHNOLOGY

#### (408)744-9040 www.thinkSRS.com

Analog Scan

X = 18.2 Y = 1.05e-01

Log every scan 1/50

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

#### editorial

## Forecast for 2013

Nobody can predict the future, of course, but 2013 is shaping up to be a good year for the semiconductor industry and its suppliers. According to SEMI, total fab spending for equipment needed to ramp fabs, upgrade technology nodes, and expand or change wafer size could increase 16.7 percent in 2013 to reach a new record high of \$42.7 billion. The estimate includes new equipment, used equipment, or in-house equipment but excludes test assembly and packaging equipment (which, if included, would bring the number up to about \$50 billion). The market for semiconductor manufacturing materials, which was \$48.6 billion this year, is expected to grow 4% to more than \$50 billion in \$2013.

There's been some hand-wringing in 2012 about

I'm bullish on opportunities in healthcare, such as body area sensor networks

continued consolidation and the number of companies that will be moving to 450mm: most pundits guess that only 5-7 companies will be able to make the move. However, that's a limited view of the industry, since there are hundreds of facilities around the world cranking out

chips, LEDs, optoelectronics, power devices, MEMS and other components. The latest edition of the SEMI World Fab Forecast lists over 1,150 facilities (including 300 opto/ LED facilities), with 76 facilities starting production in 2012 and in the near future.

There's sure to be much talk in 2013 about technology requirements at the leading edge, including the 450mm transition, progress in EUV, 3D integration and FinFET optimization. Sustainability will be key, with an emphasis on reducing power consumption, which means lower leakage currents and reduced Vdd.

The demand for semiconductors will never be higher, particularly as the middle class rise on dominance in places such as Brazil, Russia, India and China. First on the wish list it seems, after shelter, food and clothing, is a smart phone.

After a trip to imec in Leuven, Belgium, I'm particularly bullish on opportunities in healthcare, which range from body area sensor networks to amazingly advanced labs-on-a-chip that can screen 20 million blood cells per second to find a single tumor cell in 5 billion blood cells. It is these kinds of applications that could lead to a new revolution in how electronics are designed and manufactured.

-Pete Singer, Editor-in-Chief

#### Solid State =CHNOI

Susan Smith, Group Publisher Ph: 603/891-9447, susans@pennwell.com Pete Singer, Editor-in-Chief Ph: 603/891-9217, psinger@pennwell.com James Montgomery, News Editor Ph: 603/891-9109, jamesm@pennwell.com Robert C. Haavind, Editor-at-Large Ph: 603/891-9453, bobh@pennwell.com Julie MacShane, Copy Editor Phil Garrou, Contributing Editor Michael Fury, Contributing Editor Justine Beauregard, Marketing Manager Cindy Chamberlin, Presentation Editor Katie Noftsger, Production Manager Dan Rodd, Illustrator

Debbie Bouley, Audience Development Marcella Hanson, Ad Traffic Manager

EDITORIAL ADVISORY BOARD John O. Borland, J.O.B. Technologies Michael A. Fury, The Techcet Group, LLC Rajarao Jammy, SEMATECH William Kroll, Matheson Tri-Gas Ernest Levine, Albany NanoTech Lars Liebmann, IBM Corp. Dipu Pramanik, Cadence Design Systems Inc. Griff Resor, Resor Associates A.C. Tobey, ACT International

#### EDITORIAL OFFICES

PennWell Corporation, Solid State Technology 98 Spit Brook Road LL-1, Nashua, NH 03062-5737 Tel: 603/891-0123: Eax: 603/891-0597: www.ElectrolQ.com

#### PennWell

#### CORPORATE OFFICERS

1421 South Sheridan Rd., Tulsa, Ok 74112 Tel: 918/835-3161 Frank T. Lauinger, Chairman Robert F. Biolchini, President and CEO Mark Wilmoth, Chief Financial Officer

#### TECHNOLOGY GROUP

Christine A. Shaw, Senior Vice President and Publishing Director

For subscription inquiries: Tel: (847) 559-7500; Fax: (847) 291-4816; Customer Service e-mail: sst@omeda.com: Subscribe: www.sst-subscribe.com

We make portions of our subscriber list available to carefully screened companies that offer products and services that may be important for your work. If you do not want to receive those offers and/or information, please let us know by contacting us at List Services, Solid State Technology, 98 Spit Brook Road, Nashua, NH 03062. All rights reserved No part of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval sys tem, without written permission of the copyright owner. Prices for bulk reprints of articles available on request. Solid State Technology articles are indexed in Engineering Information and Current Contents, and Applied Science & Technology Index and abstracted by Applied Science & Technology Abstracts.

Qmags

www.solid-state.com

4 **NOVEMBER 2012**

ECHNOLOGY

SOLID STATE TECHNOLOGY

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

# CONNECT. COLLABORATE. CREATE.

ULVAC

CONNECT with the right people. COLLABORATE in the right environment. CREATE alliances, partnerships and strategies for a stronger future.

Presented by:

#### CONNECT... It's remarkable what can happen when you get the right people together.

That's why CEOs, CTOs, VPs of Operations and Manufacturing, Fab Managers and other executives from companies like Intel, GLOBALFOUNDRIES, Texas Instruments, Samsung, Broadcom, IBM, TSMC and more attend The ConFab.

#### Don't miss the 9th Annual ConFab, presented by Solid State Technology!

Coming to the Encore at the Wynn in Las Vegas from June 23 to 26, 2013. Visit www.theconfab.com today to learn more and pre-register or to apply to attend as our VIP guest.

Owned & Produced by: PennWell

www.theconfab.com

Please send news articles to jamesm@pennwell.com

#### worldnews

**Tezzaron Semiconductor** USA | is taking over SVTC Technologies' wafer fab in Austin, TX.

Devan lyer, director of Semiconductor Packaging in Texas Instrument's Manufacturing Group, has joined the advisory board of The ConFab.

Imec plans to start construction of a 450mm pilot line next year, with early production focused on sub-10nm devices starting at the end of 2016.

VORLD | Imec, Holst Centre, and Panasonic have developed a new prototype of a wireless EEG (electroencephalogram) headset.

**Solvay Specialty Polymers** USA has extended its line of highperformance polyester compounds with a new version targeting lightemitting diode (LED) TVs with higher heat and light stability.

WORLD | ON Semiconductor has joined imec to collaborate on the development of next-generation GaN-on-Si power devices.

WORLD | The market for semiconductor magnetic sensors used in industrial and medical applications expanded by 6% in 2011 to \$118.2 million, with green energy initiatives acting as a major growth driver, according to IHS iSuppli.

ASIA | GaN power device developer Transphorm Inc. has secured a \$35M Series E financing round led by the Japanese government-backed Innovation Network Corporation of Japan (INCJ), and Nihon Inter Electronics Company with whom it has signed a secondsource manufacturing deal.

**NOVEMBER 2012**

#### Analyst: Fab spending softness 2012 extending into 2013

Fab equipment spending continues to soften in 2012, but don't hope for a reprieve until later in 2013.

Worldwide wafer fab equipment (WFE) spending is projected at \$31.4 billion in 2012, a -13.3% decline from 2011, according to Gartner. But counter to some other industry watchers, the firm now thinks there won't be a big rebound in 2013 it's now forecasting a -0.8% slip next year to \$31.2B, before finding its footing again and bouncing back in 2014 with 15.3% growth to \$35.9B.

Earlier this summer Gartner foresaw an -8.9% decline in 2012. followed by 7.4% growth in 2013. In September SEMI predicted 2013 could be a "golden year" with nearly 17% growth in fab spending.

"The outlook for semiconductor equipment markets has deteriorated as the macro economy has weakened," stated Bob Johnson, research VP at Gartner. After starting the year strong thanks to sub-30nm production ramps at foundries and other logic manufacturers, demand for new equipment logic production will soften as yields improve, leading to declining shipment volumes for the rest of the year."

Fab utilization rates will erode to the low 80% range by the end of this year, slowly increase to about 87% by the end of 2013. (That's

less optimistic than Gartner's June outlook which saw mid-80% in mid-2012 and 87% by the end of the year.) Leading-edge capacity will recover slightly better, hitting the high-80% range by year's end and gradually getting into the low-90% range as 2013 progresses.

Increased demand combined with less-than-mature yields at the leading edge had been hoped to consume extra capacity and raise utilization rates. In leading-edge logic that has in fact helped create inventory shortages, Johnson noted, but "not enough to bring total utilization levels up to desired levels. In the memory segment, some suppliers are even cutting production in an attempt to shore up weak market fundamentals."

Memory is expected to be weak through 2012, with strong declines in DRAM investments and a virtually flat NAND market, the firm notes. Foundry spending has been revised downward for both 2012 and 2013; some foundries have improved their 28nm yields, but mainly for SiON technology, as 28nm high-k/metal gate (HKMG) processes are still yielding below normal. Longer-term, Gartner thinks foundries will ratchet up their spending more in future years due to aggressive development of EUV lithography and 450mm wafer processing. - J.M.

SOLID STATE TECHNOLOGY

www.solid-state.com

6

ECHNOLOGY

#### TV makers expanding low-brightness LED backlit models into entry-level market

When LCD TVs were first competing against plasma TVs, one key differentiating argument was their brightness. Typical TVs have brightness measuring around >400 nits (1 nit is roughly 1 candela per m<sup>2</sup>), which is deemed suitable for TVs typically viewed in a living room and at a distance. Plasma TVs' full-white brightness is typically

is still a bit higher than aforementioned gap between CCFL and direct LED backlighting. But the goal here, Kim notes, isn't to offer another CCFL alternative it's targeting the same entry segment as low-cost low-brightness direct LED backlight TVs. - J.M.

sub-200 nits; <300 nits is more typical of computer/laptop screens.

However, the trend in LCD TVs is now swinging toward lower brightness, according to DisplaySearch senior analyst Jimmy Kim. Most existing low-brightness TV models were small and targeted the secondary market, but earlier this year first trials began for low-brightness TV models, with low-cost direct LED backlighting, in the main segment of large TVs, he notes. The tradeoff is sacrificing design and picture quality for cost - lower brightness for the LED component, and a thinner light guide plate. These efforts have reduced the cost gap between LED and CCFL backlights to <1.3x, so pricing is similar. (A spike in CCFL materials prices is another reason for the shrinking cost difference.)

Consumers have responded enthusiastically, and low-brightness LED-backlit TVs accounted for more than 10% of total LCD TV shipments in 2012. So TV makers are now planning more models with low brightness, even those using edge LED backlights. Most mainstream TV models are now being designed with ~350 nits, and some entry-level models will be as low as 250 nits, to fend off the charge of low-cost backlight TVs (300-350 nits). Soon the only 400-nit LCD TVs will be high-end models, Kim predicts.

Getting edge-lit backlight TV brightness down to 250 nits narrows the cost gap between them and CCFL models from 2× to 1.5×, which

## POWER SOLUTIONS FOR ... SEMICONDUCTOR DESIGN, MANUFACTURE AND TEST

#### WIDE RANGE OF APPLICATIONS

- ▶ Semiconductor design simulators

- Die bonding

- Clean room environments

- ATE and chip testing

- Wafer fabrication

- Ion implantation

- LED fabrication

## **D** POWER

#### **FEATURES**

- Liquid cooled

- ▶ Fan cooled

- Multi output

- ▶ Redundant systems

www.tdipower.com | 908.850.5088

www.solid-state.com

ECHNOLOGY

SOLID STATE TECHNOLOGY

Qmags

**NOVEMBER 2012**

## **news**cont.

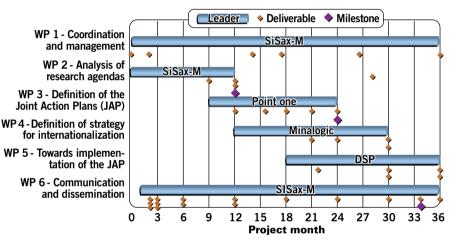

#### Europe to unite research efforts in Silicon Europe cluster alliance

A cluster of partners from across Europe are forming a new cluster alliance to cooperate in research, development, and business and reassert Europe's position as a leading world center for energyefficient micro-/nanoelectronics, and information/ communications technology.

The new collective organization, dubbed "Silicon Europe," brings together Europe's four leading micro- and nanoelectronics regions: Silicon Saxony (Dresden/Germany), DSP Valley (Belgium), Minalogic (Grenoble/France), and Point One (Eindhoven/Netherlands). They claim to represent about 800 research institutes and companies, including global leaders Philips, NXP, Globalfoundries, Infineon, STMicroelectronics, Schneider Electric and Thales - though more than 75% of all their partners are small and medium-sized businesses.

"Global competition is tough and investments into European microelectronics are declining," acknowledged Jean Chabbal, chief representative and CEO at the French Cluster Minalogic (Grenoble/France). Only 10% of all worldwide investments into microelectronics (~€28 billion) went to Europe, less than a quarter of the funds (48%) that went to Asia. Since 2000, Europe's market share in the semiconductor industry

2

ECHNOLOGY

has dwindles from 21% to 16%.

Still, the region employs 135,000 workers directly and another 105,000 in supplier sectors, the group notes. "Europe is home to a number of the world's best-known, and most active regions in the micro- and nanoelecEurope, speaking at a press conference in Dresden. "In the third year, we also want to start implementing this action plan. It's not only about creating paper, but doing some action. In addition to this, we want to involve if possi-

tronics industry and the semiconductor industry, more specifically," with regional clusters consolidating work from industry, research, and government partners, Chabbal stated. "The European micro- and nanoelectronics sector must take advantage of this leading position and further expand upon it. This is the only way for Europe to maintain its role as a world-renowned leader in technology research and development."

This is a three year effort, as shown in the diagram above. "We want to set up a joint action plan that is organized between the four clusters," said Frank Bösenberg, in charge of administration of Silicon ble additional European players."

Details are not clear on precisely how the micro/nanoelectronics work will be shared and portioned out; the groups say they are currently analyzing each cluster's main research topics, identifying ways to synchronize activities and unearth and utilize previously unused synergies. In a published executive summary, the groups do identify three key objectives: promote the strategic importance of micro/ nanoelectronics as a key enabling technology; secure European knowhow across research institutes, design houses, and system integrators; and open up new markets

NOVEMBER 2012 SOLID STATE TECHNOLOGY

The New PRESTO®

The Power of **Thermodynamics**<sup>™</sup>

by improving innovation and technology transfer from research to commercialization and internationalization.

Plans also are underway to develop a strategic technology roadmap, with the hope that it can be a template for future European Commission programs, explained Thomas Reppe, general manager of the German Cluster Silicon Saxony. The group also has identified a goal of making "a substantial contribution" to the European Union's "Europe 2020" growth strategy, which aims to advance R&D as a basis for improving European society. "With their activities, the European Commission aims at a digital and resource-efficient development [because] both of these core goals micro- and nanoelectronics are a decisive factor," noted Eelco van der Eijk, contact person for the high-tech industry at the Dutch Ministry of Economic Affairs.

Obtaining political support is key in the Silicon Europe's mission. Peter Simkens, managing director at the Belgian Cluster DSP Valley, called for a pan-European micro/nanoelectronics summit in the style of Germany's IT summit: "We are appealing to all national governments to increase the synchronization of their economic and innovation policy with the European Commission and its guidelines," he said. "Silicon Europe stands for the common interest of the European microelectronics industry [...] The European economy needs to expand on its strengths now, if it wants to remain competitive in the global market for the long run."

Some of that government support is already coalescing. "The Europe-Cluster of the micro- and nanoelectronics sites is a very important signal for both German and European politics. Together and across national borders we have to ensure that this key technology still has a home in Europe in the future," stated Michael Kretschmer, vice-chairman of the CDU Parliamentary Group at the German Bundestag, member of the German Bundestag, and member of the Committee on Education, Research and Technology Assessment. While acknowledging that previous European clusters haven't worked together, "I appreciate the Silicon Europe initiative and wish for it to find numerous supporters and advocates also in the German Bundestag and the German government. The high-tech nation Germany can simply not forego these technologies that by enabling innovations in various industries create jobs and prosperity." - P.S., J.M.

**Control Solutions** for CVD, HB-LED

Liquid Temperature

(800) 458-5226

#### www.julabo.com

SOLID STATE TECHNOLOGY

**NOVEMBER 2012**

Qmags

## **news**cont

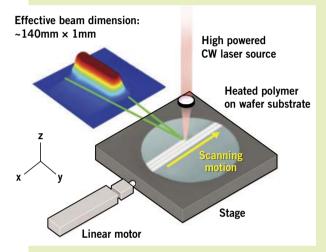

#### Laser spike anneal for photoresists outperforms hotplate bake

Researchers at Cornell University have developed a new laser-based method for ultra-fast anneal of

Figure 1: Using a continuous wave laser focused to a line and scanned over the surface, laserspike annealing heats up a silicon substrate to its melting temperature in millisecond time frames.

thin photoresist films. The research, sponsored by Semiconductor Research Corporation (SRC), has shown that the new anneal outperforms a state-of-theart hotplate bake for both 193nm and EUV lithography applications.

Laser spike annealing is already in use for dopant activation in silicon (see J. Hebb et al., "Dual-beam laser spike annealing for advanced logic applica-

tions," http://bit.ly/VLRWCg). Now, Professors Michael Thompson and Christopher Ober from Cornell are perfecting the unique advantages of laser heating vs. current

ECHNOLOGY

state-of-art hotplate bake used in chip patterning processes. Historically, wafers required

> a lengthy bake at low temperatures to avoid degradation of the photoresist properties. Heating at much higher temperatures for millisecond times using continuous wave lasers not only activates the necessary photoresist chemical reactions at higher throughput, the researchers have determined, but also improves the pattern fidelity and lineedge roughness by limit-

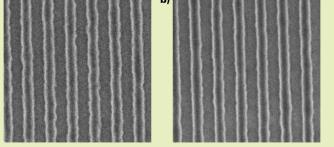

Figure 2: Patterns generated under 13.5nm EUV exposures using a) hot-plate PEB and b) laser PEB on a commercially available EUV resist. Critical dimensions were 52.1nm and 47.8nm for hotplate and laser patterns respectively, with a target half pitch of 50nm. For these comparable SEM images, laser patterns show ~15% enhancement in sensitivity and ~15% reduction in linewidth roughness compared to hot-plate patterns. PEB temperatures and durations were 85°C for 60 sec (hot-plate) and 72W (~225°C) for 2ms (laser). (SEM image courtesy of GlobalFoundries)

ing the chemical diffusion.

"This new laser method can deliver a breakthrough in thermal processing for the industry," said Ober. "Until now, lithography

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue

progress has been held back by the traditional methods for heating the resist that were regarded by many as already optimized. The laser proves otherwise."

As one of the key benefits of the laser-based bake process, Cornell Ph.D. candidate Byungki Jung has shown significant improvements in line-edge roughness for both current 193nm immersion lithography as well as for next-generation 13nm EUV lithography.

Currently, photoresists are exposed and then baked on a hot plate at low temperatures (80-150°C) for approximately 1min to activate the resist chemistry and create a solubility differential

> between exposed and unexposed parts of the resist, which delineates the post-develop pattern. Prolonged heating, especially at higher temperatures, causes excessive chemical diffusion which degrades the image quality.

The novel application of laser spike heating for a duration of milliseconds only — preserves the polymer integrity at much higher tempera-

tures (up to 800°C) and provides a means to maximize resist sensitivity while minimizing pattern roughness, thereby facilitating enhanced scalability. **– P.S.**

10 NOVEMBER 2012 SOLID STATE TECHNOLOGY

| Next Page

# CONNECT. COLLABORATE. CREATE.

## The *n*Fab.

Presented by:

#### COLLABORATE... It's impressive how the right environment can foster powerful collaboration.

"The ConFab is a great experience. The way that the conference is organized, the level of participation and the level of the participants are truly excellent. Going to a lot of these events, for me, the ConFab is the preeminent conference in the industry right now."

- IT Solutions Manager at Intel

#### Don't miss the 9th Annual ConFab, presented by Solid State Technology!

Coming to the Encore at the Wynn in Las Vegas from June 23 to 26, 2013. Visit www.theconfab.com today to learn more and pre-register or to apply to attend as our VIP guest.

Owned & Produced by: PennWell\*

www.theconfab.com

#### Qmags

## IMAPS 2012: A review

The 45th Symposium on Microelectronics (IMAPS 2012) was held September 9-13 in San Diego. Here's a quick review of some of the 3D and advanced packaging papers presented at the meeting.

Gu and co-workers at **Qualcomm** reported on a memory on logic 3DIC stack consisting of a two-chipwide IO memory stack bonded to a 28nm logic chip. TSV are 6 $\mu$ m, wafers are thinned to 50 $\mu$ m, TSV connection is to M1 of the 7-layer copper/low-k interconnect stack. The memory stack has 1200 IO on 40 $\mu$ m pitch. The bottom memory die has TSV, the top die does not need them. Thinned die are shipped either on their carrier (the OSAT removes the carrier) or after removal from the carrier on a flex frame.

A negligible shift in electrical parameters is observed after optimizing TSV formation and determining the need for a  $5\mu$ m keep-out zone (KOZ). No change in bump resistance is seen after 1000 hrs at 150°C and 1000 cycles of temp cycling.

**Xilinx** has been releasing information on its 2.5D FPGA module for the past two years. In the latest presentation, Banijamail and co-workers examine the reliability of their 2.5D Virtex-7 H580T, which consists of a transceiver chip and two FPGA slices. Interposer TSVs are 10-20 $\mu$ m and 50-100 $\mu$ m deep. FPGA chips are bumped on 30-60 $\mu$ m pitch using Cu pillar bump technology.

Different substrate sizes and designs, lid designs, lid materials, and underfills were examined to minimize warpage and maximize microbump and c4 bump reliability. Control of these variables resulted in packages that met JEDEC warpage spec and

#### Packaging

minimized BGA fatigue. With the recent announcements by **Xilinx**, **Altera** and others the commercial production of 2.5D products on "high density" interposers is entering the realm of commercial reality. While it is clear that fine featured interposers will come from foundries like TSMC, there have been questions, about "coarse featured"

**Dr. Phil Garrou**, Contributing Editor

interposers in terms of who will make them and what applications they will be used in.

Shinko and CEA Leti now describe integration and electrical characterization of such a "coarse featured" 3D silicon interposer demonstrator for a SiP application. This demonstrator consists of (4) 10x10mm chips mounted on a 26x26mm Si interposer with 25 $\mu$ m microbumps on 50 $\mu$ m pitch and underfilled. TSV diameter are 10 $\mu$ m and interposer thickness is 100 $\mu$ m for an Aspect Ratio (AR) of 10. We are told that RDL on both sides of the interposer are done with a "semi additive process" although we are not given line width or pitch.

In their paper "Stacking Aspects in the View of Scaling," **imec** points out that when pitch goes below  $40\mu m$ , "stacking accuracy is one of the main drivers to ensure yielding devices." It is shown that stacking can be made less sensitive to in plane misalignment by the obvious options of increasing the pad size or decreasing the solder bump size

In a second presentation, "Small pitch microbumping and experimental investigation for underfilling 3D stacks," they report on 3D stacking characterization when using pre-applied underfill (UF).

For 3D stacking, capillary underfilling has clear limits in terms of the gap between die and the bump pitch. This limits high density integration and therefore shifts focus onto pre-applied underfill where the material is dispensed on the landing die before stacking. Pre-applied UF does have concerns such as transparency for alignment marks and UF/filler entrapment between bumps.

imec's studies reveal that both NUF/NCP (define) and WUF (wafer underfill) have commercial products that result in >90% electrical yield after underfilling, although issues such as delamination of WUF films was observed. ◆

12 NOVEMBER 2012

ECHNOLOGY

012 SOLID STATE TECHNOLOGY

## Semiconductors and healthcare converging

Semiconductor technology is increasingly being implemented in a variety of healthcare applications.

At the recent imec International Technology Forum Press Gathering in Leuven, Belgium, imec CEO Luc Van den hove outlined uses in blood cell sorting, mobile apps for personalized medicine (such as brain

monitoring of EEG activity), and advanced bio research.

"The cost of healthcare is exploding," he said, noting that one in three people will develop diabetes in their lifetime. It is estimated that the cost of treating diabetes patients will exceed \$500 billion 20 years from now (for U.S. and Europe).

Van den hove believes the healthcare system will soon see the kind of evolution of that

the semiconductor industry has witnessed. "We have created this fabulous revolution in compute power. We went from mainframe to desktop type systems to a computer in our pocket that is more powerful than a mainframe computer we were using 20 years ago. We're convinced that we will see a similar revolution in the domain of medical diagnostics," said Van den hove. "We are clearly at a turning point and we will

MEMS

go from these very sophisticated clinical labs with big medical analysis tools to tools that will be implemented on a doctor's desk, eventually to tools we will

www.solid-state.com

INOLOGY

CMOS chip with a matrix of micronails with various dimensions, packaged in a dish suitable for cell cultures.

be using in our homes which are add-ons to our smart phones, which will allow us to do part of the analysis at home. We are convinced that if you combine the capabilities of semiconductor technology with the know-how that is available in the medical

Pete Singer, Editor-in-Chief

profession, we can come up with solutions that are more sustainable."

One cornerstone of such a medical system will be early diagnostics. One example is the early detection of cancer cells in blood. "Typically today, when you have a primary tumor, it will spread out tumor cells that will circulate through the blood and will create secondary tumors that are usually the more fatal ones. If we can find a way to detect those circulating those tumor cells in the blood in an easy way, then we can come up with a way to detect cancer at an early stage," Van den hove said.

The challenge is huge: one has to have the ability

to detect one bad tumor cell in 5 billion blood cells. This equate to a requirement to detect 20 million cells per second. "This is a real challenge, but the parallelism that can be realized with semiconductor technology is a tremendous opportunity. We can fabricate thousands of those parallel circuits on one device. This will allow us to create this kind of sensitivity," he said. "The system we are building here is

a combination of very sophisticated microfluidics, electronics and very sophisticated on-chip imaging. We also require a lot of compute power because we have to analyze 20 million images per second. It will become possible to realize these kinds of detection systems."

The second pillar of a sustainable healthcare system, according to imec, is mobile diagnostics that will allow patients to be monitored in their homes and also better access to healthcare in places that are difficult to reach. A third pillar of such a sustainable healthcare system will be personalized therapy which could lead to the discover of cures of illnesses that are now uncurable.  $\blacklozenge$

Omage

NOLOG

Next Page

#### TRANSISTORS

## IEDM preview: 20nm and below

#### PETE SINGER, Editor-in-Chief

As the industry works to perfect 28nm devices in volume manufacturing and early 20nm processes, attention is focusing on next-generation 14nm and below technologies.

here have been three primary drivers in the semiconductor industry for the last four decades: Area, power/performance and cost. The wellknown push to cram more functionality onto a single chip through continued scaling -- or into a single package through 3D integration and other advanced packaging techniques -- has been well documented. Today, with the exception of Intel, the industry's leading edge devices in high volume manufacturing have critical dimensions of 28nm. Intel, racing ahead, introduced the 22nm IvyBridge chip in 2011 and has announced plans to have 14nm by the end of 2013. How long this kind

**FIGURE 1.** A wrap FG cell (left) and a planar FG cell (right). Source: Micron, Intel.

of scaling can continue is the subject of some debate, with most recognizing the EUV lithography will be required at some point, most likely for the 10nm generation (Intel has said it doesn't need it for 14nm).

It's clear, though, that continued scaling is running out of steam, and that the industry most look for other means by which to say on the path defined by the proverbial "Moore's Law." Those advances are one of the primary focal points of the upcoming 58th annual IEEE International Electron Devices Meeting (IEDM), which will take place December 10-12, 2012 at the San Francisco Hilton Union Square. The conference will be preceded by a day of short courses on Sunday, Dec. 9 and by a program of 90-minute afternoon tutorial sessions on Saturday, Dec. 8.

As reported in last month's issue, highlights of the IEDM 2012 technical program, which comprises some 220 presentations, include Intel's unveiling of its industry-leading trigate manufacturing technology; a plethora of advances in memory technologies from numerous companies; IBM's demonstration of highperformance logic technology on flexible plastic

substrates; continuing advances in the scaling of transistors to ever smaller sizes, and breakthroughs in many other areas that will continue to move electronics technology forward.

Following, we've assembled a list of the "be sure not to miss" papers and sessions slated for IEDM 2012.

#### **Invited papers**

In the plenary session, imec's Luc Van den hove, will describe how ultimate transistor and memory technologies are the core of a sustainable society. He says that several key societal challenges in domains such as healthcare, energy, urbanization and mobility call for sustainable solutions that can be enabled by combining various technologies. These solutions will be backboned by wireless sensor systems, smart mobile devices and huge data centers and servers, the key constituents of a new information universe. They will require extreme computation and storage capabilities, bound by (ultra)low-power or heat dissipation constraints, depending on the application. This drives the need, he says, to keep on scaling transistor technologies by tuning the three technology knobs: power/performance, area and cost. To get to ultra-small dimensions, advanced patterning integration, new materials such as high-mobility Ge and III-V materials, and new device architectures such as fully depleted devices are being introduced. This comes along with an increasing need for process complexity reduction and variability control. Equally important are the continued R&D efforts in scaling memory technologies. NAND Flash, DRAM and SRAM memories are now approaching the point where new scaling constraints force exploration of new materials, cell architectures and even new memory concepts. This opens opportunities for resistance based memories such as resistive RAM, phase-change RAM or spin-torque transfer magneto resistive RAM.

In another invited paper, in the regular sessions, researchers from Micron and Intel will discuss scaling

#### Deliver more density on your IC packages without soft errors.

Honeywell RadLo<sup>™</sup> low alpha packaging materials help eliminate soft errors and single event upsets by reducing alpha emissions, a significant source

of these problems. This is becoming increasingly important as chip dimensions and designs continue to miniaturize. Our leadership and expertise in low alpha refining and metrology mean that Honeywell can help you meet critical alpha emission levels.

Honeywell reliability. Reliable low alpha. Make sure to ask your suppliers if they are using Honeywell RadLo low alpha materials for their chip packaging processes.

Find out more by visiting us at www.honeywell-radlo.com

Although all statements and information contained herein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information and results obtained. Statements or suggestions concerning the user framerias and processes are made without representation or warranty that any such use is free of patent infringement and are not recommendations to infringe any patent. The user should not assume that all toxicity data and safety measures are indicated herein or that other measures may not be required. ©2012 Honeywell International inc. All rights enserved.

www.solid-state.com

SOLID STATE TECHNOLOGY NOVEMBER 2012 15

e | Next Page

Omags

#### TRANSISTORS

directions for 2D and 3D NAND Cells. They note that many 2D NAND scaling challenges are addressed by a planar floating gate (FG) cell, which has a smaller aspect ratio and less cell to cell interference. **Figure 1** compares a wrap FG cell (left) and a planar FG cell (right). The wrap cell is limited by a required aspect ratio of >10 for both the wordline and the bitline direction in a sub-20nm cell. The planar cell eliminates this limitation.

Of course, not all IEDM presentations are focused on leading-edge logic and memory. In the plenary session, John Rogers from the University of Illinois at Urbana-Champaign, will talk on bio-integrated electronics. He notes that biology is curved, soft and elastic, while silicon wafers are not. Semiconductor technologies that can bridge this gap in form and mechanics will create new opportunities in devices that require intimate integration with the human body. He plans to cover ideas for electronics, sensors and actuators that offer the performance of state-of-the-art, waferbased systems but with the "mechanical properties of a rubber band." He'll explains the underlying materials science and mechanics of these approaches, and illustrate their use in bio-integrated, 'tissue-like' devices with unique diagnostic and therapeutic capabilities, when conformally laminated onto the heart, brain or

skin.

In the third plenary talk, Joo-Tae Moon of Samsung Display will give a talk titled "State of the Art and Future Prospects in Display Technologies." There are two parts which satisfy this vision, he notes. One is the picture quality and the other is design of the display. From picture quality point of view, bigger screen size and higher pixel density are the main factors. The need for a bigger screen size requires expediting technologies with lower RC delay and higher transistor performance. Higher pixel density mandates a smaller unit pixel area and each unit pixel has the dead space for the transistor and metal line which is protected from the light by the black matrix. Clearly, the design factor is the one of the main driving forces for the changes from CRT era to flat panel display era, he says.

#### **Notable papers**

imec, in a paper titled "Ultra Thin Hybrid Floating Gate and High-k Dielectric as IGD Enabler of Highly Scaled Planar NAND Flash Technology," will describe -- for the first time -- a demonstration of ultra-thin hybrid floating gate (HFG) planar NVM cell performance and reliability. Results not only confirm the high potential of the HFG thickness scaling down to 4 nm with improved performance, but also show

www.solid-state.com

ECHNOLOGY

Qmags

#### TRANSISTORS

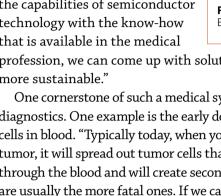

excellent post cycling data retention and P/E cycling endurance. The optimized ultra-thin HFG planar cells show potential for manufacture and scalability for high density memory application. **Figure 2** is a TEM image of a polysilicon/TiN HFG cell. The stack consists of an ISSG tunnel oxide, a dual layer FG (PVD polysilicon + PVD TiN), a high-k IPD (ALD Al<sub>2</sub>O<sub>3</sub>) and an n-type polysilicon CG.

In a paper jointly authored by GLOBAL-FOUNDRIES and Samsung, titled "Stress Simulations for Optimal Mobility Group IV p- and n-MOS FinFETs for the 14 nm Node and Beyond," researchers provide calculations of stress enhanced mobilities for n- and p-FinFETs with both Si and Ge channels for the 14 nm node and beyond. Results indicate that both for

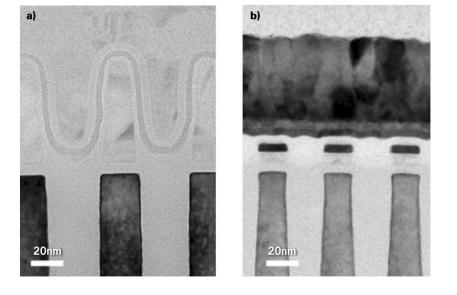

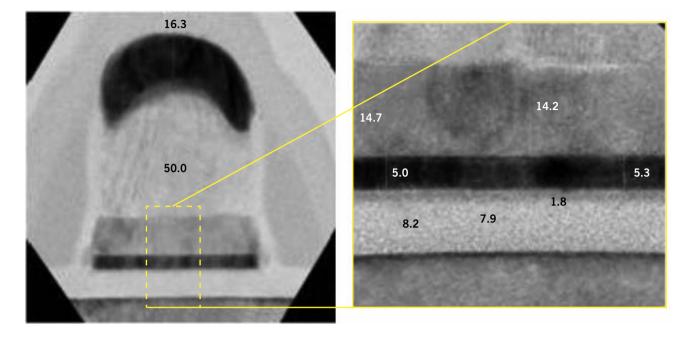

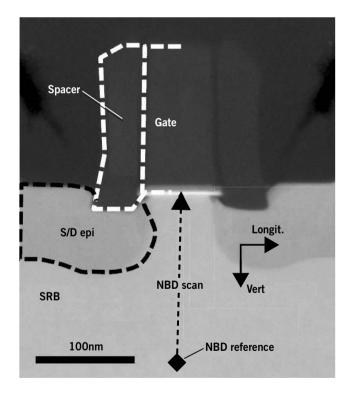

**FIGURE 3.** XTEM of a Ge-channel FET with SiGe source/ drain. Source: GLOBALFOUNDRIES, Samsung.

nFETs and pFETs, Ge is "very interesting," provided the correct stressors are used to boost mobility. **Figure 3** is a XTEM of a Ge-channel FET with SiGe source/drain. They conclude that strained channels grown on a strain relaxed buffer is effective for 14nm nodes and scalable to future nodes. TCAD simulation trends are experimentally confirmed by nano-beam diffraction (NBD).

#### **Luncheon presentation**

Ajit Manocha, CEO, GLOBALFOUNDRIES, Inc. is sure to provide an interesting luncheon talk on Tuesday, December 11th, addressing some recent jabs from Intel's Mark Bohr. The title of Manocha's talk: "Is the Fabless/Foundry Model Dead? We Don't Think So. Long Live Foundry 2.0!"

Manocha says that industry experts and observers have predicted for a long time that the fabless model has some cracks in it, and may in fact be headed for extinction at some point. "We in the foundry industry dismissed such chatter as we continue to enjoy growth rates that outpace the overall semiconductor industry," he notes in his pre-conference abstract. "But it wasn't until an executive from – surprise – Intel - officially declared the fabless model is collapsing recently that many of us really got our feathers ruffled. We firmly believe that the rumors of its death are greatly exaggerated. Evidence would seem to support that it is actually the IDM model which is dead, survived only by a very small number of anomalies that have either the financial wherewithal or stubbornness to continue down this path."

The foundry-based fabless model is not going away, and moreover it is driving manufacturers and device designers closer together, says Manocha. But like all living organisms, especially those in electronics, we have to continue to evolve. There are warning signs, both technical and economic, emerging in the foundry business that warrant our attention, and in fact require a re-thinking of how best to apply our resources and energy. Recent talks of fabless companies investing in their own fabs, and of foundries developing 'single company fabs' underscore the sense of urgency. "Clearly, we must change -Call it Foundry 2.0," he says.

Unprecedented technical and business challenges have driven semiconductor manufacturing to this new fork in the road. On the one side is the option to 'go it alone', an option available to less than a handful of companies. The temptation here is to circle the wagons, dig deep into the bank and develop an optimized, but

Continued on page 29

Qmags

www.solid-state.com

SOLID STATE TECHNOLOGY NOVEMBER 2012 17

LED MANUFACTURING

## Automated data analysis improves yield of MOCVD epitaxial process in LED manufacturing

MIKE PLISINSKI, Data Analysis & Review Business Unit, Rudolph Technologies Inc., Tewksbury, MA

Integration of collection and analysis are vital

ED manufacturers invested heavily in production equipment in 2010–2011, driven primarily by demand for backlighting for flat panel displays in TVs and computers. Although this driver has moderated and there is currently an oversupply of metal organic chemical vapor deposition (MOCVD) capacity, LED manufacturers are anticipating a new round of demand for general lighting applications. Growth in this segment is highly dependent on achieving further reductions in cost per lumen, so while forecasts for additional MOCVD capacity have softened, there is strong pressure to improve the efficiency and yield of existing process equipment.

The MOCVD process is the most critical determinant of LED performance. With long process times and complex dynamics, it is inherently difficult to control, resulting in yield losses as high as 50%. Moreover, MOCVD processing occurs early in the process flow, and there is no opportunity to rework the wafers or eliminate low or non-performing die from further processing. Although LED manufacturers are making significant progress in reducing costs in subsequent process steps, particularly packaging, improving MOCVD processing remains the single largest opportunity to increase the yields and economic performance of the manufacturing process.

MOCVD equipment manufacturers have incorpo-

FIGURE 1. The power of ADC to identify defects with the greatest impact on yield.

rated in situ measurement capabilities into their tools. Device manufacturers have also increased the amount of data they collect throughout the manufacturing process. However, much of the process knowledge that could be derived from this data remains hidden and its value unrealized.

Automated data analysis can reduce the difficulty of finding actionable information in the overwhelming volume of raw data, contributing significantly to improvements in process performance by shortening reaction times to process excursions and focusing engineering resources on solutions and innovation. Yield management systems can provide process insights to increase both yield and throughput. Automatic defect classification can help direct engineering resources to defects that are having the

MIKE PLISINSKI (Mike.plisinski@rudolphtech.com) is VP and GM of the Data Analysis & Review Business Unit of Rudolph Technologies Inc. (www.rudolphtech.com).

**NOVEMBER 2012** SOLID STATE TECHNOLOGY 18

the physics and technology of their tools. Innovative reactor designs have improved the uniformity of the deposition process across the substrate surface. Clustering of multiple chambers, engineered substrates, and higher growth rates have increased throughput. In situ metrology and diagnostics generate copious data on tool and process

**FIGURE 2.** When detected, spatial patterns can often lead to rapid identification of the defect's root cause.

greatest impact on yields. Spatial pattern recognition can identify and eliminate wafer scale systemic defects. Automated fault detection and classification can sift through terabytes of sensor data to identify equipment parameters that impact yield and anticipate equipment failures. Advanced process control techniques can be applied to narrow process windows.

#### **MOCVD process**

Modern LEDs are multilayered structures of semiconducting materials in which the thickness and composition of the various layers determine the color and brightness of the emitted light and the energy efficiency of the device. The layers are deposited sequentially using MOCVD, where the crystalline structure of each new layer is epitaxially aligned with that of the underlying layer. In the MOCVD process, precursor gases flow over the heated substrate surface, where they interact and decompose to deposit the desired material layer. Gas composition and flow rates, substrate temperature, and many other parameters must be precisely controlled to ensure the quality of the device.

THE MOCVD process is timeconsuming (6–12 hours) and largely determines the value of the final device, but the actual performance of the device cannot be measured until it has incurred the significant added costs of assembly and packaging. Yields of devices meeting the required performance specifications may be as low as 50%.

MOCVD equipment manufacturers have steadily improved performance. The most cost-effective opportunity for improving the economic performance of the manufacturing process lies in the effective collection and analysis of available data to enhance process yields.

#### **Yield management systems**

Over decades of experience, manufacturers of integrated circuits (ICs) have developed sophisticated, automated yield management systems (YMSs). While there are many similarities among the processes used for IC and LED manufacturing, there are also significant differences. Although an LED is a simple device compared to an IC containing millions of transistors and many layers of interconnecting circuitry, analysis tools optimized for IC manufacturing do not natively meet the demands of the LED manufacturers. Challenges in data collection and analysis—such as the large number of devices per wafer, long MOCVD runs that generate vast amounts of valuable sensor data, or the need to "stack" hundreds of PLM maps and then correlate the stacked data with final test results on a device by device basis—can easily

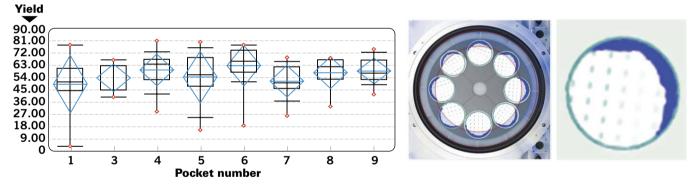

**FIGURE 3.** In MOCVD applications, FDC can provide traceability down to the individual reactor chamber and even the specific substrate pocket.

www.solid-state.com

**INOLOGY**

#### Omags THE WORLD'S NEWSTEIND®

#### LED MANUFACTURING

overwhelm systems not designed specifically for LED applications. Other barriers to effective LED yield management are more cultural than technical, such as the relative isolation of various process areas and the lack of consistent and comprehensive data collection and sharing throughout the process. It is not uncommon for the epitaxial process area to be both physically and digitally isolated, located separately with little or no network connectivity to the chip fab.

Yield management generates the greatest benefits when it operates on information gathered across the entire process, from incoming materials to final test, to identify causes of yield loss and opportunities for yield improvement. One of the most important benefits of automated yield management is its ability to eliminate much of the tedium involved in collecting and analyzing process data by generating automated reports that convert data into actionable information and allow process engineers to focus their efforts on innovations and solutions.

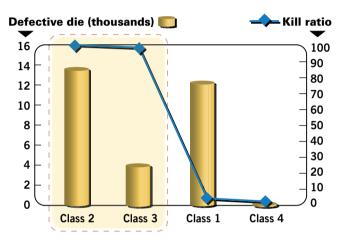

#### Automatic defect classification

Automatic defect classification (ADC) categorizes defects based on multiple characteristics, including size, shape, and color. The conventional approach to defect characterization relies on size alone, or some parameter, such as the amount of scattered light, that is presumed to be correlated to size. It further assumes that size correlates to kill ratio, i.e. the larger the defect, the more likely it is to result in a defective device. Neither of these assumptions is universally true. Figure 1 illustrates the power of ADC to identify defects with the greatest impact on yield. Defects in classes 2 and 3 have high kill ratios. Although class 2 defects are more common, both types of defect have a significant impact on yield. Defects in class 1, though numerous, are not usually deadly. Defects in class 4 are both uncommon and non-lethal. Clearly the most effective defect reduction strategy in this example will prioritize class 2 first, then class 3, ignoring classes 1 and 4.

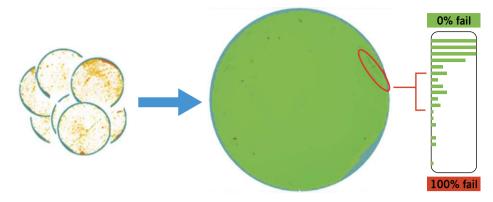

#### Spatial pattern recognition

Spatial pattern recognition (SPR) looks for relationships among defect locations on the substrate surface. When detected, spatial patterns can often lead to rapid identification of the defect's root cause (Fig. 2). The green map is a composite of 589 individual defect maps. The scratch readily apparent in the composite map was invisible in the individual maps. Further analysis revealed that the scratch killed 14–28 die 35% of the time, representing over US\$500,000 / year for this issue alone.

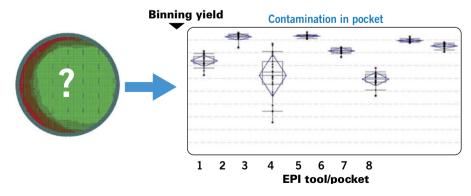

#### Automated fault detection and classification

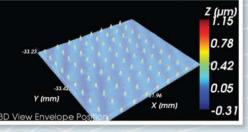

Engineers are alerted of the occurrence and type of failure conditions using automated fault detection and classification (FDC), which monitors process equipment. In MOCVD applications, FDC can provide traceability down to the individual reactor chamber and even the specific substrate pocket (Fig. 3). Bin yield data (right) indicated low yield for die from substrates processed in pocket 6. Further analysis revealed a spatial pattern with the defective die located near the edge of the substrate on one side. Engineers traced the problem to contamination in pocket 6 that was missed by photoluminescence mapping and other in-line monitoring.

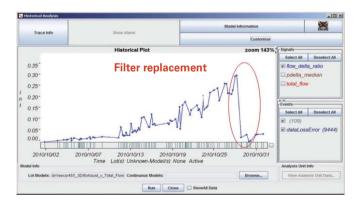

#### **Predictive maintenance**

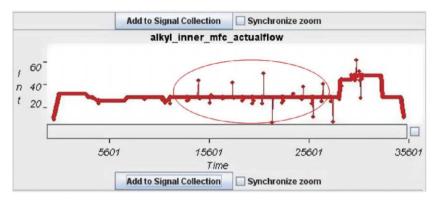

Predictive maintenance improves productivity by avoiding the unscheduled downtime that occurs with run-to-fail approach to equipment maintenance, while also reducing unnecessary scheduled downtime that occurs with strictly periodic maintenance. Predictive maintenance requires a precise and reliable indicator of imminent failure. In Fig. 4, the pressure differential across a filter is used to predict the need to change out the filter. In Fig. 5, the frequency and amplitude of spikes from a mass flow controller

**FIGURE 4.** Increasing pressure differential across a filter can be used to predict the need for maintenance. After changing the filter, the pressure differential drops back to a baseline level.

www.solid-state.com

Qmags

#### LED MANUFACTURING

indicate the need for maintenance. Automated FDC can monitor these and other equipment parameters to alert engineers of the need for maintenance.

A case study

Figure 6 illustrates the combination of various techniques to detect and resolve a problem in an LED

**FIGURE 5.** The frequency and amplitude of spikes from a mass flow controller may predict the need for maintenance.

#### and isolate a process issue, ultimately saving millions of dollars per year through increased yields and more efficient use of precious process engineering time.

#### **Future opportunities**

By narrowing process windows and increasing yields, advanced process control has the potential to signifi-

> cantly reduce the cost per unit area of MOCVD epitaxial processing, which is the most costly process in LED manufacturing. Improving bin yields also reduces assembly and packaging costs for defective die. Additional benefits may accrue from increases in die size that would be enabled by decreases in defect density. Finally, higher yields of more valuable devices can drive increases in average selling price and profitability.

**FIGURE 6.** The combination of yield analysis, spatial pattern recognition, and fault detection classification identified non-uniform radial temperature in a specific reactor as the cause of yield loss.

production line. The problem was initially detected as a yield loss due to excessive variability in the wavelength of emitted light. Commonality analysis isolated the problem to a specific reactor. Spatial pattern recognition and pocket-level traceability showed the defects concentrated near the edge of the susceptor. Analysis of sensor data from the reactor indicated a radial non-uniformity in susceptor temperature. Possible causes to be investigated include miscalibration of the outer zone pyrometer and insufficient RF power to the outer zone.

With an integrated approach to data collection and analysis, manufacturers can quickly and easily detect

#### Conclusion

Process control software is providing leading LED manufacturers with higher yields and better control of their manufacturing processes. By focusing yield management and process control strategies on the MOCVD process, these manufacturers are achieving significant reductions in the largest contributor to their manufacturing costs. Moreover, since process control systems scale inexpensively with changes in production capacity, technology, materials, or geographies, the investments of early adopters will be highly leveraged by future growth. ◆

www.solid-state.com

SOLID STATE TECHNOLOGY NOVEMBER 2012 21

## New CMP process holds promise of lower costs, improved efficiencies

CHRISTOPHER ERIC BANNON, Texas Instruments Inc., Richardson, TX

Implementing third-generation low-abrasive copper slurry

here is a certain amount of inertia involved in making a decision to deploy a new manufacturing process. However, lowering the total cost of ownership and improving the overall efficiency often provide sufficient impetus to take the first step, even when the process is so integral to semiconductor fabrication as is the chemical-mechanical polishing (CMP) of wafers. Of course, following the correct steps to discover, evaluate, qualify, and deploy the optimum materials as well as the most effective process parameters and procedures are essential to successfully migrating to a new CMP process.

#### Reducing costs, improving processes

The market for third-generation copper slurries has matured to the point where the cost of such slurries has reached a new low. This gets the attention of semiconductor manufacturers, but selecting, qualifying, and deploying a new consumable material is only part of the challenge. Third-generation slurries are typically less abrasive and more selective in the materials they remove than previous formulations. As a result, switching slurries would also require an array of design experiments to discover how the CMP process would be affected by changing a critical component in the process. In addition, the control parameters for the equipment performing the process would have to be modified to achieve an optimum level of production with high yields.

Still, the benefits that evolve from migrating

**FIGURE 1.** Results of removal rate tests on a third-generation slurry.

to a new slurry would be far reaching. Specifically, the manufacturer could expect a slurry with the following characteristics: low abrasion, high copper removal rate, highly selective to the oxide, and low dishing and erosion of the wafer. At the same time, the CMP process could have increased pad/ puck life, head life and tool throughput, as well as a

**CHRISTOPHER ERIC BRANNON** (cbrannon@ti.com) is a member of technical staff at Texas Instruments (<u>www.ti.com</u>) and currently holds a position at TI's DMOS5 factory as a copper CMP manufacturing engineer.

22 NOVEMBER 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

CHNOLOGY Previous Page

Qmags

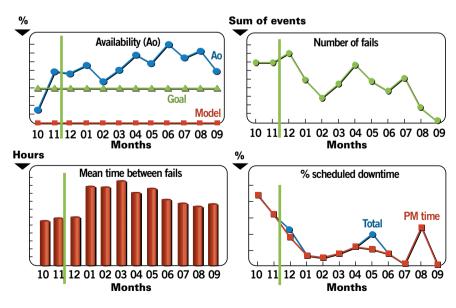

world-class mean-time-between-failures (MTBF) of approximately 48 hours.

#### **Evaluating slurries**

Integral to choosing a new copper slurry would be evaluating its compatibility with the manufacturer's existing machine tooling. A best case scenario would be to leverage existing pads, conditioning pucks, and heads. Moreover, for maximum throughput, wafers would need to be processed through the current processing equipment's onboard scrubber and dry station as quickly as possible.

Surveying commercial slurries on the basis of slurry/solid makeup and type, chemical composition, pH level, oxidizer ( $H_2O_2$ ) costs, and compatibility with the current barrier slurry should reduce the number of appropriate candidates to be evaluated on an experimental basis. First, the performance properties of each material would be evaluated and second, experiments would be performed by varying process control parameters to determine the optimum slurry to deploy and how it should be deployed on the machine tooling.

The initial criteria for testing wafer performance and thereby judging each slurry should involve: removal rate, nominal removal profile, removal profile turnability in relation to certain sets of recipe alternatives, and defect rates. Following these types of tests, experiments with process controls and the candidate slurries should compare: carrier speed, table speed, down force exerted on the wafer, carrier positioning, carrier oscillation, and slurry flow. Candidate slurries advancing beyond this point could also be evaluated on

the basis of patterned wafer tests to discover removal rate behaviors, the ability of each slurry to detect endpoints, and the over-polishing window. In addition, slurry recipe parameters could be manipulated to eliminate residual copper, especially at the wafer's edge, and to achieve uniform and reasonable dishing and erosion performance. Lastly, slurry vendors should be asked to perform and provide the results from lifetime experiments with consumables.

#### Second- vs. third-generation slurries

Throughout this type of process, manufacturers will become aware of the differences in second- and thirdgeneration slurries.

Second-generation slurries are high in abrasive solid content and have chemical additives to help stop

Once the benefits of a new slurry have been identified, the actual processes in the manufacturing line must be re-developed

the removal process as it reaches the tantalum nitride (TaN) layer. Overall, the results of such a slurry would be limited to a very mechanical process, one that would rely heavily on F.W. Preston's venerable equation that defined how quickly material would be removed from a surface as a result of mechanical polishing. Although experiments performed by TI have shown a second-generation slurry likely would be selective enough with regards to the materials removed, the tool's pad would probably degrade after approximately 400 wafers. This could cause increased dishing and erosion as a result of temperature spikes and reduced consumable performance.

In contrast, third-generation slurries are low in abrasives and have a different chemical composition than second-generation slurries. Third-generation slurries could be just as selective as second generation slurries, meaning they would also remove materials to the TaN layer, but they typically produce less dishing and erosion, and achieve higher copper removal rates at lower process parameters.

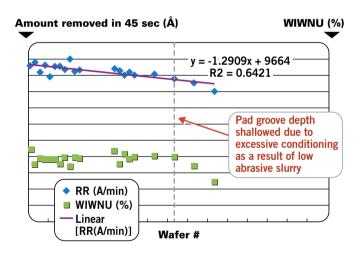

Experiments performed by Texas Instruments (TI)

www.solid-state.com

SOLID STATE TECHNOLOGY NOVEMBER 2012 23

Omag

EMERGING TECH

with one third-generation slurry compared to a currently deployed first-generation slurry showed that there could be a problem with premature balding of the machine's pad (**Fig. 1**). The removal rate for the polishing process decreased as wafers were processed and as the grooves on the machine's pad became shallower due to excessive conditioning required because of the third-generation slurry's nonabrasive nature.

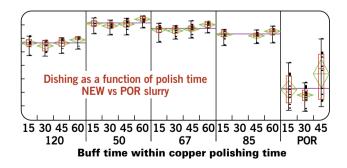

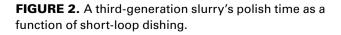

Further experimentation revealed that this could be overcome by reducing the conditioner's downforce and time. Since the third-generation slurry was low-abrasive, it would not wear down the conditioner diamonds, which caused the degrading of the cut rate of the pad. **Figure 2** shows the performance of a thirdgeneration slurry with regard to the removal of dishing over several polishing times and compares this to the same results of a first-generation slurry. This clearly demonstrates the superior performance of the thirdgeneration slurry.

#### **Process development challenges**

Once the benefits of a new slurry have been identified, the actual processes in the manufacturing line where the slurry will be deployed must be re-developed to take into account the new material. With a CMP process, these challenges often involve identifying and correcting any defects the new process may introduce. Issues such as photo-induced corrosion can usually be resolved quickly,

while others like residual copper and micro-scratching, may require adjustments in the process.

Residual copper can have a devastating effect on yields, but polish and plate engineers can usually produce custom film depositions based on the requirements of the process. In addition, wafer-level inspections on every lot processed will also help. Micro-scratching is particularly problematic with first-generation slurries which incorporate fumed silica. These processes typically lack a final table conditioner and, as a result, the machine's soft pad will become embedded with slurry until it effectively becomes a fine-grain

sandpaper. Nonabrasive, third-generation slurries which employ colloidal silica avoid this problem entirely.

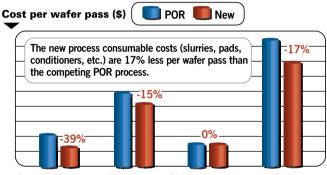

#### **Replacement costs**

Even though experiments demonstrated the benefits of a third-generation slurry, these advantages must outweigh the cost of replacing a process that is currently in place. This involves benchmarking consumable costs and the wafer yield rate with a new CMP process versus the old CMP process. The benchmark results performed at TI were quite

Continued on page 31

Consumable cost Slurry cost Clean chem cost Total

**FIGURE 3.** Consumables cost savings of thirdgeneration slurry CMP process over first-generation slurry CMP process.

**FIGURE 4.** Sample copper tool availability with the new third-generation slurry process.

24 NOVEMBER 2012 SOLID STATE TECHNOLOGY

**CHNOLOGY**

# CONNECT. COLLABORATE. CREATE.

CONNECT with the right people. COLLABORATE in the right environment. CREATE alliances, partnerships and strategies for a stronger future.

## The iFab.

HITACHI inspire the Next

ADVANTEST

Presented by:

CREATE... It's amazing what the right people in the right environment can accomplish together.

#### Alliances Partnerships Strategies for a Stronger Future CONNECT, COLLABORATE, CREATE @ THE CONFAB

#### Don't miss the 9th Annual ConFab, presented by Solid State Technology!

Coming to the Encore at the Wynn in Las Vegas from June 23 to 26, 2013. Visit www.theconfab.com today to learn more and pre-register or to apply to attend as our VIP guest.

Owned & Produced by: PennWell\*

www.theconfab.com

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

Next Page

#### FORECAST

## The scare of overcapacity

CHRISTIAN GREGOR DIESELDORFF, SEMI Industry Research & Statistics, San Jose, CA

#### *How changes in capex affect fab capacity*

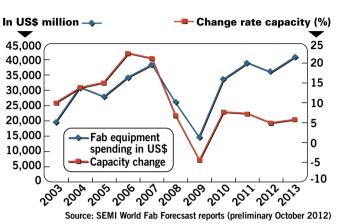

eports have surfaced recently that indicate companies including TSMC, Samsung, and Intel may change their capital expenditure plans for 2013. A number of market research firms have revised their economic scenarios and forecasts, including updates for both semiconductor industry revenues and fab spending.

For example, TSMC may increase its 2013 capex by about US\$ 2 billion — to a robust \$10 billion. Another media report in September indicated that Samsung may reduce 2013 spending, perhaps even significantly. Historically, Samsung cut capex in 2002 (by -30%), 2008 (-22%), and 2009 (-44%) — all years of economic depression. But can Samsung maintain its market share with a -30% or even -50% cut in capex?

Other media reports speculate that Intel may cut 2013 capex by about -10%. Intel's equipment spending for 2012 was actually a bit lower than the year before. If Intel does cut its 2013 capex, SEMI's data suggest that front-end equipment spending could be affected only marginally.

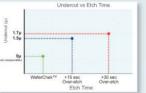

The question remains: How will changes in capex affect capacity? An increase in installed capacity may lead to oversupply, which will then drive down average selling prices and subsequently revenue.

#### Capex affects capacity

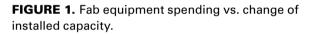

If significant changes in capex occur, installed capacity is likely to be affected. Since the last economic downturn in 2009, the industry has seen a change in paradigm. The average yearly growth rate from 2003 to 2007 (before the downturn) was 16%. From 2010 to 2015 (after the worst of the downturn), it is expected to range from 6% to 7%. Before the downturn, most

I Search Issue

fab spending went into new installed capacity; however, more money is now being spent to upgrade existing facilities (Fig. 1).

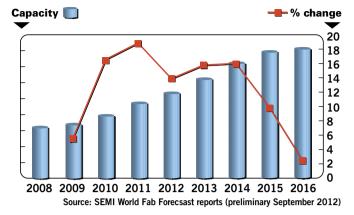

Except for foundries and system LSI (SLSI), almost all segments of the industry have seen a decrease in the rate of new capacity additions in 2012 (Fig. 2). The foundry industry segment has greater installed capacity — both in absolute terms and in the rate of growth in comparison to other segments. Given industry consolidation and as more IDMs change to a fab-lite or fabless business model, foundries become even more important to the supply chain that provides manufacturing technology. The dedicated foundry sector has added capacity at greater than a 10% rate year-over-year (YoY) since 2010, and this trend will continue going into 2013.

Most current spending for the MPU sector goes into existing fabs. While no new capacity is planned for 2012, a couple of new fabs will begin ramping in 2013, pushing installed capacity up by 4%.

Cutbacks were made in NAND flash memory production in 2012 — by companies including Sandisk, Toshiba, Samsung, and Micron — in order to improve average selling prices. Anticipating higher demand,

CHRISTIAN GREGOR DIESELDORFF (cdieseldorff@semi.org) is senior industry analyst at SEMI Industry Research & Statistics (www.semi.org), San Jose, CA.

**NOVEMBER 2012** SOLID STATE TECHNOLOGY 26

companies will likely need to increase flash capacity in 2013. While flash growth will increase only 4% YoY in 2012, it's expected to double in 2013 to 8%.

More consolidation is predicted in the DRAM market. Nanya is expected to exit the PC DRAM market, and Micron may acquire Elpida by 1H13. Ultimately, only three major DRAM makers will remain; no noticeable increase of installed capacity is expected in 2012 and into 2013.

Samsung's heavy investments in system LSI will singlehandedly spike overall SLSI capacity. One example is the recently announced \$4 billion conversion of its Austin, TX, fab from flash to 28nm SoC logic devices. Installed capacity for system LSI shows healthy growth since 2010 — about 20% every year, with an expected repeat performance in 2013.

Samsung has begun an aggressive conversion of up to four existing memory lines to system LSI. A transition from flash to system LSI is not easy to manage, so a drop in memory capacity is expected. The company is expected to compensate for this memory capacity by continuing to ramp its Line 16 fab and constructing a new fab in Xian, China, with a massive investment of \$7 billion; construction started in mid-September 2012. SEMI's World Fab Forecast gives more detail about the ramping phases of this leadingedge flash fab with huge potential capacity.

#### Needed: More 300mm fabs?

Merely shrinking die may not compensate for increasing demand for chips, such as for mobile and

www.solid-state.com

automotive applications. Volume production for the first 450mm fabs may not occur until 2018; it may take even longer until the cost-benefit ratio for 450mm volume fabs makes it an attractive option for all potential chipmakers. While 450mm production catches up to demand, the industry will still need additional 300mm fabs, especially for system LSI and flash. Of the 300mm NAND flash fabs currently in construction, ramping, or still planned, all are expected to reach full capacity by 2016 (**Fig. 3**).

The industry has a changed paradigm in that more fab equipment spending is allocated to upgrade existing capacity rather than adding new capacity. The industry reacts quickly to changes in average selling prices by reducing capacity outputs and slowing down expansion. In the five years before the economic downturn, capacity growth rates were in the doubledigits. However, since the downturn, growth YoY has been more moderate, in the low single-digits.

The assumptions in any forecast are related to macroeconomic and political factors, like the Eurozone debt crisis, China's economy, the U.S. fiscal situation,

**FIGURE 3.** Installed capacity of 300mm volume flash fabs. Actual data available in World Fab Forecast report.

turmoil in the Middle East, and the U.S. election. At this point, worldwide GDP for 2013 is expected to be higher than in 2012, while semiconductor revenue is expected to be heading for the upper single-digits in 2013. While some data suggests that 2013 front-end fab equipment growth could be as high as 17%, a range of 12% (\$40.3 billion) to 14% (\$41.1 billion) is more likely, in light of recent changes in the marketplace. ◆

Omag

Next Page

#### PACKAGING

**Previous Page**

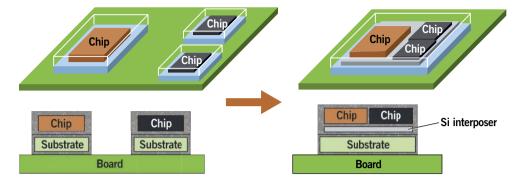

## CoWoS process cuts power, boosts performance, shrinks footprint

JERRY TZOU, TSMC, Hsinchu, Taiwan

Converging the IC package and system board into one device package