Zoom out

For navigation instructions please click here

LEDS

MEMS

Search Issue

JULY 2012

DISPLAYS

for

Gates P.14

**(**)

(3)

Next Page

SEMICONDUCTORS

Zoom in

Solid State TECHNOLOGY Insights for Electronics Manufacturing

PACKAGING

Impact of NVDs on Yield P. 18

Bonding Wire Advances P. 22

The of the second se

MEMS Manufacturing P. 26

www.solid-state.com

Contents

12

Zoom in | Zoom out

For navigation instructions please click here

-

Search Issue

Next Page

PennWell

## Omags

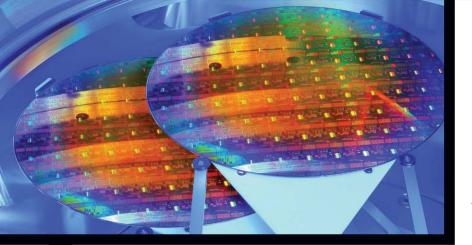

#### DID YOU KNOW YOU'RE PROBABLY HOLDING A CHIP MADE BY GLOBALFOUNDRIES?

Your smart phone performance depends on GLOBALFOUNDRIES. That's why the world's leading handset chip suppliers depend on us for a wide range of devices such as power management ICs on our award-winning 200mm 0.18µm technology, transceivers and wireless connectivity ICs on both 200 and 300mm wafers, as well as baseband and application processors at 45 and 40nm ... with new designs underway at 28nm.

> **GLOBALFOUNDRIES ...** the Smarter Choice.

FRONT END MODULE

RF TRANSCEIVER

BASEBAND PROCESSOR

APPLICATION PROCESSOR

POWER MANAGEMENT

BLUETOOTH, WIFI, NFC

GPS, FM, TV

Zoom out

For navigation instructions please click here

LEDS

MEMS

Search Issue

JULY 2012

DISPLAYS

Received a second se

or

٢

(3)

Gates P. 14

Next Page

SEMICONDUCTORS

Zoom in

# SO INSIGHTS FOR Electronics Manufacturing

PACKAGING

Impact of NVDs on Yield P. 18

Bonding Wire Advances P. 22

Ineli

MEMS Manufacturing P. 26

www.solid-state.com

Contents

Zoom in | Zoom out

For navigation instructions please click here

(3)

Search Issue

Next Page

PennWell

### Solid State Equipment LLC

#### SSEC 3300 SYSTEMS

One to Eight Stations with automation for wet and dry wafer handling. Processes may be complex, serial step processing from station to station or parallel processing, all in SEMI® Safety and Ergonomic Compliant system.

3306/8

3306/8

#### ssecusa.com

FABRICATION EQUIPMENT FOR THE INTEGRATED CIRCUIT INDUSTRY

SINGLE WAFER WET PROCESSING AND CLEANING

#### TSV CLEAN AND RESIST STRIP

#### After DRIE

#### Si ETCH TO REVEAL Cu VIAS

SEM

#### WET ETCH WAFER THINNING AND STRESS RELIEF

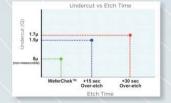

Wafer Thinning

with TTV Unchanged

After Etch (Surface Roughness)

#### UBM AND RDL METAL ETCH

Before Etch

After Etch

#### PHOTORESIST AND DRY FILM STRIP

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 000 |  |

|---|---|---|---|---|---|---|---|---|-----|--|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |  |

Post Dry Film Strip

© 2011 SOLID STATE LLC

ECHNOLOGY

Pre-strip

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend

ECHNOLOGY

COVER

18

JULY 2012 VOL. 55 | NO. 6

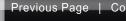

Metal ALD has become an enabling technology for gate stack integration. Source: ASM America.

#### FEATURES

#### ALD | Atomic layer deposition for metal gate integration

High-k based transistors have introduced the semiconductor industry to increasingly complex metal gate integration schemes and novel, low temperature deposition techniques such as ALD. *Mohith Verghese, ASM America, Phoenix, AZ*.

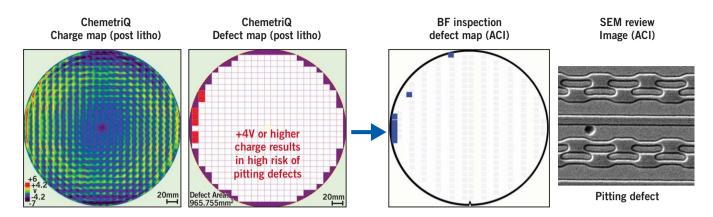

METROLOGY | Impact of charge during gate oxide patterning on yield

Detection of non-visual defects in the steps prior to optical inspection was used to trace the cause of a silicon pitting defect. *Jungtae Park, Samsung Electronics Co.; Sungjin Cho and Jeff Hawthorne, Qcept Technologies Inc.*

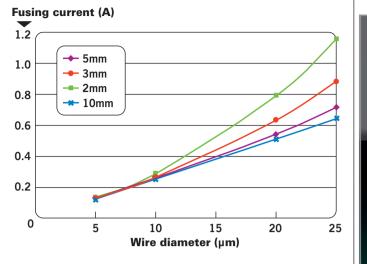

**PACKAGING** | Bonding wire: Is scalability the wave of the future? A new technology enables bonding wire to be cast instead of drawn. The wire can be used like traditional copper bonding wire but offers several advantages that make it more cost-effective. *Dominik Stephan, RED Micro Wire Pte., Ltd., Singapore.*

**MEMS** | Volume consumer markets are changing MEMS manufacturing Changes in the way MEMS are manufactured are primarily being driven by high volume consumer MEMS markets. *Eric Mounier and Jérôme Baron, Yole Développement, Lyon, France*

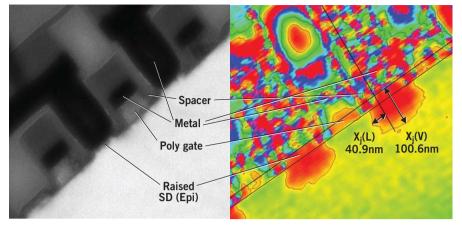

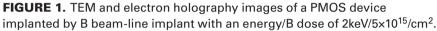

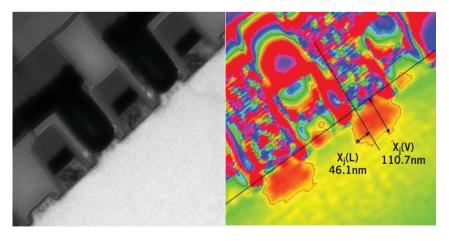

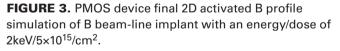

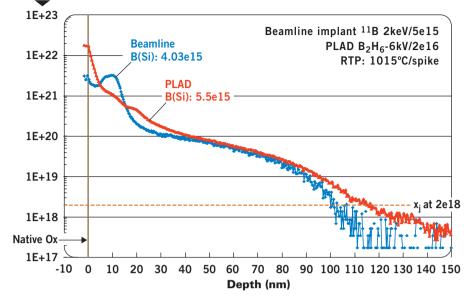

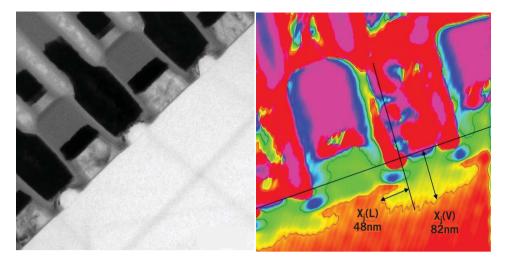

### **METROLOGY** 2D cross-sectional doping profiling study of advanced CMOS devices

Electron holography (EH), a powerful method for two-dimensional (2D) doping profiling, was used to study 2D cross-sectional doping profiles of advanced CMOS devices. *Shu Qin, Zhouguang Wang, Y. Jeff Hu and Allen McTeer, Micron Technology Inc., Boise, ID.*

26

29

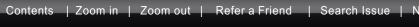

#### VACUUM | Efficiency in sealing: A BKM case study

This case study describes Microchip's experience with perfluoroelastomers o-ring seals. *Dalia Vernikovsky, Applied Seals North America Inc., Newark, CA, and Brad Ecker and Seth Urbach, Microchip Technology, Inc., Chandler, AZ.*

#### COLUMNS

- **4** Editorial From The ConFab: Chasing Price, Power and Performance *Pete Singer, Editor-in-Chief*

- **12 Packaging** From The ConFab: State of advanced packaging technologies *Meredith Courtmanche, Editor*

- **13** LEDs | The demise of sapphire wafers? *Griff Resor, Resor Associates*

- **41** Industry Forum | Government's support for long-term research *Larry Sumney, SRC*

#### DEPARTMENTS

- **3** Web Exclusives

- 6 News

- **38** SEMICON West Products

- 40 Ad Index

SNV DOI-1

D0I-2

N-1 N-2

LER

🔍 Pl

## online@www.solid-state.com

Defect count

#### Web Exclusives

#### Process Watch:

#### The dangerous disappearing defect

In this first installment of a series called "Process Watch," experts from KLA-

classified as "Not Found" or "SEM Non-visual (SNV)," and how a SNV count can disguise or hide real problems. http://bit.ly/L6rNZs

#### You make MEMS. Should you make sensor fusion software?

Solid State Technology's Meredith Courtemanche looks at the options for sensor fusion software, made by MEMS manufacturers and third-party, device-agnostic providers. http://bit.ly/LmZ2Ez

#### @ The ConFab:

#### Chip industry future

"The Economic Outlook for the Semiconductor Industry," with Jackie Sturm of Intel, Dan Hutcheson of VLSIresearch, and Jim Feldhan of Semico discussed how to

succeed in the new chip industry. http://bit.ly/LjsFF2

#### @ The ConFab:

#### Legacy fab issues

Older fabs face tool & skills obsolescence; scarce availability of parts, software, and support; etc. The Executive Roundtable shared concerns, roadblocks, and possible solutions, say Bill Ross of ISMI and Joanne Itow of Semico. http://bit.ly/KGIK84

#### @ The ConFab:

#### Video interviews

G450 Consortium's Tom Jefferson http://bit.ly/MSw8iZ ACT International'sBill Tobey http://bit.ly/LDz1kM Renesas' Ali Sebt http://bit.ly/NBocUN

#### Mobile displays @ ITF

What would our smart world be without displays? That was the question posed by imec's Paul Heremans, at ITF. http://bit.ly/K3DewF

#### **MEMS Symposium:** Chasing \$1 trillion

Michael A. Fury reports on the MEMS Technology Symposium, with the theme "Sensors: A Foundation for Accelerated MEMS Market Growth to \$1T." http://bit.ly/K3DPP2

#### **LEDs outshine legacy** lighting @ LightFair

"LED is now the dominant force in lighting," reports Ted Konnerth. What does that mean for traditional lighting, apps, distribution, and talent? http://bit.ly/NzCViX

#### MEMS isn't NEW

Karen Lightman, MEMS Industry Group, lets us in on the real meaning of MEMS new product development. http://bit.ly/JVqEiv

#### ECTC: 3D and TSVs

Electronic Components and Technology Conference (ECTC) focused on 3D integration and TSVs, says Pete Singer. http://bit.ly/L3pfb8

www.solid-state.com

| Next Page

2

Omag

#### editorial

## Price, Power and Performance

At The ConFab 2012, which took place in June at The Encore at The Wynn in Las Vegas, Mike Noonen of GLOBALFOUNDRIES kicked off the Fabless-Foundry Supply Chain session, noting that the manufacturing cycle time is now sometimes longer than the product lifetime.

Noonen noted that the semiconductor industry has always had the cyclic reality of the semiconductor cycle to deal with. This challenge has been compounded by several factors in recent years that fabless and fab-lite companies must contend with. These are:

- Financial markets demanding higher returns and hence more operational efficiency

- Fewer options for leading edge manufacturing

In parts of the world, people's first experience with the internet will be on a smart phone

Product lifecycles that much shorter than design and even production times in some markets

• Disaggregated worldwide supply chain that can be disrupted by natural disasters

In the same session, Nick Yu of Qualcomm described the "internet of things" as the biggest platform in the history of mankind. "It's going to explode," he said. "The world is moving to a higher level of abstraction," he added, pointing to the amount of social networking in the world. "All of these applications are in their infancy," he said, noting that in many parts of the world, people's first experience with the internet will be on a smart phone. "PCs and laptops are probably a thing of the past," he said. "The smartphone is the remote control for your life." He also said your first 3D camera is going to be in your phone.

All presenters emphasized three requirements moving forward: power, performance and price. "Power and cost are now a higher priority than performance," he said. "Chip cost reduction may not happen at advanced technology nodes," Yu warned.

BJ Woo of TSMC highlighted the many challenges faced by foundries, and the responsibilities they face. "Just delivering an accurate SPICE model is very challenging," she said. Fortunately, new technologies can actually reduce variability. "When you move to high-k metal gate, the variability is reduced," she said. "When you move to FinFET, it's even further reduced." -Pete Singer, Editor-in-Chief

#### Solid State CHNOL

Susan Smith, Group Publisher Ph: 603/891-9447, susans@pennwell.com Pete Singer, Editor-in-Chief

Ph: 603/891-9217, psinger@pennwell.com Meredith Courtemanche, Editor, Digital Media Ph: 603/891-9176,

mcourtemanche@pennwell.com Robert C. Haavind, Editor-at-Large Ph: 603/891-9453, bobh@pennwell.com

Phil Garrou. Contributing Editor Michael Fury, Contributing Editor Rachael Caron, Marketing Manager Cindy Chamberlin, Presentation Editor Katie Noftsger, Production Manager Dan Rodd, Illustrator

Debbie Bouley, Audience Development Marcella Hanson, Ad Traffic Manager EDITORIAL ADVISORY BOARD John O. Borland, J.O.B. Technologies Michael A. Fury, The Techcet Group, LLC Rajarao Jammy, SEMATECH William Kroll, Matheson Tri-Gas Ernest Levine, Albany NanoTech

Lars Liebmann, IBM Corp. Dipu Pramanik, Cadence Design Systems Inc. Griff Resor, Resor Associates A.C. Tobey, ACT International

#### EDITORIAL OFFICES

PennWell Corporation, Solid State Technology 98 Spit Brook Road LL-1, Nashua, NH 03062-5737 Tel: 603/891-0123: Eax: 603/891-0597: www.ElectrolQ.com

#### PennWell

#### CORPORATE OFFICERS

1421 South Sheridan Rd., Tulsa, Ok 74112 Tel: 918/835-3161 Frank T. Lauinger, Chairman Robert F. Biolchini, President and CEO Mark Wilmoth, Chief Financial Officer

TECHNOLOGY GROUP

Christine A. Shaw, Senior Vice President and Publishing Director

For subscription inquiries Tel: (847) 559-7500; Fax: (847) 291-4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

We make portions of our subscriber list available to carefully screened companies that offer products and services that may be important for your work. If you do not want to receive those offers and/or information, please let us know by contacting us at List Services, Solid State Technology, 98 Spit Brook Road, Nashua, NH 03062. All rights reserved No part of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval sys tem, without written permission of the copyright owner. Prices for bulk reprints of articles available on request. Solid State Technology articles are indexed in Engineering Information and Current Contents, and Applied Science & Technology Index ind abstracted by Applied Science & Technology Abstracts.

Qmags

www.solid-state.com

SOLID STATE TECHNOLOGY **JULY 2012**

4

cerlikon

" The HEXAGON was designed not only to be amazingly fast and easy to maintain, but also to integrate the latest process requirements for future customer products."

### Most productive packaging solution

At Oerlikon, we understand the pressure you have to lower your cost per wafer. That's why the HEXAGON, our newest tool for advanced packaging more than doubles wafer throughput, has a 50% smaller footprint than its competitors, and runs up to 5000 wafers before requiring maintenance. Innovation has a name - cost of ownership does too.

#### →Visit us at Semicon West - Booth #1307

www.oerlikon.com/systems/hexagon

Please send news articles to meredithc@pennwell.com

#### worldnews

CHINA | LED maker Cree Inc. is opening new technology centers in Shenzhen and Shanghai, China http://bit.ly/KETu73

WORLD | Universal Display Corporation's white OLED lighting technology breaks performance records http://bit.ly/LKW9I4

Inertial sensor maker Qualtré Inc. closed a \$10 million round of financing with 3 investors from Massachusetts, where Qualtre is based http://bit.ly/L9uCKv

EpiGaN NV opened its GaN epitaxial material production site, on the Research Campus Hasselt in Belgium http://bit.ly/LmW17d

Amkor Technology will build a state-of-the-art factory and global research and development center in the Incheon Free Economic Zone, Seoul http://bit.ly/L0uVp0

CHINA | ASE opened its Phase 3 manufacturing facility in Weihai, boosting discrete packaging and test capacity http://bit.ly/JLiFLp

EUROPE | ON Semiconductor expanded its Roznov, Czech Republic, operations with a 4,000sg.m. research and design facility http://bit.ly/LrgOoO

WORLD | Chinese suppliers of large-size LCD panels are the fastest growing segment of the industry, although major South Korean brands continue to dominate http:// bit.ly/KD6RXd

USA | Freescale Semiconductor named Gregg A. Lowe president and CEO, replacing Rich Bayer. Lowe joins Freescale from Texas Instruments http://bit.ly/Nn384h

## Semiconductor fabs use significantly less energy today, but work remains

Semiconductor manufacturing facilities dramatically decreased their normalized fab energy consumption from 1997 to 2011, shows The International SEMATECH Manufacturing Initiative (ISMI) Worldwide Fab Energy Study. Sanjay Rajguru, director of ISMI called energy-efficiency and conservation "critical" for semiconductor manufacturers.

Compiling data from 300mm and 200mm semiconductor fabs in Asia, North America, and Europe, the study's benchmark data helps identify areas to reduce energy use and improve efficiency in semiconductor manufacturing operations.

Process equipment consumes more than 50% of energy in a fab, found ISMI's Environment, Safety and Health (ESH) Center researchers. Energy consumption here halved in the study time period. Non-process-equipment energy consumption has dropped to one-fourth of 1997 values. The next highest energy users were central chiller plants and bulk gas production. Waste heat recovery and reuse practices were benchmarked for best-in-class performance.

To explore bulk-gas production energy efficiency, ISMI initiated a workshop in collaboration with experts at member companies. The participants benchmarked best-inclass metrics and reviewed best-inclass design practices for nitrogen plants, specifically focusing on air compressors, which consume up to 85% of the bulk gas energy budget.

Based on the energy survey results, ISMI will focus on efficiency at the nitrogen system, controlled dry air (CDA) system, process cooling water system, and process vacuum system. ISMI is also working to reduce water and chemical usage.

SEMATECH is an international consortium of leading semiconductor device, equipment, and materials manufacturers.-M.C

#### Guangzhou exemplifies China's LED industry

Guangzhou (China) Lightfair Conference is the biggest lighting fair in Asia, with companies throughout the LED lighting supply chain, including new Chinese MOCVD makers, International Solid State Lighting Alliance and China SSL Alliance. Citi alternative/renewable energy analyst Timothy Arcuri notes trends at the show in LED manufacturing and pricing ahead of China's subsidy program going into effect. Continued on page 9

www.solid-state.com

Qmags

**JULY 2012**

ECHNOLOGY

6

SOLID STATE TECHNOLOGY

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

## We've gone the extra mile so you don't go the extra nanometer.

**CHNOLOGY**

#### THE NEXT GENERATION HAS ARRIVED.

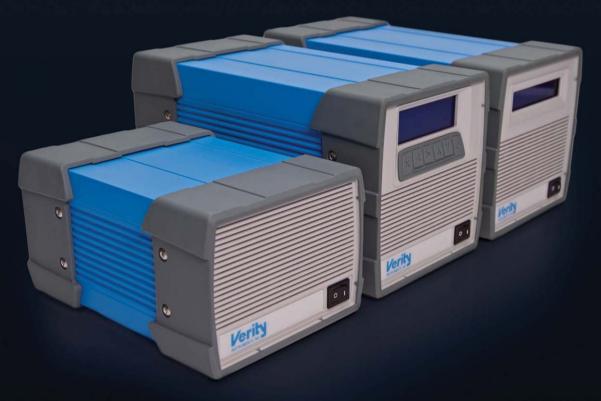

Introducing the latest additions to the Verity family of smart spectrometers featuring the SD1024X, a new industry standard that combines spectrometer and PC in the same space, eliminating the need for a dedicated applications computer. The new SD1024G Series delivers improved capability with industry leading ultra-performance, general purpose, and high resolution model options. Coupled with the compact FL2100 flashlamp module the new series addresses the broadest range of challenging plasma and film thickness/etch depth endpoint control problems. Now, more than ever, the first name in endpoint detection is the last word in performance. **Learn more at www.Verityinst.com.**

Omage

### **EVVS**cont

#### Biggest auto MEMS maker, biggest growth in 2011

**Bosch GmbH Automotive Electronics** of Germany retained its position as the world's top supplier of automotive MEMS in 2011, according to IHS.

Overall, 2011 revenue for automotive MEMS sensors amounted to \$2.24 billion, up 14% despite a disrupted supply chain in the aftermath of natural disasters last year in Japan and Thailand Expansion in the next two years will be driven by government mandates in the US and Europe for electronic stability control (ESC) and tire-pressure monitoring systems (TPMS).

The automotive MEMS Top 10 enjoyed combined revenues in 2011 of more than \$2.0 billion, up 11%. The top 10 comprised 91% of the market.

Booking \$625 million in revenue last year, Bosch's 19% expansion outpaced the growth of the automotive MEMS industry as a whole. It was also \$339 million ahead of the #2 supplier, Denso Corp., which grew 9% to post revenue of \$286 million in 2011.

"Bosch's success last year can be credited to its internal captive market, which promoted stable revenue and visibility into future demand for the company," said Richard Dixon, principal analyst for MEMS & sensors at IHS. "Bosch is the No. 1 supplier overall in MEMS sensor shipments for ESC systems in vehicles; as well as supplying the highest combined total of related automotive MEMS sensors such as accelerometers,

gyroscopes and pressure sensors. Bosch's performance was also boosted by a rapidly growing airbag market in China, along with a surge in demand for frontal and

an overly strong yen against the US dollar hindered exports.

Moving up a spot to #3 in 2011 was Panasonic, with revenue of \$202 million, up 12%. Most of Panasonic's

#### TABLE. Top 10 automotive MEMS manufacturer by revenues (\$M).

| Rank        | Company        | 2011 revenue | 2010 revenue | Y/Y growth |

|-------------|----------------|--------------|--------------|------------|

| 1           | Bosch          | \$625        | \$524        | 19%        |

| 2           | Denso          | \$286        | \$263        | 9%         |

| 3           | Panasonic      | \$202        | \$181        | 12%        |

| 4           | Freescale      | \$191        | \$190        | 1%         |

| 5           | Sensata        | \$190        | \$153        | 24%        |

| 6           | Analog Devices | \$161        | \$136        | 18%        |

| 7           | Infineon       | \$139        | \$117        | 19%        |

| 8           | VTI            | \$103        | \$76         | 36%        |

| Tie: 9 & 10 | GE Sensing     | \$64         | \$57         | 12%        |

|             | Delphi         | \$64         | \$62         | 3%         |

|             | Total Top 10   | \$2,025      | \$1,759      | 11 %       |

|             |                |              |              |            |

side airbags in the United States."

Denso is the major supplier in its domestic Japanese market, with a diverse customer base that includes almost half of Toyota's auto MEMS business. Denso reported heavy declines in sales in Q2 2011 after Japan's 3/11 earthquake-tsunami disaster, but recouped its losses during the next quarter. Denso is a top supplier of MEMS sensors of automotive heating/ventilation/ air conditioning (HVAC) systems, as well as satellite airbag accelerometers and oil-pressure sensors. The company's growth during the last two years has been relatively subdued compared to the rest of the auto MEMS market, because

SOURCE: IHS iSuppli Research, June 2012.

sales came from its automotive gyroscope business, reflecting a narrower focus compared to that of the leading two companies. However, Panasonic is the undisputed leader in in-dash navigation gyroscopes and ranks a very close second to Bosch in gyroscopes needed for ESC systems. The two devices are the highest-priced components in the automotive MEMS space. Panasonic is no longer the sole supplier of yaw rate sensors to European Tier-1 Continental, and in the future will see increased competition from VTI on combo-packaged inertial sensors for ESC systems.

Freescale Semiconductor dropped down one place to

**JULY 2012** SOLID STATE TECHNOLOGY

2

**ECHNOLOGY**

#4 with automotive MEMS revenue of \$191 million, in a near tie with #5 Sensata. Freescale is the leading supplier of satellite airbag accelerometers, even though it temporarily lost share in that market with earthquake damage at its Sendai, Japan facility. Sensata concentrates MEMS production on pressure sensors, and is #1 in highpressure applications like brake and common fuel rail sensing, using its silicon piezoresistive sensors that are glass-bonded to steel substrates. Sensata also had the second-highest yearly growth rate of 24%.

Among the remaining Top 10, growth ranged from 3% at Delphi to 36% for VTI, thanks to VTI's strong position in ESC accelerometers. Infineon and Analog Devices Inc. joined Bosch, Sensata and VTI in recording growth rates higher than the industry average, while GE Sensing had slightly below-average expansion of 12%.

Fuji Electric fell just outside the top 10, with overall revenue of \$30 million. Learn more about this topic with the IHS iSuppli report entitled: "Fat Years Ahead for Automotive MEMS Sensors."-M.C

#### Continued from page 9

The NDRC's demand rebate program is more positive than Citi originally estimated, because the rather meager RMB2.2B (~\$350MM) would get more funds if this iteration of the subsidy catalog's funds are depleted, expected to take only ~12-24months. Producers are even more excited by provincial-level subsidies, Arcuri says. In Guangdong, the province in which the conference took place, these will boost revenue for local LED producers to RMB5B (~\$850-900MM) by 2015.

Major buyers like Kingsun are finally coming to shop at the local LED makers, sourcing up to 60% of their LEDs domestically by 2013. Companies that months before were making Christmas lights are now making bulbs; bulbmakers are vertically integrating rapidly into fixtures. Lumens/W at these companies have increased dramatically even from last fall.

Citi heard of many examples of Chinese LED makers selling well below cost to gain an edge, and this could intensify as the government subsidies roll out.

Citi estimates that ~60% of all reactors shipped to China are turned on, with ~60% utilization on these tools, implying overall utilization of ~35-40%. The "gray market" for MOCVD tools is gaining steam, but provincespecific. Citi's observed talk of stronger vendors within a given province buying new, unused, or virtually unused tools from weaker vendors (in most cases recertified by the tool vendor). As long as the equipment does not leave the province, local government is happy, sometimes even "playing matchmaker" behind the scenes to force consolidation.-M.C

Andy C. Mackie PhD. MSc Global Product Manager amackie@indium.com

#### Visit my semiconductor blog for the latest on:

- 2.5D and 3D fluxes

- Package-on-package

- Pb-free power semiconductor solders

www.indium.com askus@indium.com ASIA • CHINA • EUROPE • USA

©2012 Indium Corporation

www.solid-state.com

**ECHNOLOGY**

SOLID STATE TECHNOLOGY **JULY 2012**  q

## **news**cont

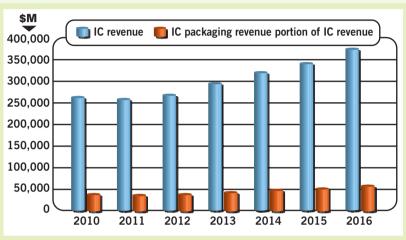

#### Packaging revenue outgrows package unit growth

Growth in smartphones and tablets and resurgent automotive demand are increasing IC demand. In turn, increased demand for product functionality is driving up IC packaging revenue faster — a 9.8% CAGR — than IC unit growth — 7.3% CAGR 2010-2016, says New Venture Research (NVR).

Handheld electronics will boost the growth of special purpose logic (SPL) communications chips by 16.7% CAGR revenue through 2016, versus 3.5% CAGR in

Photoresist Flow Meter

- No Moving Parts High Reliability

- Unique Sensitivity Highest Speed

- Non Invasive Straight Tubing Only

Specifications

Flow Rates

up to 120 ml/min

Repeatability

typical 1–2 %

Speed

response time down to 30 ms

Wetted Materials

PCTFE, Quartz Glass

SENSIRION Inc. Westlake Village CA 91361, 805-409-4900 www.sensirion.com

SENSIR

IC device and packaging revenue forecast (\$M), 2010-2016. SOURCE: New Venture Research.

units. Packages for mobile components are dominated by FPGA and QFN designs, which are at opposite ends of the pricing structure. The third most popular packaging type, QFP, is decreasing in usage over time.

Wireless infrastructure products are also in high demand, which is helping boost consumption for standard cell and programmable logic device (PLD) chips. These devices will grow at a CAGR of 16.1% in terms of revenue through 2016, while the device units are projected at 15%. High-I/O BGAs are the package of choice over the forecast period — package revenue growth is projected to be slightly higher, at 16.3% CAGR through 2016.

Logic chips are in demand for a host of products, pushing 32-bit MCUs to an 11.1% CAGR unit demand, although only 4.7% device revenue CAGR, through 2016. QFPs and BGAs are the highestdemand package designs, although the QFP is waning. Thus, the package revenue is growing at a CAGR of 12.8% through 2016 for 32-bit MCUs.

This information is included in the newly released report "The Worldwide IC Packaging Market, 2012 Edition", from New Venture Research (NVR), a technology market research firm.**–M.C**

10 JULY 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

## RIXTRON

#### QXP-8300: Cutting Edge ALD Product for Leading Edge Semiconductor Technology Nodes

#### QXP-8300 for Higher k Oxides, Metal and NVM Films

Excellent step coverage and gapfill of complex materials solution to memory market challenges

40% less precursor usage – lower CoC

Offers the best in class productivity through innovative mini-batch ALD reactor design

AIXTRON provides deposition systems with cutting edge technology for Logic, DRAM, NVM, Flash and MIM applications. QXP-8300 meets state-of-the art silicon production standards and enables innovative technology breakthroughs for sub 3x nm device feature sizes.

AIXTRON SE · info@aixtron.com · www.aixtron.com

#### Qmags

## From The ConFab:

## State of advanced packaging technologies

As packaging has played a larger and larger role in chip performance, form factor, and capabilities, Solid State Technology's The ConFab has increased its focus on back-end processes. Cue "Advanced Packaging and Progress in 3D Integration," a session chaired by Abe Yee, Nvidia, and featuring David McCann, senior director of technical business operations, GLOBALFOUNDRIES; Sandeep Bharathi, VP of engineering, Xilinx; Ron Huemoeller, SVP of advanced interconnect platform development, Amkor, and William Chen, VP, Advanced Semiconductor Engineering Incorporated (ASE).

2.5D and 3D packaging are coming together to enable the end-goal of silicon devices — high density, low power, low cost, high yield, small form factor heterogeneous silicon blocks integrated on one package, feeding a seemingly insatiable demand for video, Internet, etc. Society is shifting to "ambient intelligence," Chen said. McCann pointed out the interconnection density increase enabled by advanced packaging, whether it be 2D like flip chip bumps (10k I/Os per IC) or 3D like TSV (50k I/Os). Stacking silicon interconnects enables lower latency and power consumption in higher density than traditional I/Os, said Bharathi, creating 100X the die-to-die connectivity bandwidth per watt versus high-speed serial or standard parallel I/O.

Bharathi explained Crossover SoCs — devices that

#### Packaging

combine multiple functions on a single device with heterogeneous die. With active die stacked atop active die in a 3DIC, Crossover SoCs raise thermal and mechanical challenges. Bharathi looked at a case study of stacked silicon interconnects in FPGAs at Xilinx, FPGA building block "tiles" organized in columns then combined to create an FPGA. The device combines a 28nm active

Meredith Courtemanche, digital media editor

die and 65nm passive interposer, with low-risk microbumps and TSVs; the silicon interposer reduces stress with low-k materials.

Huemoeller zeroed in on TSVs, which can take monolithic die to die slices, or be used to segment monolithic analog/logic/cache functions onto separate die. Stacking die frees up process node choices. Wafer yield goes up, and costs go down, with no form factor sacrafice. Quoting Samsung, Huemoeller said that TSVs interconnecting stacked die offer 8X better bandwidth and 50% power savings compared to PoP.

Advanced packages call for new materials and assembly and test methods. McCann pointed out that transistors and packaging are not 2 isolated silos. Copper-filled TSV interconnects add stress to the silicon. Thinning on transistors also must be characterized for potential impacts. The wafer processing steps are complicated for advanced packaging, and KGD testing is still developing, Bharathi added.

Expect >80% CAGR for 2.5D interposers through 2015 (300mm equivalent). 2.5D interposers can be made from laminate, glass, or silicon, each with pros and cons. Laminates are limited to larger line/space pitch than package designs will require. Glass vias can be very expensive. Silicon interposer production is one option for idle legacy foundry lines, said Huemoeller.

Chen points out that, over time, various advanced packaging methods, such as WLP, die stacking, and interposer interconnects, are converging. Parallel trends are emerging that use silicon interposers and 3D packaging with heterogeneous integration. Heterogeneous integration puts MEMS devices, memory, logic processors, and RF devices all on one substrate, in a small form factor.

Read a discussion of the packaging supply chain with these ConFab speakers at http://bit.ly/KnQBsQ.  $\blacklozenge$

12

**ECHNOLOGY**

JULY 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

#### Qmags

## The demise of sapphire wafers?

"Are we witnessing the demise of sapphire wafers?" I was asked recently. "Not yet!" was my reply.

Today GaN epitaxial films grown on sapphire wafers provide the best solution for manufacturing LEDs. These chips are used as back lights in all mobile phones, all tablet computers, in most LCD-TVs , and will soon be used in many solid state lighting applications. Yields are improving, costs are dropping rapidly. Many new suppliers have entered the market. The use of LEDs for LCD-TV backlighting has provided a significant jump in unit volume – an important driver of scale and cost savings. Still people are looking for alternatives. Why?

LED makers want to move to larger wafers so they can lower unit costs. Most LED production is done on sapphire wafers 100mm in diameter and smaller. Semiconductor grade silicon wafers are readily available at 200mm and 300mm. If LED grade GaN epitaxial films can be grown on large silicon wafers, there could be a clear path to lower unit costs.

GaN epitaxial films grown on sapphire or silicon have many crystal defects. These defects cause yield loss and decrease the efficiency of converting electric current to light. The ideal material would be single crystal GaN. If large GaN boules can be grown, very

LEDs

chips lost to crystal defects. But life is not so simple. LED material systems are very complex. We

efficient LEDs might be built with very few

are operating at the edge of knowledge. It's hard to move fast. Progress is measured in decades, not years. For example, the spacing of atoms in GaN is a poor match to the atom spacing in silicon. Novel buffer layers have been developed to mitigate these problems. Recent results show

**Griff Resor,** Resor Associates, Maynard, MA USA

efficient LEDs can be built. But buffer layers add cost and production is still "2 years" away. In the meantime sapphire suppliers are supplying 150mm and 200mm wafers. It's no longer obvious that silicon wafers are

a "must have" technology for LEDs.

Sumitomo and Soitec have joined forces to fabricate high quality GaN engineered substrates. Sumitomo will grow the large boules of GaN. Soitec will use their ion-implant technology to slice off thin GaN films, and then attach these to carrier substrates. The Soitec "slicing" method will conserve expensive GaN

Bridgelux Inc. has achieved 135 Lumens per Watt GaN-on-silicon based LED technology

material. Still, cost, conversion efficiency and yield remain as serious unknowns.

This competition reminds me of the early days of IC technology. There was a two decade long debate about which technology was best for IC production. Silicon won, not because it was the ideal semiconductor material, but because it moved to high volume and low cost first and kept moving as more suppliers entered the market using silicon wafers. The parallel today in LED manufacturing is sapphire wafers. Sapphire may not be the ideal material, but it is rapidly moving ahead of the competition.

At SEMICON West this year, many of the teams working on these alternative material systems will be presenting their progress. There can always be a break-through result. Better check it out.  $\Rightarrow$

www.solid-state.com

SOLID STATE TECHNOLOGY JULY 2012 13

#### ALD

## Atomic layer deposition for metal gate integration

**MOHITH VERGHESE,** ASM America, Phoenix, AZ.

High-k based transistors have introduced the semiconductor industry to increasingly complex metal gate integration schemes and novel, low temperature deposition techniques such as ALD.

s high-k/metal gate (HKMG) technology becomes mainstream for high performance and low standby power logic devices, it is useful to review the rapid evolution of integration schemes that has made this new process architecture possible. The introduction of high-k as the gate dielectric of the transistor was one of the most significant of recent process integration changes in the semiconductor industry. Replacement of traditional silicon oxide (SiO<sub>2</sub>) and silicon oxy-nitride (SiON) dielectric layers was difficult in itself, but it was quickly discovered that metal gate integration was the single most challenging aspect of proliferating HKMG technology in production. Whereas past technology nodes utilized highly doped polysilicon gate electrodes for NMOS and PMOS devices, the use of high-k gate dielectrics necessitated a shift to metal gate electrodes. High-k materials like hafnium oxide (HfO<sub>2</sub>) were found to interact negatively with polysilicon, causing a variety of issues such as high threshold voltages  $(V_T)$  and increased equivalent oxide thickness (EOT)[1]. Metal gates, on the other hand, integrate well with the new metal oxide dielectrics, but can also come with a host of issues. Integration concerns such as film stability, compatibility with existing production flows, and contami-

nation in manufacturing fabs have to be taken into account. However, the single most important factor in choosing the appropriate metal gate is effective work function control. The effective work function of the metal gate dictates the ultimate threshold voltage of the device which in turn allows lower power operation and higher clock speeds.

#### **Transistor work functions**

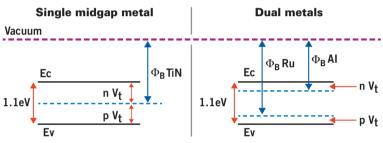

NMOS and PMOS transistors have different effective work function requirements to align appropriately with the respective Fermi levels in the underlying silicon (**Fig. 1**). To enable low  $V_T$  operation, band edge effective work functions are highly desirable (<4.1 eV for NMOS, >4.9 eV for PMOS) [2]. Metals have inherent theoretical work functions associated with them and it is possible to identify metal films which exhibit the required nominal

| Search Issue

**MOHITH VERGHESE** is the senior technical product manager at ASM America, Phoenix, AZ where he is responsible for ALD and Epi technologies. Ph: 1-602-470-2736, email: mohith.verghese@asm.com.

14 JULY 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

CHNOLOGY Previous Page

| Next Page

FIGURE 2. Effect of Thermal Budget on Metal Work Function

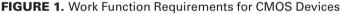

values. However, effective work function is highly dependent on the interaction at the metal-dielectric interface and hence it is sensitive to metal thickness, deposition techniques, film composition/contamination and thermal budget. In fact, the same metal can exhibit a wide range of effective work functions after complete device integration. One verity is the drift of the effective work function of most metals towards mid-gap (~4.5 eV) upon exposure to thermal anneals (Fig. 2) [3]. Furthermore, only a few metals exhibit the required thermal stability to survive the lengthy device manufacturing flow. The industry quickly converged on titanium nitride (TiN) as the most effective metal gate for HfO<sub>2</sub> based gate dielectrics. Novel low temperature deposition techniques like atomic layer deposition (ALD) are able to isolate a largely p-type version of TiN. However, thermal budget is still a concern and in traditional, gate first process flows, the TiN effective work function is driven to mid-gap after the high temperature, dopant activation anneals [4]. Some integrated device manufacturers (IDMs) have used innovative approaches to continue the use of gate first process flows along with a single mid-gap TiN based metal layer by the use of capping dielectric layers to modify the final effective work function of the device and maintain low  $V_{T}$  operation [5].

#### **Replacement gate processes**

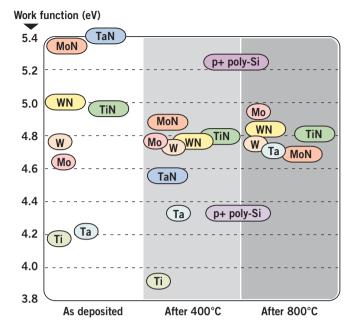

In recent years, some IDMs have transitioned to replacement gate (RPG) process flows where the formation of the high-k/metal gate stacks are performed after completion of all high temperature process steps such as dopant activation anneals. This enables a work-around the work function drift problems present in gate first integration and exploits the metals gate's native work function in the transistor [6]. While the result is a more complex integration scheme, the RPG flow gives unparalleled control of metal effective work functions. However, RPG flows also introduce more three dimensional challenges for deposition techniques. Removal of the dummy poly gate after spacer formation results in an opening that must be filled conformally with high-k and metal gate films with precise thickness control (Fig. 3). Because of its inherent conformality, ALD is a must for some of the critical steps of the formation of the metal gate stack for optimal control within the die and across the

FIGURE 3. Planar Replacement Gate Device Structure

entire wafer. NMOS work function has been the most elusive as most pure metals with low work functions (e.g. Al, Ti, Ta) are both unstable on high-k (resulting in metal migration and high leakage currents)[7] and difficult to deposit conformally at a low temperature by thermal ALD [8]. Hence, early versions of RPG technology used combinations of ALD, physical vapor

www.solid-state.com

ECHNOLOGY

deposition (PVD) and chemical vapor deposition (CVD) for metal gate formation.

As shown in Fig. 3, the novel RPG NMOS metal stack that has become standard in the industry uses a thin TiN layer and Ti/Al mixtures to set the correct effective work function [9]. Although the thin TiN layer alone is not enough to set the appropriate band edge work function, controlled diffusion of Al from the layer above allows for a work function shift towards the conduction band without degrading gate leakage significantly [10]. The PMOS transistor utilizes a thin TaN barrier along with a thicker TiN layer above it to prevent movement of Al close to the metal/high-k interface. This TiN-TaN-TiN stack is also responsible for setting a high, p-type effective work function for the PMOS transistor [11]. The final step is an Al contact fill for both NMOS and PMOS transistors. The difficulty in effectively controlling this complex RPG flow for planar devices is compounded as gate length scales. Tighter gate pitches result in higher aspect ratios and reduced real estate for the multiple metal layers required. Conformal fills of the required pure metals are also extremely challenging and variations in thickness of the thin TiN and TaN layers results in difficulty in controlling the  $V_{T}$  across multiple dies on the wafer and across different transistor channel lengths. Device reliability also becomes significantly challenging in highly scaled RPG devices.

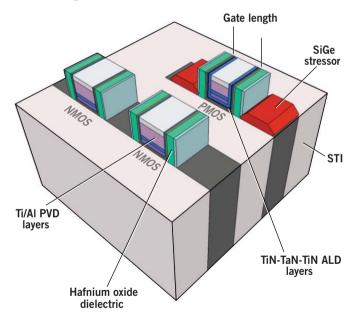

Scaling the planar transistor to gate lengths below 22nm has required high doping of the channel and source/drain regions to control short channel effects. As a result, random doping fluctuation is now a leading  $V_T$  variability issue [12]. A fully depleted device allows for a lighter channel doping or the complete elimination of doping in order to obtain better  $V_T$  variability control. As a result, a transition to three dimensional, FinFET type devices is underway for the most advanced logic nodes. Furthermore, FinFETs can relax EOT/  $L_{gate}$  scaling requirements as drive current enhancements can be achieved through better electrostatic control [13]. FinFETs also relax effective

work function requirements for metal gates (typically by approximately 100-200 mV) due to the undoped nature of the fully depleted fins [14]. However, a work function span is still required and RPG process flows remain the best path to achieve appropriate NMOS and PMOS targets.

The three dimensional channel region poses a larger issue for NMOS devices. While ALD TiN alone can achieve PMOS metal gate targets, PVD layers are no longer an option for setting NMOS work function. A

FIGURE 4. FinFET Replacement Gate Device Structure

non-conformal Ti/Al layer would result in variations in  $V_T$  both around the fin and between transistors. PVD films can neither conformally cover the fin nor is there enough space to pursue the complex multi-layer solution that was implemented for RPG planar devices (**Fig. 4**). As a result a low temperature, ALD, n-type work function material is a requisite for successful NMOS FinFET devices. This requirement has to be coupled with the previously discussed prerequisites of thermal stability and metal migration control. Ideally, the metal gate would be able to set the appropriate work function at the thinnest possible physical thickness to allow for denser packing of the fins and the transistors and for better scalability to future nodes. Furthermore, the work function metal should

www.solid-state.com

ALD

be compatible with the contact metal material so that valuable real estate between transistors is not used up by electrically inadequate barrier layers.

#### Conclusion

ECHNOLOGY

High-k based transistors have introduced the semiconductor industry to increasingly complex metal gate integration schemes and novel, low temperature deposition techniques such as ALD. Although these techniques are already immensely leveraged for RPG planar devices, the additional requirements for three dimensional FinFET device structures will further propel ALD into new spaces. The industry will inevitably see less of a reliance on traditional CVD and PVD metal films and an intense focus on ALD equivalents or replacements. Metal ALD has clearly become an enabling technology for gate stack integration in front end of line (FEOL) with expansion possibilities into middle end of the line (MEOL) and back end of the line (BEOL) applications.

#### References

- 1. C. Hobbs, et al., VLSI Tech Digest, (2003), p. 9-10

- 2. I. De, D. Johri, A. Srivastava, and C.M. Osborn, Solid-State Electron, 44 (2000), p. 1077

- 3. H. Y. Yu et al., IEEE Electron Device Letters, (2004), 25, p. 337

- 4. Westlinder, J. et al., IEEE Electron Device Letters, (2003), 24, 9, p. 550-552

- 5. S. Guha, et al., Applied Physics Letters, (2007), 90, 9, p. 092902-092902-3

- 6. F. Arnaud et al., IEDM Tech. Dig., (2008), pp. 633-636,

- 7. V. Misra, G. Lucovsky, G. Parsons, MRS Bulletin, (2002), p. 212-216

- 8. B.S. Lim et al., Nature Materials 2, 749 754 (2003)

- 9. Intel Xeon E5410 Microprocessor, Intel 45nm High-K + Metal Gate CMOS Process, Chipworks

- 10. X. R. Wang, et al., Microelectronic Engineering, (2011), 88, 5, p. 573-577

- 11. S. H. Bae, et al., VLSI Technology, (2004) p. 188-189

- 12. S. Borkar, IEEE Micro, (2005), 25, 6, p.10-16

- 13. B. Doyle, et al., VLSI Technology Digest of Technical Papers, (2006), p. 50-51

- 14. W. Haensch, et. al., IBM J. Res. & Dev., 50, No. 4/5 (2006)

#### Transfer valve for 450 mm wafer technology

L-MOTION valve for corrosive high-end semiconductor applications

Real L-MOTION valve technology assures uniform seal compression

- Excellent gate seal lifetime

- Highest yield through low particle count and high speed

- Lowest vibration

- Fast and easy gate exchange via top service cover

Visit us at Semicon - Booth #919

#### www.vatvalve.com

#### METROLOGY

## Impact of charge during gate oxide patterning on yield

JUNGTAE PARK, Samsung Electronics Co.; SUNGJIN CHO and JEFF HAWTHORNE, Ocept Technologies Inc.

Detection of non-visual defects in the steps prior to optical inspection was used to trace the cause of a silicon pitting defect.

chieving high yields in a leading-edge semiconductor manufacturing facility requires a dedicated effort to identify and eliminate the causes of defects that result in yield loss. Process measurement and inspection tools play a critical role in this effort by quantifying process variability and identifying the root cause of specific types of defects. A wide range of optical inspection tools have been developed to detect physical defects such as pits, particles and scratches. However, up to 30% of yield loss in today's fabs is not traceable to physical defects. Many of these yield issues are caused by Non Visual Defects (NVDs). NVDs are defects that are not detectable by optical inspection, and include sub-monolayer residues, contami-

nation, and process induced charging of dielectric films [1-3].

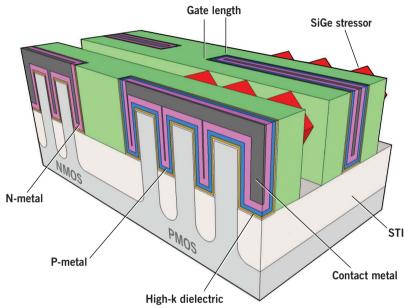

In this paper we discuss the detection and investigation of a silicon pitting defect. This physical defect was detected using standard optical inspection after an oxide wet etch operation, and resulted in yield loss at the end of line. Initial yield engineering efforts focused on varying the process conditions for the steps prior to inspection. This failed to eliminate the defect and was not successful in identifying the root cause of the pitting. Subsequent efforts focused on the detection of NVDs in the steps prior to inspection. This approach was successful in identifying the root cause, which enabled the optimization of the process and a

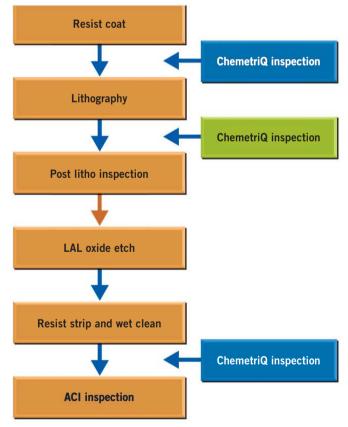

FIGURE 1. Process flow prior to detection of the silicon pitting defect at After Clean Inspection (ACI).

JUNGTAE PARK is senior engineer of defect analysis department at Samsung Electronics Co., LTD, Gyeonggi-Do, Korea. Tel: 82-031-209-0455, email: jtpark@samsung.com. SUNGJIN CHO is senior process technologist, application and development department at Qcept Technologies, 47354 Fremont Blvd, Fremont, CA. Tel: 510-933-1120, email: Jason.cho@qceptech.com. JEFF HAWTHORNE is vice president of advanced development at Qcept Technologies, 75 Fifth Street NW, Atlanta, GA. Tel: 404-526-6073, email: jeff.hawthorne@gceptech.com.

**JULY 2012** SOLID STATE TECHNOLOGY 18

ECHNOLOGY

www.solid-state.com

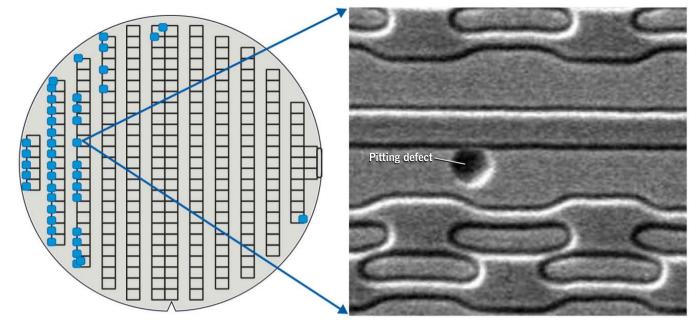

**FIGURE 2.** A defect map from a brightfield optical inspection tool used for ACI, and the SEM review image of one of the pit defects.

significant reduction in the overall defect rate, leading to higher end-of-line yield.

**Figure 1** shows the process flow prior to the point at which the pitting defect was detected. A wafer with a thermal oxide film is coated with photoresist. The resist is then patterned using lithography. This creates openings in the photoresist where the oxide film will be removed by the wet etch process. An optical inspection is performed after lithography (Post Litho) and prior to the etch operation. A wet etch of the oxide film is then performed in a low ammonium fluoride liquid (LAL), after which the photoresist is removed and the wafer cleaned. Finally, an optical After Clean Inspection (ACI) of the etched wafer is performed.

**Figure 2** shows a defect map from a brightfield optical inspection tool used at ACI. A large number of physical defects were detected, primarily near the left edge of the wafer. Scanning Electron Microscope (SEM) review was used to classify the defects as pits in the silicon surface. The image on the right of Fig. 2 is a SEM image of one of these pits.

The pitting defect was detected at ACI on 100% of the production wafers, and the defect maps showed strong correlation to end of line yield. The defect was not isolated to a single tool or set of tools, suggesting that the defect was induced by the process. The initial

**FIGURE 3.** ChemetriQ inspection was inserted into three points in the process flow for detection of possible NVDs. NVD charge results identified the inspection point inserted prior to Post Litho Inspection as the source of the process induced charge (show in green).

www.solid-state.com

#### METROLOGY

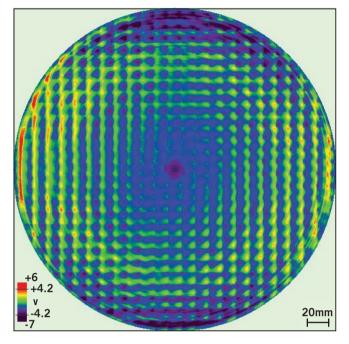

**FIGURE 4.** ChemetriQ charge map showing processinduced charge Post Litho.

assumption was that the defect occurred at the LAL oxide etch or the resist strip and wet clean operation. Experiments were run to vary the process conditions at these steps, but these variations had no effect on the number of defects. It was then decided to look at NVDs as a possible cause of the defect. metallic, and by charge trapped on or in dielectric films.

The first study inserted ChemetriQ inspections at the same points in the process as Post Litho Inspection and ACI (**Fig. 3**). No residues or charge were detected at ACI, but at Post Litho charge patterns were detected on the product wafers. Specifically, high positive charge, resulting in peak surface potential values ranging from +4 to +9 Volts, was detected primarily on the left side of the wafer in the region of the pitting defect as shown in **Fig. 4**.

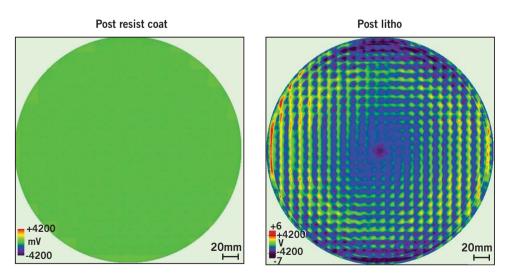

At this point, it was clear that the wafers were charged at Post Litho. An additional ChemetriQ inspection step was inserted after resist coat to better determine the source of the charge, as shown in Fig. 3. **Figure 5** shows ChemetriQ charge maps before and after lithography. Charge induced potentials after resist coat are near 0 Volts. However, after lithography the surface potential increases to greater than 4 Volts. This clearly shows that the source of the charge was the lithography step (expose and develop).

ChemetriQ inspection was implemented at Post Litho to monitor charge levels on production wafers. Peak charge levels were calculated on a per-die basis, thresholded, and exported to yield management software via KLARF files. The peak charge levels were well correlated with pitting defects detected at brightfield inspection (**Fig. 6**).

The ChemetriQ® inspection system from Qcept Technologies was used to inspect wafers at different points in the oxide etch process. This system uses a scanning surface potential difference imaging technique to generate fast, full wafer images of variations in the surface potential of a wafer [1]. Surface potential variations can be caused by several different types of non-uniformities such as sub-monolayer concentrations of contamination, including organics and

**FIGURE 5.** ChemetriQ charge maps of product wafers after resist coat and after lithography. Charge induced potentials after resist coat are near 0 Volts. Charge levels are much higher after the lithography process, where charge induced potential is greater than 4 Volts.

20 JULY 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

#### METROLOGY

**FIGURE 6.** High positive charge levels were thresholded and correlated with pitting detected by brightfield optical inspection.

Additional experiments were run in an attempt to modify the lithography process to reduce charging and, potentially, the number of pitting defects. It was found that by altering the lithography rinse process, peak surface potential values could be reduced to +3 to +5 Volts. In addition to reducing the overall charge levels, the optimized lithography process also reduced the number of wafers that had pitting defects from 100% to less than 20%, and fewer die were affected per wafer.

The success in reducing pitting defects by reducing surface charge provides strong evidence that charge on the photoresist prior to oxide etch was a direct cause of the pitting. This raises the question of how positive charge on an oxide film can lead to silicon pitting during etch. It is well known that hydrofluoric acid can electrochemically etch silicon if the wafer is anodized [4,5]. However, in this case no potential was applied to the wafer. Positive charge on the photoresist would have the effect of attracting electrons and repelling holes at the surface of the silicon, depleting p-type silicon of holes and eventually attracting enough electrons to invert the surface. This charge-induced biasing of the surface could be an important factor in accelerated etch of the silicon near the charged film, but additional work is required to understand the precise mechanism leading to pits.

In some cases, NVDs affect yield without creating a corresponding physical defect. For example, sub-monolayer metallic contamination can affect material properties resulting in yield loss. In other cases, NVDs can lead directly to physical defects through known mechanisms such as electrostatic discharge [3]. The pitting defect described here provides an interesting example where an NVD at one step in the process unexpectedly causes a physical defect at a later step in the process, which is then detected by an optical inspection tool. In this case the NVD, which is process induced charge, is a precursor to a physical defect, which is silicon pitting. This suggests that other physical defects might have precursor NVDs, such as charge or contamination, and that the detection of NVDs could provide useful insight into the cause of physical defects that are detected at later inspection steps. ◆

#### Acknowledgement

This article is based on an oral presentation given at the 2012 SEMATECH Surface Preparation and Cleaning Conference.

#### References

- K. Höppner, et al; Advanced Semiconductor Manufacturing Conference; Novel In-Line Inspection Method for Non-Visual Defects and Charging, (2009)

- 2. S. Raghavan, et al; Semiconductor International Webcast; Key Cleaning Challenges in High-Density Flash Manufacturing, (2007)

- 3. J. Hallady, et al; Sematech Surface Preparation and Cleans Conference; *Elimination of ESD Defects using DICO2*, (2008)

- Slimani, A. et al. (2009). Experimental study of macropore formation in p-type silicon in a fluoride solution and the transition between macropore formation and electropolishing, Electrochimica Acta, 54, 3139-3144.

- V. Lehman, S. Ronnebeck, (1999). The Physics of Macropore Formation in Low-Doped p-Type Silicon, Journal of the Electrochemical Society, 146 (8) 2968-2975.

www.solid-state.com

SOLID STATE TECHNOLOGY JULY 2012 21

| Next Page

Next Page

#### PACKAGING

## Bonding Wire: Is Scalability the Wave of the Future?

DOMINIK STEPHAN, RED Micro Wire Pte., Ltd., Singapore

A new technology enables bonding wire to be cast instead of drawn. The micro wire can be used like traditional copper bonding wire but offers several advantages that make it more cost-effective.

iniaturization and scalability continue to be major trends in the semiconductor industry, and they necessitate that the entire manufacturing infrastructure adapt and evolve in order to grow. In order to facilitate such growth, and greater miniaturization, it is important that the entire industry works together to attain new development targets, including those of wire bonding.

Miniaturization of bonding is critically correlated with the number of bond pads that must be placed per unit area. In the case of ball bonding, each bond pad must fully accommodate the ball bond within the bond pad, without encroaching onto adjacent bond pads. The ball/pad reduction factor applied in the industry is typically between 70-80%.

Next in line of correlation is the FAB (free air ball) during the process of bonded ball formation. Typically, the FAB is about 10-20% smaller than the bonded ball, due to the squashing of the latter during bonding. At the moment, the limiting factor for this FAB diameter is the wire diameter, assuming a typical BSR (the ratio between the FAB diameter over the wire diameter) is about 1.6-2.0. If we assume the smallest wires currently in mass production are about 0.6mil (15µm), this means that the FAB is about 24-30µm, bonded ball about 29-33µm, bond pad about 33-36µm, and bond pad pitch, at best, is  $35\text{-}38\mu\text{m}.$

Table 1 shows the correlation between process stage/bond pad pitch (BPP) and required bonding wire diameter to facilitate FAB formation.

The International Technology Roadmap for Semiconductors (ITRS) suggests the bond pitch should be down to  $20\mu m$  in 2013. This will require a large leap in wire manufacturing know-how. Back-calculating indicates the need for wire of 8-10 $\mu m$  in diameter. All major

#### TABLE 1. Required bonding wire diameter (µm)

| year of mass production        |      |      | 2005 | 2007 | 2009  | 2013 |

|--------------------------------|------|------|------|------|-------|------|

| process / BPP (bond pad pitch) | 50   | 40   | 35   | 30   | 25    | 20   |

| Bonded ball diameter           | 40   | 32   | 29.5 | 22.5 | 18.75 | 15   |

| FAB diameter                   | 32.4 | 31.0 | 27.0 | 18.7 | 15.6  | 12.5 |

| Wire diameter (at FSR=1.6)     | 20   | 19   | 17   | 12   | 10    | 8    |

| Wire diameter (at FSR=2.0)     | 16   | 16   | 14   | 9    | 8     | 6    |

wire bonding plants today are running 0.7mil copper wire (18µm) and have plans to qualify 0.6mil (15µm) within the next year or two. One of the critical factors for not seeking more aggressive targets is the lack of availability of a bonding wire of lower diameter and an infrastructure that supports such a process, including bonding machines and capillaries.

Current standard materials and tools make it possible to scale down to a certain level, but attempting to go beyond that leads to the figurative brick wall.

DOMINIK STEPHAN is the Director for Application and Product Marketing for RED Micro Wire (RMW) in Singapore.

www.solid-state.com

Capillary manufacturers are producing caps for 0.6mil wire in mass production having a hole diameter of about 21µm. There have been attempts to go as low as 15µm, accommodating

**FIGURE 1.** Fusing current (based on calculation) for wires of different wire diameter and testing length.

0.5mil wires, mainly for Au wire bonding. For copper wire bonding designs, the sizes to date have been typically slightly larger.

Wire bonding infrastructure is so extensive that no other chip-interconnection technology can displace wire bonding in the foreseeable future, although other technologies, particularly flip chip, will experience increasing utilization. Increasing miniaturization of electronic circuits has put relentless pressure on wire bonding technology to (1) increase yields (<5 ppm defects); (2) decrease pitch (<30µm for ball bonds) and (3) provide the lowest possible and ever decreasing cost.

#### Creating smaller wires – the challenges

Wire makers, wire drawing equipment manufacturers and tool makers are all approaching a boundary with existing technologies, although there are efforts to make smaller wires. When wire diameter is successfully reduced, more issues correlated with wire uniformity and production control of the low tension required during the drawing process appear. These may result in lower yield and higher cost. Another limiting point is the drawing die, which can experience high erosion and cause lower yields at very small diameters. Furthermore, once the wire is drawn to the final stage, it has dramatically "work-hardened" and must be recrystallized by an annealing process. This is typically done at about 30-60% of a metal's melting point at which, in return, it loses significant strength. This introduces further breaks, lower yield and higher cost. In order not to break the wire or stretch it (which would weaken its mechanical performance), annealing tension must be controlled at <0.5g. This is much less than the tension control capability of the typical dancer arms and pulleys supplying the tension. Here new technologies would be needed to facilitate wire drawing and annealing processes for cost effectiveness.

Even if the wire can be successfully drawn, the properties of the wire itself can be a challenge. As diameter decreases, strength decreases as a square function (0.5 mil is 25% the strength of 1 mil).

Assuming an average copper wire, having a tensile strength of about

www.solid-state.com

ECHNOLOGY

## PRESTO®

The New

#### Thermodynamic Power

Process Temperature Control Solutions for MOCVD, HB-LED

SOLID STATE TECHNOLOGY JULY 2012

23

#### PACKAGING

#### TABLE 2. Comparison of breakloads

| wire<br>diameter | normal<br>copper wire | soft copper<br>wire | RMW glass composite |

|------------------|-----------------------|---------------------|---------------------|

| <b>25</b> µm     | 9.8                   | 14.7                | 19.6                |

| <b>20</b> µm     | 6.3                   | 9.4                 | 12.6                |

| 15µm             | 3.5                   | 5.3                 | 7.1                 |

| <b>10</b> µm     | NA                    | NA                  | 3.1                 |

| 5um              | NA                    | NA                  | 0.8                 |

200MPa, the force needed to break the wire is only about 10g, making a 0.5mil wire only about 2.5g. Such a low material strength is very difficult to manually handle, and poses issues to testing strength during the appli-

cation. The stiffness is a fourth power (0.5 mil is 1/16 the stiffness of 1 mil – stiffness = deflection under a load.) This poses many issues to the handling and the application of the wire. In general, elastic modulus is not the same as stiffness. Elastic modulus is a property of the constituent material; stiffness is a property of a structure.

Another inherent issue with lower wire diameters is the electrical performance. Naturally, the current carrying capacity is lower with lower diameter. This needs to be taken into consideration by packaging designers.

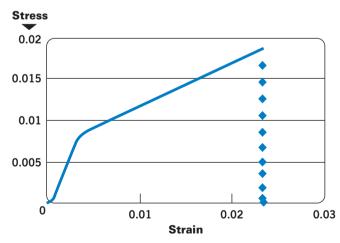

Recently there has been a new wire introduced that encases traditional copper wire in glass coating. Following, we'll take a look at how that wire scales versus traditional copper wire.

If wire properties are not sufficient, the wire will not hold its shape and will sag under its own weight. Here again a stiffer solution might help. Thinking outside the box, the ability to ignore the issue of adjacent wire shorting would ease this pain. However, increased strength is usually correlated to increased hardness, which is detrimental to the bond. The first bond poses a larger risk of cratering or bond pad deformation. The second bond poses the risk of lower strength values based on lower deformation and, respectively, a lower bond area. However, in glass coated wire, some of the strength comes from the glass layer, providing a geometric support. The hardness test shows that the copper core is even softer then a typically highly annealed copper wire, as seen in Table 3.

Table 2 is a comparison of breakload values (grams) for soft, normal and glass coated wire assuming 200,

300 and 400Mpa respectively (RMW wire is referred to as composite, because the glass is a structural member of the wire).

Table 3 wire hardness values of selected technologically available materials (\*refers to the copper core).

In normal bonding wire, we need high elongation in copper to ensure sufficient ductility to make a strong

#### TABLE 3. Wire hardness values

| wire hardness |

|---------------|

| 90-100        |

| 85-95         |

| 75-85*        |

|               |

second bond. However, in the case of glass coated wire, the EL/ BL of the wire includes the glass, but the glass is not part of the first or second bond. So the wire EL will not be high, however the copper core is still very ductile.

From the tensile test chart in **Fig. 2**, one can see that the glass plays an initial part of providing strength and limiting ductility. After further elongation, the glass will eventually crack and give way to the extension of the copper.

#### Using smaller diameter wires

Let's look at the next step: How wires are used in the wire bonder. Users are having difficulty threading the wires and only highly experienced users are able to thread a 0.6mil wire though the wire path and into the capillary, without breaking it.

Further reduction in wire diameter will decrease visibility and, more dramatically, decrease the stiffness of the wire, which makes threading more challenging. A wire that is in its geometry stiffer than usual wire would make this process easier.

**FIGURE 2.** Tensile test chart of a RED Micro Wire glasscoated wire.

www.solid-state.com

Qmags

24 JULY 2012 SOLID STATE TECHNOLOGY

The next issue is related to the loop formation. A2 wire is supposed to keep its loop shape, which was imparted from the bonder trajectory during the loop formation (which is, most of the time, highly advanced with various forward and backwards motions).

The next step in the process is typically the molding process, where the wires are heavily exposed to mechanical stress/sweep. Mold compound viscosity and melt front velocities require scrutiny.

Another consideration on the infrastructure is the use of a wire bonding capillary as a tool for the bonding machine. Typically made from ceramic, they are currently only available in mass production, down to a diameter of about  $15\mu$ m. They are getting increasingly difficult to make, but since there was no wire to drive the dimension, not enough effort has been applied to open these boundaries.

#### Glass-insluated wire - a solution to the problem

It is clear that there is a need for smaller wire diameter to support advances in miniaturization. There are, however, intrinsic challenges of physics that might limit the ability to manufacture and use such wire. Most of the issues are related the mechanical strength, and concerns about wire stability and shorting.

It seems natural to think about an insulated wire eliminating worry about shorting. Glass coated wire provides such an insulation and slightly inaccurate looping can be accommodated.

The issue of strength (or stiffness in this case) can also be addressed with the glass-coated wire. Glass that has an inherently higher strength compared to copper acts not only as a surface layer, but as an active element providing mechanical support to the wire. This leads to much higher strength and stiffness values compared to a bare copper wire (or any kind of coated wires, be it conductive or insulating).

Looking at the wire manufacturing process from a simplistic view, one could ask: How logical is it to cast the wire at a very large diameter, just to draw it down to a small diameter?

A solution whereby wire can be manufactured directly out from the melt covered by a glass coating is currently being tested and optimized for bonding wire applications.

Glass can greatly increase wire strength and stiffness, yet still provide a smaller, effective wire diameter on smaller bonds. Based on the manufacturing method, a full coverage of glass can be ensured, which in return ensures insulation. In addition, floor and shelf life are no longer limiting factors since there is no exposure of copper.  $\diamond$

#### Acknowledgement

The author would like to thank Dr. Jeffrey Seuntjens and Mr. Steven Creswick for their technical feedback, discussion and review, as well as the industry partners SPT, ASM, ITE and TPT for their experimental support.

株式会社フリチストン Bridgestone Corporation purebeta.com

www.solid-state.com

CHNOLOGY

| Next Page

#### MEMS

## Volume consumer markets are changing MEMS manufacturing

ERIC MOUNIER and JÉRÔME BARON, Yole Développement, Lyon, France

Changes in the way MEMS are manufactured are primarily being driven by high volume consumer MEMS markets.

igh volume consumer MEMS markets are driving manufacturing changes across the MEMS industry, pushing companies to drive down die size, closely connect multiple die in combinations, and move towards an efficient infrastructure for system-level integration of high value solutions for final OEM customers. That means new demands -and new opportunities—for tighter process controls, more integrated waferlevel packaging technologies, more standard process and package platforms, and more software for easy-to-use integrated sensor solutions.

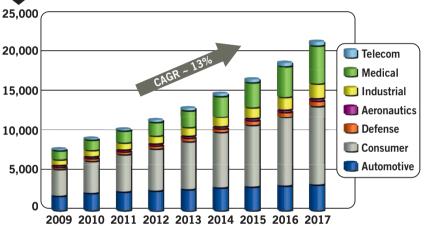

While the MEMS market still contains a highly diverse range of products, with plenty of specialty niches and high performance applications, it's also increasingly a volume consumer business. Consumer applications accounted for more than 50% of total MEMS industry revenue in 2011 (Fig. 1). And the four main devices for consumer mobile applications-accelerometers, gyroscopes, magnetometers and microphones—accounted for more than 50% of all MEMS units shipped last year (including automotive). Volumes will continue to expand, as smart phone shipments are likely to keep growing strongly, from 300 million units in 2011 to more than 800 million by 2016, and MEMS content per phone is also growing rapidly. More of

#### Sales forecasts (M\$)

FIGURE 1. The MEMS market is increasingly dominated by consumer applications, which inescapably means high volumes, short product cycles times, and pressure for low costs. Source: Yole Developpement.

> those MEMS devices will be combined into multisensor modules, both to reduce costs and to improve performance, as more accurate location and navigation information becomes a key distinguisher for smart phones. We expect these combo units will steadily replace discrete sensors and account for most of the growth in the inertial sensor market going forward, to become a \$1.7 billion opportunity by 2017.

#### Packaging innovations and production volumes drive die shrinks

Key to driving down costs to enable the growth of the consumer MEMS market is the rapid scaling down of die and package size. Over the last three to four

ERIC MOUNIER is senior analyst, MEMS devices and technologies, Yole Développement, Mounier@yole.fr, and JÉRÔME BARON, business unit manager, advanced packaging, Yole Développement, baron@yole.fr.

**JULY 2012** SOLID STATE TECHNOLOGY 26

**CHNOLOGY**

**Previous Page**

www.solid-state.com

years, MEMS 3-axis accelerometer die have shrunk from 12mm<sup>2</sup> down to 2mm<sup>2</sup>. The next generation is headed to 1mm<sup>2</sup> die size. That has helped push production cost of the packaged and tested consumer accelerometers sharply down from nearly \$.40 in 2008 to \$.25 by 2011. Gyroscopes are similarly shrinking fast. Typical 2-axis gyroscope die were 6mm<sup>2</sup>-8mm<sup>2</sup> in 2007. Now InvenSense's 3-axis gyro is ~4mm<sup>2</sup>. Manufacturing

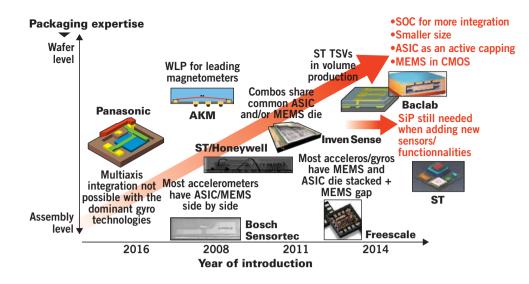

**FIGURE 2.** Demand for smaller, lower cost die, and faster handling of more complex multisensor data will drive MEMS packaging towards more value at the wafer level, with more TSVs and monolithic integration. Source: Yole Developpement.

cost has come down accordingly, with the current 3-axis packaged gyros costing the same \$0.75-\$0.85 to produce as did old 2-axis versions three years ago.

Production volumes are one key contributor to driving down die size and costs. Though wafer volumes with the tiny MEMS die of course remain small compared to CMOS, MEMS wafer volumes are getting big enough to drive tighter manufacturing controls that allow driving down the feature size. Robert Bosch credits its consumer pressure sensor production for accelerating its tight control of its manufacturing process, as getting to multimillion unit volumes in months instead of years allows it to push the limits of size and thickness much faster, which it has then transferred to its automotive products. STMicroelectronics famously credits the high volumes of its single process platform used for all its accelerometers and gyroscopes for driving the tight process control to reduce structure size and maintain consistent performance across units.

Now new packaging approaches are starting to play an increasing role in shrinking the devices. The increasing use of metal-to-metal sealing to replace glass frit bonding frames will significantly reduce the die space required. SystemPlus' reverse engineering of STMicroelectronics latest 3-axis accelerometer, for example, shows it is using gold eutectic sealing instead of glass frit to shrink packaged die size from 4.7mm<sup>2</sup> in the last generation down to 2.1mm<sup>2</sup>. Wafer-level packaging and through-silicon or through-glass vias are poised to reduce the contact pad area to shrink the die size even more. ST has recently launched an accelerometer with TSV, for example. By eliminating the area once used for I/O pads, the TSV process allows the MEMS die area to be reduced by ~25% compared to the usual accelerometer. It adds major manufacturing changes that increase the final wafer cost by more than \$100, but the reduction in die size still makes the final die cost competitive. Oma

#### **Combo sensors create new demands**

The coming industry transition to combination sensors, putting two or more MEMS sensors in a single module, sharing one ASIC and one package, will also make more complex demands on backend processes (Fig. 2). Packaging, assembly and test currently account for some 35%-45% of the typical manufacturing cost of a MEMS accelerometer, more than either the MEMS die or the ASIC, and the added complexity of the combo modules will likely move even more of the value to these manufacturing steps. Effectively managing increasing volumes of sensor data from the combos, such as to reduce sensor drift for more accurate position sensing, will require shorter, faster connections between the components than the current standard wire bonding, likely driving the modules towards interposer and TSV solutions. That means the modules will need to be assembled with high yields from known good die to be economic, and then all six or nine or ten sensor axes tested and cross-calibrated.

www.solid-state.com

| Search Issue

Qmags

#### MEMS

**FIGURE 3.** Intertial sensors combo stacked in SiP module on organic laminate substrate. Courtesy of STMicroelectronics.

Manufacturers will also need to figure out how to assure users of second sources for the complex multicomponent systems. **Fig. 3** shows one example.

#### **Cost and volumes drive MEMS**

CHNOLOGY

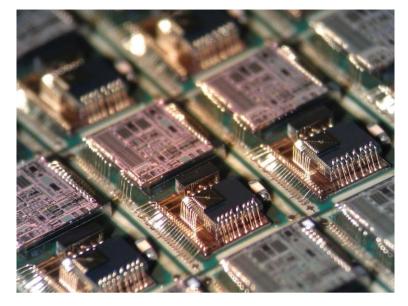

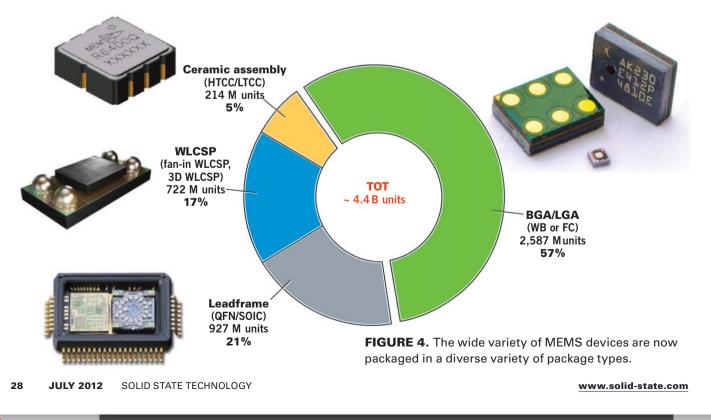

While most successful MEMS IDMS and foundries have long worked to re-use the same front-end process module for different devices as much as possible to speed time to market and time to yield, volume consumer markets are driving the sector towards standard package platforms as well, as these consumer markets do not have the luxury of time or cost to support development of fully custom packages. Naturally the wide range of different MEMS devices will maintain their different needs, but several different types of standard platforms, driven by big players in big markets, will likely develop, such as WLP and TSV interconnects, or SiP modules with micro leadframes, or chip arrays using molded or cavity packaging (Fig. 4). For example, microphone packaging from major suppliers has all now settled around the same general platform MEMS and ASIC wirebonded in a SiP module on BGA/LGA laminate PCB substrate with an air access hole, under a metal lid.