# We've gone the extra mile so you don't go the extra nanometer.

THE NEXT GENERATION HAS ARRIVED.

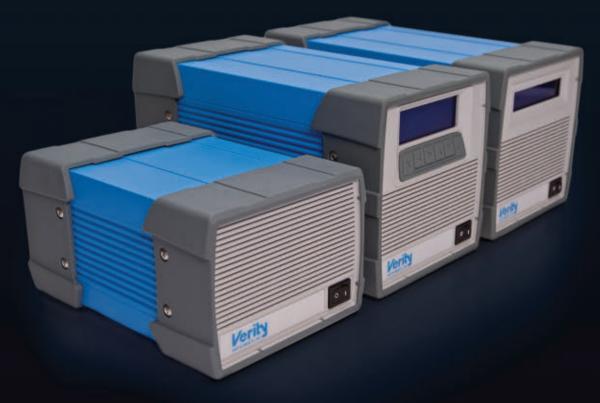

Introducing the latest additions to the Verity family of smart spectrometers featuring the SD1024X, a new industry standard that combines spectrometer and PC in the same space, eliminating the need for a dedicated applications computer. The new SD1024G Series delivers improved capability with industry leading ultra-performance, general purpose, and high resolution model options. Coupled with the compact FL2100 flashlamp module the new series addresses the broadest range of challenging plasma and film thickness/etch depth endpoint control problems. Now, more than ever, the first name in endpoint detection is the last word in performance. **Learn more at www.Verityinst.com.**

Semicon West South Hall Booth 706

JULY 2013

Extension M E D I A

# Solid State TECHNOLOGY Insights for Electronics Manufacturing

Measuring Critical Dimensions P. 21

Innovative Automation for 450mm P. 26

Paradigm Changes in 3D-IC Manufacturing P. 29

FD-SOI Targets Mobile Apps R 15

## A quick start guide to MAXIMIZING our interactive features.

Peruthett

# reduce soft errors

## Deliver more density on your IC packages without soft errors.

Honeywell RadLo<sup>™</sup> low alpha packaging materials help eliminate soft errors and single event upsets by reducing alpha emissions, a significant source of these problems. This is becoming increasingly important as chip dimensions and designs continue to miniaturize. Our leadership

and expertise in low alpha refining and metrology mean that Honeywell can help you meet critical alpha emission levels.

Honeywell reliability. Reliable low alpha. Make sure to ask your suppliers if they are using Honeywell RadLo low alpha materials for their chip packaging processes.

## Honeywell

Find out more by visiting us at www.honeywell-radlo.com

Although all statements and information contained herein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information and results obtained. Statements or suggestions concerning the use of materials and processes are made without representation or warranty that any such use is free of patent infringement and are not recommendations to infringe any patent. The user should not assume that all toxicity data and safety measures are indicated herein or that other measures may not be required. ©2013 Honeywell International Inc. All rights reserved.

JULY 2013 VOL. 56 | NO. 5

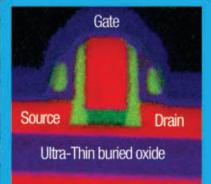

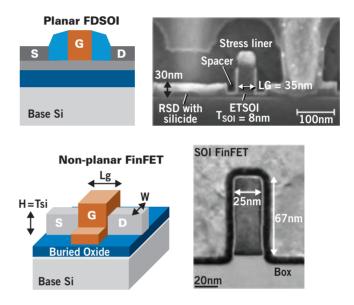

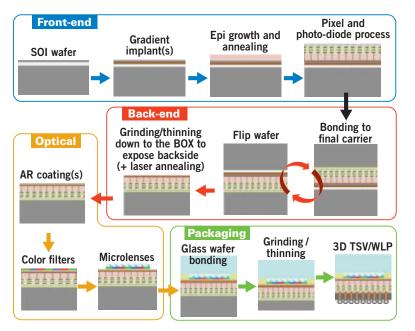

Fully depleted (FD) transistors are recognized as an effective solution for reducing the VT variability caused by random dopant fluctuation (RDF). As a planar technology, FD-SOI applies existing and design and process experience to smallchannel transistors. Source: ST Microelectronics.

#### FEATURES

#### soi | FD-SOI targets mobile applications

FD-SOI technology platform is perfectly suited for mobile IC applications where the power consumption has to be very low to maximize battery lifetime. *Giorgio Cesana, STMicroelectronics, Crolles, France and Carlos Mazure, Soitec, Bernin, France.*

## **METROLOGY** | Effects of measured spectral range on accuracy and repeatability of OCD analysis

A broadband polarized reflectometry measurement, utilizing RCWA analysis, can be used to obtain detailed trench profile results. *Franz Heider, Infineon Technologies, Villach, Austria; Jeff Roberts, Jennie Huang, John Lam and Rahim Forouhi, n&k Technology, San Jose, CA.*

21

COVER

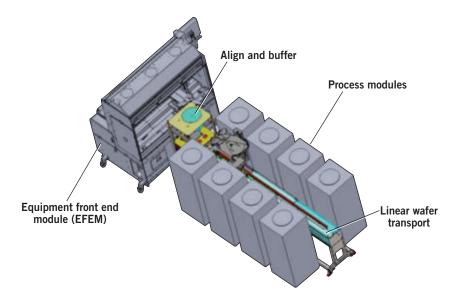

## **AUTOMATION |** Innovative automation approaches for 450mm factories

New approaches can help improve cycle time and achieve higher purity inter-process wafer environmental control. *Michael Brain, May Su, Anthony Bonora, and Daniel Babbs, Brooks Automation, Chelmsford, MA*.

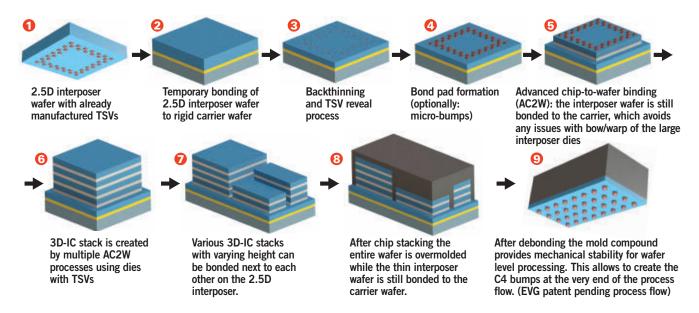

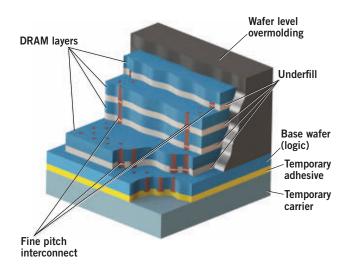

#### **3D INTEGRATION** | Paradigm changes in 3D-IC manufacturing

The process flows applied today for real product manufacturing are quite different from the process flows initially proposed for a universal 3D IC. *Thorsten Matthias and Paul Lindner, EV Group, St. Florian, Austria.*

## **SEMICON WEST** | Semicon West: Precision is key to scaling below 14nm

TechXPOT speakers highlight the challenges ahead on the road to 14nm. *Debra Vogler, SEMI, San Jose, CA*

#### COLUMNS

- **3** Editorial | A new inflection point for SST, Pete Singer, Editor-in-Chief

- **13** Packaging | Inside the ASET Dream Chip, Phil Garrou, contributing editor

- **14 MEMS** | MEMS: After the prototype, *David DiPaola, contributing editor*

- **41** Industry Forum | Learning the secrets of design for yield, Dr. Zhihong Liu, ProPlus Design Solutions

#### DEPARTMENTS

- 2 Web Exclusives

- 4 News

- **36** New Products

- 40 Ad Index

# Online@www.solid-state.com

### Web Exclusives

## 450mm – It's bigger than you think

Much has been said of the 450mm transition. But the description of this inflection is something of a misnomer. Though everyone desires a smooth, coordinated and orderly conversion, it may be a little less placid than the term "transition" implies. Rather, I suggest calling it the 450mm "transformation." Because, even for the segments that continue manufacturing semiconductor devices on 300mm and 200mm silicon wafers, the industry will change dramatically with the introduction of 450mm wafer processing. http://bit.ly/19M928x

### Necessary attributes of a MEMS engineer for new product development

In the development of new MEMS products, the team is the most important factor. With this in mind, let's review the necessary

attributes that make these engineers and entrepreneurs so successful in MEMS new product development. http://bit.ly/14sfjEg

### Get the latest SEMICON West 2013 news

Solid State Technology

will be reporting live every day at SEMICON West 2013. Be sure visit our exclusive SEMICON West 2013 page for all the latest on presentations, breakout sessions, product reveals, and more. http://bit.ly/14kRjkv

#### **Economy threatens semi** growth, not technology-so say fab engineers at ASMC

Chipworks' Dick James reviews ASMC 2013. "I always come away impressed by the quality of the engineering involved; not being a fab person myself any more, it's easy to get disconnected from the density of effort required to equip a fab, keep it running and bring new products/processes into production," he says. http://bit.ly/14OT8VB

#### **Tune in to the Solid State Watch**

Want to stay up-to-date, but only have a few minutes? Check out our weekly newscasts for a recap of leading industry headlines. http://bit.ly/17LtRQs

#### **Insights from the Leading Edge: The future of** packaging

Everyone understands the "Moore's Law Coming to an End" arguments. Dr. Phil Garrou believes that exactly when it will happen is less relevant than the fact that it is happening or has already happened for many mid-tier IC fabricators. Some top-tier fabs / foundries will find a way to move forward past 22nm to 14nm and beyond, but the important point is that the vast majority won't. This is not because the technology won't be available to them, but rather because it will be too expensive. http://bit.ly/12fsU3B

## editorial

## A new inflection point for Solid State Technology

At press time, inflection points have been top of mind, as we get ready for The ConFab. I've been reviewing all the presentations and looking forward to a fantastic event. A recurring theme is that the semiconductor industry is at an inflection point as process complexity and cost increase, consolidation across the supply chain continues, and as the need for greater synergy between design and manufacturing becomes ever more apparent.

At Solid State Technology and The ConFab, we are also at an inflection point. I'm delighted to announce that we are now part of Extension Media LLC. San Francisco-based Extension Media operates more than 50 business-to-business magazines, engineers' guides, email newsletters, web sites and confer-

# The requirements of mobile devices have become the main driver in the industry.

ences, including Chip Design, ChipDesignMag. com, EECatalog.com, Embedded Intel® Solutions, Embedded Intel® Solutions China, EmbeddedIntel. com, AutodeskCatalog.com and the Multicore Developers Conference. Extension Media also co-produces SLDCommunity.com, LP-HP.com and SemiMD.com in partnership with the Sperling Media Group.

Andy Grove, Intel's co-founder, described a strategic inflection point as "an event that changes the way we think and act." That's certainly true for me, as I look at the expanded reach of our combined forces and the potential for greater synergy between Solid State Technology, Chip Design and Extension Media's other brands.

As far as the rest of the semiconductor industry goes, it's clear that wafer costs are rising at a faster rate, partly due to increased process complexity and the delay in EUV. The cost/transistor is increasing by Moore's Law is slowing. 450mm may help, but the cost model has to be proven.

On the other hand, the requirements of mobile devices on PPAC (power, performance, area and cost/ complexity) have become the main driver in the industry. It's quite possible that some consumer-driven disruptive technology is around the corner. Chips embedded in flexible displays? Internet of Things. Bioelectronics in clothing? Those are already happening.

What's the next inflection point? The ConFab 2014 will take place on June 22-24 in Las Vegas at The Encore at the Wynn. Mark it on your calendars, and I'll see you there.

-Pete Singer, Editor-in-Chief

## Solid State TECHNOLOGY.

John Blyler, Vice President, Chief Content Officer Ph: (503)614-1082, jblyler@extensionmedia.com Pete Singer, Editor-in-Chief Ph: (978)470-1806, psinger@extensionmedia.com Shanon Davis, Editor, Digital Media Ph: (603)547-5309, sdavis@extensionmedia.com PhII Garrou, Contributing Editor Dick James, Contributing Editor

#### CREATIVE/PRODUCTION/ONLINE

Spryte Heithecker, Production Manager Jenn Burkhardt, Media Coordinator Nicky Jacobson, Graphic Designer Jacob Ewing, Graphic Designer Mariam Moattari, Senior Web Developer PENNWELL JULY ISSUE PRODUCTION TEAM Angela Millay, Editorial Art Director Sheila Ward, Production Manager Dan Rodd, Illustrator Debbie Bouley, Audience Development Marcella Hanson, Ad Traffic Manager

#### MARKETING/CIRCULATION

Jenna Johnson, jjohnson@extensionmedia.com

#### Extension M E D I A

CORPORATE OFFICES Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com 1786 18th Street San Francisco, CA 94107

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2013 by Extension Media LLC. All rights reserved. Printed in the U.S.

Please send news articles to sdavis@extensionmedia.com

#### worldnews

*EUROPE* | Silicon Labs announced its agreement to acquire Energy Micro AS.

USA GLOBALFOUNDRIES unveiled certified design flows to support 2.5D IC product development at the 50th Design Automation Conference in Austin, Texas.

**EUROPE** Fraunhofer Institute for Solar Energy Systems ISE will partner with EV Group to develop equipment and process technology to enable electrically conductive and optically transparent direct wafer bonds at room temperature.

ASIA Researchers from Ulsan National Institute of Science and Technology in South Korea and University of Illinois, U.S.A, developed the large-scale heteroepitaxial growth III-V nanowires on a silicon wafer.

**EUROPE** | **Alchimer** announced plans to collaborate with imec to evaluate copper filling solutions on advanced nano-interconnect technologies.

ASIA | United Microelectronics Corporation joined IBM's chip alliance for 10nm process development.

**USA** | **Intel** purchased the Global Navigation Satellite System business unit of ST-Ericsson.

ASIA At VLSI 2013 Symposium in Kyoto, Japan, imec highlighted new insights into 3D finFETs and high mobility channels scaling for the 7nm and 5nm technology node.

## Abu Dhabi doubles down on semiconductor research

The Advanced Technology Investment Company (ATIC) and the Semiconductor Research Corporation (SRC) last month launched the ATIC-SRC Center of Excellence for Energy Efficient Electronic Systems (ACE4S), to be hosted jointly in Abu Dhabi by Khalifa University of Science, Technology and Research, and Masdar Institute of Science and Technology. ATIC will dedicate over AED 17.5 million to the project over the next three years, which will be matched collectively by Masdar Institute and Khalifa University for a total budget of more than AED 35 million. This funding will drive innovation in next-generation electronic systems ranging in applications from smart phones and medical devices to the Internet of Things.

"This center is a significant research milestone for Abu Dhabi, the UAE and the region," said Sami Issa, Executive Director at ATIC. "ACE4S is a critical building block of our ecosystem strategy to help enable the development of homegrown talent in key areas of science and technology. Such talent development is essential as Abu Dhabi transitions into an innovation-based society as per the 2030 vision."

"Over the past 30 years, SRC has successfully helped establish

numerous university research centers and distributed more than \$2 billion dollars in research funds in the United States: ACE4S role as our first international center reflects significantly on the quality of research we pursue," said SRC President Larry Sumney. "The ACE4S Center has been established with valuable industry guidance from companies such as GLOBALFOUNDRIES, AMD, Applied Materials, Freescale, IBM, Intel, Mentor Graphics, Texas Instruments and Tokyo Electron (TEL) and will build on SRC-sponsored university research supporting 15 individual researchers in the UAE. Top semiconductor industry experts will oversee and serve as liaisons for each research task, and SRC will productively guide the overall research while also promoting strong student engagementenabling us to identify areas of areatest need and foster the move of innovations from lab to market."

The center will be overseen by a steering committee of highlevel ATIC, SRC, Khalifa University and Masdar Institute representatives and will be directed jointly by Professors Mohammed Ismail of Khalifa University, and Ibrahim Elfadel of Masdar Institute. The directors will oversee research across five targeted areas and work closely with a Technology Advisory

# **EVVS**cont.

Board (TAB) of representatives from industry-leading companies.

GLOBALFOUNDRIES will serve a special role on the TAB, assigning Mohamed Lakehal as an Abu Dhabi-based industrial liaison to oversee design tape-outs to fabrication in GLOBALFOUNDRIES' facilities worldwide. The liaison will also support design enablement, deploying design-for-manufacture tools and raising the level of local semiconductor expertise.

"As a research-oriented institution, we are proud to be part of the ACE4S leadership and offer our expertise and research capabilities," said Dr. Fred Moavenzadeh, President, Masdar Institute. "Our faculty will aim to develop microelectronic technologies with healthcare applications individually and in collaboration with their peers within the initial period of the center's operation. These innovative products will include biosensor applications, wearable devices and self-powered wireless body area networks (WBAN). We believe these applications will have a wide impact because of their energy efficiency and novel designs."

"This partnership will transform the way we conduct research in nano-scale energy efficient systems-on-chips as it will help us educate and train a highly skilled workforce with relevant skills. This is a key element in driving innovation and entrepreneurship in the UAE's semiconductor sector in line with the Abu Dhabi 2030 vision," said Dr. Tod A. Larsen, president

of Khalifa University. "The involvement of the SRC and its member companies in center development

will help create a world-leading institution with a sustainable university/ Continued on page 6

## **POWER SOLUTIONS FOR** SEMICONDUCTOR DESIGN, MANUFACTURE AND TEST

SEE US JULY 9-11 **SEMICON WEST 2013** SAN FRANCISCO, CA I MOSCONE CENTER

- Semiconductor design simulators

- Die bonding

- Clean room environments

- ► ATE and chip testing

- Wafer fabrication

- Ion implantation

- LED fabrication

#### **FEATURES**

- ▶ Liquid cooled

- ► Fan cooled

- Multi output

- Redundant systems

www.tdipower.com | 908.850.5088

# **NEV/S**cont.

# GLOBALFOUNDRIES unveils plans to accelerate adoption of 20nm-LPM and 14nm-XM finFET processes

At the 50th Design Automation Conference (DAC) in Austin, Texas, GLOBALFOUNDRIES unveiled a comprehensive set of certified design flows to support its most advanced manufacturing processes. The flows, jointly developed with EDA providers, offer support for implementing designs in the company's 20nm low power process and its 14nm-XM finFET process. Working closely with Cadence Design Systems, Mentor Graphics and Synopsys, GLOBALFOUNDRIES has developed the flows to address the most pressing design challenges, including support for analog/mixed signal (AMS) design, and advanced digital designs, both with demonstration of the impact of double patterning on the flow.

The GLOBALFOUNDRIES design flows work with its process design kits (PDKs) to provide real examples that demonstrate the entire flow. The user can download the design database, the PDK, detailed documentation and multi-vendor scripts to learn how to set up and use the GLOBALFOUNDRIES design flow.

"As the developer of the industry's first modular 14nm finFET technology and one of the leaders at 20nm, we understand that enabling designs at these advanced process nodes requires innovative methodologies to address unprecedented challenges," said Andy Brotman, vice president of design infrastructure at GLOBALFOUNDRIES.

#### Production ready AMS flow from specification to verification

To address the unique requirements of analog/mixed signal (AMS) design at advanced processes, GLOBALFOUNDRIES enhanced its design flows to provide production quality scripts and packaged methodologies. The new reference flow establishes a working flow from specification to physical verification that has been taped out to be verified on working silicon.

The AMS reference flow provides comprehensive double pattern design guidelines. It gives overview of decomposition flow for both block level and chip level. The flow also addresses decomposition for different design styles. Recommendations for color balancing, hierarchical decomposition, ECO changes are discussed. The flows also present decomposition impact on DRC run time and resulted database size.

Notably, the reference flow includes support for efficiency and productivity improvements in the Cadence Virtuoso environment specifically for designing in a double patterned process. The flow includes support for Virtuoso Advanced Node Continued on page 10 **Semiconductor research** *Continued from page 5* industry collaborative research environment conducive to high-tech job creation and direct local and foreign investment."

The center will focus on energy efficient devices with research in energy harvesting, power management, sensor technologies and wireless communications networks. The research will be conducted primarily at Khalifa University and Masdar Institute but with important involvement from UAE University, American University of Sharjah and New York University, Abu Dhabi. Within the first three years, ACE4S will seek to produce integrated prototypes with healthcare applications as well as knowledge and research relevant to safety and security, aerospace, water quality and the environment.

Supporting the transition of innovations to market, the center will develop an aggressive Intellectual Property Management Plan (IPMP). The IPMP will include early identification of interconnected families of innovation arising from technical themes, placing special emphasis on the integrated systems selected for demonstration at the end of year three.

ACE4S is a continuation of ATIC's broader focus on cultivating a technology research ecosystem within Abu Dhabi. Additional programs supported in this vein include: the Twin-Labs research center, a collaboration between Masdar Institute and Technical University of Dresden with support from the State of Saxony, ATIC and GLOBALFOUNDRIES; the ATIC professorship chairs at UAEU and Khalifa University; the Masters in Microsystems degree in collaboration with Masdar Institute; and ongoing MEES research grants in collaboration with the SRC. ◆

Reduce chemical usage and minimize excursion events Measurement made easy

The new TALYS ASP310 analyzer fulfills the needs of equipment suppliers to semiconductor, solar and LED Fabs. This low cost, high performance wet bath monitor allows real-time end-of-bath alerts and enables effective bath dosing. The TALYS can quickly measure multiple chemistries at the same sample point. The performance of this analyzer permits equipment operators and engineers to reduce chemical usage and minimize excursion events with real time bath component predictions. See us at Semicon West 2013 in booth #1210.

SemiconWest 2013 July 9-11 San Francisco, CA SEMICON® West 20/3 ABB Inc. Analytical Measurements Phone: +1 418-877-2944 1 800 858-3847 (North America) Email: ftir@ca.abb.com

Power and productivity for a better world<sup>™</sup>

## Bosch and STM tie for No. 1 MEMS supplier of 2012

For the first time ever, no clear winner has emerged to claim top honors in the MEMS business for 2012, with Bosch of Germany and French-Italian STMicroelectronics ending up evenly splitting the title of No. 1 supplier for the year, according to a MEMS Competitive Analysis Report from information and analytics provider IHS.

With both companies just shy of the \$800 million mark, Bosch and STMicroelectronics each had MEMS revenue of approximately \$793 million in 2012. The two companies do not use the same exchange rates every quarter when converting their revenue from euros to the U.S. dollar, and as a difference of less than 1 percent separates the revenue levels of both, IHS found it was not possible this time to declare a clear winner as to who was No. 1 for 2012.

"With billions of dollars up for grabs, competition in the MEMS market is intense," said Jérémie Bouchaud, director and senior principal analyst for MEMS & sensors at IHS. "Nowhere is the rivalry more furious than the battle for the market's top spot. In fact, the content for number one is so closely contested that Bosch and STMicroelectronics battled each other to a draw in 2012."

#### **MEMS** in the money

Overall, the top 20 MEMS manufacturers last year accounted for a whopping 77 percent of the industry total of some \$8.3 billion, as shown in Table 1. The figure excludes foundry revenue in order to avoid doublecounting of fabless and foundry takings within the same ranking. For instance, excluded is MEMS foundry revenue from STMicroelectronics for its fabrication of Hewlett-Packard inkjet print heads, or similar foundry revenue from Texas Instruments for Lexmark inkjet print heads.

Foremost among all the players were the four companies at the top, each with revenue ranging

#### Top 20 IDM and Fabless MEMS Suppliers Worldwide in Revenue (in Millions of US Dollars)

| Rank | Company                 | 2012  | 2011  |

|------|-------------------------|-------|-------|

| 1    | Bosch                   | 793   | 735   |

| 2    | STMicroelectronics      | 793   | 644   |

| 3    | Texas Instruments       | 751   | 776   |

| 4    | Hewlett-Packard         | 676   | 748   |

| 5    | Canon                   | 377   | 369   |

| 6    | Denso                   | 298   | 292   |

| 7    | Panasonic               | 296   | 308   |

| 8    | Knowles Electronics     | 292   | 272   |

| 9    | Analog Devices Inc      | 285   | 257   |

| 10   | Freescale Semiconductor | 255   | 245   |

| 11   | Epson                   | 223   | 246   |

| 12   | Sensata Technologies    | 200   | 190   |

| 13   | InvenSense              | 186   | 144   |

| 14   | Avago Technologies      | 167   | 193   |

| 15   | VTI                     | 163   | 135   |

| 16   | Infineon Technologies   | 156   | 139   |

| 17   | General Electric        | 141   | 132   |

| 18   | JDSU                    | 114   | 103   |

| 19   | FormFactor              | 109   | 115   |

| 20   | TriQuint Semiconductor  | 109   | 91    |

|      | Others                  | 1,957 | 1,828 |

|      | Total                   | 8,342 | 7,961 |

from \$675 million to \$800 million, and collectively well ahead of the rest of the pack.

#### **Bosch vs. STMicroelectronics**

Bosch, the No. 3 entity in 2011, enjoyed a MEMS revenue boost of 8 percent last year including a nearly 5 percent uptick in its primary automotive MEMS business, which accounted for 82 percent of overall Bosch MEMS takings. Bosch is unchallenged as the top automotive MEMS supplier with 27 percent share of the market. The company also has a growing consumer and mobile MEMS trade—up 17 percent for the year thanks to the soaring sales of pressure sensors in

handsets, compensating for slightly down revenues in accelerometers and microphones. But while the company did well in 2012, its result was impacted by an unfavorable exchange currency rate, especially in its U.S. automotive business.

STMicroelectronics, the No. 4 player in 2011, counted on a robust consumer and mobile business as its main source of MEMS revenue. While rival Bosch dominates automotive, STM leads in consumer and mobile MEMS with 32 percent of the market. STM also made inroads into automotive with \$15 million in 2012, up from \$10 million the year earlier. Gyroscopes were ahead of accelerometers in contributing to STM's cache, and similar to Bosch, pressure sensors for handsets boomed because of shipments into smartphones like the Samsung Galaxy S III.

## Texas Instruments tumbles from the top

Falling out of the No. 1 spot was Texas Instruments, down to No. 3, with revenue down 3 percent to \$751 million. While front projectors for business and education still formed the majority of its digital light processing (DLP) chip revenue, the segment was flat last year. In particular, DLP revenue in home theater and rear-projection TVs was down, especially with the exit of Mitsubishi as the last remaining rear-projection TV brand in North America. DLP revenue for picoprojectors also has not taken off as expected, with the chipset still too expensive and its adoption slow in the consumer and mobile markets. At the No. 4 spot was Hewlett-Packard with revenue of \$677 Continued on page 11

### Enjoy Infinite Possibilities.

Based on broad experience gathered over many years of developing, manufacturing and world-wide servicing field-proven electron-beam lithography systems, a team of highly-motivated employees, excellent researchers and creative engineers are constantly doing their best to fulfil our customers' requirements.

We understand E-Beam.

Vistec Electron Beam I www.vistec-semi.com

#### Globalfoundries Continued from page 6

12.1 and provides efficient access to the tool's productivity benefits for physical design with real-time, coloraware layout. Circuit designers can assign "same net" constraints in the schematic, and the layout designers can meet these requirements as they create the physical view.

The AMS flow provides detailed information on parasitic extraction and layout dependent effects, both of which introduce new challenges at 20nm and 14nm. For parasitic extraction, the flows are described in detail and customizable scripts and examples demonstrate OA and DSPF back annotation. In addition the flows illustrate methodologies to predict layout-dependent effects during schematic design and methods to include full models in post layout extraction. PEX flows for Synopsys StarRC extraction, Cadence QRC and Mentor CalibrexRC are supported.

## Sign-off ready RTL2GDSII flows that address double patterning

GLOBALFOUNDRIES is also making available new flows that support a complete RTL-to-GDSII design methodology for targeting its 20nm and 14nm manufacturing processes. The company worked with EDA vendors to certify the flows in their respective environments and provide a platform for optimized, technology-aware methodologies that take full advantage of the performance, power and area benefits of the processes.

The result is a set of fully executable flows containing all the scripts and template files required to develop an efficient methodology. The flows serve as a reference to validate the correctness of the accompanying PDK as well as the vendor tool setup. In addition the flows offer access to other critical and useful information, such as methodology tutorial papers; guidelines and methodologies for decomposition of double patterned layouts; PEX/STA methodology recommendations and scripts; and design guidelines and margin recommendations.

A critical aspect of manufacturing at this level is the use of double patterning, an increasingly necessary technique in the lithographic process at advanced nodes. Double patterning extends the ability to use current optical lithography systems and the GLOBALFOUNDRIES flows provide comprehensive double pattern design guidelines. They address design for double patterning and the added flow steps for different design styles and scenarios.

Synopsys and GLOBALFOUNDRIES worked together to minimize the impact of changes associated with the 3D nature of finFET devices as compared to planar transistors. The two companies focused on making finFET adoption transparent to the design team. The collaboration on Synopsys' RTL to GDSII flow includes 3-D parasitic extraction with the Synopsys StarRC tool, SPICE modeling with the Synopsys HSPICE product, routing rules development with the Synopsys IC Compiler tool and static timing analysis with the Synopsys PrimeTime tool.

Cadence contributed a complete RTL-GDSII flow, including physical synthesis, and planning and routing developed with the Encounter Digital Implementation (EDI) System foundation flow. The seamless implementation flow, using Cadence Encounter RTL Compiler and EDI System, supports double patterning and advanced 20 and 14nm routing rules.

Mentor's Olympus-SoC place and route system is supported in the flow, providing support for new DRC, double patterning, and DFM rules. The Olympus-SoC router has its own native coloring engine along with verification and conflict resolution engines that detect and automatically fix double patterning violations. Expanded features include DP-aware pattern matching, coloring aware pin access, pre-coloring of critical nets, and DP aware placement. The Calibre InRoute product allows Olympus-SoC customers to natively invoke Calibre signoff engines during design for efficient and faster manufacturing closure.

Double patterning also impacts LVS and other DRC issues, and the flows provide methodology details to address these areas, including hierarchical decomposition to reduce data base explosion. Parasitic extraction methodologies and scripts are provided as well, offering ways to address double patterning-induced variations via DPT corners or with maskshift PEX features.

#### MEMS Supplier Continued from page 9

million. HP also suffered a drop in ranking, down from No. 2 in 2011, as revenue associated with its inkjet printer heads contracted 10 percent last year. This follows a 15 percent decline in the shipment of inkjet printers. Moreover, HP's revenue from the replacement of disposable print heads has been shrinking continually as the company long ago started to move to printers with permanent print heads.

Rounding out the Top 5 but at a relatively far remove from the four other companies above it was Canon of Japan, with revenue of \$377 million.

#### InvenSense on the rise

In all, revenue for companies from the succeeding sixth spot all the way to No. 15 each had takings between \$100 million to just under \$300 million. Worth noting outside of the Top 5 was Californiabased InvenSense at No. 13, with revenue up 30 percent to \$186 million. InvenSense is the most successful MEMS startup ever, its market breakthrough coming in 2009 thanks to its design in the Nintendo Wii Motion Plus gaming accessory. While InvenSense initially had been heavily dependent on gaming, the company wisely diversified its business and now looks to handsets and tablets as even more important sources of revenue.

InvenSense has also pioneered serial production of 6-axis inertial measurement unit comprising accelerometers and gyroscopes in a 4 x 4-millimeter package. Combo sensors last year accounted for half of the company's revenue, and InvenSense is now producing a very small 9-axis inertial measurement unit also containing a 3-axis magnetometer that measures only 3 x 3 millimeters. ◆

Worldwide Leader in Vacuum Valve Technology

## NEW CATALOG AVAILABLE NOW

with many new products

Request your copy today and have a look at our wide range of vacuum valves

Visit us at Semicon - Booth #919

## www.vatvalve.com

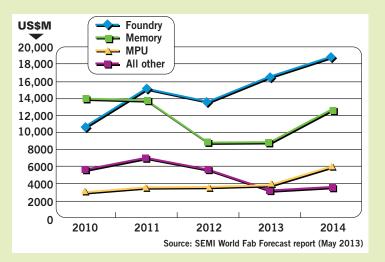

## Fab equipment spending: 23% growth in 2014

Fab equipment spending will grow two percent year-over-year (US\$ 32.5 billion) for 2013 and about 23 to 27 percent in 2014 (\$41 billion), according to the May edition of the SEMI World Fab Forecast. Fab construction spending, which can be a strong indicator for future equipment spending, is expected to grow 6.5 percent (\$6.6 billion) in 2013, followed by a decline of 18 percent (\$5.4 billion) in 2014. The new World Fab Forecast report covers fab information on over 1,140 facilities, including such details as capacities, technology nodes, product types, and spending for construction and equipment for any cleanroom wafer facility by quarter.

Fab equipment spending for the second half of 2013 is expected to be much stronger with a 32 percent growth rate or \$18.5 billion compared to the first half of 2013. The equipment spending increase in the second half is attributed to growing semiconductor demand and improving average selling price for chips. 2014 is expected to have about 23 to 27 percent growth year-over-year (YoY) to reach about \$41 billion, which would be an all-time record.

Looking at product types, the largest amounts of spending on fab equipment in 2013 will come from the foundry sector, which increases by about 21 percent. This is driven mainly by capex increases by TSMC. The memory sector is expected to have an increase of only one percent — after a 35 percent decline in the previous year. The MPU sector is expected to grow by about five percent. A double-digit increase in the Analog sector in 2013 will still translate into low absolute dollar amounts, compared to the other sectors.

Construction spending is a good indicator for more equipment spending. Fab construction spending in 2013 is expected to be almost 15 percent growth YoY (\$6.6 billion) with 38 known construction

projects. Top spenders for fab construction in 2013 are TSMC and Samsung, who plan to spend between \$1.5 and \$2 billion each, followed by Intel, GLOBALFOUNDRIES and UMC. The SEMI World Fab Forecast report reveals more detail.

2014 shows a decline of about 18 percent (\$5.4 billion) in construction spending with only 21 construction projects expected to be on-going. These construction projects include large fabs; some are 450mm-ready.

Since the last fab database publication at the end February 2013 SEMI's worldwide dedicated analysis team has made 389 updates to 324 facilities (including Opto/LED fabs) in the database. The latest edition of the World Fab Forecast lists 1,144 facilities (including 310 Opto/LED facilities), with 61 facilities with various probabilities starting production this year and in the near future. Seventeen new facilities were added and 8 facilities were closed.

The SEMI World Fab Forecast uses a bottomup approach methodology, providing high-level summaries and graphs; and in-depth analyses of capital expenditures, capacities, technology and products by fab. Additionally, the database provides forecasts for the next 18 months by quarter. ◆

## Inside ASET's Dream Chip

The International Symposium on Electronic Packaging was held in Osaka the week of April 10th with keynote speakers, Dr. Subramanian S. Iyer of IBM, Dr. Takeshi Uenoyama of Panasonic, and Dr. Urmi Ray of Qualcomm.

There were 180 papers and over 20 posters. In addition, the Japan ASET consortium, Taiwan and Korea held special sessions.

The ASET "Dream Chip" program recently ended in Japan. In the ASET special session, Sueoka and co-workers described their proposal for "High Precision Bonding for Fine Pitch Interconnection." Bonding fine pitch interconnect requires consideration of the factors which degrade the alignment accuracy such as thermal expansion of the machinery, and surface topologies of the chip an substrate.

They were able to bond  $10\mu m$  pitch bumps. Using a flip chip bonder equipped with infrared alignment optics they found that they could observe alignment marks and adjust the chip position during the bonding process, even when the solder was molten. Most importantly they could eliminate the mis-alignment caused by joining non flat chips and due to thermal expansion of the tool head.

This dynamic alignment bonding scheme consists of 4 steps:

• pre-align for the approach of the chip to the substrate

- small gap align with IR light

- correct alignment for offsets caused by impact of the chip touching the substrate

- final align during the bonding while the solder is molten.

## Packaging

Renesas and IBM Japan described "3D Package Assembly Development with the use

of Dicing Tape Having NCF Layer". Dicing and stacking are important technologies in 3DIC assembly. Bumps on the wafer backside make it difficult for general dicing tape to achieve both high quality dicing and pickup. For tight pitch, small

bump bonding it is also difficult to inject underfill into the narrow gap between the dies.

General dicing tape cannot bury the bumps and thus fully fix the die. This causes chipping and cracking of the die during dicing. If you increase the tapes thickness to fully bury the bumps, die pickup becomes difficult.

ASET studied a new ICF tape from Nitto Denko. The tape has a NCF layer (non-conductive film) on the dicing tape. Since this NCF layer ends up staying in the gap as underfill, they call this Inner chip film or ICF (just what we need more acronyms!) Hot lamination of the tape to the wafer will bury the backside bump. Wafer and NCF layer are diced together. The die pick up becomes easy since the required separation is between the ICF and the dicing tape adhesive.

Hozawa and ASET co-workers at ASET described their "3D Integration Technology using Hybrid Wafer Bonding and its Electrical Characteristics". In this study ASET examined 3D integration with vias last. Vias last was examined because it needs no modification of the front end process.

The process flow consists of: TSV formation; bump/ contact ad formation; substrate thinning and stacking. They also examined W2W bonding and thinning after bonding as process flows.

Hybrid bonding was chosen where Cu-Cu and polymer – polymer bonding (they used PBO) occur at the same interface. Hybrid bonding provides both strong metal bonding and reliable polymer underfilling simultaneously.

In the full process sequence a silicon interposer wafer and the first device wafer are bonded F2F with hybrid bonding. After backside thinning the first device wafer, TSV formation and backside bumping the second device wafer is bonded to the stack B2F. Lastly the silicon interposer is thinned, TSV formed and bumps attached. ◆

## **MEMS:** After the prototype

After a functional A-sample prototype is built, it doesn't take long for a project to gain traction that has market pull.

This is usually the point that a project becomes highly visible within a company and it enters the Technology Development Process (TDP). The TDP is made up of multiple phases including concept, prototype, pilot and production with gates at the end of each phase. Design and process reviews are required at each gate but may also occur within a phase. These reviews are an open forum for communication of project progress and gaps towards technological, business and schedule milestones. Furthermore, the product is constantly evaluated against the market need and potential changes in market that may have occurred. The audience for the reviews at a gate include peers and management, who provide feedback on the project to date and collectively decide whether additional work is needed to complete the current phase or the completed work is sufficient to allow the project to proceed to the next phase with additional funding. In certain instances, a project that has not met all of the deliverables may be allowed to proceed to the next phase, but under strict conditions, that must be fulfilled within a given timeline. The goal of the TDP is to focus the team on high quality execution, effectively screen projects allowing only the best to proceed and hence accelerate successful innovation and profitability.

The MEMS Industry Group (MIG) Technology Development Process Template is an excellent tool for companies to use to implement **MEMS** the TDP within their organization (Marty et al. 2013). The goal of the TDP was to

create a simplified frame work that could be easily customized to fit a company's needs. The TDP structure shown below is a slightly modified version of the TDP developed by MIG. In this version there are four major phases including concept, prototype, pilot and production with three major gates.

contributing editor

The concept phase is where ideas are generated and the initial A-samples are developed. It is also where the business case is first generated and the market need is defined. It is highly desirable to have market pull at this point. The prototype phase is where the design is developed in detail and B-samples are fabricated to support various levels of validation. The outcome of the prototype phase is to have design that can be manufactured in volume production. Towards the end of the prototype phase, production tooling is often released. The pilot phase is where production tooling is built and qualified. In addition, the product is made on production tooling (C-samples) and revalidated. It is important to note that there should be no change in the product design between the last revision in prototype and the first samples off the production tooling. The production phase is low to high volume production ramp. Often customers will require revalidation of products in production once a year for the life of the product.

At each gate, there is a design and process review for the project. In order for the team to be focused and efficient, there needs to be a clear set of deliverables defined for completion of each phase. These deliverables range from business and market definition to project technical details to production launch. This checklist provides an in-depth set of deliverables for the design reviews at each gate that can be tailored to the specific needs of an organization.

The Technology Development Process is an essential element of successful MEMS new product launches. The Design Review Checklist can also provide a frame work for discussion between management and engineers. With improved communication and efficient execution of technology development, the TDP is a great tool for accelerating innovation and profitable MEMS products. <a>

# FD-SOI targets mobile applications

GIORGIO CESANA, STMicroelectronics, Crolles, France and CARLOS MAZURE, Soitec, Bernin, France

The FD-SOI technology platform is perfectly suited for mobile IC applications where power consumption has to be very low to maximize battery lifetime.

he IC industry has been innovative with the introduction of new materials and process modules like stressors, high-k and metal gates (HKMG). It has been very conservative in keeping the bulk planar transistor structure. As a result, the planar transistor has become a highly doped device with decreasing dimensions. Moreover, at these smaller dimensions, transistor characteristics suffer from statistical fluctuations like random dopant fluctuations (RDF) in the channel, which impair device matching in sub-100nm circuits. This has become an important problem beyond node 28/32nm limiting VDD reduction, thus limiting the reduction of both dynamic and standby power consumption.

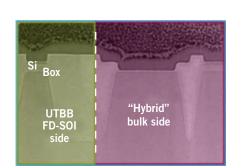

There is strong consensus in the IC community that fully depleted (FD) transistors, also known as Ultra Thin Body (UTB) devices, are an effective solution for reducing the  $V_T$  variability caused by random dopant fluctuation (RDF). FD devices can be vertical, (FinFETs, 3D MOSFET) [1], or planar (FD-SOI) [2, 3]. Their key characteristic is that the silicon channel is undoped (**FIGURE 1**).

FD-SOI is an evolutionary innovation because it has the advantage of being a planar transistor structure that extends the applicability of bulk design flows with existing design and EDA tools. It is a non-disruptive MOSFET architecture change for SOC design and processing. FD-SOI requires ultra-thin Si (<20nm) over an ultra-thin buried oxide (BOX<25nm) for improved electrostatics [3]. FD technology brings numerous benefits for power reduction, area scaling and performance improvement while enabling a lower V<sub>DD</sub> [3]. The IC SOC community has accepted that

**FIGURE 1.** Examples of fully depleted devices: a) planar FD-SOI or ultra thin body UTB (TEM courtesy of IBM); b) 3D device FinFET (TEM courtesy of IMEC).

technology nodes beyond 20nm will have to use fully depleted (FD) MOSFETs.

Pushing performance, Intel introduced the 3D transistors, FinFET, first in 2011 for CPU applications [1]. The foundry world, in contrast, was able to scale conventional bulk CMOS technology from to 28nm to 20nm. The gain in density came with a higher price per unit area and little performance gain, however. Indeed, beyond the 28nm node, CMOS technology has become more complex with double patterning (node 20nm) and with 3D FinFET devices (node 14/16nm). The performance gain from node to node is well below the 30% boost we have

**GIORGIO CESANA** is director of technology marketing at STMicroelectronics, Crolles, France and **CARLOS MAZURE** is chief technology officer at Soitec, 38190 Bernin, France.

SOI

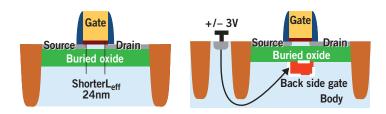

**FIGURE 2.** Schematic representation of the 28nm FD-SOI transistor. a) Cross-section of the FD-SOI MOSFET with the thin-layer channel on buried oxide; b) well contact used to apply back bias through the back gate underneath the buried oxide.

seen historically with scaling from a nodes n to the following n+1.

In this landscape, 28nm FD-SOI [4, 5] offers a very attractive value proposition: best low power at HKMG performance. In fact, 28nm FD-SOI gives the performance boost of scaling without changing the node. This is very interesting option for low-power ICs where area is not the driving factor and which

DR CALL US TODAY AT 775-883-1336

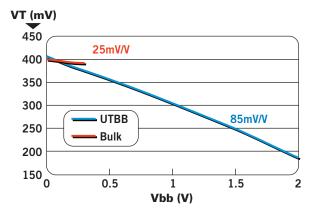

**FIGURE 3A.** VT variation as a function of applied back bias [4].

could profit from a performance boost at constant or lower power consumption. Thus for many IC products moving to FD-SOI without changing the node can be very attractive from a power, performance and cost point of view. Only density-driven ICs need to rush to the next node. The offering of 28nm FD-SOI by foundries [6] will, without doubt, be interesting for numerous fabless companies having products in 28nm that could take advantage of a higher performance second generation 28nm technology without sacrificing low-power operation. Furthermore, low-power HKMG 28nm FD-SOI will also be very attractive 40nm IC products moving to 28nm.

#### **FD-SOI technology**

For bulk MOSFETs, the channel VT is tuned through channel and Halo doping, which is where RDF originates. In contrast, the FD-SOI channel is undoped,

**FIGURE 3B.** Forward and Reverse Body Bias effectiveness for speed improvement and power saving.

significantly decreasing or eliminating RDF. The FD transistor VT is tuned through the gate work function and the back-bias voltage. Because of better electrostatics, FD-SOI transistors exhibit lower parasitics, which improves the transistor driving behavior. This is particularly advantageous at low VDD supplies. The better electrostatics also improve the short-channel

effect as compared to the bulk 28nm version. This in turn enables a CMOS technology with shorter gate lengths (Lg=24nm), relaxing the integration constraints on the source and drain contact module.

FD-SOI in the ultra-thin body and buried oxide (UTBB) configuration [2, 3] offers the additional benefit of modulating the FD transistor characteristics by applying a back bias (FIGURE **3a**). The FD-SOI transistor is, in principle, controlled by two gates: the actual transistor gate and the back plane, which acts as a second independent gate. Forward (FBB) and reverse back bias (RBB) circuit techniques have been used by many designers in earlier technology nodes but the range of biases were limited, on the one hand, by the source/drain to well diode forward-biasing, and, on the other hand, by the diminishing back biasing modulation of the bulktransistor threshold voltages (VT) due to increasing channel doping levels. UTBB enables an extended back-biasing range of several VDD (-3V<VBB<+3V) and is a very powerful design tool for power management as well as for performance boosting, as illustrated in FIGURE 3b. Moreover, FD-SOI technology allows for dynamically adjusted threshold voltages.

Body bias requires a limited area overhead (2-3%), and can be

restricted only to the IPs (i.e. CPU/GPU cores) that would benefit most from it to reduce the implementation effort and area overhead.

The 28nm FD-SOI process flow is a modified bulk 28nm HKMG LP process. It uses the same back end of the line andsame gate module. It is a simple incremental porting from bulk 28nm. Manufacturing even uses the

## **POWER SOLUTIONS FOR** SEMICONDUCTOR DESIGN, MANUFACTURE AND TEST

**TDI** POWER

www.tdipower.com | 908.850.5088

same tool set. Several process steps, specifically channel implants, halo implants and masking levels, are removed compared to the traditional 28nm bulk technology because of the undoped FD-SOI channel. There is less than a 20% change to the typical CMOS bulk flow [4, 6].

The extremely thin body and buried oxide layers makes it possible to etch them and

to co-integrate SOI and bulk devices on the same SoC (**FIGURE 5a**). The ESD and I/O structures are kept in bulk for simplicity (**FIGURE 4b**). This is the hybrid integration with diodes and bipolars in bulk [2, 3, 4].

#### **FD-SOI Substrates**

FD-SOI technology builds on an SOI substrate with ultra-thin top Si (<12nm) and ultra-thin buried oxide (25nm) and with the utmost thin-layer uniformity of  $6\sigma = \pm 0.5$ nm, all sites and all wafers [8].

**Ultra-thin Silicon:** The starting ultra-thin Si thickness has to be matched to the subsequent FD CMOS processing. Cleaning and sacrificial oxidations remove a few Si monolayers and this has to be considered when specifying the initial SOI thickness. The targeted Si channel thickness is typically between 5nm – 7nm [3, 7]. The SOI thickness (T<sub>Si</sub>) has a direct effect on the MOSFET characteristics [5]. To take advantage of the improved electrostatic behavior of

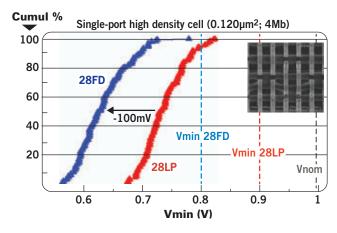

FIGURE 5. Comparison of 6T SRAMs for 28LP bulk vs. 28nm FD-SOI.

FIGURE 4A. SOI/bulk co-integration.

| Device type           | UTBB FD-SOI  | Bulk              |

|-----------------------|--------------|-------------------|

| Logic                 | 2Vt/PBO-16nm |                   |

| SRAM                  | $\checkmark$ |                   |

| Capacitance, Varactor | $\checkmark$ |                   |

| Drift MOS (OTP)       |              | $\checkmark$      |

| Digital I/O           | $\checkmark$ |                   |

| Analog MOS            | $\checkmark$ |                   |

| RF MOS                | $\checkmark$ |                   |

| Resistors             | √ (Poly)     | √ (Active)        |

| Diodes (antenna)      |              | ✓.                |

| ESD devices           | ✔ (FET)      | (FET, diode, SCR) |

| Vertical bipolar      |              | $\checkmark$      |

**FIGURE 4B.** Device partitioning of 28nm FD-SOI technology.

FD-SOI, the rule of thumb is  $L_G = 1/3 T_{Si}$  (5) in the channel region.

Thickness uniformity is the key parameter to control the  $V_T$  variation and short-channel effects (SCE) of the planar FD-SOI device. Typical uniformity requirements include on-wafer uniformity and wafer-to-wafer uniformity. Both of them combined are classified as layer total thickness variation (LTTV) and define the overall manufacturing process window for thickness uniformity. LTTV has to be achieved at the nanometer or sub-nanometer range for the SOI layer for all wafers and all sites in order to meet the FD specifications.

From circuit and device considerations, the maximum TSI fluctuation that can be tolerated is  $\pm$ 5Å within-wafer (WiW), total wafer range of the T<sub>Si</sub> non uniformity, and wafer-to-wafer (WtW) T<sub>Si</sub> reproducibility.

**Ultra-thin BOX:** The thin BOX (Buried Oxide) suppresses the lateral electrostatic coupling between source, drain and channel of the transistor through the thick BOX. Furthermore, the BOX thickness reduction improves the scalability of the FD-SOI device at almost constant channel silicon thickness down to  $L_{G}$ =10nm, which corresponds to the targeted gate length for the 10nm node. An ultra-thin BOX (UTBOX) enables the use of a back bias and a forward bias to adjust the transistor characteristics like current drive (Ion), off leakage (Ioff) and  $V_{T}$  within an extended VBB voltage range [9].

The BOX thickness  $T_{BOX}$  and silicon thickness  $T_{Si}$  are independent parameters for the SOI fabrication and can therefore be adjusted without degrading the properties of the top silicon layer. The oxide quality of ultra-thin BOX is very similar to the quality of equivalent gate oxides.

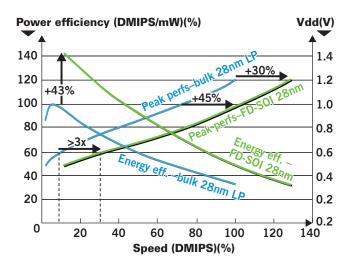

**FIGURE 6.** Best in class in core efficiency for 28nm FD-SOI vs. 28LP bulk.

#### **FD-SOI Design**

We use standard commercial EDA flow to design both bulk and FD-SOI. Design migration from Bulk to FD-SOI EDA flow is straightforward. The interconnects and routing are identical. FD-SOI devices behave very much like bulk transistors because there is no history effect and no floating-body effect, if T<sub>Si</sub> is sufficiently thin (<10nm). Logic and memory design and architecture are also similar to bulk.

The differences between FD-SOI and bulk are related to process and devices, and include, SPICE models, integration of ESD and analog devices, and application of back-bias schemes.

FD-SOI standard and custom cells can be duplicated or ported from existing bulk cells. Re-characterization is required due to a different SPICE model: Input capacitance, timing, leakage and dynamic power data in library files will change. Timing analysis needs to be rerun to check that there are no setup/ hold violations in case of direct porting. Porting bulk designs to FD-SOI is as simple as porting to an updated bulk design [10, 11, 13, 14].

The device models are validated on FD-SOI hardware and available with EDA tools. Compact device models [11, 12] are production ready.

#### **Circuit Results**

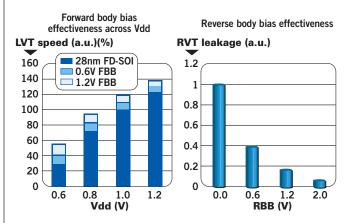

**SRAM Robustness:** The lowest  $AV_T$  values are achieved with FD-SOI [3, 9] due to the undoped channel and consequently the strong RDF reduction. Thus,

lower  $V_{DD}$  operation is enabled for minimum SRAM cell size as compared to its bulk equivalent. The FD-SOI cell has a better read stability and write ability with respect to the bulk cell. The typical bulk countermeasures of increasing  $V_{DD}$ , or increasing the channel length and width to compensate for the  $V_T$  variability are no longer necessary. At the same cell size, FD-SOI makes it possible to gain 100mV to 200mV in Vmin compared to the bulk cell [4]. The operation regime at  $V_{DD}$ <0.8V is very attractive for mobile hand-held applications.

**Circuit Performance:** FD-SOI technology is particularly suited for high speed at low-voltage operation, reducing signifantly the power consumption  $(-V_{DD}^{2})$ . **FIGURE 6** illustrates two potential optimization paths: significantly more performance at the same power or a dramatic reduction of power consumption at the same performance.

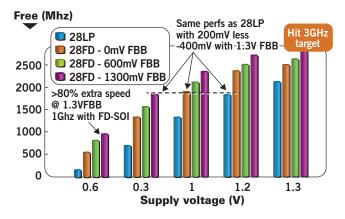

**FIGURE 7** shows the advantages of FD-SOI for different VDD voltages. At 0.6V, FD-SOI is already capable of delivering 550MHz, >3x the performance

3522 ARROWHEAD DRIVE CARSON CITY NV. 89706 of an equivalent 28LP technology implementation, without requiring any Forward Body Bias (FBB). Using Forward Body Bias, it is possible to reach 1GHz operation with a 0.6V source.

SOI

FD-SOI can also deliver the same performance as bulk while running at a lower operating voltage. As highlighted in Fig. 7, we have achieved the same performance in 28nm FD-SOI as 28LP while running with 200mV lower supply, and an even further saving of 200mV is possible when applying Forward Body Bias. This impressive reduction of 400mV on the supply voltage immediately translates into huge dynamic power savings.

**FIGURE 7.** FD-SOI enables high speed at lower VDD. Example of ARM A9 core. Si data.

In overdrive conditions, by boosting performance with FBB, we have demonstrated 3GHz operation [13], overtaking what has been obtained to date with the A9 architecture.

#### Conclusion

The FD-SOI technology targets fast performance at low voltage  $V_{DD}$  and is an ideal technology to reduce the energy gap between battery energy supply and smart handheld system energy needs, so it runs cool. The industrial ecosystem is in place for the substrate supply, technology platform and design infrastructure. The FD-SOI technology platform is perfectly suited for mobile IC applications where the power consumption has to be very low to maximize battery lifetime. Furthermore, with its simplicity, FD-SOI is an evolutionary step from bulk towards

fully depleted design because it maintains the planar device structure.  $\blacklozenge$

#### References

- C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarme, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L.Pipes, I. Post, S. Pradhan, M.Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sanford, J. Seiple, P. Smith, C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki, K. Mistry, "A 22nm High Performance and Low Power CMOS Technology Featuring Fully-Depleted Tri-Gate Transistors, self-Aligned Contacts and High Density MIM Capacitors", VLSI Symp. Tech. (2012).

- N. Planes, O. Weber, V. Barral, S. Haendler, D. Noblet, D. Croain, M. Bocat, PO Sassoulas, X. Federspiel, A. Cros, A. Bajolet, E. Richard, B. Dumont, P. Perreau, D. Petit, D. Golansli, C. Fenouillet-Beranger, N. Guillot, M. Rafik, V. Huard, S. Puget, X. Montagner, MA Jaud, O. Rozeau, O. Saxod, F. Wacquant, F. Monsieur, D. Barge, L. Pinzelli, M. Mellier, F. Boeuf, F. Arnaud and M. Haond, "28nm FD-SOI Technology Platform for High-Speed Low-Voltage Digital Applications", VLSI Symp. Tech. (2012).

- 3. T. Skotnicki; IEDM Short Course "Low Power Logic and Mixed Signal Technology", IEDM 2009.

- J. Hartmann, STMicroelectronics, "Planar FD-SOI technology at 28nm and below for extremely power efficient SOCs", 13 Dec 2012, San Francisco, California, USA. www.soiconsortium.com

- 5. T. Skotnicki, Proc. of ESSDERC 2000, pp. 19-33.

- S. Kengari, GlobalFoundries, "SoC Differentiation using FD-SOI A Manufacturing Partner's Perspective FD-SOI Workshop", 22 April 2013, Hsinchu, Taiwan. www.soiconsortium.com

- 7. K. Cheng, et al; "ETSOI CMOS with Record Low Variability for Low Power System-on-Chip Applications", IEDM 2009, session 3.2.

- 8. FD-SOI substrate Soitec data sheet.

- 9. F. Andrieu, et al; "Low Leakage and Low Variability Ultra-Thin Body and Buried Oxide (UT2B) SOI Technology for 20nm Low Power CMOS and Beyond", VLSI 2010, session 6.1.

- 10.J.L. Pelloie and B. Hold, "FD-SOI Design Portability from BULK at 20nm Node", Fully Depleted Workshop, San Francisco, Feb. 24, 2012. www. soiconsortium.com

- 11.G. Cesana, "20nm and 28nm FD-SOI Technology Platforms", Fully Depleted Workshop, San Francisco, Feb. 24, 2012. www. soiconsortium.com

- 12.C. Hu, A. Niknejad, Sriramkumar V., Darsen Lu, Yogesh Chauhan, Muhammed Karim, Angada Sachid, "BSIM-IMG: A Turnkey Compact Model for Back-gated FD-SOI MOSFETs", Fully Depleted Workshop, Hsinchu, Taiwan, April 28, 2011. www.soiconsortium.com

- 13. L. Le Pailleur, Proc. of VLSI-TSA 2013.

- 14.L. Le Pailleur, "Seamless design migration to 28nm FD-SOI", 22 April 2013, Hsinchu, Taiwan.

METROLOGY

# Effects of measured spectral range on accuracy and repeatability of OCD analysis

#### FRANZ HEIDER, Infineon Technologies, Villach, Austria; JEFF ROBERTS, JENNIE HUANG, JOHN LAM and RAHIM FOROUHI, n&k Technology, San Jose, CA

A broadband polarized reflectometry measurement, utilizing RCWA analysis, can be used to obtain detailed trench profile results.

here is a need for metrology to help control manufacturing processes for power semiconductors, where deviations from the desired structure geometry can affect device performance. Lithography and etch processes, specifi-

cally, create patterned structures, where the trench depth and width, or CD (critical dimension), must be tightly controlled. Traditionally, several techniques have been employed for this purpose, including cross-section Scanning Electron Microscopy (SEM), CD-SEM, profilometry, and Atomic Force Microscopy (AFM). Each method has its benefits and limitations, but none can provide detailed profile information with the combination of speed and measurement sensitivity of non-destructive optical metrology, based on broadband polarized reflectometry.

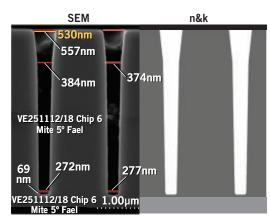

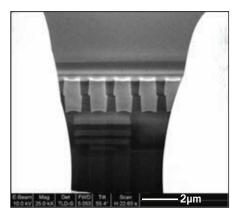

**FIGURE 1:** Cross-section SEM image of the tapered trench (left) and model of the trench structure within n&k analysis software (right). The model was created to be consistent with the trench profile seen in SEM images.

To demonstrate the capabilities of broadband polarized reflectometry, we performed measurements

on power semiconductor samples using an optical metrology instrument, the n&k Olympian. One key aspect of this system is the relatively large wavelength range, extending from deep ultraviolet to near infrared wavelengths (190nm - 1000nm). This large range

> enables applications that would not be possible with the limited range of standard reflectometers (375nm - 750nm).

#### **Measurement system**

The n&k Olympian is a fullyautomated metrology system for thin film and optical critical dimension (OCD or "scatterometry") measurements that uses broadband polarized reflectance. The data extends from the UV to NIR, with a separate optical system covering IR wavelengths up to 15,000nm. The measurement method is non-contact, non-destructive

and high throughput, with typical measurement times (including the move, acquire, measure, and analyze steps) on the order of 5s per measurement point.

**FRANZ HEIDER**, Infineon Technologies, Villach, Austria; **JEFF ROBERTS**, **JENNIE HUANG**, **JOHN LAM** and **RAHIM FOROUHI**, n&k Technology, San Jose, CA.

For the UV-NIR wavelength range, there are two light sources. UV light comes from a deuterium arc lamp, while visible and near-IR radiation is provided by a tungsten filament lamp. The source light is focused on the sample and directed to a spectrophotometer by a series of mirrors, creating a measurement spot diameter of 50µm and incident angle of 4° from normal. The spectrophotometer contains a holographic diffraction grating and a photodiode array that separates the polychromatic beam into its individual wavelength components and records the reflectance at each wavelength, in one nanometer intervals. There is a rotating polarizer in the optical path enabling the collection of two sets of measurement data (S-polarized Reflectance and P-polarized Reflectance, or "Rs" and "Rp" respectively). When line/space grating structures are measured, the structures are oriented such that Rs data relates to the TE polarization and Rp data relates to the TM polarization.

To extract values for structure dimensions, a model of the measured area is created using n&k Analysis software. The software incorporates rigorously coupled wave analysis (RCWA) for periodic structures1 with Forouhi-Bloomer dispersion relations2, 3 for n and k. The model is used to calculate theoretical reflectance spectra. The structure dimension parameters, within the model, are varied using nonlinear regression analysis in order to obtain the best match between the experimental and calculated spectra. Inputs to an OCD structure model include the optical properties for all materials within the structure, which can be determined by measuring blanket film areas, and the structure pitch.

The measurement results are determined by converging on the maximum goodness of fit (GOF) value, which describes the similarity of the calculated reflectance of a modeled profile to the experimental reflectance. The variables within the model, including CD and depth, are reported as measurement results after the software determines that the GOF cannot be further improved by changing any of the values. A higher goodness of fit value generally means that the measurement results are consistent with the physical dimensions of the actual structure. If there is variation in neighboring features within the  $50\mu$ m diameter measurement area, the results are considered to be the average dimensions. To provide measurement results with this tool and technique, the area of interest must meet certain requirements. Typically, the measurement area is either the device structures, or within designed test areas meant to approximate the features found within the actual device. OCD test structures, including 2D line/ space gratings or 3D hole arrays, must be repeated periodically, with a pitch less than 10µm.

#### **Tapered trench measurement**

To test the measurement capabilities of the n&k Olympian, Infineon Technologies created five silicon wafer test samples with line/space grating structures. Each sample was created using different process conditions, meant to represent possible unintended changes in the manufacturing process that could lead to differences in the dimensions of the grating structures, ultimately affecting the device performance. The samples were measured using both the n&k system and a cross section SEM, for comparison and determination of the approximate trench profile.

As shown in **FIGURE 1**, the tapered line/space grating structures have repeating spaces etched into silicon with a pitch of  $1.7\mu m$ , nominal trench depth of  $4\mu m$ , and space CD of  $0.55\mu m$ . The pitch is based on the design layout and will not be affected by changes in the etch processing, so pitch is fixed within the analysis model. Trench depth and space CD are the parameters of interest that need to be measured. There were no materials besides silicon in the test

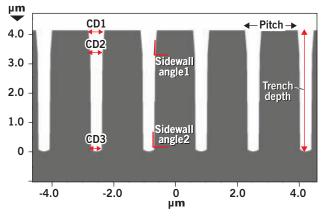

**FIGURE 2:** Cross-section view of the OCD model, drawn to scale. Pitch is fixed within the model, while CD1, CD2, CD3, and trench depth are measurement parameters. Sidewall angle values can be calculated from the results for CD and depth.

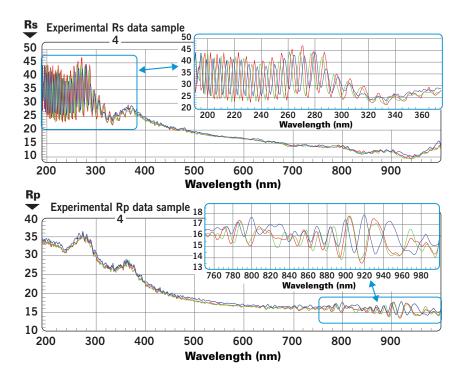

**FIGURE 3:** Experimental Rs and Rp Data for Sample 4, at 3 locations across the wafer. The data shows the areas of the spectra that are critical in distinguishing changes in trench depth and CD. The three locations appear to have differences in terms of experimental data, which relate to trench depth and CD, particularly from 190-350nm in Rs data and 800-1000nm in Rp data. A standard reflectometer with wavelength range of 375-750nm does not include data in the critical regions where there is good sensitivity to the trench depth and CD values, so measurement results using this limited wavelength range will be unreliable for Sample 4.

structures, but oxides, nitrides, and poly-silicon are often a part of OCD structures, and the analysis software allows for the inclusion of multiple layers on the trench mesa (above silicon lines), at the bottom of the trench, or on the trench sidewall.

A review of the cross-section SEM image for the grating structure (Fig. 1) shows the trench profile for one of the samples with two distinct sections. From the top of the trench until a depth of ~800nm there was a fairly constant sidewall angle, while from the depth of ~800nm to the bottom the trench sidewall angle changes to be closer to normal. Subsequent SEM images show that this inflection point is consistently near a depth of 800nm from the top of the trench. These observations of the trench profile were used to develop the analysis model for the n&k Olympian. Neither an AFM nor a CD-SEM would be able to measure CD at the inflection point as well as at the top and bottom of the trench.

Based on the trench profile from cross-section SEM images, the analysis model was created to include space CD variables at three

#### The Power of Thermodynamics™

**Liquid Temperature Control**

(800) 458-5226 info@julabo.com

www.julabo.com

METROLOGY

points (**FIGURE 2**): CD1 at the top, CD2 at 800nm from the top, and CD3 at 70nm from the trench bottom (to allow for some rounding at the trench bottom). There is good match between the SEM image and the schematic from the analysis software.

Each wafer was measured at 29 points using the n&k Olympian, while cross-section SEM images were taken at the center point for each sample. For the optical measurements, we considered two cases: 1) using the full wavelength range of the broadband polarized reflectometer (190nm - 1000nm), and 2) using a limited range typical of standard reflectometers (375nm - 750nm). This comparison was done to demonstrate the advantages of using a larger wavelength range, for this application. Other than the wavelength range, the modeling was identical for both cases.

#### **Experimental Data**

Without any data analysis, observations of the experimental data, Rs and Rp, can provide insight into the measurement sensitivity to the structure depth and CD values. Looking

at the experimental data, we clearly see oscillations in the Rs data from 190nm - 450nm, and in the Rp data from 800-1000nm. For Sample 4, the oscillations in the Rs data have a limited wavelength range and only extend from 190nm – 350nm, as shown in **FIGURE 3**.

To further test measurement sensitivity, we can create an analysis model using the nominal structural dimensions. We calculate the theoretical polarized reflectance for the nominal structure and compare this to the experimental data. By changing the parameter values for depth and CD within the model and recalculating the theoretical reflectance, we can observe the effects of changing depth or CD on the reflectance spectra. Overall, the simulations confirm that reflectance measurements of the 190nm - 450nm and 800nm - 1000nm ranges are important to measurement of the trench profile.

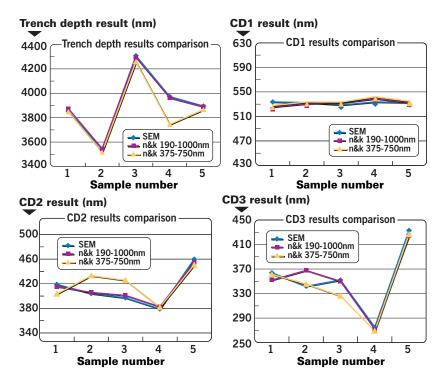

**FIGURE 4:** Comparison of n&k results, both limited range (350nm - 750nm) and broadband (190nm - 1000nm), to cross section SEM results for Trench Depth (upper left), CD1 (upper right), CD2 (lower left) and CD3 (lower right). For CD1 and CD3, the results match SEM results equally well for the full and limited wavelength range. For Trench Depth and CD2, the results from analysis of the full wavelength range have good agreement with the SEM results, while results from the limited wavelength range do not match as well. Sample 4 results were expected to be inaccurate for the limited wavelength range, and the trench depth for Sample 4 does not match the SEM result.

The calculations also confirm that decreasing the CD values limits the wavelength range in the Rs and Rp data where there is sensitivity to the depth and CD values. This is consistent with the experimental data that is measured for Sample 4, which has smaller CD values and exhibits sensitivity to the trench depth and CD values only from 190nm – 350nm in the Rs data and 800nm – 1000nm in the Rp data. This suggests that a standard reflectometer, with wavelength range of 375nm – 750nm, will have limited measurement capabilities for this type of trench structure, particularly when the CD values are smaller.

#### **SEM Comparison**

In order to verify the results from the optical measurement system, we compared results from SEM cross-sections for CD and depth to the values obtained by the n&k Olympian. Using the full wavelength range, 190nm–1000nm, there is a good match between cross-section SEM results for depth and CD and the measured results from the broadband polarized reflectometer (**FIGURE 4**). Using a limited wavelength range, 375nm–750nm, with an analysis model that is otherwise identical, the results do not compare as well with the SEM data, particularly the trench depth of Sample 4.

The reason that Sample 4 measurements are inaccurate for trench depth, using the limited wavelength range, is related to the CD values. For Sample 4, the CD3 value measured by cross-section SEM is ~275nm, significantly lower than any of the other samples. For deep trenches in silicon, as the CD gets smaller the OCD interference fringes are reduced at longer wavelengths. Experimental data in the UV region is required for measurement of this structure, as shown by the broadband data.

In order to further test the measurement limitations, we performed simulations using the full wavelength range to see the effects of smaller CD values on the Rs spectra. As CD2 and CD3 get smaller, the amplitude of interference fringes decreases and the wavelength region is narrowed. With CD2 equal to 400nm and CD3 equal to 350nm, interference fringes are present from 190nm - 420nm. However, with CD2 equal to 300nm and CD3 equal to 200nm, interference fringes are only present from 190nm - 280nm. Therefore, as the CD values become smaller the system must include UV wavelengths in order to measure the trench depth and CD.

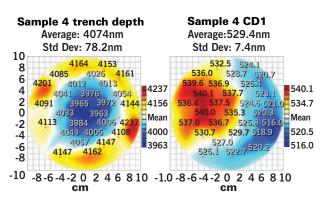

#### Wafer Uniformity

One advantage of an optical measurement system is the ease with which wafer uniformity maps can be created. While the cross-section SEM can

**FIGURE 5:** 29 Point Wafer Uniformity Results for Sample 4, 200mm wafer, as measured by broadband OCD. Dense mapping measurements are used to test the non-uniformity for depth and CD. Cross section SEM is typically done at a single point or a few points per wafer, so uniformity information is limited. The trench depth mapping shows a typical uniformity pattern after an etch process, with a center to edge effect, while CD1 is larger on the left side of the wafer, smaller on the right. show a detailed trench profile, it is both destructive and time consuming. With the broadband polarized reflectometer, however, wafer uniformity maps can be created in a few minutes, depending on the number of locations measured.

FIGURE 5 shows the wafer uniformity results for Sample 4 using the full wavelength range analysis (190nm *Continued on page 38*

The solution to help you better communicate with your tool vendors with the simulation results.

OPITCA is a fast, scalable Defect Inspection oriented FDTD Simulation software, capable of EUV Mask Inspection tool simulation.

Comprised of Modeler, Simulator and Analyzer, you can create your own DOI by adding materials and modeling Pattern/Defect/Incident Light/Aperture to assess the best optical conditions.

Save invaluable engineering resources during recipe creation/tuning and improve Inspection tool's productivity.

For more information, please contact sales@mirero.co.kr or visit www.mireroinc.com

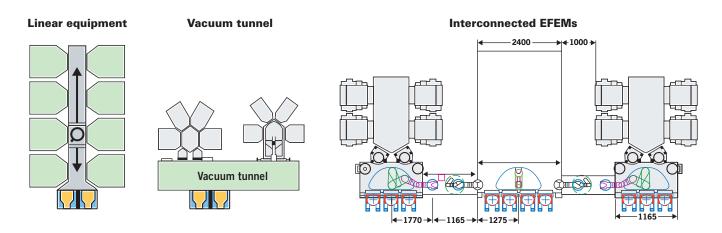

# Innovative automation approaches for 450mm factories

MICHAEL BRAIN, MAY SU, ANTHONY BONORA, and DANIEL BABBS, Brooks Automation, Chelmsford, MA

New approaches can help improve cycle time and achieve higher purity inter-process wafer environmental control.

utomation adds significant value by addressing key issues of cycle time, process variability and contamination. This is true for 300mm manufacturing and will be even more critical to enable the transition to 450mm manufacturing. It is important

to look at some of the issues facing the industry right now to understand the impact and benefits that fab automation will enable for the future. Current cycle times are unacceptable at 300mm, hindering the full utilization of assets and dulling market responsiveness. As manufacturers transition to sub-20nm process nodes, the queue time between certain process steps becomes more sensitive to variability and more difficult to support with current AMHS architectures. For example, between etch and post-etch clean the timing

stant where p of

**FIGURE 1.** 450mm sorter/EFEM with integrated tool buffer and nitrogen purge.

must be carefully controlled because exposure to moisture and oxygen immediately begins to destroy critical dimensions of features on the wafer surface.

As the industry progresses to smaller process nodes lithography requirements are driving the need innovative automation approaches. An architecture that enables wafers to be protected from oxygen and moisture between process steps will reduce the dependency on critical process timing and can positively impact yield. In the early 1990's