JULY 2015

# Sola State S

Controlling Measurements in Wafer Level Packaging

P. 27

Is it time to switch to OASIS.MASK? P. 33

More change for the chip industry P. 39

# Substrate Innovation for Extending Moore and More than Moore **P**18

### THE INTELLIGENT CHOICE

#### Giving you a clear edge

Today's challenges can never be solved by working alone. At Edwards we make it our business to understand our customers' applications as extensively as they do, and deliver innovative solutions for some of the most advanced and technically challenging processes, delivering process efficiencies and enabling the next generation devices.

find out more at www.edwardsvacuum.com

### Solid State TECHNOLOGY.

JULY 2015 VOL. 58 NO.5

The XYALIS viewer is able to display a huge database in seconds on any web browser thanks to OASIS.MASK file organization.

#### FEATURES

#### SILICON-ON-INSULATOR | Substrate innovation for extending Moore and more than Moore

Engineered SOI substrates are now a mainstream option for the semiconductor industry. Mariam Sadaka and Christophe Maleville, Soitec, Grenoble, France

18

**METROLOGY** Controlling measurements of WLP in high mix, high volume manufacturing Accurate and fast in-line monitoring is crucial for timely process drift detection and control.

Jin You Zao, STATS ChipPAC, Singapore, and John Thornell, Rudolph Technologies, Inc. Bloomington, MN.

#### **PHOTOMASKS** Is it time to switch to OASIS.MASK?

A summary of OASIS standard advantages and weaknesses is presented, based on six years of experience with customer databases. Dr Philippe Morey-Chaisemartin, Frederic Brault, XYALIS, Grenoble, France

39

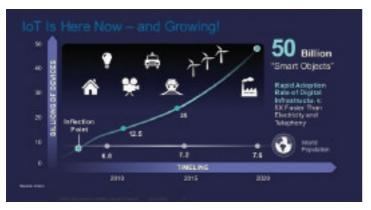

#### SEMICON WEST | More change for the chip industry

As if scaling to 7nm geometries and going vertical with FinFETs, TSVs and other emerging technologies wasn't challenge enough, the emerging market for connected smart devices will bring more changes to the semiconductor sector. And then there's 3D printing looming in the wings. *Paula Doe, SEMI, San Jose, CA*

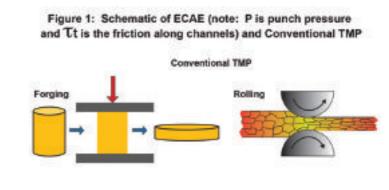

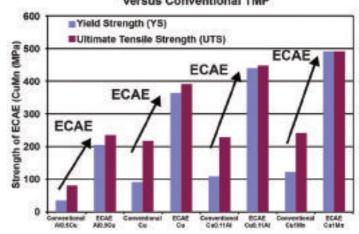

#### SPUTTERING | ECAE improves sputtering target performance

Because it can achieve extreme deformation, Equal Channel Angular Extrusion (ECAE) can deliver submicron, high strength and uniform microstructures. The resulting improvements in strength allow for monolithic targets with a longer target life of 20-100%.

Stephane Ferrasse, Susan Strothers and Christie Hausman, and Honeywell Electronic Materials, Sunnyvale, CA

#### COLUMNS

- 2 Editorial Blood and tears at DAC, Pete Singer, Editor-in-Chief

- 15 Packaging AMD announces HBM in 2015, Phil Garrou, Contributing Editor

- 16 Semiconductors Silicon technology extensions, Ed Korczynski, Sr. Technical Editor

- **48 Industry Forum** Simply obeying the laws of economics, *Phil Garrou, Contributing Editor*

#### DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 46 Ad Index

#### editorial

### Blood and tears at DAC

At this year's Design Automation Conference (DAC) in San Francisco, Brian Otis, a Director at Google, talked about how hundreds of millions of people are at risk of diabetes - and how a smart contact lens that continuously monitors blood glucose levels and transmits the data to a smartphone might just be the ideal solution.

There is a good correlation between your glucose levels in tears and that in blood (although it's a factor of magnitude lower), so a smart contact lens can measure glucose levels using a wireless chip

"What makes this all possible is the work that the semiconductor industry has done"

and miniaturized glucose sensor. The devices are embedded between two layers of soft contact lens material.

Google announced the smart lens project in January of 2014, at which time multiple clinical studies had been completed. A partnership was subsequently announced with Novartis's Alcon eye-care division in July of 2014.

Otis said that the universe of people who are either bona fide pre-diabetic or at risk is huge. "It's hundreds of millions of people," he said. "Our hypothesis is that if we are able to create more comfortable CGMs (continuous glucose monitors), this will significantly impact the diabetes management problem we're facing. No one has solved this problem yet, but we really want to do this because it could improve people's lives," he said.

A smart contact lens could solve the problem because it's a wearable device that many millions of people already wear on a daily basis. "If there is an option of wearing the device that many people wear, that's comfortable and also corrects your vision and gives you this valuable information, you're likely to do that over than, let's say, pricking your finger," Otis said.

Otis described smart contact lenses as not just another gadget. "It's really part of an ecosystem that can form a new type of proactive healthcare. We're going to work really hard on that," he said.

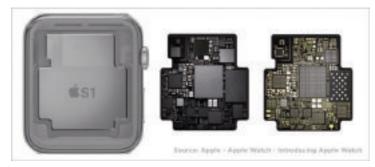

What makes this all possible, of course, is the work that the semiconductor industry has done in miniaturization over the last several decades. Otis said more work is needed: "The chips, the passive components, the power supplies, the antennas: Everything needs to shrink," he said.

-Pete Singer, Editor-in-Chief

### Solid Stat

Pete Singer, Editor-in-Chief Ph: 978.470.1806 psinger@extensionmedia.com Shannon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com Ed Korczvnski, Senior Technical Editor, edk@extensionmedia.com Jeff Dorsch, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor,

Semiconductor Manufacturing & Design

CREATIVE/PRODUCTION/ONLINE Spryte Heithecker, Production Manager Stephanie Bradbury, Media Coordinator Nicky Jacobson, Senior Graphic Designer Caldin Seides, Graphic Designer

Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION Jenna Johnson. jjohnson@extensionmedia.com

2343 (8 am - 5 pm PST)

**CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, **Business Development** msterling@extensionmedia.com

July 2015, Volume 58, Number 4 • Solid State Technology ©2015 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00, Youwill continue to receive your subscription free of charge. This fee is only for airmail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-CHAR (Darde State) State) State St

#### For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2015 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

### 3D, Parallel CT X-ray, to 0.3 µm Resolution

### The solution to your production process problems!

Omron's 3D, CT X-ray is the perfect solution to manufacturers desiring a competitive advantage in process improvement. Use Automated Inspection Logic and up to 300 slices to achieve precise and reliable analysis of your product.

# Consult with us to find the best fit for your needs.

SEMICON West BOOTH #417 South Hall

OMRON AUTOMATION AND SAFETY • Toll free: 800.556.6766 • www.omron247.com

### online@www.solid-state.com

#### Web Exclusives

#### 3DIC Technology Drivers and Roadmaps

Ed Korczynski, Sr. Technical Editor describes how, after 15 years of targeted R&D, through-silicon via (TSV) formation technology has been established for various applications. There are now detailed roadmaps for different types of 3-dimensional (3D) ICs well established in industry. http://bit.ly/1lufRdm

### Conference features the latest in flexible display technology

At Display Week 2015, bigger is better. Smaller is better. And flexible may be best of all, for the era of wearable electronics. There are some huge screens on display, so to speak, throughout the conference's exhibition floor, such as BOE Technology Group's 110-inch 8K Ultra High Definition television or LG Display's curved 77-inch 4K UHD TV. There are also very small displays, such as E Ink's smallest electronic shelf labels. (From SemiMD, part of the Solid State Technology network)

http://bit.ly/1G9HGup

### The ConFab: The semi industry is now mature

The conference portion of The ConFab 2015 started with an afternoon panel session, "Exploring the Edges of Semiconductor Technology and Business." Dick James kicked it off with a presentation on the state of the art in the business, as seen by Chipworks, followed by a panel discussion with James, Phil Garrou, and Gopal Rao.

http://bit.ly/1JVjQUx

### Isolating electrical faults in advanced IC devices

Yield improvement and production engineers working on today's ICs encounter many challenges as defects affecting device operation go undetected by traditional in-line techniques. Electrical Failure Analysis (EFA) is a suite of techniques that helps the modern day fab increase yields by isolating faults to areas small enough for Physical Failure Analysis (PFA). In this webinar, we showcase a few of the proven EFA fault isolation techniques and describe how EFA helps to characterize the underlying defects. http://bit.ly/1JYnLQn

#### Insights from the Leading Edge: Advanced Packaging at The ConFab

At the recent ConFab meeting in Las Vegas, aside from all the talk about consolidation, Bill Chen from ASE and Li Li from Cisco put together a great Advanced Packaging session. http://bit.ly/1Bglizx

### **EUV lithography: What's** next and when?

This year started with an announcement, during the SPIE AL Conference, of the achievement of 100 W+ power from high volume manufacturing (HVM) EUV sources in the fab. One hundred watts at intermediate focus has been a long-standing benchmark and is a definite success, and we also can be sure that source power and availability will increase this year. The focus will now change to addressing the remaining challenges of EUVL, with questions turning on what comes next and when, as the industry prepares to deploy EUVL into HVM. http://bit.ly/1BUUejP

The **ConFab**

Many THANKS to the attendees, speakers and sponsors who made The ConFab 2015 a resounding success. We look forward to another great event in 2016!

#### Key Executives from these organizations were at The ConFab 2015:

3MTS Advantest Air Products & Chemicals AlixPartners AMD Applied Materials **Applied Seals** ASE Group ASMC Astronics Test Systems Atmel Banner Industries Brewer Science Broadcom Cascade Microtech CEA-Leti China Wafer Level CSP CO.,LTD Chipworks Cimetrix Cisco Systems Citibank Technology Cyient **Digital Specialty Chemicals** Edwards Entrepix EV Group Flanders Investment & Trade G450C **GLOBALFOUNDRIES** Hitech Semiconductor

Hitech Semiconductor Wuxi IBM IBM Research IC Insights imec Infineon Technologies Intel ITRS KLA-Tencor Lam Research Linde Electronics M+W Group Marcy NanoCenter MDC Vacuum Products Micrel MicroChip Technology Microelectronc Consultants of NC Microtronic MRK International MUFG Union Bank Novati Technologies **NVIDIA** NY Loves Nanotech ON Semiconductor Pall Corporation Plexus **POET Technologies** Process Technology Qualcomm Rambus

Renesas Electronics America Inc. **Rockwell Automation** Rudolph Technologies Samsung Semiconductor Europe Samsung SSI SEMĬ Semico Research Siconnex Siemens Silicon Catalyst SK Hynix SK Hynix America Stelliam Investment Management Surplus Global Taiji Semiconductor (Suzhou) Co Ltd Texas Instruments The MAX Group Tosoh Quartz **Total Facility Solutions** TSI Semiconductors TSMC Ulvac Technologies UMC University of California, San Diego Valqua America VAT, Incorporated VAT Vakuumventile AG Watlow Wisdom IC

#### **MARK YOUR CALENDAR FOR 2016!**

The ConFab Conference & Networking Event Encore at the Wynn | Las Vegas June 12-15, 2016 www.theconfab.com

Owned & Produced by: Extension

MEDIA

Presented by:

Please send news articles to sdavis@extensionmedia.com

#### worldnews

USA – Fairchild Semiconductor launched its first product line of MEMS products.

**USA – Avago Technologies** announced plans to acquire **Broadcom** for \$37B.

ASIA – A research team at **KAIST** announced it has developed the first flexible phase-change random access memory

USA – DCG Systems, Inc. announced it has acquired MultiProbe, Inc.

**EUROPE – imec** announced at Intersolar Europe a new efficiency record for its large area n-type PERT crystalline silicon solar cell, now reaching 22.5 percent (calibrated at ISE CalLab).

ASIA – Sankalp Semiconductor announced FD-SOI services and IP partnership with STMicroelectronics.

**EUROPE – CEA-Leti** announced during the Design Automation Conference that seven partners have joined its new FD-SOI IC development program, Silicon Impulse.

**USA – Pixelligent** closed \$3.4 million in new funding.

**EUROPE** – Europe's leading nanoelectronics institutes, **Tyndall National Institute** in Ireland, **CEA-Leti** in France and **imec** in Belgium, have entered a €4.7 million collaborative open-access project called **ASCENT** (Access to European Nanoelectronics Network).

ASIA – SK Hynix Inc. announced that it is shipping mass production volumes of 1st generation High Bandwidth Memory based on its advanced 20nm-class DRAM process technology.

# news

### NXP Semiconductors announces agreement to sell RF power business

NXP Semiconductors N.V. announced an agreement that will facilitate the sale of its RF Power business to Jianguang Asset Management Co. Ltd. Under the terms of the agreement JAC Capital will pay \$1.8 billion for the business.

The NXP RF Power business is one of the market leaders in high performance RF power amplifiers primarily focused on the cellular base station market, but with potential future growth applications in the areas of industrial lighting, next generation cooking and automotive electronic ignition systems.

"The creation of a new company focused on the RF power amplifier market is a ground breaking transaction for JAC Capital and a great deal for our customers. Although we would have expected a higher valuation in a regular disposal, JAC Capital's ability to support continued growth and development of the business and its ability to sign and close a transaction rapidly was a key factor in enabling the best outcome for our customers and shareholders, as well as supporting the closure of the merger with Freescale Semiconductor," said Richard Clemmer, NXP Chief Executive Officer.

"We are happy to reach an agreement to acquire the RF Power business from NXP with its strong team and established technology. We will keep on increasing investment in R&D, manufacturing and customer service of the new company to strengthen its market position. JAC Capital and its shareholders will also help the new company to maintain fast and

Continued on page 11

#### "Easy does it" — Fabs trim spending plans

By Christian G. Dieseldorff, Industry Research & Statistics Group, SEMI

Semiconductor capital expenditures (without fabless and backend) are expected to slow in rate, but continue to grow by 5.8 percent in 2015 (over US\$66 billion) and 2.5 percent in 2016 (over \$68 billion), according to the May update of the SEMI World Fab Forecast report. A significant part of this capex is fab equipment spending.

Fab equipment spending is forecast to depart from the typical historic trend over the past 15 years of two years of spending growth followed by one year of decline. Departing from the norm, equipment spending could grow every year for three years in a row: 2014, 2015, and 2016 (see Table 1).

At the end of May 2015, SEMI published its latest update to the World Fab Forecast report, reporting on more than 200 facilities with equipment spending in 2015, and more than 175 facilities projected to spend in 2016.

Continued on page 12

#### Visit IPG Photonics at SEMICON West Booth #2732

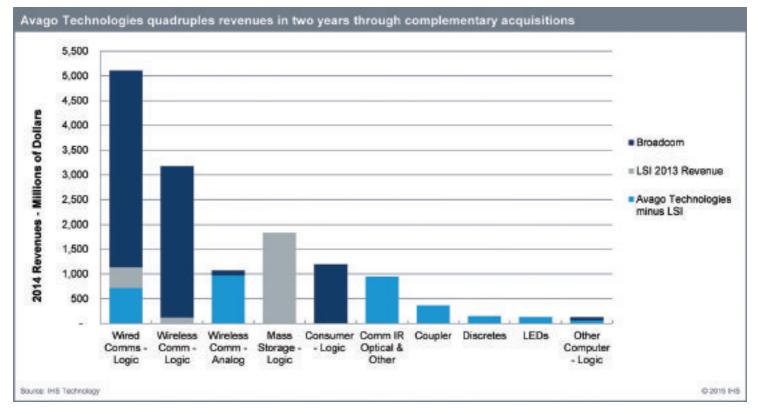

#### Avago Technologies acquisition of Broadcom creates new semiconductor powerhouse

Merger activity in the semiconductor industry moved to a new level with the announcement of the agreement for Avago Technologies to acquire Broadcom, according to IHS Inc., a global source of critical information and insight. The deal, which is valued at \$37 billion in cash and stock, will create a new company valued at \$77 billion.

"This is the latest and, by far the largest, merger in the semiconductor industry, as major players continue to move in an aggressive way to establish position and profitability in key segments of the industry," said Dale Ford, vice president and chief analyst for IHS Technology. "Investors have responded favorably to the announcement, with promised bottom-line benefits derived from realized cost savings."

The combined revenues of the two companies in 2014 exceeds \$14 billion, making the newly merged semiconductor company the sixth-largest globally, according to final annual semiconductor market shares. More significantly, the combination of the two companies creates the third-largest semiconductor supplier, trailing only Intel and Qualcomm, if memory integrated-circuit (IC) revenues are excluded. "The complementary product portfolios of the two companies move them into a powerful position, in both the communications IC market and the storage IC market," Ford said.

#### Quadrupling in size in two years

This latest move from Avago Technologies has formed a company with revenues four times greater than in 2013. The two biggest recent mergers by Avago Technologies were the acquisition of LSI in 2014 and this new acquisition of Broadcom. The mergers increase the company's strength in the communications and storage categories. Outside of these two areas, Broadcom has a much smaller presence in consumer electronics and industrial electronics and almost no revenue from other data processing and automotive electronics.

Continued on page 14

### THE POWER of TWO.

### two lasers | one station

higher efficiency

greater flexibility

lower cost of ownership

+1 (603) 518-3200 www.ipgphotonics.com sales.ipgm@ipgphotonics.com

PHOTONICS

### Your Reliable Single Wafer Processor

All-In-One Process (Chemical, Rinse, Dry in One Chamber) Clean, Etch & Remove Polymer in FEOL or BEOL Field-proven Performance < 20 nm

SSD-3000 APOLLON

### **Expertise in Wet Etch & Clean System**

Visit us at SEMICON West 2015, Booth 433 - South Hall

#### 300mm Single Spin Wet Etching & Cleaning System

#### Apollon

- High throughput (up to 330 WPH)

- Multi-chemical process (maximum 3 chemicals)

- Reduced chemical consumption by recycling

- Small footprint (2200mm × 4000mm)

- Individually controlled chamber

- 8-chamber double-decker (SS-D Type)

#### 300mm HDI Non-ashing & Resist-stripping System

#### **HTS-300S**

- Minimum consumption of chemical (< 150cc)

- Temperature control by IR heater ( $\leq$  240 °C)

- Reduced chemical fumes by flip-over processing

- Minimum process time for stripping ( $\leq$  30 seconds)

- Contamination control with separate chambers

- 4 SPM + 4 cleaning-chamber double-decker

#### www.globalzeus.com

- Main Contact : wschoi@globalzeus.com

- Sales Representative : wes.bock@malatekinc.com

#### 300/200mm Wet Batch Station

#### BW series 3000/2000

- Photo resist stripping / nitride removing / wet etching

- High throughput (up to 500 WPH)

- High-temperature processing (≤ 165℃)

- Nitride pullback in 3D flash memory

- 50 wafers/batch, immersion type

#### 4"/6" Lift-off Process Technology for LED

#### **Evolution**

- Vertical wafer positioning in the immersion bath

- Single spin processing with multi-level chamber

- Easy and efficient chemical reclaim

- Simultaneously clean the both sides of wafer

- Combining dip and spin process technologies

### **news**cont

#### **MEMS** suppliers ride automotive safety wave

Suppliers of MEMS-based devices rode a safety sensing wave in 2014 to reach record turnover in automotive applications, according to analysis from IHS, a global source of critical information and insight.

Mandated safety systems such as Electronic Stability Control (ESC) and Tire Pressure Monitoring Systems (TPMS) – which attained full implementation in new vehicles in major automotive markets last year – are currently driving revenues for MEMS sensors. Those players with strong positions in gyroscopes, accelerometers and pressure sensors needed in these systems grew as well, while companies in established areas like high-g accelerometers for frontal airbags and pressure sensors for side airbags also saw success.

Major suppliers of pressure sensors to engines similarly blossomed – for staple functions like manifold absolute air intake and altitude sensing – but also for fast-growing applications like vacuum brake boosting, gasoline direct injection and fuel system vapor pressure sensing.

#### Bosch was the overall number one

MEMS supplier with US\$790 million of devices sold last year, close to three times that of its nearest competitor, Sensata (US\$268 million). Bosch has a portfolio of MEMS devices covering pressure, flow, accelerometers and gyroscopes, and also has a leading position in more than 10 key applications. The company grew strongly in ESC and roll-over detection applications, and key engine measurements like manifold absolute pressure (MAP) and mass air flow on the air intake, vacuum brake booster pressure sensing and common rail diesel pressure measurement.

Compared to 2013, Sensata jumped to second place in 2014 ahead of Denso and Freescale, largely on strength in both safety and powertrain pressure sensors, but also through its acquisition of Schrader Electronics, which provides Sensata with a leading position among tire pressuremonitoring sensor suppliers.

While Sensata is dominant in TPMS and ESC pressure sensors, it also leads in harsh applications like exhaust

Suppliers of Automotive MEMS sensors

gas pressure measurement. Freescale, on the other hand, is second to Bosch in airbag sensors and has made great strides in its supply of pressure sensors for TPMS applications.

Despite good results in 2014, Denso dropped two places compared to its overall second place in 2013, largely as a result of the weakened Yen. Denso excelled in MAP and barometric pressure measurement in 2014, but also ESC pressure and accelerometers. Denso has leadership in MEMS-based air conditioning sensing and pressure sensors for continuous variable transmission systems, and is also a supplier of exhaust pressure sensors to a major European OEM.

> Secure in its fifth place, Analog Devices was again well positioned with its high-g accelerometers and gyroscopes in safety sensing, e.g. for airbag and ESC vehicle dynamics systems, respectively.

> The next three players in the top 10, in order, Infineon, Murata and Panasonic, likewise have key sensors to offer for safety. Infineon is among the leading suppliers

of pressure sensors to TPMS systems, while Murata and Panasonic serve ESC with gyroscope and accelerometers to major Tier Ones.

The top 10 represents 78 percent of the automotive MEMS market volume, which reached \$2.6 billion in 2014. By 2021, this market will grow to \$3.4 billion, a CAGR of 3.4 percent, given expected growth for four main sensors — pressure, flow, gyroscopes and accelerometers. In addition, night-vision microbolometers from FLIR and ULIS and humidity sensors from companies like Sensirion and E+E Elektronik for window defogging will also add to the diversity of the mix in 2021.

DLP chips from Texas Instruments for advanced infotainment displays will similarly bolster the market further in future. More details can be found in the IHS Technology H1 2015 report on Automotive MEMS.  $\diamond$

#### Continued from page 6

stable growth through our network of worldwide financial institutions, industrial leaders and JAC Capital's management team with many years of experience in the semiconductor and telecom industry," said Brighten Li, Chairman of JAC Capital Investment Evaluation Committee.

Under the agreement, the entire scope of the NXP RF Power business and approximately 2,000 NXP employees who are primarily engaged globally in the RF Power business, including its entire management team, are to be transferred to an independent company incorporated in the Netherlands, which will be 100 percent acquired by JAC Capital upon closing of the transaction. Additionally, all relevant patents and intellectual property associated with the RF Power business will be transferred in the sale, as well the NXP back-end manufacturing operation in the Philippines that is focused on advanced package, test and assembly of RF Power products.

The transaction, including the entry into and the terms of the definitive agreements and the approval of JAC Capital as the acquirer are subject to review and approval by the US Federal Trade Commission, the European Commission, MOFCOM and other agencies in connection with their review of NXP's proposed acquisition of Freescale Semiconductor, Ltd.

NXP and JAC Capital expect the sale to close within the second half of 2015, pending required regulatory approval and employee representative consultations. NXP anticipates the sale of its RF Power business to be dilutive to earnings on a standalone basis in the fourth quarter 2015 and 2016. Proceeds from the sale of the RF Power business will be used to partly fund the previously announced acquisition of Freescale Semiconductor, Ltd. ◆

Energy-efficient dry multi-stage process pumps for all applications in semiconductor industry

- Low energy consumption

- Improved temperature management to optimize the pump according to your process

- Protection of the pump against precursor cracking or condensable deposition

- Corrosion resistant and high particle tolerance

- Extended monitoring functionalities

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com

VISIT US AT SEMICON WEST BOOTH #1517

### **news**cont

#### Continued from page 6

The report shows a large increase in spending for DRAM, more than 45 percent in 2015. Also, spending for 3D NAND is expected to increase by more than 60 percent in 2015 and more than 70 percent in 2016. The foundry sector is forecast to show 10 percent higher fab equipment spending in 2015, but may experience a decline in 2016. Even with this slowdown, the foundry sector is expected to be the second largest in equipment spending, surpassed only by spending in the memory sector.

A weak first quarter of 2015 is dropping spending for the first half of 2015, but a stronger second half of 2015 is expected. Intel and TSMC reduced their capital expenditure plans for 2015, while other companies, especially memory, are expected to increase their spending.

The SEMI data details how this varies by company and fab. For example, the report predicts increased fab equipment spending in 2015 by TSMC and Samsung. Samsung is the "wild card" on the table, with new fabs in Hwaseong, Line 17 and S3. The World Fab Forecast report shows how Samsung is likely to ramp these fabs into 2016. In addition, Samsung is currently ramping a large fab in China for 3D NAND (VNAND) production. Overall, the data show that Samsung is will likely spend a bit more

for memory in 2015 and much more in 2016. After two years of declining spending for System LSI, Samsung is forecast to show an increase in 2015, and especially for 2016.

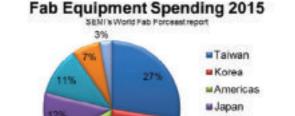

Figure 1 depicts fab equipment spending by region for 2015.

In 2015, fab equipment spending by Taiwan and Korea together

are expected to make up over 51 percent of worldwide spending, according to the SEMI report. In 2011, Taiwan and Korea accounted for just 41 percent, and the highest spending region was the Americas, with 22 percent (now just 16 percent). China's fab spending is still dominated by non-Chinese companies such as SK Hynix and Samsung, but the impact of Samsung's 3D NAND project in Xian is significant. China's share for fab spending grew from 9 percent in 2011 to a projected 11 percent in 2015; because of Samsung's fab in Xian, the share will grow to 13 percent in 2016.

China

SE Asia

Europe & Mideast

#### FIGURE 1.

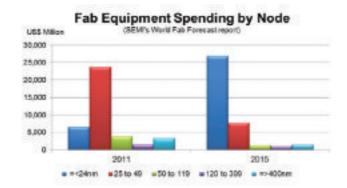

#### FIGURE 2.

#### Fab Equipment Spending

| in US\$ Million | 2011         | 2012         |    | 2013   | 2014         | 2015         | 2016         |

|-----------------|--------------|--------------|----|--------|--------------|--------------|--------------|

| 300mm           | \$<br>33,500 | \$<br>29,580 | \$ | 27,070 | \$31,166     | \$35,415     | \$38,566     |

| =<200mm         | \$<br>5,916  | \$<br>3,262  | \$ | 2,951  | \$<br>3,686  | \$<br>3,251  | \$<br>2,168  |

| Total           | \$<br>39,416 | \$<br>32,842 | \$ | 30,021 | \$<br>34,852 | \$<br>38,666 | \$<br>40,734 |

| Change %        | 16%          | -17%         | _  | -9%    | 16%          | 11%          | 5%           |

Source: SEMI's World Fab Forecast report (May 2015)

TABLE 1.

Table 2 shows the share of the top two companies drive a region for fab equipment spending:

Over time, fab equipment spending has also shifted by technology node. See Figure 2, where nodes have been grouped by size:

In 2011, most fab equipment spending was for nodes between 25nm to 49nm (accounting for \$24 billion) while nodes with 24nm or smaller drove spending less than \$7 billion. By 2015, spending flipped, with nodes equal or under 24nm accounting for \$27 billion while spending on nodes between 25nm to 49nm dropped to \$8 billion. The SEMI World Fab data also predict more spending on nodes between 38nm to 79nm, due to increases in the 3DNAND sector in 2015 and accelerating in 2016 (not shown in the chart).

#### When is the next contraction?

As noted above, over the past 15 years the industry has never achieved three consecutive years of positive growth rates for spending. 2016 may be the year which deviates from this historic cycle pattern. A developing hypothesis is that with more consolidation, fewer players compete for market positions, resulting in a more controlled spending environment with much lower volatility.

Learn more about the SEMI fab databases at: www.semi.org/MarketInfo/FabDatabase. �

| Region           | Largest spending 2015           | Share      |

|------------------|---------------------------------|------------|

| Americas         | 1. Globalfoundries<br>2. Intel  | 36%        |

| China            | 1. Samsung                      | 30%        |

| Europe & Mideast | 2. SMIC<br>1. Intel             | 27%        |

| Corope & Mideast | 2. Globalfoundries              | 15%        |

| Japan            | 1. Flash Alliance<br>2. Sony    | 57%<br>21% |

| Korea            | 1. Samsung<br>2. sk hynix       | 66%<br>33% |

| SE Asia          | 1. Micron<br>2. Globalfoundries | 71%        |

| Taiwan           | 1. TSMC<br>2. Inotera           | 65%<br>14% |

TABLE 2.

### **ATH-M**

#### Magnetically levitated turbopumps from 500 l/s to 3200 l/s

- Very high gas throughput for all process gases

- Low lifetime costs due to maintenance-free technology

- Standard, heated and corrosion resistant coating versions available

- Available with integrated or external controller

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com

VISIT US AT SEMICON WEST BOOTH #1517

### **news**cont.

#### Continued from page 7

#### **Communications focus**

The newly merged Avago-Broadcom will dominate the market, commanding 40 percent of the wired communications IC market, excluding memory. Revenues for this category in 2014 were more than five times larger than the next largest supplier, Intel.

The merged company will boost its share of the wireless communications IC market to nearly 8 percent, ranking fourth behind Qualcomm, Samsung Electronics and MediaTek. With an overall market share of 14 percent for all communications ICs, the company ranks second, trailing only Qualcomm and ahead of Samsung Electronics.

The strength of the merged Avago/Broadcom in the wired communications market positions it to benefit from the strong projected market growth. The five-

year compound annual growth rate (CAGR) for wired communications is 7 percent, leading all other market segments. On the other hand, semiconductors used in wireless communications products is projected to go through a period of weak growth at only 2 percent CAGR over the next five years. "The size of the combined company could give it a strong position to increase its market share over this time," Ford said.

#### Cost savings rolling to the bottom line

The companies predict \$750 million in annual cost synergies in 18 months. A quick look at the distribution of their revenues shows that 66 percent of Avago Technologies' revenue comes from products shipped to the Asia-Pacific (APAC) region, for use in electronics production. Broadcom derived 93 percent of its revenues from APAC shipments of its ICs. "The alignment of the supply chain between the two companies will facilitate the projected savings," Ford said.  $\triangleleft$

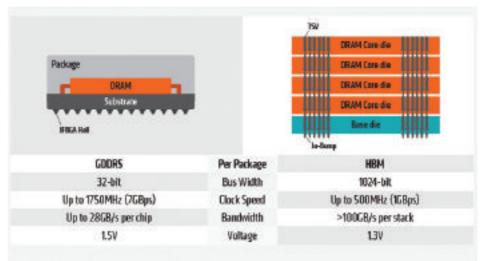

### AMD announces HBM in 2015

For over two years now, I have been saying that memory stacks will soon be seen in high end graphics processor modules. Nvidia was the first to announce the use of stacked memory with GPUs. Nvidia's Volta GPU module was scheduled for 2015 release and was supposed to use the Micron Hybrid Memory Cube (HMC). Rumors are that after HMC's development fell behind the proposed roadmap timing, Nvidia moved the Volta introduction out to > 2016 after the Pascal module, which will be based on Hynix HBM 2, scheduled to be commercial in 2016.

Now the first commercial graphics products to feature HBM clearly will be AMD's R9 390X series

Fiji GPU in 2015. The Rx 300 series will also reportedly be the first to feature TSMC's 20nm technology and the first to be equipped with HBM. There are 4 HBM stacks packed on the same interposer as Fiji. Each HBM stack has a capacity of 1GB of memory.

Recent rumors from Taiwan indicate that production is being slowed by issues concerning delivery of the silicon interposers from their primary supplier. Reports are that AMD is having to rely more heavily on the secondary supplier to try to keep production on track.

The first generation of HBM promises to deliver 4.5X the bandwidth of GDDR5 and 16X the bandwidth DDR3 as shown in Figure 1. The second generation HBM is well underway and promises to double the bandwidth by doubling the speed from 1Gbps to 2Gbps. It will also quadruple the memory capacity for 4-Hi stacks from 1GB to 4GB.

Reportedly HBM2 is scheduled to be featured in

AMD's upcoming "Greenland" GPU. It's rumored that the new graphics family will be manufactured at GlobalFoundries on their 14nm FinFET process node; that would be a major loss for TSMC. A summary of AMD graphics processor modules is shown in Figure 2.

There are also reports that AMD is working on multicore APUs that will use similar interposer / HBM memory technology. ◆

FIGURE 1. Comparison of HBM and other DRAMs. Source: SK Hynix.

| WCCFTech                 | Year | Process | Flagship GPU | Product | Memory    | Bandwidth |

|--------------------------|------|---------|--------------|---------|-----------|-----------|

| Southern Islands         | 2012 | 28nm    | Tahiti       | HD 7970 | 3GB GDDR5 | 264GB/s   |

| Volcanic Islands         | 2013 | 28nm    | Hawaii       | R9 290X | 4GB GDDR5 | 320GB/s   |

| Pirate/Caribbean Islands | 2015 | 28nm    | Fiji         | R9 390X | 8GB HBM1  | 640GB/s   |

| Arctic Islands           | 2016 | 14nm    | Greenland    | R9 490X | 16GB HBM2 | 1TB/s     |

FIGURE 2. AMD graphics processor modules.

#### Packaging

# Silicon technology extensions

In the spring meeting of the Materials Research Society held recently in San Francisco, Symposium A: Emerging Silicon Science and Technology included presentations on controlling the structure of crystalline spheres and thinfilms. Such structures could be used in future complementary metal-oxide semiconductor (CMOS) devices and in photonic circuits built using silicon.

Alexander Gumennik, et al., from the Massachusetts Institute of Technology, presented on "Extraordinary Stress in Silicon Spheres via Anomalous In-Fiber Expansion" as a way to control the bandgap of silicon and thus enable the use of silicon for photodetection at higher wavelengths. A silica fiber with a crystalline silicon core is fed through a flame yielding spherical silicon droplets via capillary instabilities. Upon cooling the spheres solidify and expand against the stiff silica cladding generating high stress conditions. Band gap shifts of 0.05 eV to the red (in Si) are observed, corresponding to internal stress levels. These stress levels exceed the surface stress as measured through birefringence measurements by an order of magnitude, thus hinting at a pressure-focusing mechanism. The effects of the solidification kinetics on the stress levels reached inside the spheres were explored, and the experimental results were found to be in agreement with a pressure-focusing mechanism arising from radial solidification of the spheres from the outer shell to the center. The simplicity of this approach presents compelling opportunities for the achievement of unusual phases and chemical reactions that would occur under high-pressure high-temperature conditions, which therefore opens up a pathway towards the realization of new in-fiber optoelectronic devices.

Fabio Carta and others from Columbia University working with researchers from IBM showed results on "Excimer Laser Crystallization of Silicon Thin Films on Low-K Dielectrics for Monolithic 3D Integration." This research

#### Semiconductors

supports the "Monolithic 3D" (M3D) approach to 3D CMOS integration as popularized by CEA-LETI, as opposed to the used of Through Silicon Vias (TSV). M3D requires processing temperature below 400°C if copper interconnects and low-k dielectric will be used in the bottom layer. Excimer laser crystallization (ELC) takes advantage of a short laser pulse to fully melt the amorphous silicon layer without allowing excessive time for the heat to spread throughout the structure,

**Ed Korczynski,** Sr. Technical Editor

achieving large grain polycrystalline layer on top of temperature sensitive substrates. The team crystallized 100nm thick amorphous silicon layers on top of SiO2 and SiCOH (low-k) dielectrics. SEM micrographs show that post-ELC polycrystalline silicon is characterized by micron-long grains with an average width of 543 nm for the SiO2 sample and 570 nm for the low-k samples. A 1D simulation of the crystallization process on a back end of line structure shows that interconnect lines experience a maximum temperature lower than 70°C for the 0.5  $\mu$ m dielectric, which makes ELC on low-k a viable pathway for achieving monolithic integration.

Seiji Morisaki, et al., from Hiroshima Univ, showed results for "Micro-Thermal-Plasma-Jet Crystallization of Amorphous Silicon Strips and High-Speed Operation of CMOS Circuit." The researchers used micro-thermalplasma-jet (µ-TPJ) for zone melting recrystallization (ZMR) of amorphous silicon (a-Si) films to form lateral grains larger than 60 µm. By applying ZMR on a-Si strip patterns with widths <3 µm, single liquid-solid interfaces move inside the strips and formation of random grain boundaries (GBs) are significantly suppressed. Applying such strip patterns to active channels of thin-film-transistors (TFTs) results in a demonstrated field effect mobility ( $\mu$ FE) higher than 300 cm2/V\*s because they contain minimal grain-boundaries. These a-Si strip pattern were then used to characteristic variability of n- and p-channel TFTs and CMOS ring oscillators. The strip patterns showed improved uniformities and defect densities, in general. A 9-stage ring oscillator fabricated with conventional TFTs had a maximum frequency (Fmax) of operation of 58 MHz under supply voltage (Vdd) of 5V which corresponds to a 1-stage delay ( $\tau$ ) of 0.94 ns, while strip channel TFTs demonstrated 108 MHz Fmax and  $\tau$  decreased to 0.52 ns.  $\blacklozenge$

# service solutions

### YOUR GLOBAL PARTNER

- Proactively improving vacuum process environments

- Providing service choices to meet application needs

- Delivering safer workplaces and a greener future

For more information visit : edwardsvacuum.com/SST

# Substrate innovation for extending Moore and more than Moore

MARIAM SADAKA and CHRISTOPHE MALEVILLE, Soitec, Austin, TX and Grenoble, France

*Engineered SOI substrates are now a mainstream option for the semiconductor industry.*

he number of mobile subscribers worldwide reached 95.5% of the world's population in 2014 and is expected to reach 9.3B by 2019 (1). This fast growing trend is driving end markets towards satisfying stringent demands of mobile connected users. Whether it is a smartphone or a wearable device, the key requirements include low cost, extended battery life, more functionalities, smaller form factor, and fast time to market. In an effort to bring more performance, more functionality or less power consumption, innovation starting at the substrate level has demonstrated significant achievements. This includes implementing planar Fully Depleted Silicon-On-Insulator (FD-SOI) devices with full back bias capability to extend Moore's Law beyond 28nm and meet power/ performance/cost requirements for low power SoCs. In addition, using High Resistivity SOI for integrating the RF Front End Module (FEM) providing significant die cost advantage with increased performance and functionality. In this paper, engineered substrates for next generation ultra-low power integrated digital and RF devices and other emerging applications will be discussed.

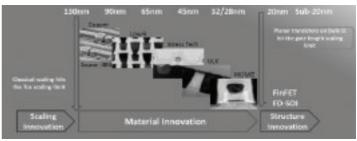

#### Device scaling and device functional diversification

Device scaling has been following Moore's law for the last five decades, doubling transistor density every two years, bringing higher performance, more functionality at lower cost. To maintain this trend, the industry implemented non-classical ways to continue on the scaling path. This started with innovation at the material level, then

FIGURE 1. Technology migration history [2].

innovation at the device structure level demonstrating improved electrostatic control enabled by fully depleted (FD) devices (**FIGURE 1**). FD devices include planar FD-SOI, vertical FinFET or multi-gate device structures. FD-SOI is a great example of device scaling in the substrate era, where the engineered substrate provides the fully depleted structure that solves the variability challenge and enables body bias capabilities to meet the power/performance and cost requirements for low power consumer SoCs.

The semiconductor industry also has another key focus called More-Than-Moore. This new trend provides added non-digital functional diversification without necessarily scaling according to Moore's Law. Morethan-Moore technologies cover a wide range of domains, and there are numerous examples where advantages brought by substrate engineering enable better performance and more functionality. With the increasing demand for wireless data bandwidth and the emergence of LTE Advanced, new RF devices with higher levels of integration and more stringent specifications need to be developed. RF-SOI substrates are a great example of how engineered substrates play a major role in achieving

**MARIAM SADAKA** is a Soitec fellow based in Austin, TX and **CHRISTOPHE MALEVILLE** is Senior Vice President, Digital Electronics Business Unit for Soitec, Grenoble, France.

#### Your production worries –

How do we keep our tools communicating for the lifetime of our systems?

How can we prevent lost batches due to missed or corrupted data?

#### Your relief – Host communication without a PC

Presenting a single controller for logic, motion, networks, and built-in SECS/GEM communication.

## See our innovative control solutions in action.

SEMICON West BOOTH #417 South Hall

OMRON AUTOMATION AND SAFETY • Toll free: 800.556.6766 • www.omron247.com

SILICON-ON-INSULATOR

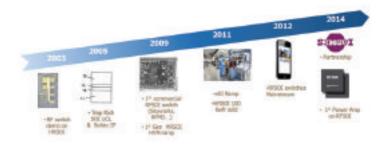

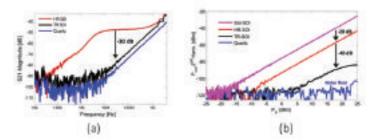

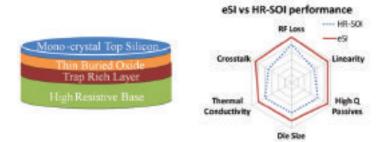

the needed level of performance and integration. Two generations of High Resistivity SOI (HR-SOI) substrates compatible with standard CMOS processing were developed [3]. While Gen 1 HR-SOI is well suited for 2G and 3G requirements, Gen 2 HR-SOI enables much higher linearity and isolation meeting most stringent LTE Advanced requirements and thus is paving the way for higher levels of integration with better performance at an improved cost (**FIGURE 2**).

#### **UTBB FD-SOI substrates**

FD-SOI with ultra-thin Box, known as Ultra-Thin-Body and Box (UTBB) substrates, are an attractive candidate for extending Moore's Law at 28nm and beyond while keeping the cost benefit from shrinking. UTBB FD-SOI devices represent an extension of the planar device architecture demonstrating several advantages essential to low power SoCs.

FD-SOI devices have excellent immunity to Short Channel Effects (SCE) leading to improved sub-threshold swing and Drain-Induced Barrier Lowering (DIBL), and minimum Random Dopant Fluctuation (RDF), thanks to the undoped channel. This ensures lowest Vt variation [4,5], improves performance at lower Vdd as well as improves SRAM and analog mismatch and analog gain, allowing superior digital/analog co-integration [6].

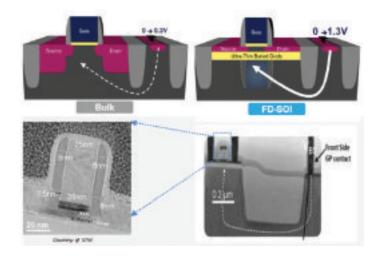

UTBB FD-SOI devices combine the advantage of tuning the front gate and back gate work function [4] as well as enabling effective back bias capabilities for multi-Vt options (**FIGURE 3**). The back bias capability is a unique feature that enables Vt modulation for better trade-off of power and performance and can be effectively applied in a static or dynamic mode. Moreover, UTBB FD-SOI back bias capabilities show no degradation with scaling and offer a wider range of biasing versus bulk at no area penalty [5].

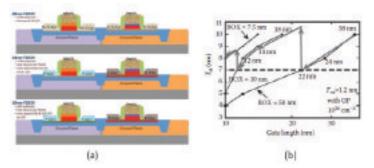

UTBB FD-SOI is a scalable technology supporting at least three nodes; 28nm, 14nm and 10nm (**FIGURE 4A**). The technology satisfies density/area, performance and power saving requirements without a disruptive change in device architecture and integration. Today, available foundry offerings demonstrate competitive performance at 28 & 22nm [1,7] and the technology is proven down to 10nm [8]. Scaling requires thinner SOI and BOX. In order to alleviate the constraints on SOI film thickness reduction, a scaling sequence

**FIGURE 2.** Soitec's RF-SOI leadership from ideas to high volume manufacturing.

**FIGURE 3.** UTBB FD-SOI with Back Bias (Courtesy of ST Microlectronics).

**FIGURE 4.** (a) UTBB FD-SOI Device integration supporting three nodes (11) (b) SOI/BOX thickness scaling ensuring a DIBL of 100 mV/V or below down to 7 nm node [9].

based on different BOX layer thickness was proposed, **FIGURE 4B** [9]. SOI substrates with 25nm BOX are already in production and 10 nm BOX has been demonstrated. Furthermore, the substrate roadmap beyond 14nm includes substrate strain engineering providing the advantage of enhancing the carrier mobility independent of device pitch. This includes strained silicon directly on insulator (SSOI) or strained SiGe-On-Insulator (SGOI) [10].

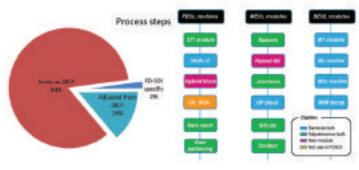

FD-SOI devices are planar devices that are fully

compatible with mainstream CMOS processing, designs and EDA tools, providing a faster time to market solution. In addition to fully leveraging conventional CMOS processes, FD-SOI process integration is simpler than bulk (**FIGURE 5**) [1, 12]. FD-SOI process saves several masks and process steps typically included for Vt tuning and for the integration of uniaxial stressors needed to boost performance in planar and FinFET bulk [13, 14]. Even with the drastically increasing lithography cost, such process simplifications more than compensate for the SOI substrate cost, resulting in a lower overall processed wafer cost [11].

While the vertical FinFET device features excellent gate control and high density/performance per area, it also requires a disruptive change in process and design resulting in higher cost and longer time to market. For applications that require the ultimate performance/ digital integration and large die size, vertical FinFETs are a good solution. For other applications that cannot afford the FinFET solution, such as cost sensitive low-mid end mobile consumer applications, FD-SOI is a great

**FIGURE 5.** 28nm FD-SOI vs. 28LP process (courtesy of ST Microelectronics).

candidate for providing low power/high performance and more analog integration capabilities with the least process and design disruption for low cost and fast time to market. Furthermore, FD-SOI devices with back bias can operate at voltages as low as 0.35V [15,16] without area and costly design penalties making them excellent candidates for Ultra-Low Power (ULP) applications. FD-SOI devices consume less energy than bulk at the MEP (Minimum Energy Point) and maintain the smallest energy per cycle with higher operating frequency across the whole Vdd range [17, 18]. This makes UTBB FD-SOI

technology a very attractive option for enabling ULP cost sensitive IoT applications.

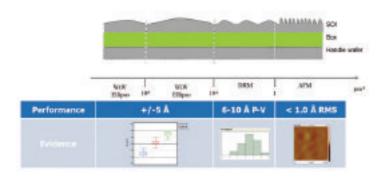

#### Smart Cut<sup>™</sup> enabling Å uniformity for Vt variability control

Optimization of the conventional Smart Cut process is essential for delivering ultra-thin SOI and BOX with well controlled wafer-to-wafer and within-wafer uniformity (FIGURE 6). The Smart Cut unique uniformity control relies on several key aspects of the process [19]: (a) A highly uniform thermal oxidation of a donor wafer

to form the BOX (b) A conformal hydrogen implant through the oxide to define the separation plane in the Silicon (c) A high temperature anneal to eliminate the SOI roughness while keeping excellent on-wafer SOI uniformity (20).

Developing an efficient smoothing process to eliminate the Si roughness

is critical for ensuring low transistor Vt variability. This requires Si thickness monitoring across the entire range of the spatial frequency. As existing ellipsometry and AFM characterizations are necessary but not sufficient, Soitec developed Differential Reflective Microscopy (DRM) to address the 100um scale SOI roughness. Consequently, bridging the gap between ellipsometry and AFM and providing a complete picture of surface roughness crucial for controlling Vt variations at the transistors level (FIGURE 7).

As the FD-SOI substrate plays a key role in defining the device structure, substrate local and global thickness

FIGURE 7. SOI layer thickness control.

FIGURE 6. The Smart Cut process.

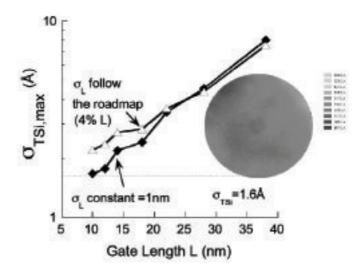

control is very important. This is especially true for UTBB FD-SOI devices, where the BOX thickness affects the efficiency of Vt tuning through back biasing, and the channel thickness uniformity and roughness influence the electrostatics of the device and Vt variation respectively. Today, Soitec guarantees volume production of SOI 12nm ±5Å and BOX 25nm ±10Å (6 sigma value, all sites, all wafers). When benchmarking variability; planar FD-SOI exhibits the best performance compared to Bulk technologies [4, 5]. Global variability is also reduced and maximum TSi dispersion (oTSi,max) obtained on 300mm wafers

is already satisfying the objective for Vt variability for advanced technology nodes [4].

#### **High resistivity SOI** substrates

The rapid adoption of new wireless standards and the increasing demand for data bandwidth requires RF IC designers to develop devices

with higher levels of integration, meeting more and more stringent specification levels. The engineered substrates on which those devices are manufactured play a major role in achieving that level of performance. The improved high frequency performance of CMOS with process shrinks, and the availability of CMOS foundry technologies on 200 or 300mm substrates has made it possible

FIGURE 8. Silicon uniformity requirements to meet ITRS variability roadmap [4].

to have high volume fabrication of integrated Si based RF systems, including high quality passive devices [21,22] and RF switches and power amplifiers on SOI substrates [23]. Historically, switches and power amplifiers were built on gallium arsenide (GaAs) substrates. Since 2008, RF-SOI has progressively displaced GaAs and silicon-onsapphire technologies by offering the best cost, area and performance for RF switches, and thus becoming the mainstream technology solution adopted by the majority of RF foundries [24].

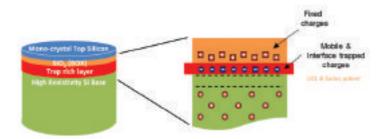

#### **Gen 2 HR-SOI engineered substrates**

Typical SOI substrates do not have thick enough BOX to prevent the electrical field from diffusing into the substrate, inducing high-frequency signal losses, non-linearity and crosstalk which are detrimental to RF performance. To improve the insertion loss, harmonic distortion and isolation performance required for switches, the bulk base substrate of an SOI substrate was replaced by a high-resistivity base substrate known as Gen 1 HR-SOI. The adoption of Gen 1 HR-SOI wafers for RF applications has allowed monolithic integration of RF FEM, leading to smaller

FIGURE 9. Gen 2 HR-SOI Substrate.

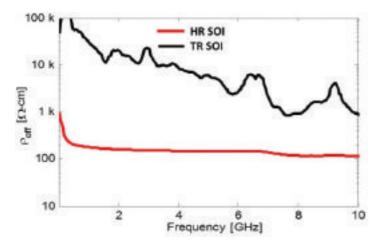

**FIGURE 10.** Measured effective resistivity of Gen 1 HR-SOI and trap-rich Gen 2 HR-SOI (TRSOI). Both use 10 kOhm.cm nominal resistivity handle Si substrate [25]. size, better reliability, improved performance and lower system cost [25, 26]. While first generation substrates are well suited for 2G and 3G applications, they suffer from the a parasitic surface conduction (PSC) layer induced under the BOX due to fixed oxide charges which attract free carriers near the Si/SiO2 interface. This drastically reduces the substrate effective resistivity by more than one order of magnitude, limiting the substrate capability in meeting the next step in performance for LTE advanced standards (**FIGURE 9**).

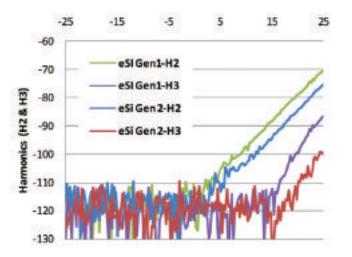

To address this intrinsic limitation, Soitec and Université Catholique de Louvain (UCL) developed a second generation (Gen 2) HR-SOI substrate with improved effective resistivity as high as 10KOhm.cm (**FIGURE 10**). This was achieved by adding a trap-rich layer underneath the buried oxide to freeze the PSC. These traps originate from the grain boundaries of a thin polysilicon layer added between the BOX and high resistivity substrate [27]. The high resistivity characteristics of Gen 2 HR-SOI substrates are conserved after CMOS processing, enabling very low RF insertion loss (< 0.15 dB/mm at 1 GHz), low harmonic

### Precise Processing.... It's Our Passion.

#### **Providing Ideal Process Environments with:**

Silane Vapor Deposition Systems Vacuum Bake/Vapor Prime Ovens High Temperature Vacuum Cure Ovens Plasma Clean Systems Plasma Strip Systems

For more information, visit www.yieldengineering.com or call 925-373-8353

**FIGURE 11.** (a) Measured crosstalk comparing Gen 2 HR-SOI (TR SOI), Gen 1 HR-SOI and quartz [25]. (b) Measured harmonic distortion along a CPW line, on standard SOI (~ 10ohm.cm) and Gen 1 HR-SOI (~ 1 kOhm.cm) and Gen 2 HR-SOI (TR-SOI) (~ 10 kOhm.cm).

**FIGURE 12.** Harmonic two and three measured on CPW on commercially available versions of Gen 2 HR-SOI (eSi) substrates.

**FIGURE 13.** Gen 2 HR-SOI (eSi) substrates, advantages vs Gen 1 HR-SOI substrate.

distortion (-40dB) along coplanar waveguide (CPW) transmission lines, and purely capacitive crosstalk close to quartz substrates (**FIGURE 11**). It was further demonstrated that the presence of a trapping layer does not alter the DC or RF behavior of SOI MOS transistors [28]. With second generation HR-SOI products, RF IC performance is further advanced meeting more stringent losses, coupling and non-linearity specifications (**FIGURE 12**) [25].

#### TABLE 1. Performance / Cost elements for substratedriven advantages.

| Segment         | Performance contribution                                                             | Cost Benefits                                              |

|-----------------|--------------------------------------------------------------------------------------|------------------------------------------------------------|

| Photonics       | SOI and double SOI layers to guide light                                             | Silicon integration and 300mm processing                   |

| FinFET          | High mobility layers<br>integration onto silicon,<br>low TDD                         | Decoupling material<br>epitaxy and device<br>optimization. |

| lmage<br>sensor | Antireflective layers<br>integrated in SOI stack<br>to be front after BSI<br>process | Simplification of BSI processing                           |

Because the trap-rich layer in Gen 2 HR-SOI substrates is integrated at the substrate level, additional process steps and consequently more conservative design rules are no longer needed, leading to a more cost effective process and a possible smaller die area per function. Gen 2 HR-SOI substrates now enable RF designers to add diverse on-chip functions such as switches, power amplifiers and antenna tuners with excellent RF isolation, good insertion loss and better signal integrity at lower cost than traditional technologies (FIGURE 13). It also brings clear benefits for the integration of passive elements, such as high quality factor spiral inductors [29], tunable MEMS capacitors [30], as well as reducing the substrate noise between devices integrated on the same chip. Beyond performance, RF-SOI offers a unique advantage to further reduce board area by integrating all FEM devices on the same die [3].

In addition to innovation at the substrate level, Soitec developed the characterization needed to predict the RF Harmonic Quality Factor (HQF) at the substrate level and before device/circuit manufacturing. The characterization method is based on spreading resistance profiling (SRP), which can predict the 2nd harmonic distortion (HD2) performance of a coplanar waveguide (**FIGURE 14**). This essential metrology step is used today throughout the Soitec product line to ensure Gen 2 HR-SOI SOI substrates provide the expected RF performance at the device level.

#### New substrates for new collaborations

As demonstrated, UTBB FDSOI and Gen 2 HR-SOI substrates are well positioned to address ULP IoT and mobile connectivity applications that will respectively require drastic power reduction and higher frequency bands at very low cost. Combining advanced CMOS

**FIGURE 14.** Harmonic Quality Factor (HQF) methodology.

process capabilities with the demonstrated benefit of engineered SOI substrates is paving the way for digital and RF integration for next generation cost sensitive integrated ULP mobile connected devices.

Furthermore, there are multiple examples where innovative substrate engineering can address roadmap challenges, enable further integration; provide differentiation in final product at a more efficient cost and footprint. Some examples of different application segments include: Photonics, Imaging sensors, advanced FinFET (**TABLE 1**).

Looking beyond a wafer and an application, entering the substrate era requires critical partnerships across the entire ecosystem. This includes having an augmented collaboration along the value and supply chain, covering collaborations with material, equipment and substrate suppliers as well as collaborations with foundries, IDMs and fabless companies. Soitec greatly supports this model and believes in establishing strong collaborations to seed future critical innovations.

#### Conclusion

Engineered SOI substrates are now a mainstream option for the semiconductor industry adopted by several foundries. UTBB FD-SOI substrates enable planar fully depleted devices with full back bias capability to extend Moore's Law at 28nm and beyond providing excellent power/performance/cost benefits. Gen 2 HR-SOI substrates enable FEM integration and higher linearity and isolation meeting stringent performance requirements for advanced standards at an improved cost. Combining advanced CMOS process capabilities with the demonstrated benefit of engineered SOI substrates is paving the way for digital and RF integration for next generation cost sensitive integrated ULP mobile connected devices. As such, engineered SOI substrates are well positioned to serve future integrated IoT applications.

#### **Acknowledgement**

The authors would like to thank Bich-Yen Nguyen and Eric Desbonnets for their valuable contribution and constructive discussions.

#### References

- The International Telecommunication Union & Ericsson (2014)

- Yongjoo Jeon, 2015 FD-SOI and RF-SOI forum, http://www. soiconsortium.org/fully-depleted-soi/presentations/january-2015, Tokyo (2015)

- 3. Soitec, White paper on RF substrates, http://www.soitec. com/pdf/Soitec\_RF-SOI\_Substrates\_WP.pdf (2015)

- 4. O. Weber et.al., IEDM, p.1-4, (2008)

- 5. L. Grenouillet et. al., IEDM, p.3.6.1-3.6.4, (2012)

- 6. S. Le Tual et. al., ISSCC, p. 32-383, (2014)

- 7. M. Mendicino, S3S conference, http://semiengineering. com/time-to-look-at-soi-again/ (2014)

- 8. Qing et. al., IEDM, p. 9.1.1 9.1.4, (2014)

- 9. O. Faynot et. al., IEDM, p. 3.2.1-3.2.4. 6-8, (2010)

- 10. W. Schwarzenbach et al., ICICDT, p. 1-4, (2012)

- 11. Nguyen, et. al., Advanced Substrate News, (2014)

- 12. P. Magashak et. al., DAC (2014)

- J. Hartmann, FD-SOI Tech Symposium, http://www.soiconsortium.org/fully-depleted-soi/presentations/december-2012/ (2012)

- 14. P. Flatresse, S3S Conference short course, Monterey, 2013

- 15. P. Flatresse, ISSCC, p. 424-425, (2013)

- 16. H. Makiyama et. al, IEDM, p. 33.2.1 33.2.4, 2013

- 17. Mäkipää & Billiot, IEE 2013

- 18. N. Sugii et. al, J. Low Power Electron. Appl., 4, 65-76, (2014)

- 19. W. Schwarzenbach et al., ECS Trans., 45, p. 227 (2012)

- 20. W. Schwarzenbach et al., ECS Trans., 53, p. 39 (2013)

- C. Didier, White Paper :RF-SOI Wafer Characterization, Soitec (2015)

- 22. J.-P. Raskin et al., IEEE Trans. on Electron Devices, 44, p. 2252 (1997)

- 23. A. Larie et. al, ISSCC, p.48-50, 2015

- 24. Yole Développement: RF Filters, PAs, Antenna Switches & Tunability for Cellular Handsets, (2014)

- 25. J. Le Meil, et. al., VSLITSA, (2015)

- 26. J.-P. Raskin et. al., IEEE Trans Electron Devices, v.44, #12, p. 2252-2261, (1997)

- 27. D. Lederer and J.-P. Raskin, Solid-State Electronics, 47 (11), p. 1927 (2003)

- 28. K. Ben Ali et. al, IEEE Trans. Electron Devices, v. 61,.#3, p. 722-728, (2014)

- 29. F. Gianesello et. al. SOI Conference, p. 119-120 , 2007

- 30. Y. Shim, IEEE MWCL, v. 23, # 12, p. 632-634, (2013) 🔶

#### A SPONSORED TECHNOLOGY PAPER

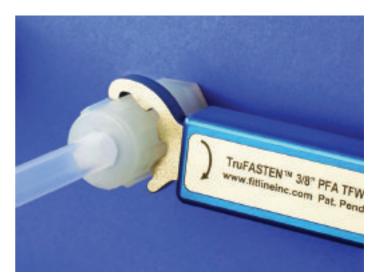

### Fit-LINE, Inc.'s Three Key Factors to Create Leak-Free Fitting Assemblies for Fluid Processing Applications

Can operational efficiency, a critical factor in the fluid processing industry, be achieved by focusing on the synergy of fitting components and assembly technology? Creating quality fittings and innovative assembly tools for the most demanding applications is part of Fit-LINE, Inc.'s mission. With extensive highpurity fluoropolymer expertise and in-depth research, testing and evaluation, Fit-LINE has isolated three critical variables to ensure leak-free fitting assemblies.

#### Variable #1 – Fitting Quality

The first variable is the quality of fittings. Producing fittings for the semiconductor, pharmaceutical, biotech, life science and ultra-pure water industries requires adherence to extremely stringent quality standards. Fit-LINE produces

PFA and PVDF fittings using high-quality resins and advanced injection-molding technology while holding industry-leading manufacturing tolerances.

#### Variable #2 - Tube Flaring Quality

The industry-accepted standard process of flaring tubing on-site using a hand-held heat gun can introduce a number of quality and training issues. To reduce rejection rates and time, the use of welldesigned, semi-automated hot tube flaring systems has proven to be an effective method to create standard, repeatable tube flares.

#### Variable #3 – Nut Tightening Methods

The final variable isolated by Fit-LINE in the pursuit of leak-free fitting assemblies is the method used to tighten assemblies to the required torque value. Hand tightening, a commonly-used practice, will not produce a consistent and accurate flared assembly seal. While the use of a torque wrench and nut adapter can provide more consistency, this combination is more complicated. Furthermore, overtightening the nut will affect the yield strength of the materials, which may result in leaks.

#### **One-Two-Three = Leak Free**

As a trusted engineering and design resource with a focus on problem solving, Fit-LINE works closely with customers to identify their needs and develop effective recommendations to create leak-free fitting assemblies and efficient manufacturing processes. To learn more about Fit-LINE's innovative high-purity fittings and assembly solutions, visit fitlineinc.com.

#### **DOWNLOAD THE COMPLETE TECHNOLOGY PAPER NOW!**

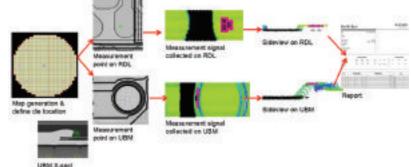

### Controlling Measurements of WLP in High Mix, High Volume Manufacturing

JIN YOU ZAO, STATS ChipPAC, Singapore, and JOHN THORNELL, Rudolph Technologies, Inc. Bloomington, MN, USA

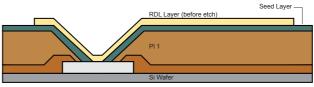

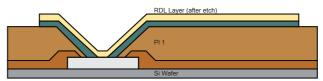

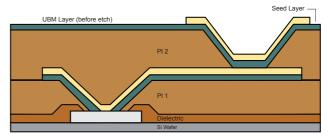

he demand for 4-mask layer Cu-plated wafer-level chip scale packaging (WLCSP) is increasing rapidly, and the current capability for in-line Cu height measurements is not suitable for high volume manufacturing (HVM). Thus, metrology constrains production capacity and limits volume ramp. Furthermore, the bottleneck created by a backlog of Cu step height measurements risks the timely detection of process drift and control. For a 4-mask layer Cu-plated WLCSP, accurate Cu step height measurement is required for both the Redistribution Layer (RDL) and Under Bump Metal (UBM) to ensure consistent delivery of good electrical performance and package reliability. This is especially important as WLCSP is moving towards finer feature size and pitch to meet increasing demand for smaller form factor.

In this article, the current measurement methodology is reviewed and an alternative measurement solution is derived. Full automation capability is delivered, yet the solution is reliable and versatile enough for high-mix production volumes. For quick-turn and high-mix volume manufacturing, accurate and fast in-line monitoring is crucial for timely process drift detection and control.

#### WLCSP in-line process measurement challenges

Contact-based profilometers are commonly used in wafer bumping for measurement of metal feature (RDL, UBM) thicknesses due to their ease of use and their low cost of ownership. However, the method of measurement is largely semi-automatic, and the identification of exact features and measurement locations is challenging.

(a) RDL-Seed layer on top of PI1

(b) RDL-Seed layer etch away from PI1

(c) UBM-Seed layer on top of Pl2

(d) UBM-Seed layer etch away from PI2

This becomes more acute in a high product-mix HVM environment, where measurement needs to be highly adaptive to different features on different products. As such, contact-based profilometers are limited to sampling

JIN YOU ZAO is with STATS ChipPAC in Singapore, and JOHN THORNELL is with Rudolph Technologies, Inc., in Bloomington, MN.

#### METROLOGY

measurements, and cannot perform 100% die inspection for process characterization.

It is thus desirable to have an automated feature measurement system capable of measuring features at precise locations on different topology on wafers in both sampling and full inspection modes.

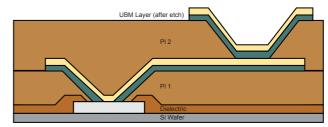

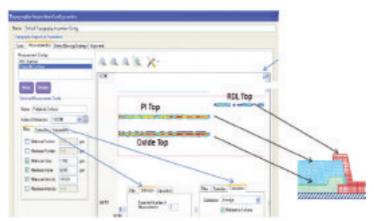

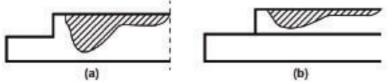

Specifically, feature measurement for wafer bumping comprises the following configurations (**FIGURE 1**):

- a) Cu RDL feature height measurement after Cu electroplating, where the sputtered metal seed layer to enable Cu plating remains on the first layer polyimide surface

- b) Final Cu RDL feature thickness measurement on first layer polyimide surface (PI-1) after the Cu seed layer

is etched away. Accurate final Cu RDL thickness measurement would require a good gauging of the PI-1 thickness underneath, especially if the topology is not flat.

- c) Cu UBM feature height measurement after Cu electroplating

- d) Final Cu UBM feature thickness measurement on second layer polyimide surface (PI-2)

The development for automated feature measurement proceeded in two phases: (Phase-1) Cu step height highlight measurement on reflective metal surfaces, and (Phase-2) Cu thickness and polyimide thickness measurement on non-reflective surfaces.

#### Phase-1: Auto Cu height measurement

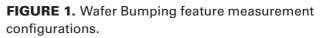

In this phase, the 3D inspection (3DI) system commonly used for solder bump height (typically greater than  $20\mu m$ ) measurement is explored for

auto Cu feature height measurement. Typical 3DI system such as Rudolph's WaferScanner, is equipped with the 3D triangulation laser sensor (**FIGURE 2**). Laser triangulation, where a laser is directed at the wafer surface at an angle of 45° and focused to a spot size of  $8\mu$ m, provides fast, precise measurements of bump height and coplanarity. Through a combination of laser-scanning and wafer movement, the beam scans the entire wafer surface. A lens collects the reflected/scattered laser light and focuses it on a position sensitive detector.

To enable Cu feature height measurement (typically in the range of 2-  $20\mu m$ ), the Triangular laser sensor was redesigned with a spot size of  $5\mu m$ , providing accuracy down to +/-0.2  $\mu m$ . The laser scanning algorithm was also improved from an array to a stagger method to improve the repeatability of scanning signals. As Cu feature height measurement is influenced by the surrounding topology, the ability to select any datum for measurement is critical. This was achieved through the integration of camera-based 2D inspection to the improved triangular laser sensor system using the developed datum selection

program. An automated height measurement report can be conveniently generated for further analysis through the program (**FIGURE 3**).

To verify the consistency of measurement performance, both the improved 3D triangulation laser sensor system and contact profilometer were used to

**FIGURE 3.** Selectable datum for Cu feature height measurement through camera-sensor integration.

measure feature Cu height on correlation device wafers. It confirmed that the automated 3D triangulation laser sensor system registers statistically similar Cu feature height mean compared to the manual contact profilometer, but required only one-fifth of the measurement time taken by the profilometer. Wafer bumping facilities which already have an existing pool of 3DI inspection tools can be modified to extend measurement application

**METROLOGY**

to Cu feature height without the need for excessive new investment.

#### Phase-2: Auto Cu/ PI thickness measurement

While a strong signal can be derived using the 3D triangular laser signal for Cu feature height measurement after electroplating (Fig. 1, a and c), it is more difficult to establish a stable signal for Cu feature height measurement after the reflective metal seed layer is etched away, and a reference datum needs to be established on the remaining transparent polyimide surface (Fig. 1, b and c). Several conventional methods exist for non-contact measurement of step heights, such as various confocal sensors, triangulation sensors, and scanning white light interferometry. These sensors typically have difficulty differentiating between reflections from the top and bottom surfaces of a layer, that is, layer thickness. This limitation comes from the depth of focus of the objective, which in turn depends on its numerical aperture (NA). Thus, for all these techniques, sensor performance is highly dependent on objective lens.

To overcome this technical constraint, it was necessary to develop a metrology system that can measure concurrently the transparent layer thickness as well as the metal feature step height above the surface of the transparent layer. This can be achieved through the integration of reflectometry and visible light interferometry principles [3]. In this method, the direct reflection from the transparent layer provides direct thickness measurement of the transparent material, while the interferometry captures topography (distance from the sensor), allowing the system to measure the thickness of the opaque metals by scanning over the edge of the feature. This technique is called the visible thickness and shape sensor (VT-SS) system.

In the following sections we provides further description of how the VT-SS system can be adapted for feature height/thickness measurement on varying topology and opaque materials. For this work, we used the Rudolph Technologies NSX® System configured with the VT-SS sensor.

#### Planar<sub>HDX</sub> High Throughput, Silicon Carbide, Planar Air-Bearing Stage

#### Optional Items

WaferMax Z Lift Stage

Custom Wafer Chucks

- Advanced silicon-carbide structure for high-dynamics and ultra-precise motion performance

- Speeds to 1.5 m/s and accelerations to 5 g

- Proprietary reactionmass design enables fast turnaround and move-andsettle times

- Active and passive isolation system options

- Encoder or laser interferometer feedback

- Linear motors with improved thermal management

- Advanced control solutions offer enhanced throughput

Ph: 412-963-7470 Email: sales@aerotech.com www.aerotech.com

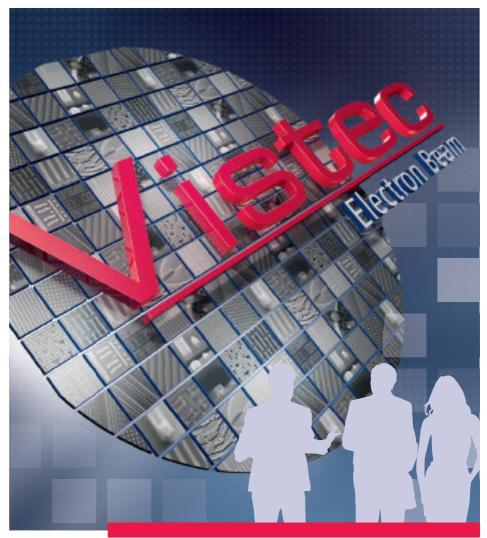

#### VT-SS system MSA study

Measurement system analysis (MSA) seeks to qualify a measurement system for use by quantifying its accuracy, precision and stability. VLSI standard wafers with  $8\mu$ m,  $24\mu$ m, and  $48\mu$ m step heights were used to assess gauge repeatability and reproducibility (GR&R) and accuracy of the VT-SS system, as well as system correlation on two different NSX Systems (tool matching) that were retrofitted with the VT-SS system.

#### A. Gauge repeatability and reproducibility

For the GR&R study, a total of ten parts on VLSI wafers (4 parts from  $8\mu$ m, 3 parts from  $24\mu$ m and  $48\mu$ m respectively) were measured three times each, including wafer loading and unloading.

**FIGURE 4** shows gauge R&R for VT-SS is 1.35% of tolerance and fully meeting AIAG standard of <10%.

#### B. Accuracy

Step height measurement accuracy was evaluated by means of bias and linearity analysis using the VLSI step height wafers. For this study, one location on each standard wafer was measured ten times and compared to the VLSI specification for the wafer.

Based on the studies in **FIGURE 5**, measurement with VT-SS system shows an average bias of 0.95%, and linearity error of 0.0059%, meeting the AIAG standard of <5%.

#### 50 45 40 35 Height (µm) 30 25 20 15 10 5 5 6 8 9 10 System A 0.014 0.012 0.010 Dev 0.008 0.006 Std 0.004 0.002 0 000 -0.002 5 6 2 3 Δ 7 8 q 10 System A Part within Equipment

Variability Chart for Height (µm)

#### Gauge R&R

| Variation     | % of                                                                                   |

|---------------|----------------------------------------------------------------------------------------|

| (5.15 StdDev) | Tolerance                                                                              |

| 0.027061      | 1.35                                                                                   |

| 0.000000      | 0.00                                                                                   |

| 0.000000      | 0.00                                                                                   |

| 0.000000      | 1.35                                                                                   |

| 0.027061      | 4508 2                                                                                 |

| 91.964971     | 4598.2                                                                                 |

| 91.964975     | 4598.2                                                                                 |

|               | (5.15 StdDev)<br>0.027061<br>0.000000<br>0.000000<br>0.000000<br>0.027061<br>91.964971 |

**FIGURE 4.** Measurement repeatability and reproducibility on ten different parts on VLSI wafers. The first four are from the  $8\mu$ m step height wafer, #5-#7 are from the  $24\mu$ m step height wafer, and #8-#10 are from the  $48\mu$ m step height wafer.