JULY 20<u>16</u>

Insights for Electronics Manufacturing

Fan-Out Wafer Level Packaging P. 22

Extending Tungsten Metallization

P. 26

Ensuring Safety in the Sub-fab P. 30

# Uniformity Control in Plasma Etch P16

# THIS IS EFFICIENCY

FR Series UHP single-stage pressure regulators

Provides precise control of process gas

Parker enables its partners in the semiconductor industry to cost-efficiently control process gases in downstream point-of-use applications with its new lines of FR 1000 and FR 1400 Series UHP regulators. This reflects Parker's commitment to engineering short- and long-term costs. **Call Parker's Veriflo Division at (510) 235-9590 to learn more or visit solutions.parker.com/semicon**

ENGINEERING YOUR SUCCESS.

©2016 Parker Hannifin Corporation SS-2-1

### **Solid State TECHNOLOGY**®

JULY 2016 VOL. 59 NO. 5

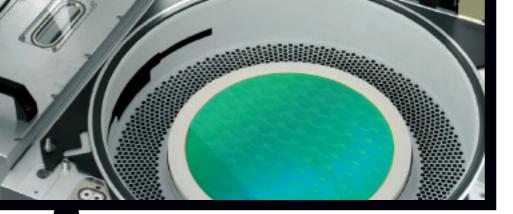

Etch chambers have been designed to produce similar plasma conditions on every location on the wafer to achieve uniform process results. Source: Lam Research

### FEATURES

#### **ETCHING** Evolution of across-wafer uniformity control in plasma etch A look at control of process uniformity across the wafer during plasma etch processes. *Stephen Hwang and Keren Kanarik, Lam Research Corporation, Fremont, CA*

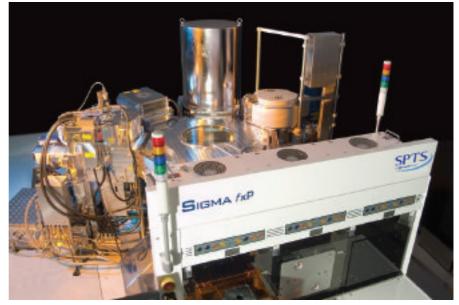

### FOWLP | Fan-Out Wafer Level Packaging (FOWLP): Breakthrough

#### advantages and surmountable challenges

New wafer processing technologies overcome FOWLP's technical hurdles, paving the way for a new generation of ultra compact, high I/O electronic devices. David Butler, SPTS Technologies, an Orbotech company, Yavne, Israel

### TUNGSTEN | Extending tungsten metallization for next-generation devices

Recent breakthroughs in materials engineering of low-resistance W barriers/liners and bulk fill are making it possible to extend W use to next-generation devices. Jonathan Bakke, Applied Materials, Santa Clara, CA

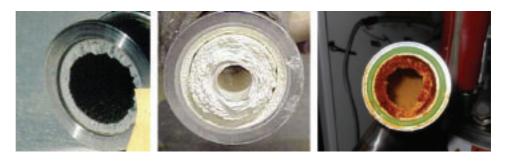

### **SAFETY** | Ensuring safety in the sub-fab

Problems frequently arise as a result of an incomplete or absent formal risk assessment when processes are modified or new materials introduced. Alan Ifould and Andrew Chambers, Edwards, North Somerset, UK

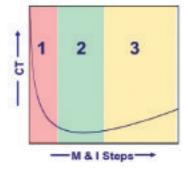

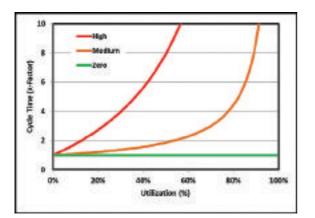

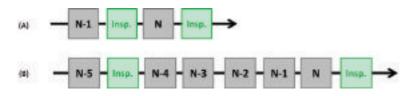

### PROCESS WATCH | Process control and production cycle time

Having more process control points will not immediately change the number of excursions in a fab but it will immediately improve the efficiency with which the fab reacts to them. By Douglas G. Sutherland and David W. Price, KLA-Tencor, Milpitas, CA

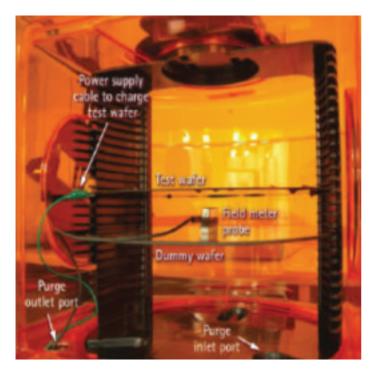

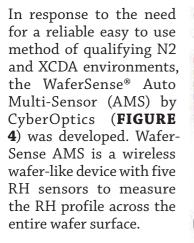

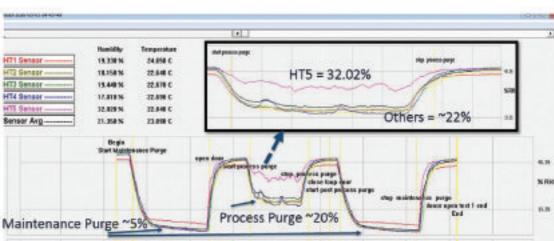

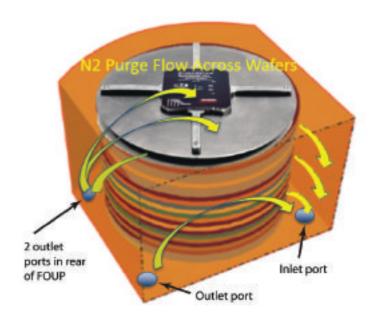

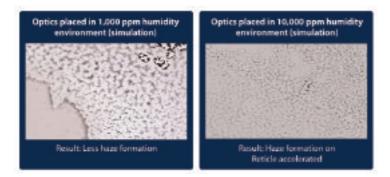

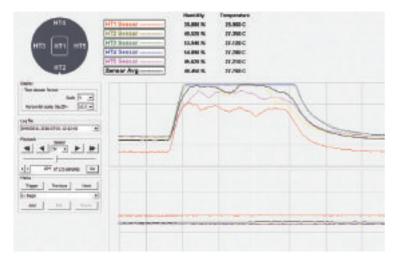

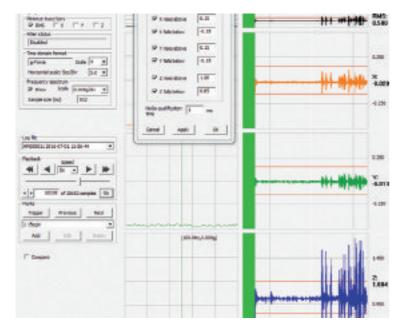

#### **MEASUREMENT** Advancements in RH measurement in wafer and reticle environments

A wireless wafer-like humidity sensor can simultaneously measure RH across the wafer and in critical processes Allyn Jackson, CyberOptics Corp., Minneapolis, MN

45

**SEMICON WEST** | Changing markets drive smarter manufacturing by IC sector A day-long forum will be held at SEMICON West on the future of smart manufacturing in the semiconductor supply chain. *Paula Doe, SEMI, San Jose, CA*

### COLUMNS

- 2 Editorial HITRS roadmap aims to integrate photonics and CMOS, Pete Singer, Editor-in-Chief

- **12 Packaging** X-Celeprint and RTI propose FOWLP free of mold compound, *Phil Garrou, Contributing Editor*

- **13 Semiconductors** Applied Materials releases selective etch tool, *Ed Korczynski, Sr. Technical Editor*

- **48** Industry Forum Time to uncover the process mystery for IC designs, Dr. Zhihong Liu, Chairman and CEO, ProPlus Design Solutions

### DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 46 Ad Index

### editorial

# HITRS roadmap aims to integrate photonics

A new roadmap, the Heterogeneous Integration Technology Roadmap for Semiconductors (HITRS), aims to integrate fast optical communication made possible with photonic devices with the digital crunching capabilities of CMOS.

The roadmap, announced publicly for the first time at The ConFab in June, is sponsored by IEEE Components, Packaging and Manufacturing Technology Society (CPMT), SEMI and the IEEE Electron Devices Society (EDS).

Speaking at The ConFab, Bill Bottoms, chairman and CEO of 3MT Solutions, said there were four significant issues driving change in the electronics industry that in turn drove the need for the HITRS roadmap: 1) The approaching end of Moore's Law scaling of CMOS, 2) Migration of data, logic and applications to the Cloud, 3) The rise of the internet of things, and 4) Consumerization of data and data access.

"CMOS scaling is reaching the end of its economic viability and, for several applications, it has already arrived. At the same time, we have migration of data, logic and applications to the cloud. That's placing enormous pressures on the capacity of the network that can't be met with what we're doing today, and we have the rise of the Internet of Things," he said. The consumerization of data and data access is something that people haven't focused on at all. "If we are not successful in doing that, the rate of growth and economic viability of our industry is going to be threatened," Bottoms said.

These four driving forces present requirements that cannot be satisfied through scaling CMOS. "We have to have lower power, lower

latency, lower cost with higher performance every time we bring out a new product or it won't be successful," Bottoms said. "How do we do that? The only vector that's available to us today is to bring all of the electronics much closer together and then the distance between those system nodes has to be connected with photonics so that it operates at the speed of light and doesn't consume much power. The only way to do this is to use heterogeneous integration and to incorporate 3D complex System-in-Package (SiP) architectures.

The HITRS is focused on exactly that, including integrating single-chip and multichip packaging (including substrates); integrated photonics, integrated power devices, MEMS, RF and analog mixed signal, and plasmonics. "Plasmonics have the ability to confine photonic energy to a space much smaller than wavelength," Bottoms said. More information on the HITRS can be found at: http://cpmt.ieee.org/technology/ heterogeneous-integration-roadmap.html

Bottoms said much of the technology exists today at the component level, but the challenge lies in integration. He noted today's capabilities include Interconnection (flip-chip and wire bond), antenna, molding, SMT (passives, components, connectors), passives/ integrated passive devices, wafer pumping/WLP, photonics layer, embedded technology, die/package stacking and mechanical assembly (laser welding, flex bending).

"We have a large number of components, all of which have been built, proven, characterized and in no case have we yet integrated them all. We've integrated more and more of them, and we expect to accelerate that in the next few years," he said.

### -Pete Singer, Editor-in-Chief

Pete Singer, Editor-in-Chief Ph: 978.470.1806, psinger@extensionmedia.com

Shannon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor, edk@extensionmedia.com

Jeff Dorsch, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design CREATIVE/PRODUCTION/ONLINE LS Jerrett, Production Traffic Coordinator Nicky Jacobson, Senior Graphic Designer Simone Bradley, Graphic Designer Slava Dotsenko, Senior Web Developer Jon Franke, Media Coordinator

MARKETING/CIRCULATION Jenna Johnson, jjohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridlev@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, Business Development msterling@extensionmedia.com

JULY 2016 VOL. 59 NO. 4 • Solid State Technology ©2016 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmaii: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343. (8 am – 5 pm, PST).

#### For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2016 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

### HEIDENHAIN – expanding horizons in semiconductor fabrication

- Repeatability ±0.001 µm (1 nm) @90 m/min

- 450 mm ready

- Ideal for ultra-high-precision positioning subassemblies

In the world of ultra-precise wafer lithography and inspection, HEIDENHAIN's depth of knowledge gives machine builders the ultimate competitive advantage – access to next-generation R&D that's deployable today. Case in point: our high precision LIP 400 linear and ROP 8080 angle encoders boost speed, repeatability and yield without sacrificing accuracy.

For an inside look at what's coming tomorrow contact us today. 1-847-490-1191 www.HEIDENHAIN.us

Come see us at SEMICON WEST B00TH #1809

HEIDENHAIN Angle Encoder ROP 8080

HEIDENHAIN Linear Encoder LIP 400

HEIDENHAIN Linear Encoder LIP 400

# Online@www.solid-state.com

### **Web Exclusives**

### An interview with Dr. Dongkai Shangguan

Dr. Dongkai Shangguan is currently the Chief Marketing Officer of STATS ChipPAC. Previously, Dongkai served as the founding CEO of the National Center for Advanced Packaging Co., Ltd., worked for 10 years at Ford Motor Company in various technical and management functions, and for 11 years at Flextronics as Corporate Vice President of Global Advanced Technology.

http://bit.ly/1timOOS

### More change for the chip industry

As if scaling to 7nm geometries and going vertical with FinFETs, TSVs and other emerging technologies wasn't challenge enough, the emerging market for connected smart devices will bring more changes to the semiconductor sector. And then there's 3D printing looming in the wings.

http://bit.ly/1JN1Tav

### Changing markets drive smarter manufacturing by IC sector

The changing market for ICs means the end of business as usual for the greater semiconductor supply chain. Smarter use of data analytics looks like a key strategy to get new products more quickly into high yield production at improved margins. http://bit.ly/1sEFUhw

### ASMC 2016 Conference has highest attendance ever; Chipworks achieves twelfth paper

ASMC is an annual conference focused on the manufacturing of semiconductor devices; in this it differs from other conferences, since the emphasis is on what goes on in the wafer fab, not the R&D labs, and the papers are not research papers – some are better described as "tales from the fab"! After all, it's the nitty-gritty of manufacturing in the fab that gets the chips out of the door, and this meeting discusses the work that pushes the yield and volumes up and keeps them there.

### http://bit.ly/28VWSiJ

### Insights from the Leading Edge: Samsung Electro-Mechanics enters FOWLP packaging market

Samsung Electronics System LSI and Samsung Electro-Mechanics will join forces to staff the project and launch the business. They will transform current LCD assembly lines in Cheonnan KR into IC packaging lines. It is unclear whether they have developed full panel processing capability, which many packaging OSATS have been trying to accomplish, or they will work in smaller formats.

http://bit.ly/28QQux0

### Latest on EUVL development to be discussed in EUVL Workshop in Berkeley

This year's 2016 EUVL Workshop is being held in Berkeley, CA, organized in cooperation with CXRO. With keynotes from Intel, GlobalFoundries and ASML, along with 45 speakers and about 50 papers, we expect to hear a good bit of new information on these topics and stimulating discussion of R&D topics.

http://bit.ly/28QQEEk

### **Contact resistance and its role in limiting transistor performance**

In logic devices, contacts and local interconnects form the critical electrical pathways between the transistors and the rest of the circuit. Low resistivity is therefore crucial for robust and reliable device performance. Consequently, lowresistivity CVD tungsten (W) has historically been used for logic contact and local interconnect fill. (From SemiMD.com)

http://bit.ly/28P3nn9

### Eloquent executives ecosystem expositions

With dimensional scaling reaching economic limits, each company in the IC fab industry must rely upon trusted connections with customers and suppliers to know which way to go, and the only way to gain trusted connections is through attending live events. Fortunately, whether you are an executive, and engineer, or an investor, there is at least one must-attend event happening these days to keep you informed. (From SemiMD.com)

http://bit.ly/28OsU3A

# Delivering Real-world Solutions

Today's lithography systems provide overlay accuracy and throughput capabilities far beyond what was previously thought possible. However, it is real-world, on-product performance that is vital to chipmakers.

Nikon combines superior stepper and scanner technology with innovative software solutions to deliver exceptional manufacturing performance and productivity—now and for the future.

Nikon. Delivering Real-world Solutions.

See Nikon at SEMICON West 2016 - Visit booth 1705 in South Hall to learn about the latest Nikon semiconductor lithography solutions and MEMS exposure systems.

www.nikonprecision.com

Please send news articles to sdavis@extensionmedia.com

### worldnews

**USA - Amkor Technology** received Qualcomm Technologies' 2015 Supplier of the Year award.

ASIA - GLOBALFOUNDRIES announced plans to expand presence in China with 300mm fab in Chongqing.

**EUROPE - EV Group** scored its fourth consecutive triple crown win in the annual VLSIresearch customer satisfaction survey.

USA - Ultratech, Inc. announced its LXA melt laser annealing technology enabled the world's lowest contact resistivity for finFETs.

**ASIA** - **Samsung** introduced a new line-up of LED components for automotive lighting, featuring chip-scale packaging.

**EUROPE – Leti** teams have demonstrated how Fully Depleted Silicon on Insulator (FDSOI) technology can be scaled downwards and how the experience in thin-film engineering built on FDSOI development can be harnessed for innovative architectures and computing paradigms.

**USA** - **FEI** launched three new tools for next-generation semiconductor manufacturing.

**EUROPE** - **Soitec** receives Best Quality Award from NXP Semiconductors.

USA - Electronic Fluorocarbons began construction of manufacturing facility in Pennsylvania.

*EUROPE* – **ams** signed an agreement to acquire Cambridge CMOS Sensors Ltd (CCMOSS).

**ASIA** – Samco held a completion ceremony for its second production center on June 17.

# Equipment spending up: 19 new fabs and lines to start construction

This month, SEMI announced that 19 new fabs and lines are forecasted to begin construction in 2016 and 2017, according to the latest update of the SEMI World Fab Forecast report. While semiconductor fab equipment spending is off to a slow start in 2016, it is expected to gain momentum through the end of the year. For 2016, 1.5 percent

| 2016                                                     | 2017                                                                                                                      |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1 Analog                                                 | 1 Foundry                                                                                                                 |

| 1 Memory<br>1 MEMS (200mm)<br>1 Foundry<br>1 LED (100mm) | 1 Memory<br>1 MEMS (200mm)<br>3 Foundry<br>1 Power (200mm)                                                                |

| 1 Power                                                  |                                                                                                                           |

|                                                          | 1 Memory                                                                                                                  |

| 1 Memory                                                 |                                                                                                                           |

| 1 LED (150mm)                                            | 1 Analog (200mm)                                                                                                          |

| 1 Foundry                                                | 1 LED (50mm)                                                                                                              |

| 210,000 wspm                                             | 330,000 wspm                                                                                                              |

|                                                          | 1 Analog<br>1 Memory<br>1 MEMS (200mm)<br>1 Foundry<br>1 LED (100mm)<br>1 Power<br>1 Memory<br>1 LED (150mm)<br>1 Foundry |

New Fabs & Lines Beginning Construction (2016 & 2017)

Source: World Fab Forecast report, June 2016, SEMI (www.semi.org)

growth over 2015 is expected while 13 percent growth is forecast in 2017.

Fab equipment spending—including new, secondary, and in-house—was down 2 percent in 2015. However, activity in the 3D NAND, 10nm Logic, and Foundry segments is expected to push equipment spending up to US\$36 billion in 2016, 1.5 percent over 2015, and to \$40.7 billion in 2017, up 13 percent. Equipment will be purchased for existing fabs, lines that are being converted to leading-edge technology, as well as equipment going into new fabs and lines that began construction in the prior year.

Table 1 shows the regions where new fabs and lines are expected to be built in 2016 and 2017. These projects have a probability of 60 percent or higher, according to SEMI's data. While some projects are already underway, others may be subject to delays or pushed into the following year. The SEMI World Fab Forecast report, published May 31, 2016, provides more details about the construction boom.

Breaking down the 19 projects by wafer size, 12 of the fabs and lines are for 300mm (12-inch), four for 200mm, and three LED fabs (150mm, 100mm, and 50mm). Not including LEDs, the potential installed capacity of all these fabs and lines is estimated at almost 210,000 wafer starts per month (in 300mm equivalents) for fabs beginning construction in 2016 and 330,000 wafer starts per month (in 300mm equivalents) for fabs beginning construction in 2017.

In addition to announced and planned new fabs and lines, SEMI's World Fab Forecast provides information about existing fabs and lines with associated construction spending, e.g. when a cleanroom is converted to a larger wafer size or a different product type.

In addition, the transition to leading-edge technologies (as we can see in planar technologies, but also in 3D technologies) creates a reduction in installed capacity within an existing fab. To compensate for this reduction, more conversions of older fabs may take place, but also additional new fabs and lines may begin construction.

### Tiny lasers enable faster, less powerhungry next-gen microprocessors

A group of scientists from Hong Kong University of Science and Technology; the University of California, Santa Barbara; Sandia National Laboratories and Harvard University were able to fabricate tiny lasers directly on silicon — a huge breakthrough for the semiconductor industry and well beyond.

For more than 30 years, the crystal lattice of silicon and of typical laser materials could not match up, making it impossible to integrate the two materials — until now.

As the group reports in Applied Physics Letters, from AIP Publishing, integrating subwavelength cavities — the essential building blocks of their tiny lasers — onto silicon enabled them to

Continued on page 9

### Long-term strategy pays off as TI maintains analog leadership

The 2015 analog market grew 2% to \$47.0 billion. Combined sales of general-purpose analog products (amplifiers/comparators, interface, power management, an signal conversion devices) increased 2% to \$19.1 billion and sales of application-specific analog devices also improved 2% to \$27.9 billion. Among analog IC products the market for signal conversion devices showed the largest increase in 2015, growing 14% to \$2.9 billion.

IC Insights' ranking of top analog IC suppliers for 2015 is shown in Figure 1. Collectively, these 10 companies accounted for 56% of global analog sales last year, down slightly from 57% in 2014. Among the top suppliers, nine had analog sales in excess of

Continued on page 10

### Aerotech Motion Solutions for Surface Measurement

### Planar<sub>DL</sub>

- Linear motor XY positioning stage

- Provides superior geometric performance in a low-profile package

### MPS75SLE

- Compact positioning stage with direct feedback

- Allows for precise positioning of measurement sensor

MPS75SLF

Planar

- Open-frame XY positioning stage

- Allows simultaneous access to both sides of workpiece

Ph: 412-963-7470 • Email: sales@aerotech.com • www.aerotech.com WORLD HEADQUARTERS: USA THE AMERICAS • EUROPE & MIDDLE EAST • ASIA-PACIFIC

### Expert motion solutions for surface measurement that include:

- Advanced 2D calibration available with Aerotech control system

- Excellent geometric characteristics

- Low CTE encoder substrate

- Integral cable management for clean, professional appearance

- High-accuracy Z-stage with linear encoder for sensor positioning

Add an Aerotech award-winning control system for a complete motion solution.

Contact an Aerotech Engineer today to discuss your application.

Dedicated to the Science of Motion

## **NEWS**cont

### Automotive semiconductor market grows slightly in 2015 while ranks shift

Despite slower growth for the automotive industry and exchange rate fluctuations, the automotive semiconductor market grew at a modest 0.2 percent year over year, reaching \$29 billion in 2015, according to IHS (NYSE: IHS), a global source of critical information and insight.

A flurry of mergers and acquisitions last year caused the competitive landscape to shift, including the merger of NXP and Freescale, which created the largest automotive semiconductor supplier in 2015 with a market share of 14.3 percent, IHS said. The acquisition of International Rectifier (IR) helped Infineon overtake Renesas to secure the second-ranked position, with a market share of 9.8 percent. Renesas slipped to third-ranked position in 2015, with a market share of 9.1 percent, followed by STMicroelectronics and Texas Instruments.

"The acquisition of Freescale by NXP created a powerhouse for the automotive market. NXP increased its strength in automotive infotainment systems, thanks to the robust double-digit growth of its i.MX processors," said Ahad Buksh, automotive semiconductor analyst for IHS Technology. "NXP's analog integrated circuits also grew by double digits, thanks to the increased penetration rate of keyless-entry systems and in-vehicle networking technologies."

NXP will now target the machine vision and sensor fusion markets with the S32V family of processors for autonomous functions, according to the IHS Automotive Semiconductor Intelligence Service Even on the radar front, NXP now has a broad portfolio of long- and mid-range silicon-germanium (SiGe) radar chips, as well as shortrange complementary metal-oxide semiconductor (CMOS) radar chips under development. "The fusion of magnetic sensors from NXP, with pressure and inertial sensors from Freescale, has created a significant sensor supplier," Buksh said.

The inclusion of IR, and a strong presence in advanced driver assistance systems (ADAS), hybrid electric vehicles and other growing applications helped Infineon grow 5.5 percent in 2015. Infineon's 77 gigahertz (GHz) radar system integrated circuit (RASIC) chip family strengthened its position in ADAS. Its 32-bit microcontroller (MCU) solutions, based on TriCore architectures, reinforced the company's position in the powertrain and chassis and safety domains.

The dollar-to-yen exchange rate worked against the revenue ranking for Renesas for the third consecutive year. A major share of Renesas business is with Japanese customers, which is primarily conducted in yen. Even though Renesas' automotive semiconductor revenue fell 12 percent, when measured in dollars, the revenue actually grew by about 1 percent in yen. Renesas' strength continues to be its MCU solutions, where the company is still the leading supplier globally. STMicroelectronics' automotive revenue declined 2 percent year over year; however, a larger part of the decline can be attributed to the lower exchange rate of the Euro against the U.S. dollar in 2015, which dropped 20 percent last year. STMicroelectronics' broadbased portfolio and its presence in every growing automotive domain of the market helped the company maintain its revenue as well as it did. Apart from securing multiple design wins with American and European automotive manufacturers, the company is also strengthening its relationships with Chinese auto manufacturers. Radio and navigation solutions from STMicroelectronics were installed in numerous new vehicle models in 2015.

Texas Instruments has thrived in the automotive semiconductor market for the fourth consecutive year. Year-over-year revenue increased by 16.6 percent in 2015. The company's success story is not based on any one particular vehicle domain. In fact, while all domains have enjoyed double-digit increases, infotainment, ADAS and hybrid-electric vehicles were the primary drivers of growth.

### Other suppliers making inroads in automotive

After the acquisition of CSR, Qualcomm rose from its 42nd ranking in year 2014, to become the 20th largest supplier of automotive semiconductors in 2015. Qualcomm has a strong presence in cellular baseband solutions, with its Snapdragon and Gobi processors; while CSR's strength lies in wireless application ICs — especially for Bluetooth and Wi-Fi. Qualcomm is now the sixth largest supplier of semiconductors in the infotainment domain.

Moving from 83rd position in 2011 to 37th in 2015, nVidia has used its experience, and its valuable partnership with Audi, to gain momentum in the automotive market. The non-safety critical status of the infotainment domain was a logical stepping stone to carve out a position in the automotive market, but now the company is also moving toward ADAS and other safety applications. The company has had particular success with its Tegra processors.

Due to the consolidation of Freescale, Osram entered the top-10 ranking of automotive suppliers for the first time in 2015. Osram is the global leader in automotive lighting and has enjoyed double-digit growth over the past three years, thanks to the increasing penetration of light-emitting diodes (LEDs) in new vehicles.

*Tiny lasers*, Continued from page 7

create and demonstrate highdensity on-chip light-emitting elements.

To do this, they first had to resolve silicon crystal lattice defects to a point where the cavities were essentially equivalent to those grown on lattice-matched gallium arsenide (GaAs) substrates. Nano-patterns created on silicon to confine the defects made the GaAs-on-silicon template nearly defect free and quantum confinement of electrons within quantum dots grown on this template made lasing possible.

The group was then able to use optical pumping, a process in which light, rather than electrical current, "pumps" electrons from a lower energy level in an atom or molecule to a higher level, to show that the devices work as lasers.

"Putting lasers on microprocessors boosts their capabilities and allows them to run at much lower powers, which is a big step toward photonics and electronics integration on the silicon platform," said professor Kei May Lau, Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology.

Traditionally, the lasers used for commercial applications are quite large — typically 1 mm x 1 mm. Smaller lasers tend to suffer from large mirror loss.

But the scientists were able to overcome this issue with

### **ELECTRONIC SPECIALTY GASES**

- ADVANCED. RELIABLE. CONSISTENT.

- PURITY AND INNOVATION

- ADVANCED MATERIALS

COMING SOON

NEW Plant Location: 3266 Bergey Road Hatfield, PA 19940

+508-435-7000 www.efgases.com

### **NEV/S**cont.

"tiny whispering gallery mode lasers — only 1 micron in diameter — that are 1,000 times shorter in length, and 1 million times smaller in area than those currently used," said Lau.

Whispering gallery mode lasers are considered an extremely attractive light source for on-chip optical communications, data processing and chemical sensing applications.

"Our lasers have very low threshold and match the sizes needed to integrate them onto a microprocessor," Lau pointed out. "And these tiny high-performance lasers can be grown directly on silicon wafers, which is what most integrated circuits (semiconductor chips) are fabricated with."

In terms of applications, the group's tiny lasers on silicon are ideally suited for high-speed data communications.

"Photonics is the most energy-efficient and cost-effective method to transmit large volumes of data over long distances. Until now, laser light sources for such applications were 'off chip' — missing — from the component," Lau explained. "Our work enables

### Leading Analog IC Suppliers (\$M)

| 2015<br>Rank | Company                   | 2014  | 2015  | %<br>Change | %<br>Marketshare |

|--------------|---------------------------|-------|-------|-------------|------------------|

| 1            | Texas Instruments         | 8,104 | 8,340 | 3%          | 18%              |

| 2            | Infineon                  | 2,770 | 2,885 | 4%          | 6%               |

| 3            | <b>Skyworks Solutions</b> | 2,570 | 2,700 | 5%          | 6%               |

| 4            | Analog Devices            | 2,615 | 2,665 | 2%          | 6%               |

| 5            | ST                        | 2,836 | 2,465 | -13%        | 5%               |

| 6            | Maxim                     | 2,035 | 1,960 | -4%         | 496              |

| 7            | NXP                       | 1,730 | 1,905 | 10%         | 4%               |

| 8            | Linear Technology         | 1,437 | 1,440 | 0%          | 3%               |

| 9            | ON Semi                   | 1,291 | 1,155 | -11%        | 2%               |

| 10           | Renesas                   | 910   | 805   | -12%        | 2%               |

Source: IC Insights, company reports

on-chip integration of lasers, an [indispensable] component, with other silicon photonics and microprocessors."

The researchers expect to see this technology emerge in the market within 10 years.

Next, the group is "working on electrically pumped lasers using standard microelectronics technology," Lau said.

### Long-term strategy, Continued from page 7

\$1.0 billion; five of these had sales in excess of \$2.0 billion. Only tenth-ranked Renesas fell short of the \$1.0 billion mark. With a 10% increase, NXP's analog sales outperformed the total analog market by the widest margin (Figure 1).

Texas Instruments was again the leading supplier of analog devices in 2015 with \$8.3 billion in sales, which was good for 18%marketshare. TI's analog sales slightly surpassed the combined revenue of the next three-largest analog suppliers, and represented 69% of its total semiconductor revenue last year. TI has always been a major player in analog, but beginning in 2009, it doubled down on its long-term efforts to dominate this market segment. That year, TI became the first company to manufacture analog devices on 300mm equipment. It purchased 300mm manufacturing tools from defunct Qimonda and transferred it to its existing fabs in Texas to build analog ICs. In 2010, TI acquired two wafer fabs operated by Spansion in Aizu-Wakamatsu, Japan, and a fully equipped 200mm fab in Chengdu, China from Cension Semiconductor Manufacturing. Both facilities were converted and immediately put to use making analog ICs. In April 2011, TI acquired National Semiconductor-its rival in many analog markets-for \$6.5 billion.

TI also strengthened its analog position by transitioning to 300mm manufacturing capacity at its newer RFAB and its older DMOS 6 fabs. Aside from boosting its analog manufacturing capacity, moving to 300mm wafer helped reduce total production costs by 40%, according to the company.

Other changes seen in the 2015 ranking include Infineon moving up one place to become the second-largest analog supplier and Skyworks Solutions moving up two spots to #3. ST slipped from #2 in 2014 to #5 in the 2015 ranking following its 13% decline in analog sales, which it attributed to soft equipment sales (computer, consumer, automotive, industrial) among its primary customers. Collectively, Infineon, NXP, and ST–Europe's three-largest IC suppliers—accounted for 15% analog marketshare last year.

Skyworks continues to enjoy solid analog sales due to design wins with smartphones providers around the world. Skyworks Solutions makes analog and mixed signal semiconductors for Apple, Samsung, and other suppliers of mobile devices. Many of Skyworks' power amplifier components are found in Apple's iPhone 6 models. It has been estimated that Skyworks supplies \$4 worth of content for every iPhone 6 handset.

###

# Medical Electronics Symposium 2016

**Multiple Track Topics Include:**

Track 1 - Designs, Components and Assembly for High-Density Medical Electronics Solutions

Track 2 - Next Generation Microelectronics for Changing Healthcare Markets

MARYLHURST UNIVERSITY

**Register Today at www.smta.org/medical**

### SEPTEMBER 14 & 15, 2015 • PORTLAND, OR

**REGISTER NOW**

Although highly focused in mobile markets, Skyworks plans to expand into the automotive, home, and wearable markets to develop its presence in applications linked to the Internet of Things. Analog ICs such as audio amplifiers, op amps, and analog switches are building blocks for creating wearable applications. Skyworks' wireless technology is used in General Electric healthcare equipment, and the company recently sealed a deal to supply high-performance filter solutions to Panasonic.

| Y2015<br>Rank | Company Name             | 2014 Revenue | 2015 Revenue | 2014<br>Market Share | 2015<br>Market Share | Growth (YoY) |

|---------------|--------------------------|--------------|--------------|----------------------|----------------------|--------------|

| 1             | NXP                      | 1861         | 4178         | 6.4%                 | 14.4%                | 124.5%       |

| 2             | Infinean<br>Technologies | 2702         | 2850         | 9.3%                 | 9.5%                 | 5.5%         |

| 3             | Renesas<br>Electronics   | 3032         | 2671         | 10.5%                | 9.2%                 | -11.9%       |

| 4             | STMoroelectronica        | 2144         | 2096         | 7.4%                 | 7.2%                 | -2.2%        |

| 5<br>6        | Texas Instruments        | 1605         | 1871         | 5.5%                 | 6.4%                 | 16.6%        |

| 6             | Robert Basch             | 1621         | 1478         | 5.6%                 | 5.7%                 | -8.8%        |

| 7             | ON Semiconductor         | 1000         | 1142         | 3.7%                 | 3.9%                 | 6.8%         |

| 8             | Micron Technology        | 706          | 661          | 2.4%                 | 2.3%                 | -6.4%        |

| 9             | Toshiba                  | 729          | 682          | 2,5%                 | 2.2%                 | -10.6%       |

| 10            | Osram                    | 568          | 646          | 2.0%                 | 2.2%                 | 13.7%        |

|               | Others                   | 12946        | 10785        | 44.7%                | 37.2%                | -18.7%       |

|               | Tetal                    | 29963        | 29030        | 100.0%               | 100.0%               | 0.2%         |

### Analog Devices' analog sales grew

2% last year. One of its key analog ICs is a device that enables 3D/Force Touch, a feature available on the Apple Watch, the latest iPhones, and new generations of the iPad, that uses tiny electrodes to distinguish between a light tap and a deep press to trigger contextually specific controls.

IC Insights forecasts the total analog market to grow 4% this year, reaching \$49.1 billion and then surpass the \$50.0 billion mark for the first time in 2017 as analog sales climb to an expected \$51.4 billion. From 2015 to 2020, the analog market is forecast to grow at a compound annual growth rate of 6%, one point higher than the total IC market.

### X-Celeprint and RTI propose FOWLP free of mold compound

PHIL GARROU, Contributing Editor

At the ECTC conference in May, in the "Advances in Fan Out Packaging" session, Matt Lueck of RTI International discussed the results of their joint program with X-Celeprint.

A common aspect to all fan-out packaging is the requirement to physically assemble devices into dispersed arrays, often called reconfigured wafers, which provides the real estate needed to fan-out. Devices made in sub-mm chip sizes can impose cost and performance challenges to FO-WLP using serial pick-and place assembly technologies. RTI and X-Celeprint joined forces to develop a fan out package for sub mm IC using the X-Celeprint massively parallel assembly technology called micro transfer-printing, which is well-suited for handling very thin and fragile devices.

In their micro transfer-printing technology a polymer layer is first applied to the substrate before the assembly process, and the devices are assembled in a face-up configuration. Following the formation of the reconfigured substrates, conventional redistribution layer (RDL) and solder ball processing was performed. Two different photo-imageable spin on dielectrics, HD4100 PI and Intervia 8023 epoxy, were used as the RDL dielectrics. The fan-out package contains no molding compound and is made using standard wafer-level packaging tools.

There are potential benefits from fan-out packaging strategies that do not require molding compound. The process described here does not suffer from the "die drift" that occurs during compression molded fan-out packaging which often requires special adaptive alignment techniques. It also does not suffer from the wafer and package warpage that can occur in molding compound based fan-out packages.

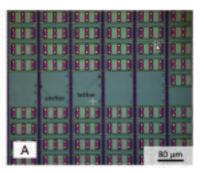

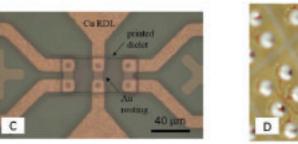

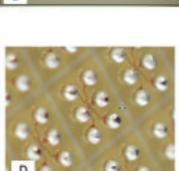

Micro-transfer printing was used to assemble reconfigured wafers of devices (80um x 40um chips with a redistribution metal and six contact pads), onto 200mm wafers. After assembly, they undergo a standard wafer level redistribution and bumping process. The final fan-out package pitch on the 200 mm wafer is 1.4mm x 1.0mm with six 250  $\mu$ m solder bumps. The fan-out packages were assembled and reflowed onto FR4 test boards.

The Figure shows (A) the chiplet source wafer after partial removal of chiplets with the elastomer stamp; (B) a completed fan out package before solder ball placement; (C) close-up of the interconnect to the chi pads; (D) Final FO-WLP. Initial yields are reported to be 97%.

Two PCB test vehicles populated with 60 die each were built for thermal cycle testing. The board level thermal cycle testing was run under -40°C to 125°C. None of the die showed more than 0.2 ohm change in average resistance. ◆

### Packaging

# Applied Materials releases selective etch tool

Applied Materials has disclosed commercial availability of new Selectra(TM) selective etch twin-chamber hardware for the company's high-volume manufacturing (HVM) Producer® platform. Using standard fluorine and chlorine gases already used in traditional Reactive Ion Etch (RIE) chambers, this new tool provides atomic-level precision in the selective removal of materials in 3D devices structures increasingly used for the most advanced silicon ICs. The tool is already in use at three customer fabs for finFET logic HVM, and at two memory fab customers, with a total of >350 chambers planned to have been shipped to many customers by the end of 2016.

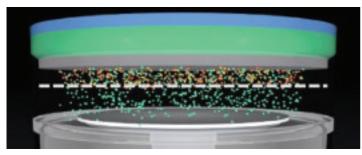

**FIGURE 1** shows a simplified cross-sectional schematic of the Selectra chamber, where the dashed white line indicates some manner of screening functionality so that "Ions are blocked, chemistry passes through" according to the company. In an exclusive interview with Solid State Technology, company representative refused to disclose any hardware details. "We are using typical chemistries that are used in the industry," explained Ajay Bhatnagar, managing director of Selective Removal Products for Applied Materials. "If there are specific new applications needed than we can use new chemistry. We have a lot of IP on how we filter ions and how we allow radicals to combine on the wafer to create selectivity."

**FIGURE 1:** Simplified cross-sectional schematic of a silicon wafer being etched by the neutral radicals downstream of the plasma in the Selectra chamber. (Source: Applied Materials)

From first principles we can assume that the ion filtering is accomplished with some manner of electrically-grounded metal screen. This etch technology accomplishes similar process results to Atomic Layer Etch (ALE) systems sold by Lam, while avoiding the need for specialized self-limiting chemistries and the accompanying chamber throughput reductions associated with pulsepurge process recipes.

### Semiconductors

"What we are doing is being able to control the amount of radicals coming

to the wafer surface and controlling the removal rates very uniformly across the wafer surface," asserted

ED KORCZYNSKI, Sr. Technical Editor

Bhatnagar. "If you have this level of atomic control then you don't need the self-limiting capability. Most of our customers are controlling process with time, so we don't need to use selflimiting chemistry." Applied Materials claims that this allows the Selectra tool to have higher relative productivity compared to an ALE tool.

Due to the intrinsic 2D resolutions limits of optical lithography, leading IC fabs now use multi-patterning (MP) litho flows where sacrificial thin-films must be removed to create the final desired layout. Due to litho limits and CMOS device scaling limits, 2D logic transistors are being replaced by 3D finFETs and eventually Gate-All-Around (GAA) horizontal nanowires (NW). Due to dielectric leakage at the atomic scale, 2D NAND memory is being replaced by 3D-NAND stacks. All of these advanced IC fab processes require the removal of atomic-scale materials with extreme selectivity to remaining materials, so the Selectra chamber is expected to be a future work-horse for the industry.

When the industry moves to GAA-NW transistors, alternating layers of Si and SiGe will be grown on the wafer surface, 2D patterned into fins, and then the sacrificial SiGe must be selectively etched to form 3D arrays of NW. The Selectra tools can etch the SiGe from alternating Si/SiGe stacks, with sharp Si corners after etch indicating excellent selectivity.

"One of the fundamental differences between this system and old downstream plasma ashers, is that it was designed to provide extreme selectivity to different materials," said Matt Cogorno, global product manager of Selective Removal Products for Applied Materials. "With this system we can provide silicon to titaniumnitride selectivity at 5000:1, or silicon to silicon-nitride selectivity at 2000:1. This is accomplished with the unique hardware architecture in the chamber combined with how we mix the chemistries. Also, there is no polymer formation in the etch process, so after etching there are no additional processing issues with the need for ashing and/or a wet-etch step to remove polymers."

Systems can also be used to provide dry cleaning and surface-preparation due to the extreme selectivity and damage-free material removal. 'You can control the removal rates," explained Cogorno. "You don't have ions on the wafer, but you can modulate the number of radicals coming down." For HVM of ICs with atomic-scale device structures, this new tool can widen process windows and reduce costs compared to both dry RIE and wet etching.

# ONYX: A New In-Line and Non-Destructive Hybrid Technology

By BENNY DONNER, RONI PERETZ and BRAD LAWRENCE, XwinSys, Israel

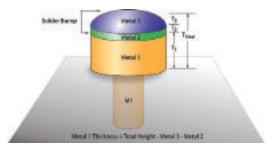

XwinSys has recently launched the 'ONYX' - a novel in-line and non-destructive hybrid metrology system, uniquely integrating advanced XRF, 2D and 3D optical technologies, designed to meet the current and future metrological challenges of the semiconductor industry.

FIGURE 1: The ONYX System

This is the case where the whole is greater than the sum of its parts the three integrated optical sensors creates an innovative synergistic approach to problem solving and product monitoring. This was only possible with off-line analytical tools in the past. By integrating components outputs, full scaled inspection parameters can be obtained.

The unique hybrid configuration of the ONYX enables a solution to challenging applications through various analytical approaches and effective SW algorithms:

- Metal film stacks thickness measurements

- Feature dimensions measuring

- Detection and analysis of voids or missing layers

- XRF thickness standards verification

- Detecting specific miss-processing out of a multi-variable metrology application

- Algorithm compensation for parameter variations of a film stack

FIGURE 2: Hybrid Configuration

The ONYX's unique triple-mode technologies and capabilities, designed to meet both fast in-line and in-depth metrology challenges, without interrupting the process flow. Enabling several physical parameters to be measured across the wafer, wafer to wafer, and lot to lot - ensures the process is in control. The ONYX is dedicated and designed to serve multiple in-line and non-destructive metrology and inspection needs in the semiconductor and related micro-electronics industries.

FIGURE 3: Multi-Stack Application

XwinSys Technology Development Ltd. Website: www.xwinsys.com Email: info@xwinsys.com Phone: +972-4-9891313

XwinSys is dedicated to the design, manufacture and marketing of novel solutions based on improved X-ray technology combined with automated optical 3D & 2D microscopes, for the Semiconductor and related industries.

Visit us at SEMICON WEST: booth 2245

### **DOWNLOAD THE COMPLETE TECHNICAL PAPER NOW!**

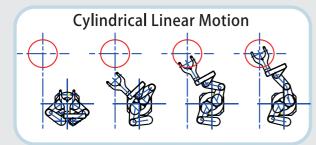

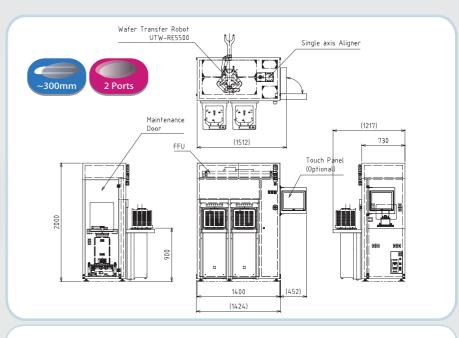

# Ophiuchus Equipment Front End Module

### **OPS-2300 Series**

### **OPS-2300 2 FOUP EFEM**

**Cylindrical Linear Motion** allows Trackless Two FOUP access.

Cooperative control between robot and single-axis aligner.

Various options to meet customer's requirements.

Visit us at booth 517 during SEMICON West 2016 Mention promo code DAC-SW16 to receive a special gift

### DAIHEN Advanced Component, Inc.

1223 East Arques Ave, Sunnyvale, CA 94085

Tel:

+1 408 736 2000

Fax:

+1 408 736 2010

E-mail:

info@daihen-ac.com

Website:

www.daihen-ac.com

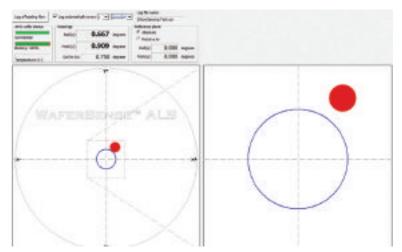

Evolution of across-wafer uniformity control in plasma etch

STEPHEN HWANG and KEREN KANARIK, Lam Research Corporation, Fremont, CA

A look at control of process uniformity across the wafer during plasma etch processes.

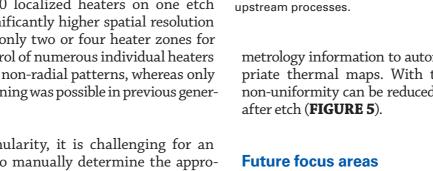

ontrolling process variability to achieve repeatable results has always been important for meeting yield and device performance requirements. With every advance in technology and change in design rule, tighter process controls are needed. In all of these cases, there are multiple sources of variability, often generalized as: within die, across wafer, wafer to wafer, and chamber to chamber. Typically, less than one third of the overall variation is allowed for variation across the wafer. For example, at the 14 nm node, the allowable variation for gate critical dimensions (CDs) is less than 2.4 nm, of which only about 0.84 nm is allowed for variation across the wafer [1]. At the 5 nm node, the allowable variation across the wafer may be less than 0.5 nm, or equivalent to two or three silicon atoms. In this article, we will discuss control of process uniformity across the wafer during plasma etch processes, its evolution in the industry, and some key focus areas.

ETCHING

A fundamental challenge in controlling uniformity in etch processes is the complexity of a plasma. Achieving the desired etch result (e.g., post-etch profile with selectivity to different film materials) requires managing the ratio of different ions and neutrals (e.g.,  $Ar^+$ ,  $C_4F_8$ ,  $C_4F_6^+$ , O,  $O_2^+$ ). Since the same plasma generates both types of species, the relative amount of ions to neutrals is strongly coupled. As a result, the impact of parameters typically used to control the plasma (e.g., source power and chamber pressure) are also interdependent.

### Improving uniformity through design

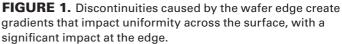

Since the start of single-wafer processing in the early 1980s, etch chambers have been designed to produce similar plasma conditions on every location on the wafer to achieve uniform process results. This is especially challenging since there can be inherent electrical and chemical discontinuities at the edge (**FIGURE 1**) that affect uniformity across the wafer. Voltage gradients are created at the wafer edge due to the change from a biased surface to a grounded or floating surface. This bends the plasma sheath at the wafer edge, which changes the trajectory of ions relative to the wafer. The chemical potential discontinuity is analogous and produces concentration gradients for different species

STEPHEN HWANG is technical director and KEREN KANARIK is senior technical director, Lam Research Corporation, Fremont, CA

ETCHING

**FIGURE 2.** Process non-uniformity has both radial and nonradial components (A). On a wafer map showing overall nonuniformity, removal of radial asymmetry allows isolating the more challenging non-radial component (B).

across the wafer. The gradients are caused by multiple phenomena, including variation in reactant consumption and by-products emissions rates at the center relative to the edge, as well as differences in temperature between the chamber and wafer that cause different absorption rates of chemical species.

Many chamber design changes have been implemented over the years to improve radial symmetry (**FIGURE 2a**). For example, a key hardware parameter for capacitively coupled plasma (CCP) chambers is the gap between the cathode and anode. Historically, the gap would be designed to provide the most uniform etch for a given power, pressure, and mixture of gas chemistries. On inductively coupled plasma (ICP) chambers, the

gas injection location was a key design feature that would vary by process. In aluminum etch chambers, the reactant gas was delivered from a showerhead above the wafer. For silicon etch, the reactant gases

# **A4 SERIES**

### Energy efficient dry multi-stage Roots process pumps for all semiconductor applications

- Low energy consumption

- Improved temperature management to optimize the pump according to your process

- Protection of the pump against precursor cracking or condensable deposition

- Corrosion resistant and high particle tolerance

- Extended monitoring functionalities

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com **VISIT US AT SEMICON WEST BOOTH #1716**

were injected from around the perimeter of the wafer, but then evolved so that the gas was injected from above the center of the wafer.

With continuous optimization of chamber design, non-radial patterns became more apparent. On a uniformity map, the average of all the points within every radius can be taken and subtracted from the map, which leaves the more difficult asymmetric portion (**FIGURE 2b**). With this awareness, focus shifted toward eliminating asymmetries in the chamber design.

In retrospect, some of these improvements seem obvious. For instance, up to the late 1990s, it was not uncommon to have etch chambers with the turbomolecular pump located to the side of the wafer. This design created a sideto-side pattern due to the convective flow of reactants and by-products laterally across the wafer. By moving the pumps under the wafer, the flow became radially symmetric, thereby eliminating the process asymmetry.

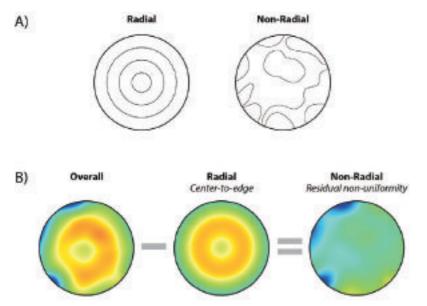

In other cases, the source of asymmetry was more subtle. One interesting non-uniformity corrected with design was a problematic side-to-side pattern on the wafer that had a seemingly random orientation chamber-to-chamber. After extensive investigation to eliminate possible sources in the chamber hardware, the pattern was correlated with the Earth's magnetic field (**FIGURE 3**). This example demonstrates the sensitivity of plasma processes, even to minor external influences. Although not specifically a

**FIGURE 3.** Non-uniformity induced by the Earth's magnetic field was identified in an etch process (A). Applying magnetic shielding corrected the problem and provided uniform etch results (B).

chamber issue, the problem was corrected by applying special shielding with high magnetic-permeability materials around the chamber.

### **Development of process tuning capabilities**

As etch processes became more varied and complex, fixed chamber designs were not sufficiently flexible to meet increasingly stringent requirements since it was not practical to provide a specific uniformity kit optimized for each etch process. Moreover, it was more challenging to achieve uniform results when etch technology transitioned from processing 200 mm to 300 mm wafers in the early 2000s. As a result, tuning capabilities were developed to deliver the uniformity control needed for a wide range of processes and larger wafer sizes.

By the early 2000s, the first uniformity tuning knobs focused on controlling the chemistry over the wafer. This was done in several ways, for example by splitting the main reactant gases into different locations or by adding tuning gases at separate locations from the main reactant gas. Since then, a number of tunable parameters have been identified for etch processes (**Table 1**). Ideally, orthogonal (independent) tuning knobs are used in order to match compensation as closely as possible to root causes. This provides the greatest impact on the process while limiting impact on other parameters. For example, in many dielectric etch processes, the etch rate is limited by the flux of ions from the plasma. Since gas injection doesn't significantly impact plasma density uniformity, Lam Research developed tunable gap technology for CCP chambers to achieve uniform flux of ions across the wafer for a given set of process conditions.

Over the years, continued development has focused on increasing the spatial resolution for better control across the wafer. For example, gas was at first only injected from the center location above the wafer. Then, additional capability was added that allowed controlling the ratio

| Tunable Parameter                   | Process Parameters Impacted                                      |

|-------------------------------------|------------------------------------------------------------------|

| Inner/outer inductive current (ICP) | <ul><li>Neutral density</li><li>Ion density</li></ul>            |

| Capacitive gap (CCP)                | <ul><li>Neutral density</li><li>Ion density</li></ul>            |

| Gas injection location              | <ul><li>Chemistry control</li><li>Convective transport</li></ul> |

| Wafer temperature (radial)          | Reactant and by-product absorption                               |

| Chamber/edge temperature            | Reactant and by-product absorption                               |

TABLE 1. Tunable Etch Parameters

of gas directed to the center or edge of the wafer. Several years later, an additional gas injection location was added around the periphery of the wafer. To use wafer temperature as a control knob, different heating or cooling zones can be added to an electrostatic chuck (ESC), which holds the wafer. Historically, the number of temperature zones has increased from one to two (by 2002) to four radial zones (by 2006) to improve the radial uniformity of CDs. Since temperature directly affects CD uniformity (CDU), this is an effective way to tackle one of the most critical uniformity challenges.

Some of the most complex process flows today rely on these sophisticated tuning capabilities. Innovations that drive continuous scaling, such as 3D FinFET devices, advanced memory schemes, and double/quadruple patterning techniques, add to the challenge of reducing variability due to the increasing number of steps within the integration flows. Even if the uniformity for individual unit processes (including etch) are relatively good, their combined impact can be significant, and there is need to compensate somewhere in the flow.

When the uniformity profile of a step in the sequence, upstream or downstream, is known and difficult to correct, the profile of an etch step can be modified. For example, if one step is center fast, etch can compensate by being edge fast. This may sound simple, but it is actually quite difficult to achieve the level of process control that can essentially provide a mirror image of the non-uniformity in another process. Fortunately, plasma etch is one process that has matured to being capable of this level of control.

### **Uniformity control today**

After many years of innovation, uniformity control capabilities now have the following characteristics:

Yield Engineering Systems, Inc.

# Quality Process Equipment, Built for Process Engineers.

### **YES-VertaCure**

Designed for wafer-level packaging (WLP), fan-out wafer level packaging (FOWLP) and Redistribution layers (RDL).

Visit YES @ SEMICON West - South Hall, Booth 1610 www.yieldengineering.com

1 Zone

CD Uniformity

2 Zones

Radial

### A high degree of granularity (numerous independent tuning locations across the wafer)

- Active tuning of both radial and non-radial patterns

- The ability to compensate for non-unifor-. mities upstream and downstream of the etch process

One strategy being used at Lam to achieve the degree of control now needed is providing numerous independent heaters

or micro-zones to control the wafer temperature, which is a critical parameter impacting CD uniformity. For example, using more than 100 localized heaters on one etch chamber delivers significantly higher spatial resolution than a system using only two or four heater zones for the entire wafer. Control of numerous individual heaters tunes both radial and non-radial patterns, whereas only center-middle-edge tuning was possible in previous generations (FIGURE 4).

With such high granularity, it is challenging for an individual engineer to manually determine the appropriate settings for so many heaters that will achieve a target thermal pattern across the wafer. To address this issue, advanced algorithms and controls with special temperature calibrations were developed so that the system automatically controls the heaters. Moreover, it can be difficult to determine the thermal map profile that will achieve the required process uniformity. Sophisticated software algorithms have also been developed to use process trends, chamber calibration data, and wafer

#### FIGURE 4. Active uniformity control has evolved from limited radial tuning of large areas of the wafer to independent tuning of ever smaller regions across the wafer, enabling control of both radial and non-radial uniformity.

Non-radial

4 Zones

- Overall

### **Distribution of CDs after Litho**

COLUMN TO A DESCRIPTION OF THE OWNER OWNER OF THE OWNER OWNE ..... **FIGURE 5.** Proprietary hardware and software map incoming CDs and adjust etch process conditions in the numerous microzones across the wafer to compensate for variability from

metrology information to automatically create the appropriate thermal maps. With this capability, incoming non-uniformity can be reduced to less than 0.5 nm CDU after etch (FIGURE 5).

Beyond the uniformity challenges discussed, performance at the edge of the wafer – the outer 10 mm, where up to 10% of the die may be located – is an increasingly important area of future focus for improving yield. In this region, uniformity control is dominated by the electrical discontinuities at the edge of the wafer that can cause sheath bending. The impacted region of sheath bending is much smaller (~10-15 mm from the edge) compared to chemical or thermal effects (50-70 or 30-50

mm, respectively). While fixed edge hardware can be redesigned for optimal uniformity, new technologies are in development to provide in situ tunability of the sheath at the wafer edge.

Looking ahead, we can expect more types of control knobs and further granularity for finer tuning along with a greater focus on automation. Compensatory process control should continue to develop and be used as process modules become increasingly complex.

### REFERENCES

ITRS 2013: Table FEP 12 Etch Process Technology Require-1 ments 🔷

Increasing spatial

resolution

>100 Zones

1.8 nm

3o variation

**Distribution of CDs after Etch**

# We create the future of **Motion Systems** - from top to bottom

### **ADVANCED MOTION PLATFORM**

addressing your most stringent requirements down to sub-nanometer levels. Come see us at

SEMICON WEST

HEIDENHAIN BOOTH #1809 ETEL BOOTH #1909

### **ACTIVE ISOLATION SYSTEM**

cancelling more than 99% of the vibration enabling unprecedented performance.

### **MOTION CONTROL**

providing sub-nanometer stability, high acceleration as well as very short move and settle time.

**ETEL is 100% dedicated to direct drive technology.** Our wide range of linear and torque motors, position and motion controllers and high-end motion system products provides a portfolio to meet your needs. The key process improvements you have been looking for are now available.

### www.heidenhain.us/etel

FOWLP

# Fan-Out Wafer Level Packaging: Breakthrough advantages and surmountable challenges

DAVID BUTLER, SPTS Technologies, an Orbotech company, Hereford, UK

New wafer processing technologies overcome FOWLP's technical hurdles, paving the way for a new generation of ultra compact, high I/O electronic devices

ur ability to create ever-smaller electronic devices that maintain or surpass the performance of their physically larger predecessors – exemplified by today's wearables, smartphones and tablets – is dictated by many factors that extend well beyond Moore's Law, from the underlying embedded components to the ways in which they're packaged together. With regard to the latter, fan-out wafer level packaging (FOWLP) is quickly emerging as the new die and wafer level packaging technique of choice, and is widely anticipated to underpin the next generation of compact, high performance electronic devices.

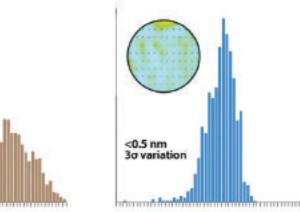

Whereas with conventional flip-chip WLP schemes the I/O terminals are spread over the chip surface area, limiting the number of I/O connections, FOWLP embeds individual die in an epoxy mold compound (EMC) with space allocated between each die for additional I/O connection points, avoiding the use of more expensive silicon real estate to accommodate a higher I/O count. Redistribution layers (RDLs) are formed using physical vapor deposition (PVD) and subsequent electroplating and patterning to re-route I/O connections on the die to the mold compound regions on the periphery (**FIGURE 1**).

Leveraging FOWLP, semiconductor devices with thousands of I/O points can be seamlessly connected via finelyspaced lines as thin as two to five microns, maximizing interconnect density while enabling high bandwidth data transfer. Significant height and cost savings are achieved via the elimination of the substrate.

With FOWLP today we have the ability to embed heterogeneous devices including baseband

FIGURE 1. FOWLP process flow.

DAVID BUTLER is Vice President of Product Management and Marketing, SPTS Technologies, an Orbotech company, Hereford, UK.

processors, RF transceivers and power management ICs in these mold wafers, thereby enabling the latest generation of ultra-thin wearables and mobile wireless devices. With continued line and space reductions, FOWLP has the potential to accommodate higher performing devices including memory and application processors, positioning FOWLP to extend into new markets including automotive and medical applications and beyond.

Leading vendors implementing FOWLP today include Amkor, ASE, Freescale, NANIUM, STATS ChipPAC, and TSMC, with TSMC being the most high-profile vendor given its widely-reported contract win to produce A10 processors for Apple's iPhone 7 – a deal said to be attributable in part to TSMC's mature FOWLP-based InFO technology.

According to a report entitled "FO WLP Forecast update 09/2015" published by research firm Yole Développement in September 2015, the launch of TSMC's InFO format is expected to increase industry packaging revenues for FOWLP from \$240M in 2015 to \$2.4B in 2020. With a projected 54% CAGR, Yole expects FOWLP to be the fastest growing advanced packaging technology in the semiconductor industry.

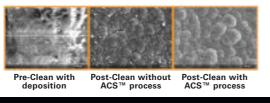

### Low heat, high speed processing

All fan-out wafers feature singulated die embedded in the EMC, with spin-on dielectrics surrounding the RDL. These materials present some unique challenges, including moisture absorption, excessive outgassing and a limited tolerance to elevated temperatures. If not dealt with properly, contamination at the metal deposition stage can compromise contact resistance.

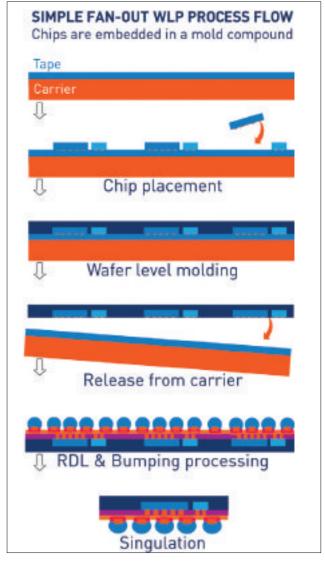

Whereas conventional circuits built on silicon can withstand heat up to 400oC and can be degassed in under one minute, the EMC and dielectrics used in FOWLP have a heat tolerance closer to 120oC. Temperatures exceeding this low threshold can cause decomposition and excessive wafer warping. Degassing wafers at such low temperatures naturally takes a longer amount of time, and can drastically reduce the throughput of a conventional sputter system.

Multi-wafer degas (MWD) technology has emerged as a compelling solution to this problem, enabling up to 75 wafers to be degassed at 120oC in parallel before being individually transferred to subsequent pre-clean and sputter deposition, without breaking vacuum. With this approach, wafers are dynamically pumped under clean, high vacuum conditions, with radiation heat transfer warming wafers directly to temperatures within the operating budget for packaging applications.

Each wafer can spend up to 30 minutes inside the MWD, but because they're processed in parallel, a "dry" wafer is outputted for metal deposition every 60 to 90 seconds, at a rate of between 30 to 50 wafers per hour. This approach increases PVD system throughput by 2-3 times compared to a single wafer degas processing technology, and as materials emerge with even lower thermal budgets based on increased passivation thickness, longer degas times can be accommodated with no impact on throughput (**FIGURE 2**).

These benefits are not readily attainable, however, unless we can overcome the attendant warping challenges. Epoxy

### NEW Plasma resistant O-ring material

- Avoid over-specification

- Reduce cost of consumables

- Reduce particulation

Utilizing the latest polymer and compounding technology, PPE has developed a new cost-effective, low particulate, low erosion elastomer material as shown by independent benchmarking against the leading brands in common plasma process chemistries.

► Discover more at SEMICON WEST, booth #1345 South

July 12 – 14, 2016 Moscone Centre San Francisco. CA

mold wafers can be warped after curing, and the size and shape of the warpage hinge on the different shapes, densities and placement of the embedded die. A FOWLP PVD system must therefore be able to minimize temperature-induced shape shifting, and accommodate wafers with up to a 10mm bow. The acceptable industry threshold for bowing is probably lower than 6mm, however, as it's not easy to make uniformly thick conductors on a substrate exhibiting 6mm+ warpage.

### **Utmost integrity**

After successful degas, but prior to metal deposition, the FO wafer is pre-cleaned in a plasma etch module. This facilitates the removal of trace oxide layers from the contacts, but due to the composition of the organic dielectric surrounding the contacts, will result

in carbon build-up on the chamber walls. This carbon does not adhere well to ceramic chamber surfaces, and if not carefully managed, can result in early particle failure.

New in-situ paste technologies allow these carbon deposits to better adhere to chamber surfaces during the pre-cleaning process, enabling preventative maintenance intervals that exceed 6,000 wafers. This approach can significantly improve productivity by reducing the frequency of dedicated wafer pastes, which typically require production to be paused every 10 to 20 wafers for chamber pasting when using conventional techniques.

**FIGURE 2.** The Sigma® fxP PVD system with multi-wafer degas module from Orbotech-SPTS.

The myriad benefits that FOWLP promises for the production of ultra compact, high I/O electronic devices far outweigh the aforementioned technical barriers to mainstream FOWLP adoption. With the ability to overcome the degassing, warping, and integrity challenges that can impede FOWLP implementations, electronics manufacturers can unlock the full potential of FOWLP while eliminating frictions affecting production speeds and yields. ◆

SEP. 7-9, 2016 TAIPEI NANGANG EXHIBITION CENTER, HALL 1

### Connect to the Global Semiconductor Supply Chain at SEMICON Taiwan

The Taiwan equipment and materials market is expected to remain the largest in the world, reaching more than US\$17 million in 2016. Connect to this exciting and dynamic market at SEMICON Taiwan, the most influential annual event serving the microelectronics supply chain in Taiwan. SEMICON Taiwan brings together leading international companies from across the region and around the world, with more than 700 international exhibitors, more than 1,600 booths, and more than 43,000 attendees expected making it the must-attend event of the year!

### **Explore Latest Trends and Emerging Markets**

- AOI Pavilion

- High Tech Facility Pavilion

- Materials Pavilion

- CMP PavilionLaser Pavilion

- Precision Machinery Pavilion

- Smart Manufacturing Pavilion

- Secondary Market PavilionTaiwan Localization Pavilion

### Expand Professional Network at Diverse Events and Activities

- International Program

- Leadership Gala Dinner

semi

- Supplier Search Program

- TechXPOT

Register Online for FREE www.semicontaiwan.org

TUNGSTEN

# Extending tungsten metallization for next-generation devices

JONATHAN BAKKE, Applied Materials, Santa Clara, CA

Recent breakthroughs in materials engineering of low-resistance W barriers/liners and bulk fill are making it possible to extend W use to next-generation devices.

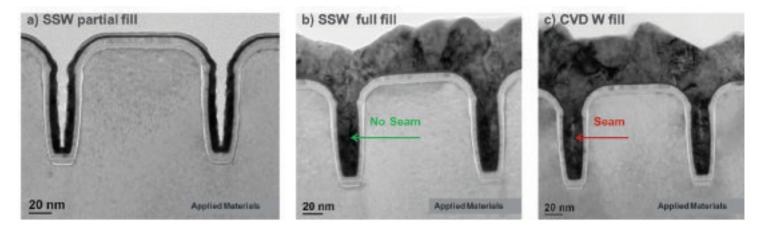

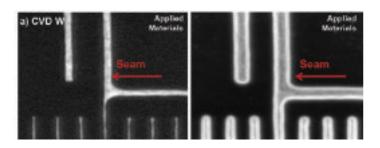

ungsten (W), with its low resistivity and minimal electro-migration, has long been used for a variety of applications in fabricating semiconductor devices. For instance, it is used for logic contact, local interconnect (LIC), and metal gate (MG) fill as well as DRAM buried word line and contact and 3D NAND MG and contact. Sustained scaling, however, is posing challenges to its continued use with conventional process flows. Interconnect dimensions have shrunk to the point at which contact resistance is becoming an obstacle to realizing optimum transistor performance; fill integrity degrades as aspect ratios and the degree of re-entrance increase, making it difficult to ensure highquality metallization.

At earlier nodes, larger dimensions made W fill possible using conformal CVD deposition. Now, overhang around the tops of ultra-small openings or bowing from the interconnect etch open preclude the conformal process from completely filling features without voids, while center seams are an inevitable result of conformal deposition, even in the absence of voids. These attributes render extremely small features vulnerable to breach during CMP, causing high resistance or complete failure of an interconnect. High feature densities and lack of via redundancy in advanced chip designs mean that a single void can cause complete device failure and significant yield loss.

Fortunately, recent breakthroughs in materials engineering of low-resistance W barriers/liners and bulk fill are overcoming these limitations and making it possible to extend W use to next-generation devices. The former lower resistance by simplifying fill film requirements and enlarging the volume available for W fill; the latter elimi-

nates undesirable seams to create more robust structures.

### **Low-resistance liners**

To date, high-resistivity TiN has been predominantly used as an adhesion layer for CVD W and to block fluorine penetration during the bulk fill process. W does not grow directly on TiN; thus, it requires deposition of a nucleation layer before the fill step. As logic devices scale through the 10 nm node and beyond, the maximum critical dimension (CD) of the LIC will be <25 nm. This leaves <12 nm for low-resistance W fill after the relatively high-resistance TiN and

**JONATHAN BAKKE** is global product manager for Contact and Middle of Line Products in the Metal Deposition Products Business Unit of Applied Materials, Santa Clara, CA.

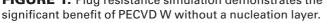

**FIGURE 2.** PECVD W plus gap fill reduces line resistance by nearly 90% over the conventional stack. The inset TEM shows conformal gap fill and CMP integration for PECVD W.

nucleation layers, which results in an overall high contact resistance. Further, every metal interface adds to the resistance to the contact. Metal-organic deposition of thin W-based films offers an ideal solution, because it can eliminate high-resistance liners and nucleation layers while maintaining adhesion and fluorine-barrier properties equivalent to those of the current process flow. A new W liner has been developed that lowers line resistance for further device scaling: plasma-enhanced (PE) CVD W that nucleates on metal and oxides.

The PECVD W film is produced using a specialized chemical in the presence of reactive plasma that breaks down the ligands. The film composition is primarily

W, and the atoms from the decomposed ligands are bonded to the W. The amorphous character of the film and the dopants in it from the ligand lead to good adhesion to dielectrics and fluorine barrier properties in the 20-30Å range.

**FIGURE 1** shows a simulation of a contact plug in the 4-30nm range. The model contains parallel and series resistors for the plug and through resistance. Features

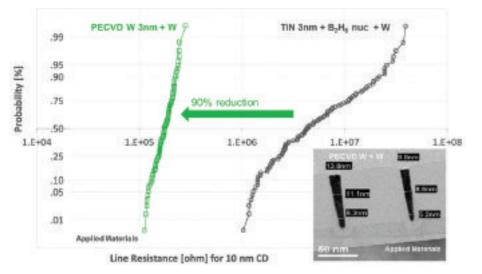

### Optimize Your Surface Measurement and Inspection Motion Save 40% Measurement Time and 60% Footprint

Traditional Cartesian systems require frequent, time-consuming motion reversals in X and Y to raster-scan a part, which necessitates longer travel ranges to account for inefficiencies in constantly starting and stopping. The vastly superior SMP design utilizes an industry-leading rotational motion profile to deliver smooth, continuous scanning of the part, with no starts and stops, resulting in significantly reduced measurement time and machine footprint.

Ph: 412-963-7470 • Email: sales@aerotech.com • www.aerotech.com WORLD HEADQUARTERS: USA THE AMERICAS • EUROPE & MIDDLE EAST • ASIA-PACIFIC

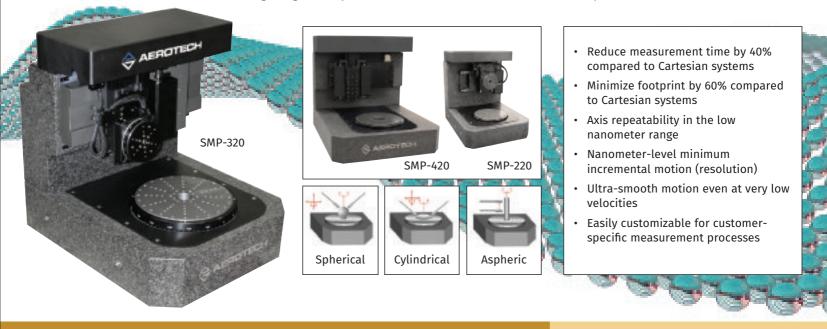

**FIGURE 4.** Line resistance comparison of SSW and conventional CVD W on 10nm trench.

are assumed to be straight wall trenches. Resistance of 12  $\mu\Omega^* cm$  is used for W at all thicknesses, which underestimates the benefit of PECVD W. Scattering at film interfaces is not taken into account. The inflections in the curves (from right to left) occur when a film is removed due to volume constraints. It is clear that the benefit of PECVD W increases exponentially as CDs decrease, especially without the nucleation layer.

SiO2 trench structures with CDs ranging from 10nm to 150nm and a depth of 100nm were used to investigate W line resistance and evaluate gap-fill performance. As shown in **FIGURE 2**, line resistance in a ~10 nm CD dropped by nearly 90% compared with the conventional stack.

### Seam-suppressed gap fill

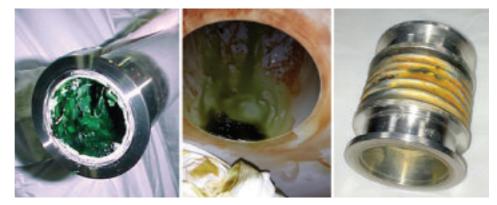

Until now, feature dimensions have made W fill integration possible using nucleation followed by