SEMICONDUCTORS • PACKAGING • MEMS • LEDS • DISPLAYS JUNE 2012

# SOCIAL STREET

Thin Die Stacking for Wide I/O P. 17

BTI Mechanisms p. 21

TSV Inspection P. 24

# The Next Transistor P. 13

www.solid-state.com

PennWell

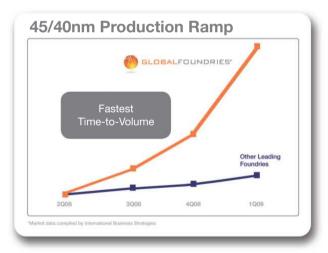

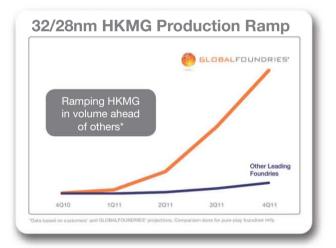

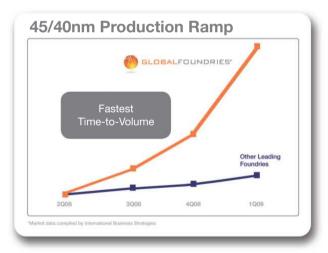

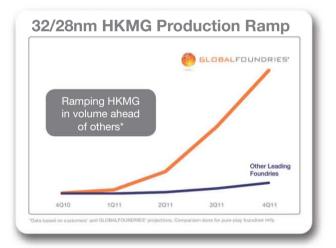

#### **LEADING THE FOUNDRY RAMP IN 32/28nm WAFER PRODUCTION**

GLOBALFOUNDRIES has shipped >250,000 32/28nm HKMG wafers to date. This milestone represents a significant lead over other foundries in 32/28nm manufacturing.

On a unit basis, cumulative **32/28nm shipments** for the first five quarters of wafer production are **more than double that achieved during the same period of the 45/40nm technology node ramp**, demonstrating that the overall HKMG ramp has significantly outpaced the 45/40nm ramp.

The tradition of rapidly ramping leading-edge technologies to volume production continues.

Omag

Zoom in | Zoom out

For navigation instructions please click here

Search Issue | N

DISPLAYS

Next Page

SEMICONDUCTORS •

• MEMS • LEDS •

JUNE 2012

# SOCOLOGY TECHNOLOGY Insights for Electronics Manufacturing

PACKAGING

Thin Die Stacking for Wide I/O P. 17

BTI Mechanisms p. 21

TSV Inspection P. 24

# The Next Transistor P. 13

www.solid-state.com

Contents

Zoom in | Zoom out

Search Issue

Next Page

ADVANCED PACKAGING SINGLE WAFER WET PROCESSING

### Solid State Equipment LLC

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

ADVANCED PACKAGING SINGLE WAFER WET PROCESSING

#### TSV RESIST STRIP AND CLEAN

As received - post DRIE

After SSEC Cleaning

As received - post DRIE

After SSEC Cleaning

As received - post DRIE

ISIS 3D

#### Si ETCH TO REVEAL Cu TSV

DRY FILM STRIP

SEM

Ζ (μm) 1.15 0.78 33.23 0.42 0.05 Y (mm X (mm) -0.31

FLUX CLEANING

UBM AND RDL METAL ETCH

UBM Post Etch

UBM Post Strip

ssecusa.com

© 2012 SOLID STATE EQUIPMENT LLC

ECHNOLOGY

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend

| Search Issue | Next Page

After SSEC Cleaning

ECHNOLOGY

COVER

JUNE 2012 VOL. 55 | NO. 5

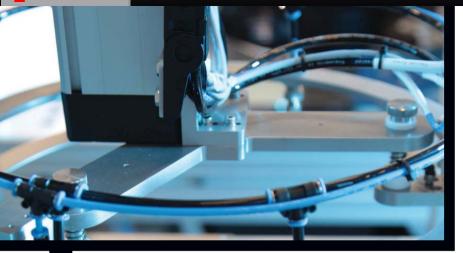

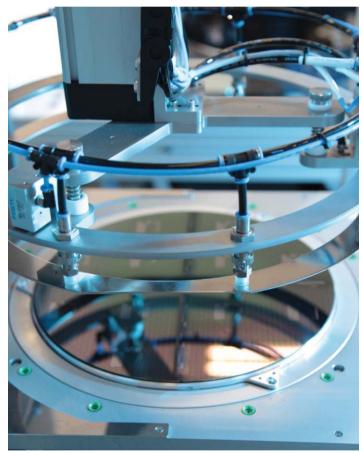

Loading station of integrated film frame mounter in an EVG 850DB automated debonding system.

#### FEATURES

#### TRANSISTORS | The Next Transistor

New transistor technologies in development include high mobility transistors with III-V channel materials, tunneling and quantum-well FETs, and more "exotic" approach involving silicon nanowires, CNTs and graphene. *Pete Singer, Editor-in-Chief*.

#### **3D INTEGRATION** | Thin die stacking for wide I/O memory-on-logic Wide I/O DRAM is pushing thin wafer processing into high-volume manufacturing

Wide I/O DRAM is pushing thin wafer processing into high-volume manufacturing readiness. Thorsten Matthias, Jürgen Burggraf, Daniel Burgstaller, Markus Wimplinger, and Paul Lindner, EV Group, St. Florian am Inn, Austria.

#### **RELIABILITY** | Bias temperature instability mechanisms

NBTI is considered to be one of the most difficult reliability challenges facing the semiconductor manufacturing community today. *Christopher L. Henderson, Semitracks, Inc., and David W. Rose, Keithley Instruments, Inc.*

### **PACKAGING** |TSV inspection in 3D advanced packaging applications

Laser triangulation provides fast, accurate and repeatable 3D measurement of TSV nails and microbumps. *Reza Asgari, Rudolph Technologies, Inc., Flanders, NJ.*

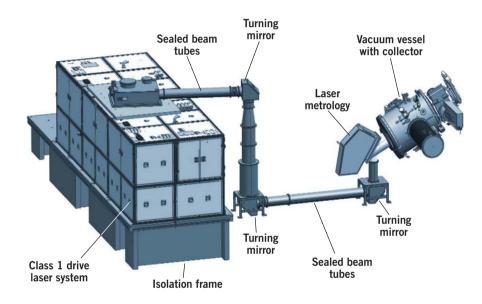

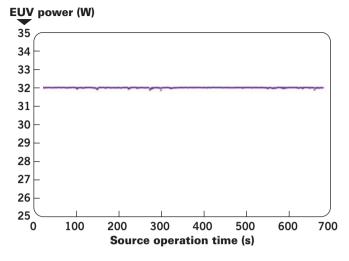

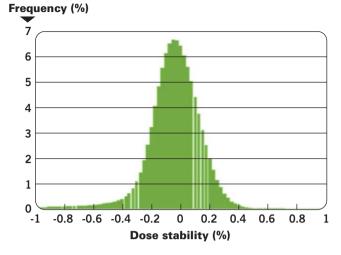

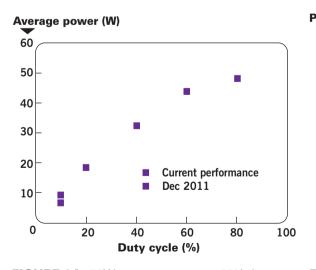

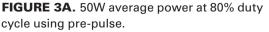

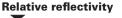

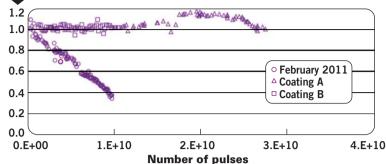

#### EUV SOURCES | LPP Light Sources for EUV

Today's sources have an average power of 50W at intermediate focus, at 80% duty cycle using pre-pulse technology. *David C. Brandt, Igor V. Fomenkov, Bruno M. La Fontaine and Michael J. Lercel, Cymer, Inc., San Diego, CA.*

#### COLUMNS

- **4** Editorial Funding the future: Managing the cost of R&D, *Pete Singer, Editor-in-Chief*

- **11 Packaging** 3.5D interposers: PCB replacement?, Dr. Phil Garrou, Contributing Editor

- 12 MEMs | Epidermal electronic systems , Mike Fury, Techcet Group

- **33** Industry Forum | SEMI educates policymakers on 450mm, Jonathan Davis, SEMI

www.solid-state.com

#### DEPARTMENTS

- **2** Web Exclusives

- 6 News

- 31 Ad Index

SOLID STATE TECHNOLOGY June 2012

Next Page

1

### Qmags

# Online@www.solid-state.com

### Web Exclusives

### Improving HB-LED economics

SEMI's Paula Doe covers the "commodity market" of LEDs, including capacity utilization at LED fabs, automation in manufacturing that could improve yields, LEDs fabbed on silicon and GaN instead of sapphire wafers, and more. <u>http://bit.ly/KNWhLx</u>

# MEI wet process tools built to prevent contamination

MEI uses Vycom Flametec PVC-C for chemical rinse tanks and other wafer-contacting elements of its process tools, reducing tool-based contamination and protecting fab workers. Bill Mc-Ginty, MEI operations manager, discusses the benefits the newgeneration plastic for semiconductor fab tools. http://bit.ly/lwq2jz

#### **Book review:**

### Energy Harvesting for Autonomous Systems

Contributing editor Steve Groothuis reviews a book titled "Energy Harvesting for Autonomous Systems (Smart Materials, Structures, and Systems)" by Stephen Beeby (Author, Editor), and Neil White (Editor). The book highlights the progres-

sion from the basic principles behind energy harvesting to the comprehensive systems that control the sensing, actuation, and transmission of those devices. <u>http://bit.ly/JAE331</u>

# OLED makers develop new color patterning tech

OLEDs are gaining adopters in small screen sizes, and just moving into large-size displays. Mass production color-patterning technology for large-area OLED is increasingly an issue. Displaybank looks at new technologies under development at major display makers. <u>http://bit.ly/J3PXOI</u>

### Intel's 22nm trigate transistors exposed

When Intel held its Q1 results call, the company said that the 22-nm Ivy Bridge parts

would make up 25% of their shipment volume in Q2. Blogger Dick James, Chipworks, man-

aged to track some down: Xeon E3-1230 v2 CPUs, which are four-core, 3.3 GHz, 64-bit parts intended for the server market.

A quick cross-section reveals that Intel stayed with the nine metal layers used in the last two generations.

Looking at TEM images of the die (visit the blog URL to see images), James found that the PMOS S/D fins have epitaxial growth on them, and the fins have an unexpected slope -- a bit different from Intel's trigate schematic shown last year.

As announced by Intel, there is embedded SiGe in the source/ drains, although not etched to the <111> planes as in the 32 and 45nm product. It also looks as though the tops of the gates have been etched back and back-filled with dielectric, and the contacts are self-aligned as in memory chips. http://bit.ly/ J9PGcD

CHNOLOGY

www.solid-state.com

Omage

# Vacuum Pressure Measurement

The SRS line of Residual Gas Analyzers and Ion Gauge Controllers are designed to meet virtually any vacuum pressure measurement need.

The IGC100 Ion Gauge Controller monitors total pressure from up to two ion gauges, two convection enhanced Pirani gauges and four capacitance manometers. There's a touchscreen display that shows gauge pressures in large, easy to read numbers. You can also graphically display pressure vs. time curves. In addition, the IGC100 has an optional ethernet port for web interfacing.

RGAs from SRS bring large dynamic range, high resolution and excellent linearity to partial pressure measurements. A dual ThO<sub>2</sub>Ir filament and unique four channel electron multiplier extend operating life. Windows control and analysis software along with an RS-232 interface is provided at no charge.

### **Residual Gas Analyzers**

- 100, 200 and 300 amu models

- Sensitivity to 5×10<sup>-14</sup> Torr

- Dual ThO<sub>2</sub>Ir filament

- Long-lasting electron multiplier

- 6 decades of dynamic range

- Windows software

RGAs starting at \$3750

#### Ion Gauge Controller

- 1000 Torr to UHV range

- 0.3 % controller accuracy

- Touch-screen display

- Pressure vs. time curves

- 8 channel process control

- 4 analog I/O ports

- RS-232, GPIB and Ethernet

IGC100 starting at \$1495

Prices are U.S. list

**Stanford Research Systems** 1290-D Reamwood Ave. Sunnyvale, CA 94089 Phone (408) 744-9040 Fax (408) 744-9049 email: info@thinkSRS.com www.thinkSRS.com

### editorial

# Funding the future: Managing the cost of R&D

One of the big issues now facing the industry is to how best spend limited funding for research and development, when so much needs to be done. Continued scaling to 10nm and below, a transition to 450mm, 3D integration, device new structures such as the FinFET, a bevy of new materials with unknown integration challenges - these are all needed.

I think it's fairly clear that, with the industry's present model, it's going to be difficult to fully finance everything on the wish list. This isn't a new dilemma, of course. In a SEMI-funded reported published in

### "A new model is needed or not everything will get funded"

2005, Ron Leckie analyzed all the things that were noted in the International Technology Roadmap for Semiconductors (ITRS) and concluded that the funding gap could reach upwards of \$9.3 billion by 2010 (which included the 450mm transition). Seven years later, Moore's Law is holding firm. The way the industry has been able to get around the funding challenge is through collaboration. Consortia such as SEMATECH and imec are great models of collaboration, enabling companies to work on "pre-competitive" research to share costs and reduce risks. The Common Platform model employed by IBM/Samsung/ GLOBALFOUNDRIES is another great example. The entire CNSE/Albany Nanotech/G450C effort is perhaps the best example of university, industry, consortia and government working together.

But is this enough? One could argue that fabless companies could do more to support semiconductor R&D. Ditto for the likes of Microsoft, Facebook and many other entities that have built their company on the internet and electronics technology.

Perhaps the semiconductor industry will go the way of the automotive and aerospace industries, which have very different models when it comes to cost-sharing and risk-sharing. One thing is for sure: a new model is needed or not everything will get funded.

-Pete Singer, Editor-in-Chief

### **Solid State** ECHNOLOG

Susan Smith, Group Publisher Ph: 603/891-9447, susans@pennwell.com Pete Singer, Editor-in-Chief

Ph: 603/891-9217, psinger@pennwell.com Meredith Courtemanche, Editor, Digital Media Ph: 603/891-9176, mcourtemanche@pennwell.com

Robert C. Haavind, Editor-at-Large Ph: 603/891-9453, bobh@pennwell.com

Phil Garrou, Contributing Editor Michael Fury, Contributing Editor Rachael Caron, Marketing Manager Cindy Chamberlin, Presentation Editor Katie Noftsger, Production Manager Dan Rodd, Illustrator

Debbie Bouley, Audience Development Marcella Hanson, Ad Traffic Manager

EDITORIAL ADVISORY BOARD John O. Borland, J.O.B. Technologies Michael A. Fury, The Techcet Group, LLC Rajarao Jammy, SEMATECH William Kroll, Matheson Tri-Gas Ernest Levine, Albany NanoTech Lars Liebmann, IBM Corp. Dipu Pramanik, Cadence Design Systems Inc. Griff Resor, Resor Associates A.C. Tobey, ACT International

#### EDITORIAL OFFICES

PennWell Corporation, Solid State Technology 98 Spit Brook Road LL-1, Nashua, NH 03062-5737 Tel: 603/891-0123: Eax: 603/891-0597: www.ElectrolQ.com

#### PennWell

#### CORPORATE OFFICERS

1421 South Sheridan Rd., Tulsa, Ok 74112 Tel: 918/835-3161 Frank T. Lauinger, Chairman Robert F. Biolchini, President and CEO Mark Wilmoth, Chief Financial Officer

TECHNOLOGY GROUP

Christine A. Shaw, Senior Vice President and Publishing Director

For subscription inquiries: Tel: (847) 559-7500; Fax: (847) 291-4816; Customer Service e-mail: sst@omeda.com: Subscribe: www.sst-subscribe.com

We make portions of our subscriber list available to carefully screened companies that offer products and services that may be important for your work. If you do not want to receive those offers and/or information, please let us know by contacting us at List Services, Solid State Technology, 98 Spit Brook Road, Nashua, NH 03062. All rights reserved No part of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval sys tem, without written permission of the copyright owner. Prices for bulk reprints of articles available on request. Solid State Technology articles are indexed in Engineering Information and Current Contents, and Applied Science & Technology Index ind abstracted by Applied Science & Technology Abstracts.

AMERICAN BUSINESS MEDIA

Qmags

Omag

www.solid-state.com

SOLID STATE TECHNOLOGY **JUNE 2012**

4

# RIXTRON

Omags

### QXP-8300: Cutting Edge ALD Product for Leading Edge Semiconductor Technology Nodes

### QXP-8300 for Higher k Oxides, Metal and NVM Films

Excellent step coverage and gapfill of complex materials solution to memory market challenges

40% less precursor usage – lower CoC

Offers the best in class productivity through innovative mini-batch ALD reactor design

AIXTRON provides deposition systems with cutting edge technology for Logic, DRAM, NVM, Flash and MIM applications. QXP-8300 meets state-of-the art silicon production standards and enables innovative technology breakthroughs for sub 3x nm device feature sizes.

AIXTRON SE · info@aixtron.com · www.aixtron.com

Please send news articles to meredithc@pennwell.com

#### worldnews

**EUROPE** | Infineon Technologies AG CEO Peter Bauer will resign his post at the end of the current fiscal year due to worsening osteoporosis. http://bit.ly/Jexoy3

ASIA Micron Technology Inc. (Nasdaq:MU) confirmed that it is engaged in discussions to take over the assets of bankrupt DRAM maker Elpida Memory. http://bit.ly/KsofQn

**WORLD** Worldwide silicon wafer area shipments increased slightly during Q1 2012 when compared to Q4 2011 area shipments, according to SEMI. <u>http://bit.ly/MgXKz6</u>

ASIA Hanking Industrial Group broke ground on a MEMS manufacturing campus in Fushun City, China, outside of Shenyang. http://bit.ly/Kk6gJa

WORLD Semiconductor packaging and test services provider Carsem will assemble and test LED packages. http://bit.ly/L3CpUi

USA The CNSE Smart System Technology and Commercialization Center of Excellence (STC), Canandaigua, NY, was designated as a Trusted Foundry by the US DoD. http://bit.ly/lcA3UG

ASIA Many display manufacturers are transitioning tablet panel production to larger plants, including Gen 6 and Gen 8, which will lead to greater capacity for tablet displays, as well as lower prices. <u>http://bit.ly/</u> JtkLPq

USA Microsoft has joined the Hybrid Memory Cube Consortium (HMCC), a collaboration of original equipment manufacturers (OEMs), enablers and integrators. <u>http://bit.</u> ly/Lg0spg

6

ECHNOLOGY

# MOCVD capex disobeys fab utilization rules at LED makers

Barclays Capital analysts attended Lightfair International (May 9-11) and gleaned several trends in LEDs and OLEDs for lighting. This year's Lightfair was "almost entirely focused on LEDs," said Barclays analysts. While LED dominance in new products at the booths is not yet indicative of end market penetration, it highlights the inevitability of LED lighting adoption in the coming years.

While utilization rates are still relatively low in LED fabs, many chipmakers are reluctant to convert all of their backlighting-specific (BLU LEDs for display applications) LED tools to lighting-specific production, because they value yields honed for a specific design. Chipmakers told Barclays that they do not want to reconfigure MOCVD tools unless they are confident that this backlighting-specific production will no longer be needed. This suggests that anticipated LED lighting demand in H2 2012 and beyond will require more MOCVD tool orders, even without higher capacity utilization rates in LED fabs. Gradually improved MOCVD capex, in Q3 2012 and beyond, will be supported by a steady stabilization in LED supply/ demand as 2013 approaches.

Barclays observed that LED

chips still compete based on price, even among the Tier 1 LED makers, and further cost reductions are needed if margins are to survive. LED component price declines did moderate to an extent relative to last year's price cuts, but the aggressive pricing trend continues, driven in part by end customers leveraging Tier 3 quality price points in China against Tier 1 and 2 LED makers. Until yields top 80%, lower-quality LEDs will be dumped on the market at lower prices. Indeed, even in lightinggrade LEDs, there is "no rationality for price points," according to 1 Tier-1 supplier. The good news for LED revenues is that unit volume growth is offsetting the price cuts.

Only ~10 LED makers can reach 100lm/W efficacy levels in mass production, and meet Energy Star, UL, etc., specifications. Samsung is becoming a major threat to Tier-1 LED suppliers, longer term, as it focuses on quality.

While still in the early stages of development, OLED lighting was also being exhibited by several suppliers, with Philips and OSRAM appearing to be at the lead with efficacy and product quality. Philips' OLED lighting panels reached 25Im/W this year, with

Continued on page 7

JUNE 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

the company aiming for 60lm/W next year, driven by new developments in OLED materials (Philips using RGB stack with combination of phosphorescent and fluorescent materials); new developments in the glass substrate (adding reflective element to the glass composition); and advances in the deposition and processing technology. However, while reaching 60lm/W efficacy would be a big breakthrough, the key from there would be lumen maintenance, which is still very low for the OLED lighting panels currently available on the market. And while some companies suggested that OLED lighting is now moving from a designer/architectural application to a highend lighting application, based on the product specs and the pricing, Barclays puts OLED lighting ~5-7 years behind LED lighting.-**M.C.**

#### Top OSATS raise 2012 capex with test focus

The top three outsourced semiconductor assembly and test services (OSATS) providers raised 2012 capital expenditures during their earnings reports, from initial plans announced in January, report analysts at Citi.

To increase capacity due to mobility growth, Amkor (AMKR) raised capex from \$300 million to \$550 million; Advanced Semiconductor Engineering Incorporated (ASE) raised capex from \$725 million to \$800 million; and Siliconware Precision Industries Co. Ltd. (SPIL) raised capex from \$350 million to \$600 million. Collectively, the three companies increased 2012 capex by \$575 million or 42% vs. January plans.

"Several of our major customers that sell into smartphones and tablets have substantially increased their demand forecasts with us and we are raising our estimate of 2012 capital additions...to meet these specific new opportunities. However, our sales and capital additions may vary depending on a number of factors including the supply of 28 nanometer wafers for some of our customers," said Ken Joyce, Amkor's president and CEO.

All three OSATS singled out test capacity addition as the focus of higher capex, with total test capex up from \$280 million (in Jan plan) to \$628 million, up 124% from the original plan. OSATS commented that baseband and power management ICs are the main driver. Citi expects Teradyne to get a sizable share of the orders due to its 60% share in mobility.

The current capex plan for these top 3 OSATS is slightly H1 loaded, with 55% of planned capex earmarked for the first half of 2012. However, with low/unstable yield at 32/28nm fabs, and a large amount of capacity entering the market starting in Q3, there is a general concern over skyrocketing test burden in H2. Citi expects this could drive the upside in H2 of OSATS test capex.**–M.C.**

### Semiconductor Assembly

### Visit my semiconductor blog for the latest on:

- 2.5D and 3D fluxes

- Package-on-package

- Pb-free power semiconductor solders

©2012 Indium Corporation

www.solid-state.com

**ECHNOLOGY**

7

# **NEV/S**cont

# President Obama speaks on "insourcing" at Albany Nano-Tech complex

US President Barack Obama toured the University at Albany - State University of New York (SUNY) -Albany Nano-Tech Complex on May 8, speaking about the economy in the College of Nanoscale Science and Engineering's (CNSE) NanoFab Extension Building.

CNSE is a global education, research, development and technology deployment resource educating scientists and researchers in national and international sources. Fab 8 created an additional 4,300 construction-related jobs and established the largest private Project Labor Agreement in history, generating hundreds of millions of dollars of economic development throughout upstate New York, the foundry reports. Fab 8 began production in January 2012, and should ramp to volume this year. In January. President Obama

"The true engine of job creation in this country is the private sector. There are steps we can take as a nation to make it easier for companies to grow and to hire"

nanotechnology. It hosts myriad private-public partnerships with academia and research organizations partnering with global semiconductor equipment and materials suppliers, as well as chip makers.

GLOBALFOUNDRIES CEO Ajit Manocha spoke during the event. The presidential visit had to move from GLOBALFOUNDRIES' new Fab 8 to the college for logistical reasons. Since breaking ground on Fab 8 in 2009, GLOBALFOUNDRIES has created more than 1,300 new direct jobs with the project, drawn from local talent in the region and

2

**ECHNOLOGY**

visited Intel's Ocotillo semiconductor manufacturing location in Chandler, AZ, touring Fab 42, which is under construction. The visit carried a similar theme as the one to CNSE in May

– advanced manufacturing jobs in America, and improving education to develop future technological leaders from America. Obama is emphasizing the connection between education, innovation, and manufacturing in supporting investment and bringing jobs back to the US, which the administration touts as "insourcing."

"The true engine of job creation in this country is the private sector. There are steps we can take as a nation to make it easier for companies to grow and to hire — to create platforms of success," said Obama at CNSE (a transcript of Obama's

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

remarks is available from the White House, http://1.usa.gov/JoFqCb). He listed ways to accelerate the US economy, including tax breaks for clean-energy companies and small business owners, support for veterans in the job market, and encouraging US-based manufacturing and exports. "American manufacturers are creating new jobs for the first time since the 1990s," he said, and asserted that half of America's largest companies are considering moving manufacturing operations from China to the US. "Even when we can't make things cheaper than other countries, we can always make them better."

From the White House: "The President's visit to the College of Nanoscale Science and Engineering at SUNY-Albany demonstrates the important role that partnerships between universities and companies can play in accelerating education, innovation and U.S. manufacturing investment."

The President compared CNSE to his administration's proposed "National Network for Manufacturing Innovation" consisting of up to fifteen institutes, each bringing diverse companies, research organizations and universities, federal agencies, and states together to make US manufacturing facilities and enterprises "more competitive and encourage investment." **–M.C.**

JUNE 2012 SOLID STATE TECHNOLOGY

www.solid-state.com

### **GLOBALFOUNDRIES** joins top-20 ranks in Q1 on **Elpida bankruptcy**

The top 20 semiconductor suppliers in Q1 2012, compiled in IC Insights' May Update to The McClean Report, show Intel's firm hold on the top of the rankings, registering a 68% higher sales level than Samsung in Q1.

With the addition of GLOBALFOUNDRIES, 3 pureplay foundries are now in the top 20 ranking. GLOBALFOUNDRIES replaced bankrupt Elpida. If

. . . . . .

Micron takes over the bankrupt DRAM maker, it could jump 1 or 2 positions in the rankings.

Q1 sales from the top 20 semiconductor suppliers were "generally disappointing," says IC Insights, which believes that the bottom of the semiconductor market slowdown occurred for most top companies in Q4 2011/Q1 2012. IC Insights expects much improved sequential quarterly sales performance starting in 2Q12, based

on company reports and analysis. Expect a 6% increase from Q1 to Q2, and even stronger growth Q2 to Q3.

The top 20 semiconductor suppliers saw a wide range of Y/Y growth in Q1. Only 3 companies registered better-than-flat Y/Y growth rates: Qualcomm, Fujitsu, and Broadcom. Each of the big four memory suppliers in the top 20 ranking - Samsung, Toshiba, SK Hynix, and Micron saw sales decline Y/Y.-M.C

.....

-----

.....

| Q1 2012<br>rank   | 2011 rank | Company          | HQ       | 2011 total semi | Q1 2011<br>total semi | Q1 2012<br>total semi | Q1Y/Y %<br>change |

|-------------------|-----------|------------------|----------|-----------------|-----------------------|-----------------------|-------------------|

| 1                 | 1         | Intel            | US       | 49697           | 11819                 | 11874                 | 0                 |

| 2                 | 2         | Samsung          | S. Korea | 33483           | 8215                  | 7067                  | -14               |

| 3                 | 3         | TSMC*            | Taiwan   | 14600           | 3600                  | 3568                  | -1                |

| 4                 | 5         | Toshiba          | Japan    | 12745           | 3435                  | 3232                  | -6                |

| 5                 | 7         | Qualcomm**       | US       | 9828            | 1962                  | 3059                  | 56%               |

| 6                 | 4         | TI               | US       | 12900           | 3167                  | 2934                  | -7                |

| 7                 | 6         | Renesas          | Japan    | 10653           | 2897                  | 2344                  | -19               |

| 8                 | 10        | Micron           | US       | 8571            | 2218                  | 2120                  | -4                |

| 9                 | 9         | SK Hynix         | S. Korea | 9403            | 2499                  | 2115                  | -15               |

| 10                | 8         | ST               | Europe   | 9631            | 2523                  | 1997                  | -21               |

| 11                | 11        | Broadcom**       | US       | 7160            | 1752                  | 1770                  | 1                 |

| 12                | 12        | AMD**            | US       | 6568            | 1613                  | 1585                  | -2                |

| 13                | 13        | Sony             | Japan    | 6093            | 1520                  | 1514                  | 0                 |

| 14                | 14        | Infineon         | Europe   | 5599            | 1362                  | 1297                  | -5                |

| 15                | 15        | Fujitsu          | Japan    | 4430            | 1148                  | 1216                  | 6                 |

| 16                | 17        | NXP              | Europe   | 4147            | 1071                  | 1071                  | 0                 |

| 17                | 18        | Nvidia**         | US       | 3939            | 936                   | 935                   | 0                 |

| 18                | 16        | Freescale        | US       | 4391            | 1155                  | 912                   | -21               |

| 19                | 21        | GLOBALFOUNDRIES* | US       | 3480            | 845                   | 840                   | -1                |

| 20                | 20        | UMC*             | Taiwan   | 3760            | 995                   | 834                   | -16               |

| Top 10 Total      |           |                  |          | 171511          | 42335                 | 40310                 | -5                |

| Top 20 Total      |           |                  |          | 221078          | 54732                 | 52284                 | -4                |

| *foundry **fables | S         |                  |          |                 |                       |                       |                   |

Q1 2012 Top 20 semiconductor sales leaders (\$M, includes foundries). SOURCE: IC Insights.

www.solid-state.com

**CHNOLOGY**

SOLID STATE TECHNOLOGY **JUNE 2012**

q

## **news**cont

#### ST's MEMS revenues jump 82% in 2011, but TI holds onto #1 spot

Texas Instruments Inc. (TI, TXN) remained the top manufacturer of MEMS in 2011 with \$779.0 million in MEMS revenues, fending off runners-up Hewlett Packard Co. and Bosch in tough competition for market share, according to an IHS iSuppli MEMS Market Brief report.

TI's MEMS revenue fell 4% from 2010 to 2011, owing in part to supply chain disruptions caused by the 3/11 Japan earthquake. Sales of digital light processing (DLP) MEMS chips kept TI on top in 2011, said Jérémie Bouchaud, director and senior principal analyst for MEMS & sensors at IHS. The DLP business was what helped propel TI to the top spot in 2010, rebounding in the business and education front-projector segment. "Sales are especially strong in China and India," Bouchard notes, where DLP-based projectors have taken market share from LCDs. While front-projection designs are growing, rearprojection DLP TVs have virtually disappeared.

TI also found success in pico-projectors, a still relatively small portion of its MEMS business at <\$50 million of MEMS revenues. The company is the top supplier of picoprojectors for both accessory and embedded projectors such as those found in the Beam handset from Samsung Electronics. The product segment will be a

| Rank      | Company            | 2011<br>Revenue | 2010<br>Revenue | Y/Y<br>Growth<br>(Decline) % |

|-----------|--------------------|-----------------|-----------------|------------------------------|

| 1         | Texas Instruments  | 779.0           | 810.5           | -4%                          |

| 2         | HP                 | 748.4           | 782.1           | -4%                          |

| 3         | Bosch              | 742.2           | 643.0           | 15%                          |

| 4         | STMicroelectronics | 651.6           | 357.5           | 82%                          |

| 5         | Canon              | 368.7           | 354.7           | 4%                           |

| 6         | Panasonic          | 310.1           | 285.7           | 9%                           |

| 7         | Denso              | 286.4           | 262.5           | 9%                           |

| 8         | Knowles            | 270.9           | 191.5           | 41%                          |

| 9         | Analog Devices     | 250.2           | 204.2           | 22%                          |

| 10        | Epson              | 247.7           | 264.7           | -6%                          |

| Total for | Тор 10             | 4,655.1         | 4,156.4         | 12.0%                        |

| Share of  | Total MEMS market  | 59.0%           | 58.5%           |                              |

Worldwide revenue forecast for MEMS IDM and fabless manufacturers, excluding foundries (\$M). SOURCE: IHS iSuppli Research, May 2012.

10 JUNE 2012 SOLID STATE TECHNOLOGY

**ECHNOLOGY**

main growth driver at TI over the next 5 years. TI also introduced a MEMS temperature sensor, or thermopile, in 2011, targeting new handsets and tablets.

Hewlett-Packard also lost 4% of revenues from 2010 to 2011, coming in with \$748.4 million from its MEMS business. HP held the #1 rank from 2005 to 2009, but suffers from price erosion in its MEMS thermal actuators, used in inkjet printheads. HP has lower shipments of disposable printheads as well, since it started migrating to permanent ones in 2005.

Bosch and ST had much larger revenue jumps than the 2 top suppliers, which could indicate more competition for #1 in the near future. The Bosch Group GmbH remained #3 with revenue of \$742.2 million, shooting up 15% from 2010. Bosch saw growth in automotive MEMS as new vehicle safety products ramp up with inertial and pressure sensors. STMicroelectronics saw 82% revenue growth in MEMS – the largest of any in the rankings – to \$651.6 million. **–M.C.**

### Large-area TFT-LCD panel makers see rising shipments, revenues in Q2 2012

Large-area TFT-LCD panel shipments declined in Q4 2011 and again in Q1 2012, but should grow 11% to 189.6 million in Q2 2012, with brands and OEMs increasing orders, and panel makers increasing capacity utilization. Revenues will rebound as well, with panel prices increasing, according to NPD DisplaySearch's Quarterly Large-Area TFT LCD Shipment Report - Advanced LED.

Following a "long-standing over-supply" in the TFT LCD industry, which induced lower panel prices, panel makers are "restructuring and adding new technologies and processes" to improve costs and performance, said David Hsieh, VP, Greater China Market, NPD DisplaySearch. Hsieh sees 2012 as a year of "gradual recovery," when panel prices rebound and shipments increase. Q2 2012 is an example, with double-digit growth in shipment units, shipment area, and revenues. Large-area TFT LCD shipment revenues will grow 14% Q/Q to \$20.6 million.—**M.C.**

### Qmags

# 3.5D interposers: PCB replacement?

#### At the 15<sup>th</sup> Symposium on Polymers for

Microelectronics (May 8-10 in Wilmington, DE), TSMC and Yole Developpement gave plenary presentations on the use of polymeric materials in wafer-level packaging (WLP) from foundry and overall industry perspectives.

The most controversial comment came from TSMC's Doug Yu, senior director of front-end and back-end

technology development, who challenged the current nomenclature and pronounced that the versatile interposer technology should be called "3.5D" instead of 2.5D, since it is and will be capable of much more than the simple 3D packaging stack. Yu's presentation was title "Semiconductor Paradigm Shift and Increased Foundry Roles."

The term 2.5D is usually credited to ASE's Dr. Ho Ming Tong who, around 2009 (or even earlier), declared that we might need an intermediate step towards 3D packaging, since the infrastructure and standards were not yet

ready. The silicon interposer, Tong felt, would get us a major part of the way there, and could be ready sooner than 3D technology, thus the term 2.5D, which immediately caught on with other practitioners.

Yu's new position is that interposer technology actually is more versatile and

thus should be called 3.5D,

since it not only offers a better

### Packaging

www.solid-state.com

thermal solution than 3D integration, but "can someday replace most of the high density PC boards [PCBs]." Yu's position is that this modular silicon technology will need minimal low-density PCB substrates to connect the functions that have

**Dr. Phil Garrou**, Contributing Editor

been fabricated on silicon and will be, in essence, the perfect "fab-centric" solution. Future smartphones and tablets could be made up of such simple 3.5D silicon modules.

Representing Yole Developpement, I presented an overview of polymeric materials in wafer level packaging (WLP), considering the pros and cons of the major material choices — epoxies, PI, PBO, BCB, siloxanes — and the offerings of 25 major suppliers. There have only been 5 major categories of polymers developed for microelectronics in the last 50 years, or one per decade. "If you think you have the next great polymer chemistry for electronics, you better also have deep pockets and patience," I warned attendees.

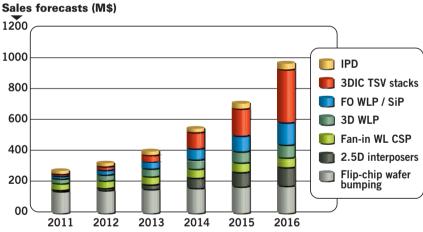

2011 2012 2013 2014 2015 2016 FIGURE 1. Global materials market for wafer-level packaging. SOURCE:

Yole Developpement.

We also looked at the 6 key functions that these materials serve, and where they are used in the 7 key WLP applications.

According to Yole, the polymeric semiconductor material market reached a value of \$274 million last year and will see 26%+ compound annual growth rate (CAGR) over the next 5 years, fueled by the expansion of key WLP applications. ◆

# Epidermal electronic systems

Scientists have developed a new type of ultra-thin, self-adhesive electronics device that can effectively measure data about the human heart, brain waves and muscle activity - all without the use of bulky equipment, conductive fluids, or glues.

Presenting at the MRS Spring 2012 meeting in San Francisco, Nanshu Lu (now at UT Austin) of the John Rogers group at U Illinois Urbana discussed

the groups' recent achievements in epidermal electronic systems. Micro-transfer printing is the method of choice for interconnecting small rigid silicon electronics elements with thin nanoribbons of silicon or metal. Depositing onto a pre-stretched elastomer substrate provides a resting state in which the interconnects are buckled or

canted and can endure up to 100% elongation while imparting ≤1% stress to the rigid circuit elements.

The trick of fabricating extremely thin silicon for flexibility applies to the PDMS polymer substrate as well when the objective is to apply the device to the skin and tolerate stretching and bending without adhesion loss. The thin polymer stability is maintained until it is applied using technology

**MEMS**

similar to that used in applying temporary tattoos. For some device types, the rigid silicon electronics can be eliminated by integrating the

**ECHNOLOGY**

12

**JUNE 2012** SOLID STATE TECHNOLOGY

active device elements into the serpentine interconnects themselves. For development of integrated devices, functions that have been demonstrated include amplifiers, temperature sensors, strain gauges, solar power sources, induction

Mike Fury, Techcet Group

couplers and wireless transmitters & receivers for device control. Current devices, however, use wires to connect to external control and power sources. The only three elements in contact with the skin are gold, silicon and polyimide, all of which are FDA approved.

Also presenting at MRS, Michael Melzer of IFW Dresden extended the family of stretchable electronics from silicon and optoelectronics to now include magneto electronics. Stretchable GMR multilayers are fabricated by depositing GMR thin films on a pre-strained PDMS substrate. Data indicates no loss of magnetic performance through this process to 2.5% strain even though resistance

> starts to rise above 1.6% strain. For greater detection sensitivity, stretchable spin valves were developed using the same process flow as for the GMR multilayers. After some refinement of the process, they were able to achieve 29% strain without losing functionality or sensitivity.

A Gaikwad of City College NY

described a stretchable battery embedded in cloth with Zn and MnO<sub>2</sub> as the active materials. Cracking and delamination due to flexing and stretching was addressed by embedding these materials in a non-conducting nylon mesh in an earlier version. In the new version, a silver coated nylon cloth is used as the substrate for the Zn electrode and separately for the MnO<sub>2</sub> electrode. No delamination or electrical degradation was observed at 100% strain in either the x- or the y-direction. The capacity of 4 mAh/cm<sup>2</sup> was maintained even with this stretching 100% level. 🔶

www.solid-state.com

Next Page

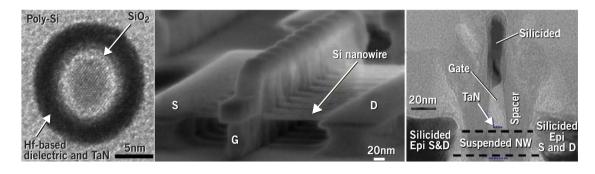

#### TRANSISTORS

# The Next Transistor

PETE SINGER, Editor-in-Chief

We are in the age of the FinFET, which may soon feature III-V channels. Longer term, CNTs and graphene may come into play.

echnologies such as strained silicon, high-k metal gates and FinFETs have enabled smaller transistors, which improve packing density and lower the cost per transistor. Moving forward, the goal is to continue to increase density and reduce cost, but also to improve energy efficiency by limiting leakage and lowering the power supply.

FinFETs, which were rolled into volume production by Intel last year, will likely be the transistor of choice for many years to come, as others follow Intel's lead. Transistors with highmobility channel materials, such as InGaAs, offer tremendous promise, particularly when implemented in a quantum-well FET (QWFET) design (but they can also be implemented in a FinFET).

Eventually, a move to the next "switch" will be required. It might be transistor – a spin-transistor or a tunneling transistor, for example — but it could be some other kind of switch, perhaps based on carbon nanotubes (CNTs) or graphene. Early work shows good results, but it's a long road from the lab to volume production, often many decades.

As Intel's Mark Bohr noted in his keynote address at the 2011 International Electron Devices Meeting (IEDM) in December, traditional MOSFET scaling has served the industry well for more than three decades by providing continuous improvements in transistor performance, power and cost. However, with the growing market interest in mobile products with long battery life, and growing need to lower the energy cost of running large data centers, there is more interest in reducing transistor leakage current and operating voltage [1].

Intel's announcement in May of last year was

historic in the world of transistor evolution. The announcement was that the 3-D transistor design called tri-gate, first disclosed by the company in 2002, would be moved into high-volume manufacturing at the 22nm node in an Intel chip codenamed "Ivy Bridge." In the second quarter of this year, Ivy Bridge will ramp to nearly 25% of Intel's processor production.

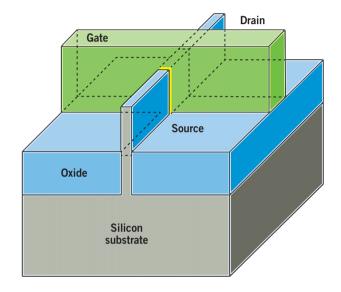

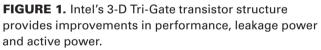

Offering improvements in performance, leakage power and active power, tri-gate transistors — also called FinFETs because of their "fins" as shown in **Fig. 1** and **Fig. 2** — are in the general category of multi-gate transistors that have fully depleted operation. Fully depleted devices can offer three forms of improved transistor operation: lower off-state leakage, higher performance and/or lower active power [1]. The tri-gate structure wraps

www.solid-state.com

| Next Page

TRANSISTORS

the gate electrode around three sides of tall and narrow silicon fin, providing improved electrostatic control of the channel region compared to a traditional planar device. The improved channel control results in a steeper sub-threshold slope which can provide up to a 10X off-state leakage reduction. The improved channel control also enables gate length scaling, which benefits both area scaling and reduces gate capacitance.

Alternately, the tri-gate device can be operated at a lower threshold voltage with the same leakage as a planar device. This lower  $V_T$  can be used to provide either higher performance or allow lower operating voltage for reduced active power. 22nm tri-gate transistors provide a 37% gate delay improvement at 0.7V or a 50% active power reduction at constant performance when compared to Intel's 32 nm logic technology on a comprehensive set of benchmark circuits.

#### Long live the FinFET!

With the advantage of FinFETs firmly established, the rest of the industry is following suit. "Today, what the foundries are focused on, GLOBALFOUNDRIES in particular, is the FinFET," said David Bennett, vice president of alliances for GLOBALFOUNDRIES, speaking at SEMI's Advanced Semiconductor Manufacturing Forum (ASMC) in May. "The initial introduction

will be around 20nm-type design rules. Once we get 'on the fins,' there's going to be an absolute, strong motivation across the entire IP ecosystem to maintain that architecture and to continue to drive price/performance and cost down. We'll do that through improved dimensional controls on heights and profiles of the fins, as well as materials, such as III-V channels. We'll also really work on V<sub>dd</sub> scaling."

Subu Iyer, IBM Fellow and Chief Technologist at the Microelectronics Division, IBM Systems &

CHNOLOGY

**FIGURE 2.** This image shows the vertical fins of Intel's tri-gate transistors passing through the gates.

| Contents | Zoom in | Zoom out | Refer a Friend | Search Issue

Technology Group, also spoke at ASMC. "I dare say that everybody in the next generation, 14/15nm or whatever nanometer technology we're talking about, is going to be using FinFETs," he said. But he also noted that, for the first time in the industry's history, the cost per transistor has not decreased with a new technology generation. "If you look carefully, it does not buy us the density that we're used to. It's not the 0.7 scaling that doubles the number of circuits per unit area," he said. "It's also not really buying us power. If we were following Danard's scaling, which he proposed back in the late '70s, we should have been sitting around 300 or so mV of  $V_{dd}$  supply. We're not. Why? Because, from a circuit perspective, we don't have noise immunity at those low voltages. That's a problem," he said.

All of these factors have many calling for a new way of thinking. "The next step of innovation, and the next step for our R&D dollars, has to be in figuring out what are we going do to actually reduce power dramatically. If you look at where we are today, the power/circuit – even though it's very impressive for all of our handheld appliances and so on – is still way, way out of the league of biologically competing systems, for example," Iyer said. "I believe quite honestly that there is something that is going to come from some other direction that is really going to upset this whole apple cart." He

> noted that the supercomputer Watson may have won the Jeopardy match, but consumed 3-4 kW vs the 20W of brain power used by the two human competitors.

### Strained silicon and III-V channels

Straining semiconductor material within a transistor increases the mobility of the electrons flowing through it, leading to either faster or lower-power devices than could be built with

Previous Page

Oma

transistor drive currents at given off-currents. The researchers say these strain engineering techniques are extendable to even smaller transistors.

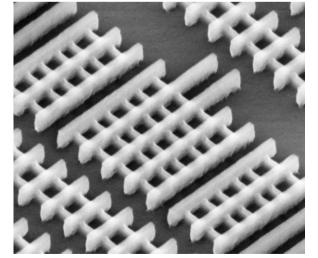

However, still higher electron mobilities are required to enhance transistor performance at lower supply voltages. Figure 3 shows several different "flavors" of transistors with III-V channels that offer this high-mobility.

At IEDM, an Intel-led team unveiled tri-gate FinFET-type quantumwell InGaAs MOSFETs with 30-nm gates that deliver the best electro-

FIGURE 3. Cross-sections of common types of device structures build with III-V channels. Source: Shinichi Takagi, University of Tokyo.

unstrained silicon.

As transistors shrink to nanoscale dimensions, however, variability in performance is growing and high manufacturing yields are getting harder to achieve. According to reports provided in advanced of the VLSI Symposium, to be held June 12-15 in Honolulu, two main reasons are atomistic doping effects (i.e. the discreteness of doping becomes important in devices with nanoscale dimensions) and manufacturing-process-induced variations. In transistors for low-power applications, thin-body structures have been shown to suppress off-state leakage current without the need for doping, and also to reduce sensitivity to gate-length variations. But whether these benefits can be achieved for high-performance applications is unclear, because it is difficult to strain thin-body structures effectively to enhance performance.

At the VLSI Symposium, IBM Alliance researchers will describe how they managed to do this for transistors at the 22nm CMOS technology node. The strain was enabled by in-situ-doped raised-source/drain (implant-free) and strainedchannel processes. The devices achieve record-high static performance of any III-V MOSFET. Two key metrics are subthreshold slope and drain-induced barrier lowering, or DIBL. Long-channel devices exhibited a subthreshold slope of 66 mV/decade, close to the theoretical minimum of 60 mV/decade, while DIBL of short gate length devices was significantly improved over best-in-class planar III-V MOS devices. At the upcoming VLSI Symposium, University of Tokyo researchers will report the first sub-60nm III-V n-channel MOSFETs on silicon substrates with excellent control of short-channel effects and suppression of off-state leakage current. The devices, which are made from InGaAs- and InAs-on-insulator on silicon substrates, enable higher transistor on-state current thanks to carrier mobility enhancement and to reduction of parasitic resistance.

#### **Beyond 10nm**

With current scaling approaches, gate lengths as small as 10 nm are likely to be achieved. But is that the end? A Purdue-led team decided to try to find out. Through atomistic simulations, they looked at several promising device designs and

www.solid-state.com

SOLID STATE TECHNOLOGY **JUNE 2012** 15

#### TRANSISTORS

material combinations: carbon nanotubes, graphene nanoribbons, and III-V and silicon ultra-thin-body devices and nanowires (graphene is a one-atomthick sheet of carbon atoms with an exceptional set of properties that give it great potential for electronics applications). They performed extensive numerical simulations of intrinsic characteristics, limiting factors and design impacts. The simulations show that a) with careful engineering, good sub-threshold swing can be obtained for many of these device alternatives for gate lengths down to 8 nm; b) non-planar devices can provide good tions, they performed better than theory predicts they should have. Single-walled CNTs are a possible replacement for silicon but it hasn't been clear that sub-10-nm gate length CNT-based transistors can avoid short-channel effects that degrade performance. The IBM researchers have shown that such aggressively-scaled CNT-based transistors are, in fact, feasible. They built devices that achieved more than four times the current density (2.41 mA/ $\mu$ m) of the best competing silicon device, at a low operating voltage of 0.5 V. The researchers speculate that theoretical predictions were

performance even at 5-nm gate lengths; and c) when the bandgaps are the same, carbon nanotube FETs and smalldiameter silicon and III-V nanowires exhibit

**FIGURE 4.** The ultimate 3D transistor might be a silicon nanowire with the gate wrapped entirely around it. The dots in the left-most image are individual atoms. Source: IBM.

roughly the same performance, but the details of the potential profile and the onset of interband tunneling are critical.

In recent work, IBM used synthesized graphene to produce record radio-frequency (RF) performance from transistors (reported at IEDM 2011). The IBM team demonstrated a 280-GHz cut-off frequency in a 40-nm gate-length FET, the fastest ever reported from synthesized graphene. They also achieved record high output current (5 mA/  $\mu$ m) and transconductance (2 mS/ $\mu$ m) in synthesized graphene FETs (albeit with longer gate lengths), and explored the impact of gate dielectric selection. These devices also demonstrated an appreciable RF voltage gain of 10 dB.

The first experimental demonstration of sub-10-nm transistors made from carbon nanotubes (CNTs) was also conducted by IBM. The CNT-based transistors not only demonstrated better current-drive performance than conventional silicon devices under similar bias condiexceeded because the transistor gate modulates the charge not only in the channel but in the contact regions as well, which had not been considered previously.

As exciting as the potential of new materials may be, IBM's Bernie Myerson, speaking at ISS earlier this year, sounded a cautionary note. "There are carbon nanotubes, and people have made transistors out of them. But when you really get serious about making these things into technology, you really have to start looking at the genuine dimensions you want to use them at, what you're going to do with them and how they're going to behave. It's really great to see all these picture where people make a device and they get some numbers from them, but you have to make about 10 billion of them work to be competitive with current silicon.  $\blacklozenge$

#### References

1. Mark Bohr, "The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era," IEDM 2011, p. 1.1.1.

CHNOLOGY

I Next Page

#### **3D INTEGRATION**

# Thin die stacking for wide I/O memory-on-logic

#### THORSTEN MATTHIAS, JÜRGEN BURGGRAF DANIEL BURGSTALLER, MARKUS WIMPLINGER, PAUL LINDNER, EV Group, St. Florian am Inn, Austria

Wide I/O DRAM is pushing thin wafer processing into high-volume manufacturing readiness.

ide I/O interface memory-on-logic has the potential to be the long awaited killer application that will boost through silicon vias (TSVs) and 3D integration into high-volume manufacturing. Information transfer is rapidly transforming from text based communication to picture and video-based communication, which creates an insatiable demand for bandwidth. The convergence of smart phone and media server requires DRAM bandwidth >12GB/s in order to allow streaming of 1080p HD videos onto large displays. Conventional memory-logic interfaces ("narrow I/O interface") consume too much power at the input/outputs (I/Os) and do not allow scaling to multiple hundreds or thousands of I/Os. TSVs enable a significant power reduction at the I/O. Current DDR3 technology consumes 40mW per pin, whereas I/Os based on TSVs only consume  $24\mu$ W per pin [1]. This power reduction by 1000x gives chip designers the freedom to implement 512 I/Os with the next device generation.

Wide I/O memory-on-logic is one of the most challenging 3D applications for various reasons:

- Form factor is crucial since mobile applications are the primary drivers.

- The individual memory layers require a thickness of

50µm or less.

• For memory, bandwidth and power consumption are not the only important factors; total data storage capacity is at least equally important.

DR. THORSTEN MATTHIAS is business development director at EV Group, St. Florian am Inn, Austria, ph: +43 676 84531148, e-mail: t.matthias@evgroup.com. JÜRGEN BURGGRAF is senior process technology engineer at EV Group. DANIEL BURGSTALLER is product manager at EV Group. MARKUS WIMPLINGER is corporate technology development and IP director at EV Group. PAUL LINDNER is executive technology director at EV Group.

www.solid-state.com

ECHNOLOG

Qmags

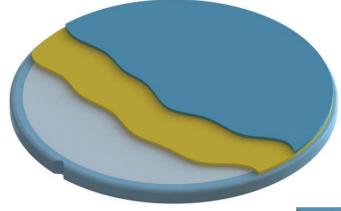

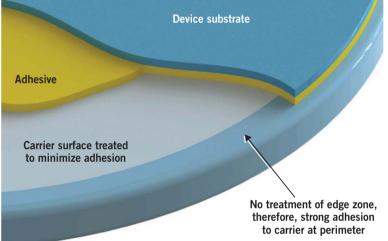

**3D INTEGRATION**

**FIGURE 1.** ZoneBOND<sup>™</sup> carrier schematics and close-up

#### **TSV integration**

For these reasons, multiple memory dies have to be stacked. Initial designs require 4 layers, but 8+ layer stacks will follow very rapidly. In terms of chip stacking with TSVs, wide I/O DRAM will initially require stacking of 4 ultra-thin memory dies plus 1 logic controller. Companies have already successfully implemented manufacturing of memory-on-logic, as evidenced by recent wide I/O DRAM shipments. The key to success was a paradigm shift in TSV manufacturing. In the past, a "one solution fits all" approach had been envisioned by the industry, where an identical TSV manufacturing process would support power devices, image sensors, stacked memory and GPU-on-CPUs. For wide I/O memory-on-logic, however, specialized TSV manufacturing processes are required.

Reliable 3D integration schemes have now been developed, following system engineering principles where all aspects of the device manufacturing are considered simultaneously. In the past, engineers tried to use identical processes-of-record for frontside and backside RDL processes, leaving many integration issues to be addressed during TSV manufacturing. However, it turns out that co-engineering backside RDL and TSV manufacturing is the easier road to success. There are now multiple integration schemes for memory-on-logic.

Cost is, of course, another important factor beyond bandwidth, power and total storage capacity. The cost of TSV manufacturing correlates with the depth and the aspect ratio of the via. The cycle times for the process steps for via etching and via filling correlate with via depth and aspect ratio. For memory, silicon real estate comes at a premium so the TSV area consumption has to be minimized. The only way to minimize the TSV diameter and to keep the aspect ratio low is by reducing the TSV depth. Memory stacking with TSVs inevitably leads to the requirement to process ultra-thin wafers on frontand backside.

#### Thin wafer processing

Co-engineering of backside RDL, TSV and die stacking processes has changed the primary requirements for thin wafer processing. Temporarily bonding the device wafer to a carrier wafer enables wafer thinning and backside processing [2]. After backside processing, the thin device wafer is separated from the carrier. One key requirement is that this thin wafer is stackable, meaning that a) the wafer has to be particle and residue free and b) the thin wafer surface chemistry and physics has to be compatible with bonding and especially underfill processes. As memory-on-logic devices have at least 5 (without interposer) or 6 die levels (with interposer) both sides of the thin wafer have to be particle and residue free. Thermoplastic adhesives have the advantage that they allow single-wafer cleaning after debonding and that there is no modification of the device wafer passivation.

Stacking of memory sub-stack to logic controller is

18

usually performed by chip-to-chip (C2C) or chip-to-wafer (C2W) stacking as memory die and logic die do not necessarily have the same size. Stacking of the memory dies (i.e., the assembly of the memory "sub-stack") can be performed as C2C, C2W and also wafer-to-wafer (W2W). Stacking of memory is well suited for W2W as all the dies have the same size, the volume is high and the yield is high.

Stacking of thin wafers can be performed either after the thin wafer is debonded or while the thin wafer is still bonded onto a carrier wafer. Bonding of the thin wafer while still mounted to the carrier wafer allows comfortable and safe wafer handling, but adds some complexity to the wafer bonding process. For ultra-thin wafers, stacking before debonding might be necessary. For C2W this means dicing while the die is still on the carrier, which destroys the carrier and adds to the overall costs. W2W allows re-using the carrier wafer.

Cu-Cu bonding is the most promising process for memory stacking. Current activities are targeting a reduction of the bond temperature in order to reduce cycle time and cost of ownership, but also in order to facilitate permanent Cu-Cu bonding prior to debonding from the carrier.

Stacking of dies is typically performed by the OSAT whereas thin wafer processing is performed by the foundry. In either case, it is necessary to ship the thin wafers. Shipping of thin wafers on a film frame is quite well established, but nevertheless shipping of ultra-thin wafers with less than  $50\mu$ m thickness results in small yield hits. As the wafers are very valuable at this point of the manufacturing processes (after complete front- and backside processing) the cost of yield is non-negligible.

The alternative approach is to ship the thin wafers while still securely bonded to the carrier and debond directly at the assembly site. This requires an innovative supply chain where the foundry performs temporary bonding and the OSAT performs the debonding. Such a supply chain is only feasible with the existence of standards for bonding and debonding processes and equipment.

As previously mentioned, new TSV manufacturing processes are specifically engineered for different products, such as power devices or wide I/O DRAM, which typically means that different optimized adhesives are being

#### FIGURE 2. 1st step: Edge zone release (EZR®) ZoneBOND™ debonding is a 2-step process: during the Releases adhesives at the stack edge release step the adhesive 2nd step: Edge zone debond (EZD®) edge zone is Separation at the carrier; dissolved; the No vertical force to device wafer thin device wafer is separated from the carrier during the debond step.

#### www.solid-state.com

ECHNOLOGY

The New PRESTO®

#### Thermodynamic Power

Process Temperature Control Solutions for MOCVD, HB-LED

Julaba

www.julabo.com

(800) 458-5226

RATURE CONTROL COMPAN

**JUNE 2012**

SOLID STATE TECHNOLOGY

19

**3D INTEGRATION**

used. LowTemp<sup>®</sup> ZoneBOND<sup>™</sup> debonding brought a revolutionary breakthrough toward standardization [2]. With this technology debonding is a function of the carrier, which makes the debonding process independent of the used adhesive. Figure 1 shows the ZoneBOND carrier wafer. In the center is a zone with reduced adhesion, whereas the edge zone provides full adhesion. Figure 2 shows the debonding process. First, the adhesive in the edge zone is dissolved in single wafer mode during the Edge Zone Release (EZR®) process. Then the device wafer is separated from the carrier wafer during the Edge Zone Debond (EZD®) process. The thin wafer is mounted on a film frame for subsequent singulation and assembly. The physical separation process happens at the interface between carrier wafer and adhesive film. During this debonding, the bumps are safely embedded in the adhesive film. No force is applied to the bumps during debonding. An open platform has been established which enables a versatile supply chain for ZoneBOND materials from multiple adhesive suppliers.

Temporary bonding/debonding was introduced for compound semiconductors more than 10 years ago, but in order to be ready for memory manufacturing, major changes to the equipment were required. The new EVG850 "XT Frame" Temporary bonding and debonding system is optimized for high volume memory manufacturing.

Wide I/O DRAM was the driving force that pushed TSV manufacturing in general and thin wafer processing in particular into high volume manufacturing readiness. For thin wafer processing, LowTemp ZoneBOND has enabled a standardization of equipment and processes. The open platform for adhesives has generated a versatile supply chain with multiple adhesive suppliers. The new equipment generation features integrated advanced process control on the module level, high throughput and optimized wafer cassette logistics. ◆

#### Acknowledgement

ZoneBOND<sup>™</sup> is a trademark of Brewer Science, Inc. LowTemp<sup>®</sup>, EZR<sup>®</sup> and EZD<sup>®</sup> are registered trademarks of EV Group.

#### References

- 1. B. Patti, Lessons learned, Proc. IMAPS DPC 2011

- 2. T.Matthias et al., *Room temperature debonding An enabling technology for TSV and 3D Integration*, Proc. IMAPS DPC 2012

www.solid-state.com

Next Page

#### RELIABILITY

# Bias temperature instability mechanisms

CHRISTOPHER L. HENDERSON, Semitracks, Inc., and DAVID W. ROSE, Keithley Instruments, Inc.

NBTI is considered to be one of the most difficult reliability challenges facing the semiconductor manufacturing community today.

ias temperature instability (BTI), particularly negative BTI (NBTI) in p-channel transistors, affects small feature size devices and is guite difficult to reduce or eliminate. As feature sizes become smaller, the effects of NBTI become more pronounced, resulting in increases in threshold voltage and decreases in drain current and transconductance in p-channel devices. NBTI results from a positive charge buildup in p-channel transistors. It occurs at low negative gateto-source voltages and does not result in an increase in gate leakage current. Rather, it affects off-state drain-to-source leakage and reduces the drive current. Generally, this problem is worse than standard hot carrier degradation because it results in permanent interface traps being generated, reducing device lifetime.

Although the NBTI phenomenon has been well known for years, it was a controllable problem in earlier CMOS devices. The problem resurfaced around 1990 with the introduction of dual-doped polysilicon gates, but hot carrier effects were more dominant during that timeframe. Hot carrier effects were brought under control by drain and channel engineering, and voltage reduction. Now, aggressive scaling has made NBTI more problematic than hot carrier effects.

NBTI occurs mostly in p-channel MOSFETs when either (a) a negative bias is applied to the gate, or (b)

Activated by negative gate voltage and temperature Holes apparently catalyze reaction Hydrogen (of some form) involved in degradation kinetics Now a larger problem than hot carrier degradation

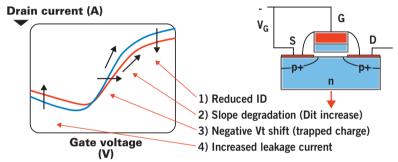

FIGURE 1. Typical results before and after a bias temperature stress on a 0.25-micron channel length transistor. Stress applied at 250°C for 50 hours at an electric field of 4.3 megavolts/cm.

> the DUT is used at an elevated temperature. The effect is much more significant when both a negative bias AND an elevated temperature occur. It results from holes migrating to the silicon-oxide interface and is manifested by the current-voltage characteristics becoming unstable. This is accompanied by reduced drain current in the linear saturation regime, slope degradation that indicates an increase in interface trapped charge, negative threshold voltage shifts that indicate positive trapped charge, and an increase in off-state leakage current in certain instances (Fig. 1).

Holes apparently catalyze the reaction, so holes are needed at the silicon-oxide interface. Researchers believe that hydrogen in some form is involved in

CHRISTOPHER L. HENDERSON, Semitracks, Inc., and DAVID W. ROSE, Keithley Instruments, Inc.

www.solid-state.com

RELIABILITY

the degradation kinetics. This phenomenon is not as prevalent in n-channel MOSFETs because they are electron majority carriers, but they can have the less common PBTI problem. One possible reason why PBTI is less of a problem is that nitrogen is used in p-channel transistor gate oxides to block boron penetration.

NBTI typically increases with decreasing channel length. This is due to the increased contribution from the source and drain overlap regions. It can be quite pronounced in deep submicron technologies. At 90nm channel lengths, the change in threshold voltage can exceed 100mV and the change in drive current can approach 10% using the stress conditions in Fig. 1. In addition, the off-state leakage for the transistor after stressing is typically between one and two orders of magnitude higher than before stressing.

NBTI effects increase as oxide thickness decreases. For example, threshold voltage  $(V_{TH})$  can increase by almost an order of magnitude as oxide thickness is decreased from 40 angstroms to 20 angstroms.

#### Important NBTI processes

Three processes associated with NBTI and its measurement should be understood:

- Relaxation processes

- Fast vs. slow measurement methodologies

- Relationship of  $V_{TH}$  shifts with interface traps

Through a charge pumping measurement technique, Vincent Huard [1] of ST Microelectronics has shown

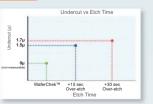

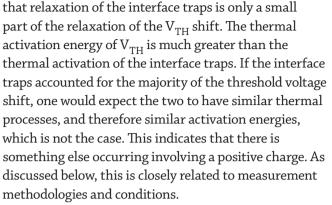

The measurement techniques for NBTI are somewhat different than for other hot carrier mechanisms. A typical measurement scenario uses a parameter analyzer, with the test taking about 10 seconds. One can then extract  $DV_{TH}$  using SPICE models and extrapolating down from the maximum slope to the x-axis. Another technique is to hold the gate voltage constant for the majority of the measurement time, change it for a few milliseconds and add a drain bias during this time, as shown in the two graphs on the lower portion of Fig. 2. In this scenario, the charge in the gate does not have time to relax. One can measure the drain current and then extrapolate back to get the threshold voltage. If you compare the conventional DC technique with an "on the fly" measurement, the change in threshold voltage is higher by a factor of ten when using an "on the fly" method. More importantly, there is also a change in the slope. This relates to whether the mechanism involves

ΔV. "On the fly" technique 10 × difference **Conventional DC technique** V<sub>G</sub> "On the fly" technique VD Stress time (sec) V<sub>stress</sub> 25mV Time (sec) Time (sec)

In contrast to a power law dependency, sometimes a linear-log time dependence in DV<sub>TH</sub> is observed. This eliminates the possibility of a drift component, which researchers initially thought was occurring. Mickael Denais [2] discovered that the threshold voltage shift is correlated with the amount of hole current injected. This can be measured through carrier separation techniques. The results of his study point to a positive charge rather

interface traps or fixed charge.

FIGURE 2. Large differences in DV<sub>TH</sub> shifts are observed between "fast" and "slow" measurements. V. Huard, IRPS 2004.

ECHNOLOGY

Previous Page

www.solid-state.com

Next Page

#### RELIABILIT

FIGURE 3. Stress-measurement delay time and test temperature clearly affect results.

than interface traps. This charge could be protons, positively charged silicon, or even H<sub>3</sub>O+. Denais also verified relaxation of the  $V_{TH}$  shift, the magnitude of which is greater at higher positive voltage but eventually reaching a saturation level, indicating this is most likely a positive charge process.

#### Implications on measurement methods

Dhanoop Varghese [3] and his co-workers have studied the effects of measurement conditions on NBTI and its  $V_{TH}$  degradation. It was found that for a fixed gate voltage, the slope of the  $\mathrm{DV}_{\mathrm{TH}}$  vs. stress time curve varies with the drain voltage used in the measurement, stress temperature, and stress-measure delay time. The slope is greater for higher temperatures, longer delay times, and lower drain (measurement) voltages. A similar relationship is also apparent when examining the interface traps, but the effect is much less pronounced.

Varghese also found there is an Arrhenius dependency in this behavior by measuring the time delay effect at two different temperatures. He modeled this phenomenon using a Reaction-Diffusion simulation with H<sub>2</sub> hydrogen, showing there is good correlation between the data and the simulation. This indicates that the underlying mechanism is not hole trapping or charge trapping but rather some form of diffusion. The slopes of the lines that fit the data indicate molecular hydrogen or  $H_2$  as the species.

These results underscore the need to make ultra-

fast measurements. This can be seen clearly in Fig. 3, which shows the threshold voltage shift over many orders of magnitude of time. Notice that there is a change in slope below 2 to 4 seconds. The increase in slope suggests a dispersive-type process or some type of trapping and detrapping. When the time is longer, there is more of a diffusion phase, i.e., NBTI is a reaction-diffusion process. Holes react at the interface, releasing something, most likely hydrogen, which then diffuses. The process is diffusion limited rather than reaction limited. The Power Law takes over for the diffusion process. The process follows Arrhenius behavior at longer times, but the temperature effect is nonlinear.

Varghese and his group reached the conclusion that under most conditions these phenomena are strictly related to interface traps. Arrhenius plots of data collected for devices having different oxide thicknesses, different charge doses, different electric fields, and different doses of nitrogen, all fall nicely on a line that indicates a thermal activation energy of 0.6 eV. They also get an n value of about 1/6, which is consistent with molecular hydrogen diffusion.

#### Conclusions

Researchers agree on several aspects of NBTI. NBTI is a hole catalyzed reaction that has a pronounced effect on p-channel transistors, and is quite difficult to reduce or eliminate, particularly in devices with short channel lengths. NBTI field dependence is due to the reaction phase, not a field drift component. The damage increases the threshold voltage shift. Interface traps are certainly involved, but there may be another component such as fixed charge as well.

#### References

- 1. V. Huard et al, International Reliability Physics Symposium Proceedings (42nd Annual IEEE IRPS), 2004, pp 40-45, IEEE International.

- 2. M. Denais et al, presented at IEDM 2004, in IEEE Transactions on Device Materials Reliability, vol. 4, 2004. pp 715-722, IEEE International.

- 3. D. Varghese et al, "Material dependence of hydrogen diffusion: Implications for NBTI degradation," in IEDM Technical Digest, 2005, p. 705, IEEE International.

www.solid-state.com

SOLID STATE TECHNOLOGY **JUNE 2012** 23

| Search Issue

| Next Page

#### PACKAGING

# TSV inspection in 3D advanced packaging applications

REZA ASGARI, Rudolph Technologies, Inc., Flanders, NJ.

Laser triangulation provides fast, accurate and repeatable 3D measurement of TSV nails and microbumps.

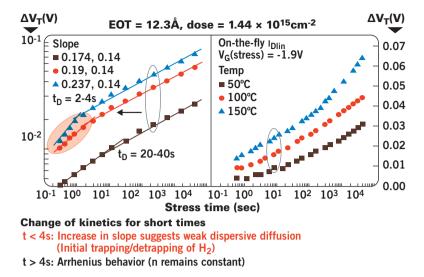

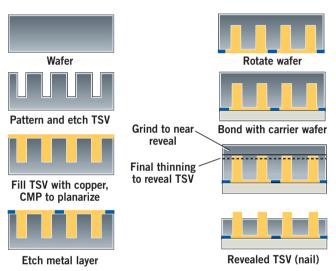

hree-dimensional integrated circuits (3D ICs) using through silicon vias (TSVs) are gaining momentum as more and more technology challenges are being successfully addressed. Development projects are ongoing at semiconductor companies around the globe and some manufacturers have 3D ICs in production. 3D ICs offer several advantages such as faster communication, higher I/O, smaller footprint, lower power consumption, and more. It is safe to assume 3D packaging is here to stay.

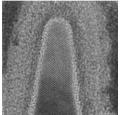

TSV technology is a key technology for 3D ICs. Vias are etched into the silicon and filled with copper. The back side of the wafer is then thinned, typically using a combination of grinding and CMP, to reveal the end of the copper fill above the wafer surface (**Fig. 1**). This is often referred to as a copper nail. The height of these nails typically varies from 1 micron to 5 micron. A copper nail on one IC and a micro bump on another are used to stack two ICs to develop a 3D device. The height and co-planarity of the nails are critical parameters that must be correct to ensure the connectivity and, therefore, require inspection and measurement (Fig. 2).

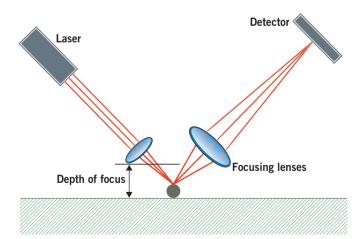

Laser triangulation is a measurement technique that uses a scanned laser to collect 3D data points which can then be used to build a 3D model of the surface features. The speed and accuracy of laser triangulation have made it the dominant technology for three-dimensional characterization of solder bumps

FIGURE 1. TSV nails are formed by filling vias, usually with copper, etched into the wafer. The wafer is then flipped and mounted to a carrier wafer. A combination of processes is used to remove material from the wafer surface, leaving the ends of the copper fill protruding above the surface. These TSV nails will be matched to corresponding solder bumps on a stacked wafer or die to provide electrical connections. (Courtesy of Sematech)

used in conventional packaging techniques such as flip chips. Microbumps and TSV nails used in 3D ICs are typically smaller, more closely spaced and more numerous, having diameters and heights as small as a few micrometers. The number of bumps and nails used in 3DIC schemes has grown explosively, with current roadmaps calling for as many as 1,000,000 per die and 60 million per wafer.

Existing metrology tools are significantly challenged

**REZA ASGARI** is wafer scanner product manager, Rudolph Technologies, Inc., Flanders, NJ.

24 **JUNE 2012** SOLID STATE TECHNOLOGY

www.solid-state.com

Contents | Zoom in | Zoom out | Refer a Friend

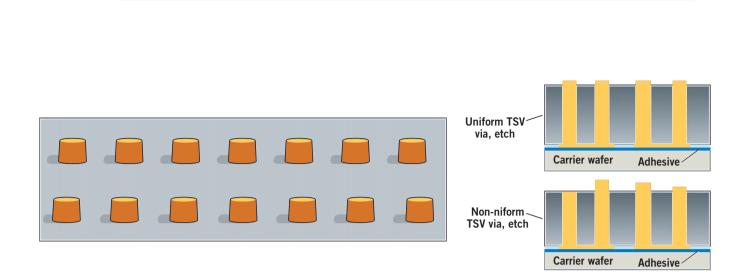

**FIGURE 2.** On the left is an illustration representing TSV nails. The diagrams on the right illustrate one type of fault: non-uniform etching has created vias of varying depths, causing variations in nail height and failure of some nails to reveal at all.

to provide the speed and precision required to maintain sufficiently narrow process windows and ensure high yields. Heights of only a few microns require submicron 3D measurement precision. Diameters as small as 5 microns pose equally daunting challenges for 2D measurement. The large number of features places a heavy load on data storage and processing facilities. Finally, the measurement system must strike an optimal balance between precision and throughput if it is to be used in production.

Previous Page

The inspection system (Wafer Scanner<sup>™</sup> 3880, Rudolph Technologies) uses laser triangulation for 3D measurements of bump height and co-planarity (**Fig. 3**). A laser on the wafer surface at an angle of 45 degrees and focused to a spot size of 5 µm scans a line 1.4 mm in length on the wafer surface while the

**FIGURE 3.** Laser triangulation uses a finely focused laser and a position sensitive detector to measure feature height.