EQUIPMENT • MATERIALS PACKAGING • TEST SEMICONDUCTORS • LED PV • EMERGING MARKETS

## The Power of $[\mathcal{X}]$

## The Power of

#### New Programs for 2013

- Silicon Innovation Forum—Top strategic investors review an exciting line-up of new and emerging companies

- A conversation on semiconductor R&D with leaders from imec, SEMATECH and CEA-Leti

- 450 mm Wafer Processing: Opportunities and Prospects

- The latest requirements on nonplanar architectures, stacked 3D ICs, the two paths for lithography, nano defect detection, silicon photonics, printed/flexible electronics, MEMS, LEDs

- Keynote address: Ajit Manocha, CEO, GLOBALFOUNDRIES

Wafer Processing Packaging Test [SENICON West] Photovoltaic Silicon Photonics MEMS-LEDs

REGISTER NOW and get ready to be a part of the biggest event in microelectronics manufacturing— SEMICON<sup>®</sup> West 2013!

- Access more than 50 hours of technical programs focused on the critical issues in microelectronics manufacturing

- 450 mm, 3D IC, next-generation lithography, test, contemporary packaging, advanced materials, and more

- Discover technologies, materials, and manufacturing solutions for LEDs, MEMS, plastic electronics, and other emerging and adjacent markets

- Connect with technical experts and find solutions that move your ideas from the lab to the fab

Connect to the Power of [X]— Connect to the Power of SEMICON West

**July 9–11** Moscone Center San Francisco, California www.semiconwest.org

SEMICON West is brought to you by:

**ADVANTEST**

JUNE 2013

R

PennWell

## SOIDSIGNE TECHNOLOGY Insights for Electronics Manufacturing

Monitoring Parametric Variation P. 19

Eliminating Nonvisual Defects P. 22 SEMICON WEST Preview P. 29

Sub-20nm STI Etching PM

#### A quick start guide to MAXIMIZING our interactive features.

Peruthett

**LIMITED TIME OFFER: \$995** Register at www.theconfab.com/register Enter code AD13

June 23-26, 2013 Encore at the Wynn, Las Vegas

The ConFab's 2013 conference "Filling Fabs of the Future," takes an executivelevel look at significant challenges to sustained growth, including:

- Improving R&D Efficiency

- Why 2.5D and 3D Semiconductors are **Changing Everything**

- CMOS Scaling Beyond 10nm

- Inside Today's Chips: What Teardowns Reveal

- 3D Integration's Killer App

- Innovation, Specialization and Performance **Drive Semiconductors**

- The "New" IC Industry Cycle Model

- Embedded Die Packaging: The Next Step in 3D System-in-Package Miniaturization

- A Review of the Cost and Technology Needed to Implement Next Generation **Device Technology**

- And more!

#### **KEYNOTE SPEAKERS**

#### **MONDAY, JUNE 24, 2013**

**Technologies and Business** Strategies of the Future IT Industrv

Mr. Yoon-Woo Lee Executive Advisor Samsung Electronics Co., Ltd.

#### **Orthogonal Scaling to Fill** Today's Fabs in the Future

Mr. Subu Iver IBM Fellow IBM Systems & Technology Group

For a preview of the outstanding line-up of sessions and speakers at The ConFab 2013, please visit http://www.theconfab.com/conference. **LIMITED TIME OFFER: \$995 REGISTER AT WWW.THECONFAB.COM/REGISTER**

CONNECT. COLLABORATE. CREATE.

www.theconfab.com

JUNE 2013 VOL. 56 | NO. 4

The Applied Centura AdvantEdge Mesa silicon etch system brings Angstrom-level precision to shallow trench isolation (STI), buried bit/word line, and double patterning at 32nm and below.

#### FEATURES

**ETCHING** | The challenges of sub-20nm shallow trench isolation etching

Major challenges for sub-20nm STI etching include intra-cell depth loading, across-wafer uniformity, etch profile control near the wafer edge, and propensity for pattern collapse. *Hui Zhou, Xiaosong Ji, Sunil Srinivasan, Jim He, Xuefeng Hua, Ankur Agarwal, Shahid Rauf, Valentin N. Todorow, Jinhan Choi, and Anisul Khan, Applied Materials, Inc., Sunnyvale, CA*

## 19

COVER

#### **RELIABILITY** | Statistical variation monitoring for production control

The sources of parametric variation are reviewed, with an eye on why these issues become worse as the technology is scaled and how this variation can be monitored and controlled. *Timothy Turner, College of Nanoscale Science & Engineering (CNSE), Albany, NY.*

#### INSPECTION | Detection and elimination of a yield-critical

#### non-visual residue defect

A post-wet clean residue that was causing a yield issue was found and eliminated. *Soonhaeng Lee, Wiseok Kang and Hobong Shin, Samsung Electronics Gyeonggi-Do, Korea; Sungjin Cho, Jaeyoung You and Jeff Hawthorne, Qcept Technologies, Fremont, CA.*

## **SIMULATION** | Multiphysics simulation accelerates the development of electrochemical etching

A team of researchers from Germany use multiphysics simulation to elucidate the impact of important process variables in the electrochemical etching of silicon and make progress toward the integration of the process for commercial applications. *Jennifer A. Segui, COMSOL, Inc., Billerica, MA*.

#### BUSINESS | A Preview of Semicon West 2013

Hot topics to be discussed at the show include dynamic changes to R&D processes, tools, technical challenges, and funding/business models. *Debra Vogler, SEMI, San Jose, CA*.

#### COLUMNS

- **3** Editorial | The value of innovation, *Pete Singer, Editor-in-Chief*

- **12** Packaging | NVIDIA's GPUs; Patent analysis, Phil Garrou, contributing editor

- **13 MEMS** | Inside biomedical devices, *Denise Rael, contributing editor*

- **41** Industry Forum | A new era in equipment development, *Tim Bowe, CEO, Foliage*

#### DEPARTMENTS

- 2 Web Exclusives

- 4 News

- **33** New Products

- 36 Ad Index

## Online@www.solid-state.com

#### Web Exclusives

#### Solid State Watch

Tune in to our new, weekly newscasts to get caught up on leading industry headlines. http://bit.ly/17LtRQs

#### **Reinventing Intel**

The semiconductor chip giant revealed plans to branch out beyond PCs. Will it work?

http://bit.ly/12t4jp1

#### How war on the Korean peninsula could affect worldwide electronics production

What would happen if half of all global production for DRAM, twothirds of NAND flash manufacturing and 70 percent of the world's tablet display supply suddenly disappeared from the market? http://bit.ly/12QJTpe

#### Slide Show: Top 10 medical applications for MEMS

Nowadays, it's just a spoonful of MEMS that helps the medicine go down... http://bit.ly/YLmD8z

## Semiconductor R&D: A state of transition

Karen Savala, president of SEMI Americas, addresses the growth and changing role of R&D consortia. http://bit.ly/Zcnwdm

#### Insights from the Leading Edge: Qualcomm updates 2.5D/3D

At ICEP in Osaka, Japan, Qualcomm's Umi Ray presented "Architecture Trends in Mobile Industry and Impact on Packaging and Integration." http://bit.ly/10EaJhq

## Series: Who's driving the MEMS evolution revolution?

Long-time MEMS industry insider, Howard Wisniowski takes readers with him to "visit" three exciting MEMS startups that are breaking new ground in the mobile/ consumer market. http://bit.ly/15RT640

#### **Studying 1/f noise**

In his first blog, Dr. Zhihong Liu, Executive Chairman of ProPlus 1/f noise is an important characteristic for various semiconductor devices, such as MOSFETs, BJTs, JFETs, Diode, and IC resistors. http://bit.ly/10uhllT

#### editorial

## The value of innovation

Speaking at SEMI's Advanced Semiconductor Manufacturing Conference (ASMC) in Saratoga Springs, Subramani "Subi" Kengeri, vice president, advanced technology architecture, GLOBALFOUNDRIES, gave a wide-ranging overview of the challenges facing leading edge SoC semiconductor manufacturers.

He mapped out the many technical challenges facing the industry, highlighted ongoing innovations to meet those challenges, and then showed how it all meshed with market demand and cost considerations. "Everything must be related to SoC-value," he said.

In his talk, titled "Threats to Semiconductor Growth," Kengeri said huge semiconductor growth was predicted, reaching \$408 billion by 2015 (from \$355 billion in 2013). Mobile and foundry growth

#### "SoC chips designed for mobile apps are increasingly driving semiconductor tech."

is expected to outpace the overall industry, and SoC chips designed for mobile apps are increasingly driving semiconductor technology.

Yet, critical issues need to be resolved to achieve that

growth, particularly in the areas of power density, BEOL RC, cost and, perhaps most importantly, time to volume. "With the technology become more and more complex, the time to volume has become a bigger and bigger challenge," he said. He said delayed time to volume equates to a delayed ROI, which could mean less revenue to build the next technology node and the next fab.

He noted SoC designs are getting larger (47% now use more than 5M gates), and they're also getting faster (37% run at 750MHz and above). There are also a larger number of clock domains, which means managing multiple macros operating at different frequencies, and more voltage domains across the chip (five different ones on average). A problem with large complex designs is that product life can be shorter than development time. He said automating design through EDA helps, but there is still a gap.

The good news is that R&D innovations, including improvements in the gate stack, stress engineering, silicides, lithography, middle- and backend-of line, and low-k dielectrics are bringing value to the overall SoC in terms of performance, power, area and cost/ complexity (PPAC). "The innovation engine is running," Kengeri said.

-Pete Singer, Editor-in-Chief

## Solid Stat

Susan Smith, Group Publisher Ph: 603-891-9447, susans@pennwell.com Pete Singer, Editor-in-Chief Ph: 603-891-9217, psinger@pennwell.com Shannon Davis, Editor, Digital Media

Ph: 603-891-9145, shannond@ pennwell.com Robert C. Haavind, Editor-at-Large

Ph: 603-891-9453, bobh@pennwell.com Phil Garrou, Contributing Editor Michael Fury, Contributing Editor Justine Beauregard, Marketing Manager Angela Millay, Editorial Art Director Sheila Ward, Production Manager Dan Rodd, Illustrator Debbie Bouley, Audience Development

Marcella Hanson, Ad Traffic Manager

#### EDITORIAL ADVISORY BOARD

John O. Borland, J.O.B. Technologies Michael A. Fury, The Techcet Group, LLC Rajarao Jammy, SEMATECH William Kroll Matheson Tri-Gas Ernest Levine, Albany NanoTech Lars Liebmann, IBM Corp. Dipu Pramanik, Cadence Design Systems Inc. Griff Resor, Resor Associates A.C. Tobey, ACT International

#### EDITORIAL OFFICES

PennWell Corporation, Solid State Technology 98 Spit Brook Road LL-1, Nashua, NH 03062-5737; Tel: 603-891-0123; Fax: 603-891-0597; www.ElectrolQ.com

#### CORPORATE OFFICERS

1421 South Sheridan Rd., Tulsa, Ok 74112 Tel: 918-835-3161 Frank T. Lauinger, Chairman Robert F. Biolchini, President and CEO Mark Wilmoth, Chief Financial Officer

#### TECHNOLOGY GROUP

Christine A. Shaw, Senior Vice President and Publishing Director

#### For subscription inquiries:

Tel: (847) 559-7500; Fax: (847) 291-4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

We make portions of our subscriber list available to carefully screened companies that offer products and services that may be important for your work. If you do not want to receive those offers and/or information, please let us know by contacting us at List Services, Solid State Technology, 98 Spit Brook Road, Nashua, NH 03062. All rights reserved. No part of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval system, without written permission of the copyright owner. Prices for bulk reprints of articles available on request. Solid State Technology articles are indexed in Engineering Information and Current Contents. and Applied Science & Technology Index and abstracted by Applied Science & Technology Abstracts.

AMERICAN

Please send news articles to peters@pennwell.com

#### worldnews

US - MEMSIC, Inc., a MEMS solution provider, announced that it has agreed to be acquired by IDG-Accel China Capital II, L.P. and its affiliates.

**EUROPE - Silex Microsystems** joined the international European Union-funded program PROMINENT to develop new low-cost technologies for TSVs, hermetic highvacuum seals for wafer-to-wafer bonding including advanced material deposition, advances in piezo-MEMS fabrication, and more.

ASIA - Freescale Semiconductor announced that the company plans to open ten new sales offices across China.

UK - University of Manchester researchers reported that they have developed the first graphenebased transistor with bistable characteristics.

ASIA - Yole Développement reported that TSMC's MEMS foundry business enjoyed approximately 80 percent growth in 2012, making it the largest of any MEMS open foundry.

**EUROPE - Morgan Advanced Materials** joined **SEMATECH's** International SEMATECH Manufacturing Initiative (ISMI), a program designed to improve semiconductor equipment manufacturing productivity, yield, and cost.

**EUROPE - LFoundry** confirmed the completion of the acquisition of **Micron's** manufacturing facility in Avezzano, Italy.

**US - GT Advanced Technologies** announced that it has acquired substantially all of the business of Thermal Technology LLC.

## Combo MEMS inertial sensors report brisk growth in automotive market

Combo MEMS sensors for automotive applications are off to another exhilarating ride this year as revenue continues to climb, spurred by rapidly accelerating use in car safety systems, according to an IHS iSuppli MEMS and Sensors Report from information and analytics provider IHS.

Global revenue in 2013 for combo inertial sensors used in motor vehicles will reach a projected \$163 million, up a notable 77 percent from \$92 million last year. The anticipated increase continues a hot streak for the market, which saw a phenomenal 338 percent surge last year from just \$10 million in 2011.

MEMS combo sensors Combo inertial sensors are multiple-sensor devices integrating accelerometers, gyroscopes into a single package, providing inertial inputs to the electronic stability control (ESC) system in cars to prevent or minimize skidding.

"ESC systems are mandated in North America, Europe and in other areas where the edicts are maturing, such as Australia, Japan, Canada and South Korea," said Richard Dixon, Ph.D., principal analyst for MEMS and Sensors at IHS. "But a huge growth opportunity exists in untapped territories like China, which would significantly impact the penetration of ESC worldwide given the vast size of the Chinese market. Such gains, in turn, would provide tremendous impetus and momentum for automotive combo sensors overall."

#### Why combos?

Three architectures are currently possible for ESC systems in cars: on a printed circuit board as a separate ESC engine control unit (ECU); attached to the brake modulator to save cabling; or collocated in the airbag ECU. Of these three usable locations, the current trend favors placing ESC systems in the airbag ECU to achieve a smaller footprint and greater efficiency, given that there is a space constraint for the ECU in this position near the cup holder in a vehicle, which favors an architecture of reduction.

All told, as much as a fivefold reduction in space could be achieved for the sensors in a combo-sensor ESC system made by a manufacturer like Continental, compared to the same accomplished via separate sensors.

A non-combo solution also exists in the form of the sensors separately mounted on the printed circuit board. But deploying the sensors in a combo form factor saves not only on packaging cost but also on expensive real estate for the semiconductors being used, since the two sensors in the combo package share the same application-specific integrated circuit.

#### Cost is a factor

A paramount issue for ESC systems is cost. Cost is especially important because ESC formerly was considered an optional feature—but since being mandated by

governments—it now has attained the same required status as the seat belt.

As a result, the entire supply chain and price structure for automotive combo sensors has been experiencing huge pressure, exerted from car makers down the chain. Tier 1 companies then pass on this pressure to their suppliers, accounting for the accelerated move to provide efficient combo sensor solutions for inertial sensors in the system.

Because of such pressure, some top-tier companies have indicated that only legacy businesses will use older arrangements featuring separate sensors—not a combo solution—on a printed circuit board in the future. All new car models will use combo sensors.

#### Top suppliers identified

The major suppliers of automotive combo inertial sensors are Bosch of Germany and Japan's Murata (formerly VTI). Two other potential manufacturers, Panasonic of Japan and Massachusetts-based Analog Devices, will need to develop similar solutions to have a chance in the market.

For its part, Panasonic has indicated that a product will be available by 2014. Panasonic Industrial makes the gyroscope part of the solution, while Panasonic Electric Works makes the accelerometer component.

However, the two entities do not have a good track record of working together, so it remains to be seen how soon a unified combo sensor solution from Panasonic will come to market. Meanwhile, Analog Devices is divulging little information, but it will almost certainly develop a combo sensor solution, IHS iSuppli believes, based on an analysis of developments surrounding the competition.

## reduce soft errors

### Deliver more density on your IC packages without soft errors.

Honeywell RadLo<sup>™</sup> low alpha packaging materials help eliminate soft errors and single event upsets by reducing alpha emissions, a significant source

of these problems. This is becoming increasingly important as chip dimensions and designs continue to miniaturize. Our leadership and expertise in low alpha refining and metrology mean that Honeywell can help you meet critical alpha emission levels.

Honeywell reliability. Reliable low alpha. Make sure to ask your suppliers if they are using Honeywell RadLo low alpha materials for their chip packaging processes.

#### Find out more by visiting us at www.honeywell-radlo.com

Although all statements and information contained herein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information and results obtained. Statements or suggestories concerning the use of materials and processes are made without representation or warranty that any such use is free of pletern infringement and are not recommendations to infininge any patert. The user should not assume that all toxicity data and safety measures are indicated herein or that other measures may not be required. ©2012 Honeywell International Inc. All rights reserved.

## **news**cont.

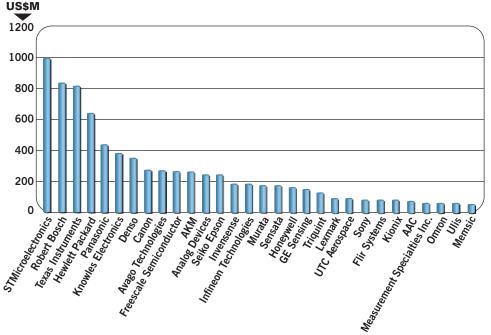

#### Top 30 MEMS companies of 2012

The fast growing market for sensors for smart phones is re-shuffling the ranks of MEMS suppliers. For the first time, suppliers of inertial sensors have surpassed the major makers of micro mirrors and inkjet heads that have long dominated the industry on Yole Développement's annual ranking of the Top 30 MEMS companies.

STMicroelectronics increased MEMS sales by ~10 percent in 2012, to become the first company with \$1 billion in MEMS revenue, moving past Texas Instruments to become the

sector's largest company. Robert Bosch saw 14 percent growth, to ~\$842 million in MEMS sales, pushing ahead of both Texas Instruments and Hewlett Packard for the first time to become the second ranking player, according to Yole's figures. Both ST and Bosch have been aggressively expanding their consumer product lines to offer customers a broad range of sensors, and increasingly also combinations of sensors in a single package for easier integration at lower cost. Their growing volumes also help keep their fabs running more efficiently, for the assured manufacturing capability that volume users demand. ST, Bosch and other major inertial sensor suppliers saw strong revenue growth despite the 20-30 percent drop in average selling prices for accelerometers and gyroscopes over the year--because of even bigger ramps in unit volume.

"ST increased unit production by 58 percent, to 1.3

Source: Status of the MEMS Industry report, Yole Développement, to be released Q2, 2013 © April 2013

billion MEMS devices in 2012, up to some 4 million units a day—not counting its foundry business," notes Yole Market & Technology Analyst, Laurent Robin. "It's hard for many companies to match that."

Yole calculates the MEMS industry overall saw another ~10 percent growth in 2012 to become an ~\$11 billion business—in a year when the semiconductor industry saw a ~2 percent decline. The Top 30 companies account for nearly 75 percent of that total MEMS market.

The traditional gap between the big four MEMS makers and the rest of the pack narrowed this year, as strong demand for more MEMS sensors in both consumer and automotive markets drove strong growth across a range of suppliers. Knowles Electronics saw better than 20 percent growth to climb into fourth place with some \$440 million in revenues from MEMS microphones, closing in on HP. Panasonic and Denso were close behind with more than \$350 million in MEMS sales in their largely automotive markets.

Mobile phones and tablets were the real sweet spot

that do not release MEMS revenues, Yole estimate the figures based on data for product market size, market share, product teardowns, reverse costing, and discussions with the companies. ◆

for big growth opportunities, though. Chinese electret microphone supplier AAC made the top companies ranking for the first time as its MEMS microphone sales jumped ~90 percent to ~\$65 million, as it became the second source for the iPhone. InvenSense saw some 30 percent growth as it ramped up production of its inertial sensors. Triquint saw a 27% increase in revenues from its BAW filters.

Murata moved sharply up the ranking as its acquisition of VTI created ~\$179 million in combined MEMS revenue.

Meanwhile, the traditional major MEMS markets for micromirrors and inkjet heads have matured and slowed, with demand for inkjet heads particularly hit by the consumer printer market's rapid turn away from replaceable heads to pagewide and fixed-head technologies. That hit revenuesat both the inkjet companies and their manufacturing partners.

Yole defines MEMS as three dimensional structures made by semiconductor-like processes, with primarily mechanical, not electronic, function. We also include magnetometers, as they are now so closely integrated with MEMS inertial sensors, and all microfluidics, including those on polymer. Yole figured MEMS units and value at the first level of packaged device. For companies

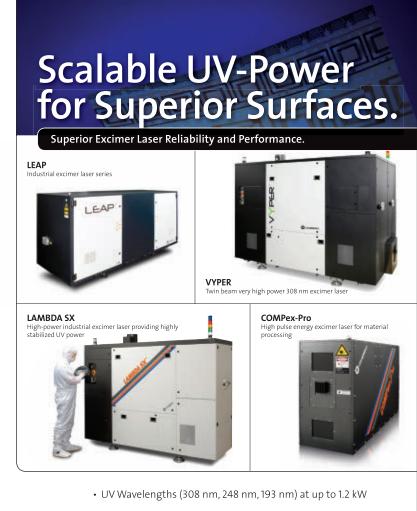

- Optical Modules for Square Field and Line Beam Scanning

- Selective Layer Processing with up to 100 cm<sup>2</sup>/sec

tech.sales@Coherent.com www.Coherent.com toll free: (800) 527-3786 phone: (408) 764-4983

**Superior Reliability & Performance**

China +86 (10) 8215 3600 France +33 (0)1 8038 1000 Germany +49 (6071) 968 333 Italy +39 (02) 31 03 951 Japan +81 (3) 5635 8700 Korea +82 (2) 460 7900 UK +44 (1353) 658 833

Benelux +31 (30) 280 6060

www.solid-state.com

## Personal computer shipments post worst quarter on record, says IDC

In another sign of the worldwide shift in preferred personal devices, PC shipments posted the steepest decline ever in a single quarter, according to the International Data Corporation Worldwide Quarterly PC Tracker (IDC).

Worldwide PC shipments totaled 76.3 million units in the first quarter of 2013, down -13.9 percent compared to the same quarter in 2012 and worse than the forecast decline of -7.7 percent, according to the IDC. Despite some mild improvements in the economic environment, PC shipments were down significantly across all regions compared to a year ago, marking the worst quarter reported since IDC began tracking the PC market in 1994. The results also marked the fourth consecutive quarter of year-on-year shipment declines.

The reduction in shipments isn't entirely shocking, given the obvious cannibalization from tablets and smartphones. Smartphones shipments are expected to continue their historic rise at a rate of 24 percent CAGR from 2011 to 2016, according to Andy Oberst, Strategic Vice President of Qualcomm, and PC makers are collectively bracing for the change, as other indicators have risen throughout the past year. DRAM content growth is reported slowing, as slim notebooks have limited space for it, and tablets and smartphones have no use for it at all. Instead, its low-power variant, mobile DRAM, is seeing an increase. Additionally, the chip market outlook was downgraded in 2012, with the weak PC market mostly to blame.

"Although the reduction in shipments was not a surprise, the magnitude of the contraction is both surprising and worrisome," said David Daoud, IDC Research Director, Personal Computing. "The industry is going through a critical crossroads, and strategic choices will have to be made as to how to compete with the proliferation of alternative devices and remain relevant to the consumer. Vendors will have to revisit their organizational structures and go to market strategies, as well as their supply chain, distribution, and product portfolios in the face of shrinking demand and looming consolidation."

PC makers had pinned their hopes on the launch of Microsoft's Windows 8 OS, which is a complete overhaul Continued on page 10

## GLOBALFOUNDRIES demonstrates 3D TSV capabilities on 20nm technology

GLOBALFOUNDRIES announced the accomplishment of a key milestone in its strategy to enable 3D stacking of chips for next-generation mobile and consumer applications. At its Fab 8 campus in Saratoga County, N.Y., the company has demonstrated its first functional 20nm silicon wafers with integrated Through-Silicon Vias (TSVs). Manufactured using GLOBALFOUNDRIES' leading-edge 20nm-LPM process technology, the TSV capabilities will allow customers to stack multiple chips on top of each other, providing another avenue for delivering the demanding performance, power, and bandwidth requirements of today's electronic devices.

TSVs are vertical vias etched in a silicon wafer that are filled with a conducting material, enabling communication between vertically stacked integrated circuits. The adoption of three-dimensional (3D) chip stacking is increasingly being viewed as an alternative to traditional technology node scaling at the transistor level. However, TSVs present a number of new challenges to semiconductor manufacturers.

GLOBALFOUNDRIES utilizes a "via-middle" approach to TSV integration, inserting the TSVs into the silicon after

the wafers have completed the Front End of the Line (FEOL) flow and prior to starting the Back End of the Line (BEOL) process. This approach avoids the high temperatures of the FEOL manufacturing process, allowing the use of copper

as the TSV fill material. To overcome the challenges associated with the migration of TSV technology from 28nm to 20nm, GLOBALFOUNDRIES engineers have developed a proprietary contact protection scheme. This scheme enabled the company to integrate the TSVs with minimal disruption to the 20nm-LPM platform technology, demonstrating SRAM functionality with critical device characteristics in line with those of standard 20nm-LPM silicon.

"Our industry has been talking about the promise of 3D chip stacking for years, but this development is another sign that the promise will soon be a reality," said David McCann, vice president of packaging R&D at GLOBALFOUNDRIES. "Our next step is to leverage Fab 8's advanced TSV capabilities in conjunction with our OSAT partners to assemble and qualify 3D test vehicles for our open supply chain model, providing customers with the flexibility to choose their preferred back-end supply chain."

As the fabless-foundry business model evolves to address the realities of today's dynamic market, foundries are taking on increasing responsibility for managing the supply chain to deliver end-to-end solutions that meet the requirements of the broad range of leading-edge designs. To help address these challenges, GLOBALFOUNDRIES is engaging early with partners to jointly develop solutions that will enable the next wave of innovation in the industry. This open and collaborative approach will give customers maximum choice and flexibility, while delivering cost savings, faster time-to-volume, and a reduction in the technical risk associated with developing new technologies. ◆

## **POWER SOLUTIONS FOR** SEMICONDUCTOR DESIGN, MANUFACTURE AND TEST

- Redundant systems

- www.tdipower.com | 908.850.5088

#### Intel board elects Brian Krzanich as CEO, Renée James as President

Intel Corporation announced in May that the board of directors has unanimously elected Brian Krzanich as its next chief executive officer (CEO), succeeding Paul Otellini. Krzanich assumed his new role at the company's annual stockholders' meeting on May 16. The board of directors also elected Renée James, 48, to be president of Intel. She also assumed her new role on May 16, joining Krzanich in Intel's executive office.

Krzanich, Intel's chief operating officer since January 2012, will become the sixth CEO in Intel's history. As previously announced, Otellini will step down as CEO and from the board of directors on May 16.

"After a thorough and deliberate selection process, the board of directors is delighted that Krzanich will lead Intel as we define and invent the next generation of technology that will shape the future of computing," said Andy Bryant, chairman of Intel.

"Brian is a strong leader with a passion for technology and deep understanding of the business," Bryant added. "His track record of execution and strategic leadership, combined with his open-minded approach to problem solving has earned him the respect of employees, customers and partners worldwide. He has the right combination

of knowledge, depth and experience to lead the company during this period of rapid technology and industry change."

Krzanich, 52, has progressed through a series of technical and leadership roles since joining Intel in 1982.

As chief operating officer, Krzanich led an organization of more than 50,000 employees spanning Intel's Technology and Manufacturing Group, Intel Custom Foundry, NAND Solutions group, Human Resources, Information Technology and Intel's China strategy.

James, 48, has broad knowledge of the computing industry, spanning hardware, security, software and services, which she developed through leadership positions at Intel and as chairman of Intel's software subsidiaries --Havok, McAfee and Wind River. She also currently serves on the board of directors of Vodafone Group Plc and VMware Inc. and was chief of staff for former Intel CEO Andy Grove. <>

#### **Computer Shipments** Continued from page 8

of the operating system with touch-screen capabilities. Unfortunately, these new shipment trends are indicating that the upgraded operating system has not had the desired effect on consumers.

Bob O'Donnell, IDC Program Vice President, believes it is clear that Windows 8 not only failed to provide a positive boost, but also appears to have slowed the market.

"While some consumers appreciate the new form factors and touch capabilities of Windows 8, the radical changes to the UI, removal of the familiar Start button, and the costs associated with touch have made PCs a less attractive alternative to dedicated tablets and other competitive devices," said O'Donnell. "Microsoft will have to make some very tough decisions moving forward if it wants to help reinvigorate the PC market."

Microsoft, at least in public, does not appear to be on the verge of making tough decisions at the moment, however. A Microsoft spokesperson told the Wall Street Journal that, along with their partners, they planned "to continue to bring even more innovation to market across tablets and PCs."  $\diamond$

## IBM announces \$1B investment in flash memory R&D

IBM announced plans to invest \$1 billion in flash memory research and development and launch a series of systems that will use solid state drives.

At an event in New York, IBM's Steve Mills, head of IBM's software and systems division, said Flash is at a key tipping point and IT will see all-solid state data centers sooner than later.

Corporate servers have struggled to keep up with the substantial growth in data use from smartphones and tablets. IBM believes there is a solution in flash memory, which is faster, more reliable, and uses less power than a traditional hard disk drive. The \$1 billion investment will be put to use in research and development to design, create and integrate new flash-based products in its portfolio of servers, storage systems and middleware.

"The economics and performance of flash are at a point where the technology can have a revolutionary impact on enterprises, especially for transaction-intensive applications," said Ambuj Goyal, IBM's general manager of systems storage. "The confluence of Big Data, social, mobile and cloud technologies is creating an environment in the enterprise that demands faster, more efficient, access to business insights, and flash can provide that access quickly."

As part of its commitment to flash development, IBM said it plans to open 12 Centers of Competency around the globe, which will allow customers to test IBM flash products in real-word scenarios.

"Clients will see first-hand how IBM flash solutions can provide real-time decision support for operational information, and help improve the performance of mission-critical workloads, such as credit card processing, stock exchange transactions, manufacturing and order processing systems," IBM said in a news release. ◆

#### Second phase of Nanoelectronics Research Initiative to focus on post-CMOS electronics

Semiconductor Research Corporation (SRC) and the National Institute of Standards and Technology (NIST) in May announced the second phase of the Nanoelectronics Research Initiative (NRI). SRC and NIST will provide a combined \$5 million in annual funding for three multi-university research centers tasked with demonstrating non-conventional, low-energy technologies that outperform current technologies on critical applications in 10 years and beyond.

The second phase of NRI also features joint projects with the National Science Foundation

Continued on page 35

#### INTRODUCING THE PE-25-JW

The Plasma Etch, Inc. PE-25-JW is a fully automated plasma cleaning system.

Surface energy modification with plasma treatment yields improved markability, adhesion and ease of assembly with a low environmental impact.

Removes organics and improves bonds

LOW STARTING PRICE \$ 6,900 USD

TO LEARN MORE, VISIT <u>WWW.PLASMAETCH.COM</u> OR CALL US TODAY AT **775-883-1336**

## NVIDIA's GPUs; Patent analysis

NVIDIA has publically updated their roadmap with the announcement of the GPU family that will follow 2014's Maxwell family. That new family is Volta which will use stacked DRAM, which will be connected to the GPU with TSV.

NVIDIA is targeting a 1TB/sec bandwidth rate for Volta, which, to put things in perspective, is over 3x what GeForce GTX Titan currently achieves with its 384bit, 6Gbps/pin memory bus (288GB/ sec). This would imply that Volta is shooting for something along the lines of a 1024bit bus operating at 8Gbps/pin, or possibly an even larger 2048bit

bus operating at 4Gbps/pin. Volta is still years off, but this at least gives us an idea of what NVIDIA needs to achieve to hit their 1TB/sec target. At the GPU Technology Conference in San Jose, CEO Jen-Hsun Huang spoke about the Volta. "Volta is going to

solve one of the biggest challenges facing GPUs today, which is access to memory bandwidth," Huang told the attendees.

The Volta GPU will include stacked DRAM. Figure 1 is a shot of the Volta with stacked DRAM (drawn to scale).

Huang didn't provide a timeline for Volta's release, but 2016 seems reasonable since Nvidia debuts new GPU architectures every two years. Huang said that

#### Packaging

Nvidia will be putting the stacked DRAM and the GPUs onto the same silicon substrate and inside of the same packaging before it welds that package to a peripheral card.

#### New patent report

In other news, Yole Développement announced its 2.5D,

3DIC and TSV Interconnect Patent Investigation report. Yole Développement's investigation aims at providing statistical analysis of existing IP to give a landscape overview together with an in-depth investigation on five player portfolios selected by the analyst.

For this analysis of 3D packaging technology patents, more than 1800 patent families were screened. Fifty-two percent of the families have been classified as relevant and further studied.

"The in-depth analysis quickly revealed that the overall patent landscape was pretty young with 82 percent of patents filed since 2006," explained Lionel Cadix, technology and market analyst of the Advanced Packaging division at Yole Développement. "Actually about 260 players

are involved in 3DIC technology while the top 10 assignees represents 48 percent of patents filed in the 3DIC domain."

In this report, Yole Développement selected five companies from these 10 most active players to focus on and lead an accurate analysis of

their patent portfolios.

Yole Développement also found main types of business models among the top 10 assignees involved in this mutating middle end area: •Foundries and IDM: IBM, Samsung, Intel •OSATs: STATS ChipPAC, Amkor •Memory IDM/Foundries: Micron, SK Hynix, Elpida •Research centers: ITRI

It is also interesting to note that the USA is the early player increasingly involved in 3DIC since 1969. China and Korea are new players since 2005. ◆

Nvidia's Volta with stacked DRAM.

# Inside biomedical devices

The interface of human physiology with electronic processing provides a market for medical devices whose applications are boundless. The convergence of scientific and medical research, new materials, wireless communication and evolving healthcare policies create an expanding market opportunity for medical devices that detect and analyze biological functions.

The ability to unobtrusively monitor vital signs and stress biomarkers can save lives. For military personnel or first responders to an emergency situation, new technology will sense when rescue workers are in danger. For the chronically ill, elderly, newborn or other high risk patients, these monitoring devices can save lives and dramatically reduce health care costs.

Lux Research estimates the worldwide medical device market is over \$300 billion. The advent of smaller, more conformable components enabled by organic electronics is fueling additional market opportunities and will lead to more cost-effective medical care.

Biosensors and microfluidic devices are core components for bio-monitoring devices. These technologies will help detect early signs of infection, the onset of a stroke or heart attack and eventually provide early diagnosis of chronic diseases that can be detected with biomarkers.

A biosensor generally consists of three parts. First is the sensitive biological element such as microorganisms, enzymes or nucleic acids. Next is the transducer element which transforms a biological reaction

MEMS

into a measurable signal. The final stage is the electronics and signal processors that communicate the results. Several sophisticated, micro-sized and flexible biosensors are under development. For example, Massachusetts-based startup MC10 is developing a new class of catheters embedded with ultra-low profile, nanometerthin sensors. These sensors provide physicians with real-time feedback during procedures.

**Denise Rael,** Contributing Editor

moving liquids from one location to another. They can be used to collect bio-fluids for analysis or to dispense medication automatically. Microfluidics are especially useful in biomedical applications because they perform tests such as detecting toxins or DNA analysis using just a small amount of bodily fluids.

While microfluidic devices have been around for decades, the technology has historically involved large equipment in a lab setting for analysis. Currently, a number of organizations are working on bringing a Lab-on-a-Chip to market. For instance, researchers at Harvard University and the University of Washington have actually formed paper microfluidic devices. The Microfluidic Paper-based Analytical Devices ( $\mu$ PADs) are made from paper patterned into hydrophilic channels or paper cut into channels with controlled geometry using laser cutters. They are inexpensive, simple-to-use, and equipment-free - easily adaptable to remote locations.

Innovative sensor and microfluidics technologies enable the next generation of medical devices with the potential to improve both the economics and outcomes of healthcare. However, organizations interested in bringing a medical device to market need to be aware of regulatory considerations.

"You want to understand the pathway to market as early as possible," says Nathan A. Beaver, Partner at Foley & Lardner LLP. Medical devices are subject to regulation by numerous regulatory bodies, including the Food and Drug Administration (FDA). Companies must comply with laws and regulations governing the testing, manufacturing, labeling, marketing and distribution of medical devices. Devices are subject to varying levels of regulatory control, the most comprehensive of which requires that a clinical evaluation be conducted before a device receives approval for commercial distribution.

# The challenges of sub-20nm shallow trench isolation etching

HUI ZHOU, XIAOSONG JI, SUNIL SRINIVASAN, JIM HE, XUEFENG HUA, ANKUR AGARWAL, SHAHID RAUF, VALENTIN N. TODOROW, JINHAN CHOI, AND ANISUL KHAN, Applied Materials, Inc., Santa Clara, CA

Major challenges for sub-20nm STI etching include intra-cell depth loading, across-wafer uniformity, etch profile control near the wafer edge, and propensity for pattern collapse.

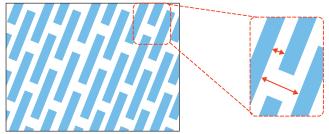

hallow trench isolation (STI) is used for device isolation in state-of-the-art semiconductor process technologies [1]. For optimal transistor performance and desired yield, the line critical dimension (CD) and the trench depth must be tightly controlled [2]. As feature sizes scale below 20nm, the aspect ratio of the isolation trench can be as high as 20:1. Given the small space CD, variation in trench width (e.g., from double patterning) is no longer negligible, and the subsequent aspect ratio dependent etching effect can lead to non-uniform trench depths [3]. Consequently, minimizing intra-cell depth loading is crucial.

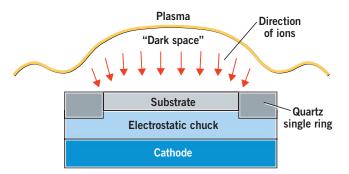

As feature sizes scale, profile uniformity across the wafer and, in particular, near the wafer edge assume greater importance. The outer edge (10mm) of a 300mm wafer accounts for over 10% of total devices that yield. But the edge area is characterized by discontinuities of materials (wafer to focus ring/process kit transition), and electrical and thermal properties (due to the wafer overhang on the electrostatic chuck). Consequently, the plasma sheath characteristics are not necessarily similar to those over the center of the wafer, leading to significant impact on STI features near the wafer edge. Both of these aspects must be managed simultaneously for sub-20nm features.

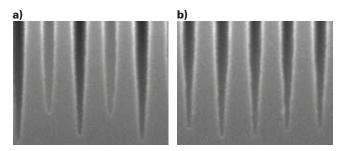

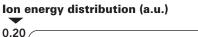

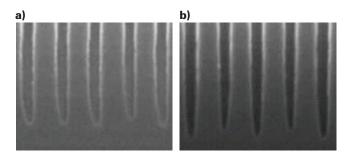

**FIGURE 1.** STI etching profiles using 13MHz bias power with (a) continuous wave plasma and (b) pulsed plasma (processes are not fully optimized).

Aside from the above challenges for sub-20nm features, some new issues also arise. One is the potential for line collapse, which can substantially reduce production yield. Pattern collapse has been a major problem for lithography resist, and numerous research papers addressing this issue have been published [4-7]. Owing to their low Young's modulus of 1-5 GPa, lithography resist patterns succumb to capillary pressure during the drying process [8]. Silicon, unlike a typical resist material, is much more rigid with a Young's modulus of ~150 GPa [9] and is usually immune to pattern collapse for STI etching when line widths are on the order of 100s nm. However, line collapse has been increasingly observed in sub-20nm STI features, especially after wet cleaning.

HUI ZHOU, XIAOSONG JI, SUNIL SRINIVASAN, JIM HE, XUEFENG HUA, ANKUR AGARWAL, SHAHID RAUF, VALENTIN N. TODOROW, JINHAN CHOI, and ANISUL KHAN, Applied Materials, Inc., Santa Clara, CA

In this paper, we discuss the above four challenges (intra-cell depth loading, wafer edge profile, acrosswafer etch uniformity, and line collapse) in etching sub-20nm STI features, using experimental results from the Applied Materials inductively coupled plasma silicon etcher. Some general guidelines to overcome these challenges are also reviewed.

#### Intra-cell depth loading

In most cases, high aspect ratio features etch more slowly than low aspect ratio features due to the transport limit of etchant in the trenches [3]. In other words, the etching rate of a wider trench is higher than that with a smaller CD. As the CD scales below 20nm, any space CD variation is no longer negligible compared to the CD and leads to depth loading with plasma etching. Ions are less affected by trench shadowing due to their higher directionality resulting from acceleration within the sheath. Therefore, shadowing of neutral species — the radicals, molecules, and the etching products — dominates aspect ratio dependent etching. Through our process developments, we identified three general rules that are most effective for minimizing intra-cell depth loading during sub-20nm STI etching:

- 1. Prevent further space CD variation by maintaining a clear trench with thin sidewall protection film.

- 2.Alleviate the transport limit of neutral species between wider and less open trenches by using pulsed plasmas.

- 3. Make the process less radical driven and more ion driven by using high-energy etchant ions, such as Cl<sup>+</sup> or Br<sup>+</sup>.

Sidewall protection is critical in high aspect ratio etching [10]. The passivation layer protects the trench sidewall from etchant species and helps maintain a straight sidewall profile. The efficiency of the protection layer depends on the film composition and its thickness. However, a thicker film also reduces the space CD, which can have a significant impact in sub-20nm STI etching. A thin sidewall passivation layer is therefore desired for minimal reduction of the space CD. Note that during silicon etching, the trench can get blocked due to deposition of the etching radicals or redeposition of etching byproducts. The trench therefore also needs periodic cleaning. A practical approach is to have alternating trench cleaning, passivation, and silicon etch steps. The exact order may vary, but throughout the process, a clear trench should be maintained with a thinnest possible sidewall protection film.

Continuous wave plasma etching technology has served microelectronic fabrication very well in most applications, but with the transport limit of neutral species for STI etching, we must consider an alternative plasma etching regime, namely, a pulsed plasma. Pulsed plasma is transient, which is different from continuous wave operation [11], alleviates the transport limit. During the off cycle, the radicals/ ions/byproducts have extra time to move out of the trench or act independently on the sidewall, for better sidewall polymer deposition management. FIGURE 1 shows an example of improved intra-cell depth loading using pulsed plasma. STI features etched using continuous wave plasma etching (Fig. 1a) have large intra-cell depth loading due to space CD variation while those etched using a pulsed plasma (Fig. 1b)

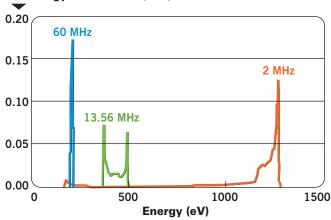

FIGURE 2. Modeling results of ion energy distribution versus bias frequency.

have significantly less intra-cell depth loading in spite of the same space CD variation.

Unlike neutral species, ions are less susceptible to shadowing effects due to their acceleration by the sheath electric field, which leads to more directionality. Consequently, intra-cell depth loading can be reduced if the silicon trench formation were dominated by ions (Cl<sup>+</sup> or Br<sup>+</sup>) instead of radicals. Ion dependent etching can be realized by increasing ion energy or ion density. To increase ion energy, one can elevate the bias power or lower the bias frequency. As shown in **FIGURE 2**, model-predicted ion energy distributions for varying bias frequencies at constant bias power indicate that ion energies can be increased with lower bias frequency. In fact, pulsed plasma and lower bias frequency can be combined to reduce depth loading. FIGURE 3 shows STI etching profiles with 2 MHz bias power operated

in continuous wave or pulsed plasma mode. While the high ion energy approach with lower bias frequency of 2 MHz reduced the intra-cell depth loading (compared to the trench profiles in Fig. 1), the pulsed plasma with 2 MHz bias power showed the least depth loading. Besides decreasing the intra-cell loading, the high ion energy etching approach has another benefit of maintaining a flat trench bottom. This facilitates a uniform etching front, which is desirable for achieving a high production yield.

By following the three guidelines, we minimized intra-cell depth loading of STI trenches with similar CD, for such applications as NAND STI. The three rules also have the potential to significantly reduce depth loading between dense areas and wide open regions. For example, a typical DRAM STI pattern, as shown schematically in **FIGURE 4**, is designed to have trenches with narrow openings between the cells and wide open regions at the cell ends as illustrated in [12, 13]. We have also applied the three general rules for DRAM STI etching and achieved promising results.

#### Edge profile and uniformity

Two other issues are also challenging for sub 20nm STI etching. These are edge profile control and uniformity tuning across the wafer. These two issues originate from the nature of plasma distribution inside the reaction chamber, which is often beyond the capability of process tuning. The fundamental solution would be implementing novel hardware to achieve more uniformly distributed plasma.

Three main kinds of discontinuities occur at the wafer edge: 1) material discontinuity from the silicon wafer to the support ring; 2) geometrical disconti-

FIGURE 3. STI etching profiles using 2MHz bias power with (a) continuous wave plasma and (b) pulsed plasma (processes were not fully optimized).

FIGURE 4. Plan view of a typical DRAM STI pattern, with narrow open area between cells and wide open region at the cell ends, as illustrated in [12, 13].

**FIGURE 5.** Schematic of plasma sheath curvature due to discontinuities at the wafer edge.

nuity from the wafer level to the ring level; and 3) electrical discontinuity due to RF coupling termination at the wafer edge. Because of these three discontinuities, the plasma sheath profile at the wafer edge becomes curved, resulting in off-normal incidence of ions **(FIGURE 5)**. Consequently, for certain processes, the trench profile at the wafer edge may tilt in the direction of ion incidence, as shown in **FIGURE 6a**. One innovation for improving the edge profile is our advanced edge control (AEC) kit. The AEC kit alleviates electrical discontinuity by optimizing the cathode to extend uniform RF coupling beyond the edge of the wafer. Sheath bending is thereby corrected and the ions are normally incident (i.e., are no longer tilted), resulting in straighter trench profiles **(FIGURE 6b)**.

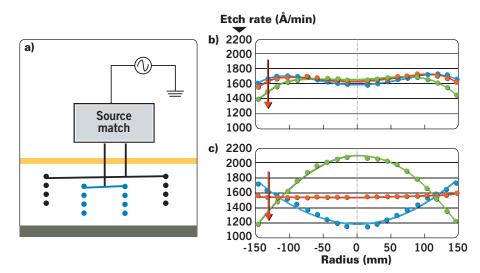

Mainstream commercial inductively coupled plasma (ICP) sources utilize planar or helical coil geometries [14]. For either type, radial distribution of the electromagnetic fields are not homogenous, leading to non-uniformities in plasma generation that in turn introduce non-uniformity in the etching rate across the wafer. As plasma uniformity is mainly related to the plasma source and gas delivery, tweaking the source coil configurations and gas delivery systems can help improve uniformity. This is achieved in our silicon etcher's source by using two helical coils where both the current ratio between the coils can be independently controlled and the phase between the currents can be tuned (FIGURE 7a) [15,16]. When the inner and outer coil currents are in phase, the characteristic donut shape in the etch rate distribution across the wafer is observed (FIGURE 7b). Note that varying the current ratio improves the uniformity slightly, but not significantly enough to be production worthy. When

the inner and outer currents are out of phase by 180 degrees, etch rate distribution can be tuned from being edge-high to center-high **(FIGURE 7c)**. By optimizing the inner-to-outer coil current ratio, a very uniform etch rate can be achieved.

#### Pattern collapse

Pattern collapse becomes a significant problem as STI line widths shrink and aspect ratios increase. STI lines may bend when an external force is applied, and the bending distance depends on the magnitude of the force and the stiffness of the line. The external forces might arise from electrical charges, mechanical movement, or capillary forces during wet cleaning. The multiplicity in the origins of the force makes the pattern collapse issue complicated and each case different. In the case where electrostatic forces dominate, plasma etching processes must be tuned to prevent charging. For mechanical shocks, wafer transfer procedures must be adjusted. If the pattern collapse derives from wet cleaning, an alternative cleaning solution or method (e.g. dry cleaning) must be adopted. In summary, external forces should be eliminated or minimized.

From the point of view of line stiffness, the line profile is also important to prevent line sticking. Senturia [17] showed that the stiffness of a line is a function of the material properties and the pattern geometries:

$$k \propto E \cdot A R^{-3} \tag{1}$$

Where, *k* is the line stiffness, *E* is the Young's modulus, and *AR* is the aspect ratio of the line. The high Young's modulus of silicon makes it less subject

**FIGURE 6.** STI profiles at 3mm from the wafer edge (147mm radius) (a) without AEC kit and (b) with AEC kit (processes were not fully optimized).

ETCHING

to pattern collapse than the resist in photo lithography; before the sub-20nm era, line collapse was not a significant issue for STI etching. However, as shown in Eq. 1, the stiffness of a line is inversely proportional to the cube of the line aspect ratio. Thus, as the aspect ratio increases, the propensity for silicon lines to stick to each other increases even under constant external force magnitudes. Moreover, any profile defect, such as local bowing, could significantly decrease the line stiffness. And if the device design and the integration process allow, a tapered line profile might be preferred to prevent line collapse as the feature sizes shrink further.

**FIGURE 7.** Uniformity improvement with reverse source (a) schematic of Mesa source with inner and outer coils, (b) the etching rate distribution with the inner/ outer coil currents in phase, and (c) the etching rate distribution with the inner/ outer coil currents out of phase by 180 degrees. Arrows in (b) and (c) indicate increased inner/outer source current ratio.

#### Conclusion

STI etching has become very challenging in the sub-20nm era. Four major challenges were reviewed in this paper. Intra-cell depth loading could be managed with advanced process tuning, and three general process development rules for avoiding this issue were provided. A combined solution of hardware innovation and process tuning achieved across-wafer etching rate uniformity and uniformity control over profiles near the wafer edge. Sub-20nm node STI features are susceptible to pattern collapse; aside from eliminating or minimizing external forces, a reasonable STI profile should be obtained if bowing is avoided during the plasma etching process. ◆

#### References

- T. Speranza, Y. Wu, E. Fisch, J. Slinkman, J. Wong, and K. Beyer, IEEE/ SEMI Advanced Semiconductor Manufacturing Conference, 59 (2001).

- S. Gaddam and M.W. Braun, IEEE/SEMI Advanced Semiconductor Manufacturing Conference, 17 (2005).

- R.A. Gottscho, C.W. jurgensen, and D.J. Vitkavage, J. Vac. Sci. Technol. B 10, 2133 (1992).

- T. Tanaka, M. Morigami, and N. Atoda, *Jpn. J. Appl. Phys.* 32, 6059 (1993).

- 5. O. Miyahara, K. Tanaka, S. Wakamizu, J. Kitano, and Y. Yamada, Proc.

SPIE 5376, 830 (2004).

- W. Yeh, R.A. Lawson, and C.L. Henderson, *Proc. SPIE* **7972**, 79721X (2011).

- A. Dave, K. Yoshimoto, and J. Sturtevant, *Proc. SPIE* 8326, 83261K (2012).

- K. Yoshioto, C. Higgins, A. Raghunathan, J.G. Hartley, D.L. Goldfarb, H. Kato, K. Petrillo, M.E. Colburn, J. Schefske, O. Wood, and T.I. Wallow, *Proc. SPIE* **7972**, 79720K (2011).

- 9. J.J. Wortman and R.A. Evans, J. Appl. Phys. 36, 153 (1965).

- 10. H. Abe, M. Yoneda, and N. Fujiwara, Jpn. J. Appl. Phys. 47, 1435 (2008).

- S. Banna, A. Agarwal, G. Cunge, M. Darnon, E. Pargon, and O. Joubert, J. Vac. Sci. Technol. A 30, 040801 (2012).

- H. Hoenigschmid, A. Frey, J.K. DeBrosse, T. Kirihata, G. Mueller, D.W. Storaska, G. Daniel, G. Frankowsky, K.P. Guay, D.R. Hanson, L.L. Hsu, B. Ji, D.G. Netis, S. Panaroni, C. Radens, A.M. Reith, H. Terletzki, O. Weinfurtner, J. Alsmeier, W. Weber, and M.R. Wordeman, *IEEE Journal of Solid-State Circuits* **35**, 713 (2000).

- C.J. Radens, U. Gruening, M.E. Weybright, J.K. DeBrosse, R.L. Kleinhenz, H. Hoenigschmid, A.C. Thomas, J.A. Mandelman, J. Alsmeier, and G.B. Bronner. Symposium on VLSI Technology, 36 (1998).

- M.A. Lieberman and A.J. Lichtenberg, "Principles of Plasma Discharges and Materials Processing", 2nd ed., Wiley-Interscience, Hoboken, 2005.

- 15. A. Agarwal, S. Banna, V. Todorow, S. Rauf, and K. Collins, *Trans. Plasma Sci.* **39**, 2516 (2011).

- S. Banna, V.N. Todorow, K.S. Collins, A. Nguyen, M.J. Salinas, Z. Chen, A. Agarwal, A. Pal, T. Wang, S. Rauf, US Patent 2011/0097901 A1.

- S. Senturia, "Microsystem Design," Kluwer Academic Publishers, Boston, 2001.

RELIABILITY

# Statistical variation monitoring for production control

TIMOTHY TURNER, College of Nanoscale Science & Engineering (CNSE), Albany, NY.

The sources of parametric variation are reviewed, with an eye on why these issues become worse as the technology is scaled and how this variation can be monitored and controlled.

s semiconductor technologies become smaller, the processes become more complex. This is a long established trend in the semiconductor industry. Unfortunately, it is not a linear relationship. The relationship is exponential. As we approach the limits of scaling, this exponential effect becomes nearly vertical. In his presentation "Beyond 28nm: New Frontiers and Innovations in Design for Manufacturability at the limits of the scaling roadmap," Luigi Capodieci [1] describes the significant increases in technology required to move from 28 to 20nm. He describes multiple new layers, double patterning and extensive error corrections and review procedures required to achieve the new scaling targets.

Monitoring and controlling the variation in a semiconductor process during production has long been the task of parametric testing. These are electrical tests performed on semiconductor wafers at the end of the production cycle. The parametric variation increases with the square of the number of sources of the variation. Thus, the parametric testing function is stretched even more than the process by the exponential increase in complexity.

In chapter 1 of the book "Low Power Variation-Tolerant Design for Nanometer Silicon" [2] A. Bansai and R. Rao point out sources of manufacturing variation, intrinsic variation and design variation. Design variation is not an issue for parametric test. Process variation has long been the focus of parametric test. However, this focus has long been on lot-to-lot variation, wafer to wafer variation within a lot and site-to-site variation across a wafer (typically center-toedge variation). Unfortunately, at the nanoscale level, transistor-to-transistor or metal line-to-metal line variation is also a concern.

This is a significant departure from historic techniques for parametric test where the structures tested were typically one transistor or one via. To

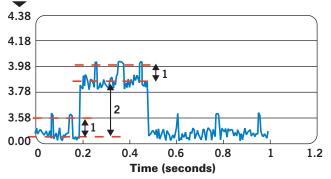

**FIGURE 1.** Charge trapped in the gate oxide modulates the channel current. Shown are two traps: 1 and 2. The peak magnitude of the noise is the sum of all traps.

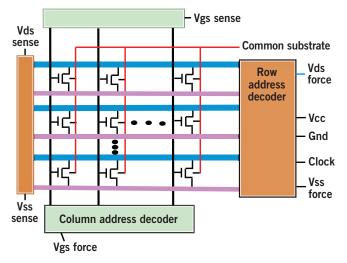

address the element to element variation, statistical structures tabulating the variation of hundreds or thousands of circuit elements is necessary.

Since about the 2 micron generation, parametric test has been limited to scribe lanes. At that technology

**TIMOTHY TURNER**, is the Reliability Center Business Development Manager at the College of Nanoscale Science & Engineering (CNSE), Albany, NY. tturner@albany.edu.

#### RELIABILITY

node, single elements were all that would fit in the scribe lanes. Now, it is possible to place thousands of transistors in a scribe lane structure beside a die that might hold billions of transistors.

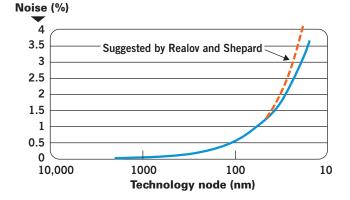

Statistical test structures are required to monitor the changes in variation that are critical to designers. Consider the impact of Random Telegraph Noise. This issue was first identified as a future issue back in the 1980's. Van der Zeil [3] pointed out that Random Telegraph Noise (RTN) was proportional to the inverse of the size of the gate area on the transistor. RTN is caused by traps in the gate dielectric. As shown in FIGURE 1, trapped charge in the dielectric modulates both the number of carriers and the mobility of the carriers under the gate [4]. Large transistors with perhaps hundreds of trap sites per transistor show little impact when one trap fills or emits. At the 45nm node, Realov and Shepard [5] showed that almost half of the transistors contained no traps, but the rest contained as many as five traps per transistor. The probability of holding one or more traps decreased with the gate area, but with a billion transistors on a die, 0.1% would leave 1 million transistors with multiple traps per die.

With 45nm transistors, a single trap caused on the order of a 10% change in the channel current at the worst case bias [5].

Realov and Shepard also showed that van der Zeil was an optimist concerning the scaling implications. They showed that a reduction in channel length could not be compensated by an increase in channel width

**FIGURE 2.** RTN increases with the inverse of the gate area. Realov and Sheppard showed that below 45nm, this increase can be greater, more a function of length than area.

(**FIGURE 2**). With identical effective gate dielectric areas (effective length times effective width), the shorter length transistor would always show a higher amplitude for the noise.

Further adding to the problem is the reduction in signal levels required to scale the gate dielectric voltage when the transistor is scaled. The trap is a fixed charge. Its impact is set by that charge. As we lower the signal level, we increase the percent impact of that charge.

Waltl, Wagner, Reisinger, Rott and Grasser [6] characterized the traps using a technique called Time Dependent Defect Spectroscopy (TDDS). This technique uses a short (1ms) gate voltage pulse to fill the traps, then biases the channel so as to measure the emission of the traps. The traps are characterized by the voltage step when the trap emits and the time since the gate pulse was turned off when the trap emits. This was shown to be a repeatable characterization for each transistor, providing a characterization of the traps in that transistor. This technique allows not only the measurement of the number of transistors that show traps, but a further characterization of the traps.

TDDS can identify 1/f noise sources as well as RTN. When a large number of transistors are measured, a spectrum of the traps available at that site on the wafer is provided. This spectrum can be an important process control tool.

For instance, Pobegen, Nelhieel and Grasser showed the impact of local hydrogen concentration on interface hole traps. This suggests that TDDS could be used to monitor the local hydrogen concentration across

% change in drain current

Time since gate voltage turned off (ms)

**FIGURE 3.** TDDS – Charge emitted from traps after a gate voltage pulse is removed. Multiple charge and discharge repetitions generate the probability clouds around different magnitude and time points [6].

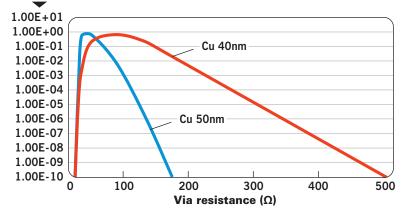

**FIGURE 4.** Via Resistance Distribution for different via sizes (J. W. Sleight et. Al. [7])

a wafer (**FIGURE 3**). Other issues such as radiation damage, charge damage and interface stress may be correlated with TDDS spectra.

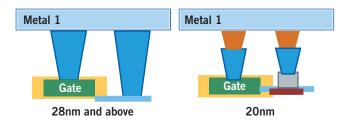

Contact resistance is another statistically distributed function. As shown in **FIGURE 4**, Sleight et. Al. [7] observed that the contact resistance followed an analytical cone model due to variation in the bottom diameter, height and angle of a contact stud. If we now add the process changes projected by Capodieci [1] for 20nm technology, we may see the variation caused by stacking up to 4 via layers below metal 1 (**FIGURE 5**). The variation of each via layer will be a much more tightly distributed parameter than what results when 4 of these layers are stacked.

Line Edge Roughness (LER) is another source of variation [8]. LER on a gate electrode can modify the local channel length resulting in a variation in the transistor's performance. Since this variation provides an effective variation in the transistors

**FIGURE 5.** 20nm technology will require more process steps than previous technology. This will increase the variability in the process parametrics. (Capodieci[1])

channel length and a shorter channel length provides a higher Random Telegraph Noise, LER will introduce still more variation in the RTN.

LER also impacts metal lines. In this case, the resistance of the line will always show the average line width. The metal line resistance is most important for long lines. Long lines tend to average out any line width variation making line resistance insensitive to LER. Unfortunately, linewidth variation correlates with line spacing variation. Line spacing will have a lifetime limited by the shortest space.

Measuring the leakage between two long lines is not an effective way to

measure the variation in the line width. The best way to directly measure the variation is to measure the variation in the voltage required to induce a very low amount of leakage between a large number of shorter metal lines. This will provide the desired statistical variation in the line to line space.

Continued on page 36

**FIGURE 6.** Array of Transistors for Characterization. For instance, the row and column addresses could be generated by two six bit counters allowing the independent characterization of 4096 transistors using only 8 probe pads (Vdsforce, Vdssense, Vgsforce, Vgssense, Vsub, Clock, Vcc, Gnd, Vsforce and Vssense). Adding an on chip A/D converter would decrease measurement time while reducing noise and adding only one serial data port.

## Detection and elimination of a yield-critical non-visual residue defect

SOONHAENG LEE, WISEOK KANG and HOBONG SHIN, Samsung Electronics, Gyeonggi-Do, Korea; SUNGJIN CHO, JAEYOUNG YOU and JEFF HAWTHORNE, Qcept Technologies, Fremont, CA.

A post-wet clean residue that was causing a yield issue was found and eliminated.

ntegrated circuit manufacturers rely heavily on optical inspection techniques to monitor and control manufacturing processes. Optical inspection has proven effective in detecting and classifying a wide range of physical defects on semiconductor wafers, such as pits, particles and scratches. In recent years, circuit features have continued to shrink while semiconductor manufacturers have been introducing many new materials, processes and structures for advanced technologies, such as high-k metal gates, low-k dielectrics and stressed silicon channels. The accelerating pace of change has introduced new types of yield-limiting defects, some of which are not detectable using optical inspection techniques. These defects are sometimes referred to as Non Visual Defects (NVDs), and include sub-monolayer residues, surface contamination and process-induced charging of dielectric films [1-4].

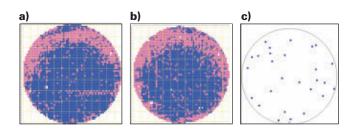

Samsung Electronics and Qcept Technologies previously presented a case study where a chargebased NVD was identified as a precursor to a physical "pitting" defect in the gate oxide process [5]. In this

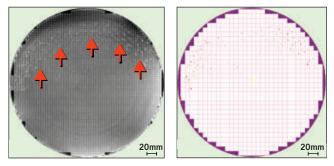

**FIGURE 1.** Images (a) and (b) are sample EOL failure maps that show a common pattern of failed (pink) die across the top of the wafer. Image (c) is a brightfield optical inspection defect map at After Clean Inspect (ACI). Optical inspection provided no indication of the defect causing the yield loss.

article we describe the detection and elimination of a post-wet clean residue on a logic device. The residue defect correlated to a known yield issue from end-ofline (EOL) electrical test. The failed die were clustered in a semicircular arc across the top of the wafer. The defect was believed to occur at the front end of line (FEOL) gate module, but no matching defect pattern was detected by the existing optical inspection tools. The residue defect was ultimately determined

**SOONHAENG LEE** is senior engineer of defect analysis group at Samsung Electronics Co., LTD, Yongin, Gyeonggi-Do, Korea. **WISEOK KANG** is senior engineer of defect analysis group and **HOBONG SHIN** is principal engineer of yield enhancement team at Samsung. **SUNGJIN CHO** is senior application manager at Qcept Technologies, 47354 Fremont Blvd, Fremont, CA. Tel: 510-933-1131, email: jason.cho@qceptech.com. **JAEYOUNG YOU** is senior application engineer at Qcept Technologies Korea, Hwasung, Gyeonggi-Do, Korea. **JEFF HAWTHORNE** is vice president of applications engineering at Qcept Technologies. to be an NVD as detected by a unique, non-optical inspection technique.

The problem was initially noticed when a leadingedge-node logic device was experiencing increased yield loss at EOL electrical test. A large number of die on random wafers from random lots were failing for low grounded voltage of the collector  $(V_{cc})$ . The failures occurred in an arc pattern across the top of the wafer (FIGURE 1), and the failure mode suggested that the defect was happening somewhere in the gate and spacer module. A review of the existing brightfield optical wafer inspection data from the gate and spacer module did not identify a physical defect pattern that matched the yield-loss signature. In an effort to detect and diagnose the problem, inspection was initiated at several process steps within the gate and spacer module using a unique, non-optical inspection technology that is sensitive to a wide range of NVDs, including sub-monolayer contamination and process induced charge.

The inspection system used was the ChemetriQ system from Qcept Technologies. ChemetriQ is a scanning probe system that produces a full wafer image showing changes in the work function of the wafer. The resulting differential data can be numerically integrated and thresholded to detect regions of the wafer with relatively high or low work function. Changes in work function can result from a variety of surface conditions, including changes in surface chemistry, such as residues or contamination. This technique is sensitive to low-level, sub-monolayer contamination that does not scatter light and cannot be detected using traditional optical means.

ChemetriQ inspection was initiated at several process steps in the gate and spacer module, including post gate photo, post gate etch / clean, post spacer deposition, and post spacer etch / ash / clean. These types of partition studies are facilitated by the fact that the ChemetriQ system can scan wafers at many different process steps without modifying the scan recipe, so no time is spent optimizing recipes for each process step. NVD inspection data detected strong spots of increased work function (+WF) at the top portion of the wafer after the spacer etch, ash, and clean steps. The NVDs detected at the spacer process

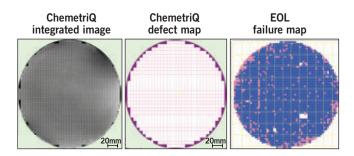

ChemetriQ integrated image

#### ChemetriQ defect map

**FIGURE 2.** The image on the left is a ChemetriQ image showing a residue pattern across the top of the wafer after spacer deposition, etch, ash and clean (red arrows). Areas of increased work function (+WF) appear bright in the image. The image on the right is a defect map created by thresholding the integrated image. The pattern of defects across the top of the wafer closely matched the pattern of EOL yield loss.

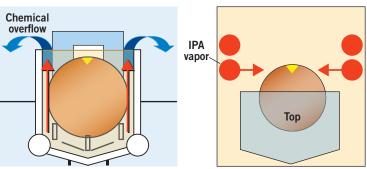

**FIGURE 3.** Diagram of the batch tool used to clean wafers after spacer etch. The wafers were extracted from the bath with the notch up so the rinse water flowed from the bottom (notch side) of the wafer to the top.

were thresholded into Defect Maps as shown in **FIGURE 2**. The number and spatial location of the NVDs correlated with failed die at EOL and closely matched the top of wafer yield-loss pattern.

The partition study provided strong evidence that the defect occurred at spacer etch and clean. The batch wet clean process was targeted as the most likely source of the NVD defect. During the clean process, the wafers were extracted from the batch tool notchedge up, so the rinse water flowed from the notch (bottom) to top of the wafer as shown in **FIGURE 3**. It was suspected that this process might result in less effective rinsing on the top of the wafer.

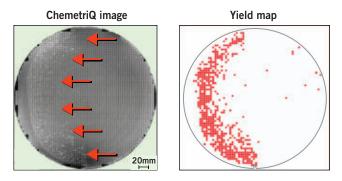

**FIGURE 4.** Sample results from an experiment with wafers rotated 90 degrees in the batch clean tool. Rotating the wafers also rotated the NVD pattern detected by the ChemetriQ inspection system and the pattern of yield loss at EOL test.

An experiment was designed to determine if the defect could be caused by the flow of liquid as the wafers were extracted from the batch wet clean tool. Wafers were loaded in the tool with the notch at 90 degrees. The ChemetriQ images after clean showed that the +WF NVD pattern was rotated by 90 degrees. EOL electrical tests showed that the pattern of failed die was also rotated by 90 degrees (**FIGURE 4**). These results provided convincing evidence that the batch clean tool rinse was leaving a residue on the wafer surface that was causing the yield loss.

Different options were evaluated to eliminate the NVD from the batch wet clean process, including modifying the existing process and switching to a single-wafer clean process. One promising option was to use a new linear, single-wafer clean process for a more robust cleaning process and to eliminate

**FIGURE 5.** Sample inspection and test results for a wafer cleaned with a linear single-wafer clean process. The pattern of positive work function defects was eliminated from the ChemetriQ inspection image and defect map, and EOL yield was increased significantly.

the NVDs. ChemetriQ inspection results on wafers processed with the new linear, single-wafer clean process showed a cleaner and more uniform surface. EOL data also exhibited a significant increase in yield and elimination of the characteristic yield-loss pattern as shown in **FIGURE 5**.

As a result of this work, a linear, single-wafer clean approach was implemented after spacer etch, and the ChemetriQ tool was used to monitor production wafers to insure that the problem did not recur. In addition, Samsung engineers performed parametric tests and device modeling, which confirmed that a negative ionic contaminant was consistent with both the shift in electrical parameters for failed devices and the increase in work function detected by the ChemetriQ system.

#### Summary

In this paper we have presented the detection and elimination of a yield-critical residue at the FEOL gate and spacer module. The contamination responsible for the yield loss is an example of an NVD, which could not be detected using optical inspection. In this case the residue was detected using a scanning probe technique that detects changes in surface work function, which can be induced by chemical contamination or charging of dielectric films. Surface work function inspection results were used to identify and modify the clean process responsible for the defect. As a result, the defect was eliminated and yield was increased. The inspection system was subsequently used to monitor the process to insure that the defect did not recur. ◆

#### References

- J. Park, et al; SEMATECH Surface Preparation and Cleans Conference; Impact of Charge at Gate Oxide Patterning on Yield for an Advanced Technology Node, (2012).

- J. Hallady, et al; SEMATECH Surface Preparation and Cleans Conference; Elimination of ESD Defects Using DICO2, (2008).

- K. Höppner, et al; Advanced Semiconductor Manufacturing Conference; Novel In-Line Inspection Method for Non-Visual Defects and Charging, (2009)

- J. Hawthorne, et al; MICRO; Inspection Wafers Using a Potential Difference Imaging Sensor Method, (2005).

- 5. J. Park, et al; Solid State Technology; Impact of Charge During Gate Oxide Patterning on Yield, (July 2012).

#### SIMULATION

## Multiphysics simulation accelerates the development of electrochemical etching

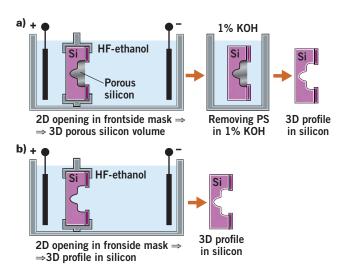

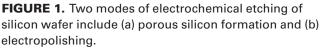

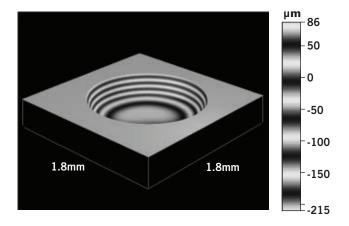

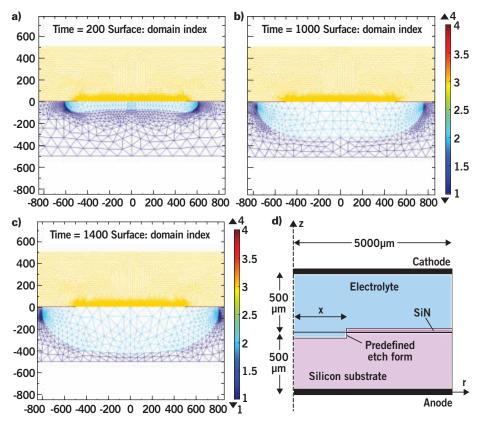

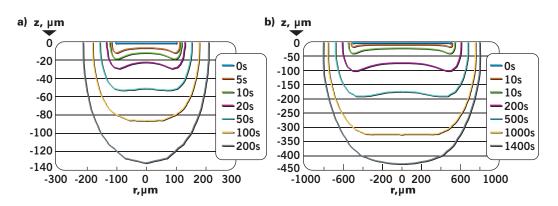

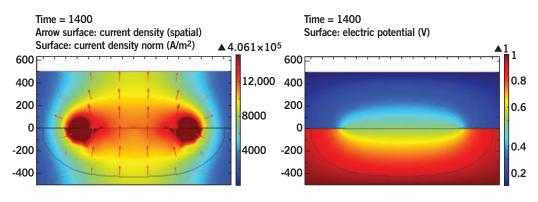

JENNIFER A. SEGUI, COMSOL, Inc., Burlington, MA.