**JUNE 2014**

# SofdState **Insights for Electronics Manufacturing**

WLP of ICs for Mobile **Systems** P. 17

450mm Facility and Infrastructure Requirements P. 20

**ITRS Scouting** Report on Materials P. 24

### **Tuning Up for sub-5nm** Scaling **R** 14

#### SEMICON® West2014

July 8–10 Moscone Center San Francisco

# without limits.

#### Connect to the Future of Microelectronics Manufacturing—Without Limits!

To stay on the cutting-edge of microelectronics design and manufacturing, you need to connect to the people, products, and companies moving Moore's Law, and the best place to connect is SEMICON® West. From the latest research in next-generation materials and device architecture, to the current status of 3D IC, EUV, and 450 mm, no other event brings you closer to more technology, information, or solutions than SEMICON West.

- More than 25,000 attendees

- More than 600 international exhibitors

- More than 50 hours of technical and business programs, including the new Semiconductor Technology Symposium (STS)

Register online through June 6 and SAVE \$100 www.semiconwest.org

#### Solid State TECHNOLOGY.

JUNE 2014 VOL. 57 NO.4

An operator makes an adjustment on an ASML TWINSCAN lithography system. Source: ASML.

#### FEATURES

#### LITHOGRAPHY Scaling to 5nm: A plethora of paths

Continued shrinks will require a mix of different approaches to lithography, device structures and 3D integration. *Debra Vogler, SEMI, San Jose, CA.*

#### ADVANCED PACKAGING Wafer-level packaging of ICs for mobile systems of the future

Wafer-level packaging continues to gain slow IC market share, and novel fan-out redistribution drives the need for improvements in existing packaging materials within tight cost and reliability constraints. *Ed Korczynski, Senior Technical Editor.*

#### **450mm** 450mm transition toward sustainability: Facility and infrastructure requirements

Design and construction professionals are showing unprecedented levels of collaboration through the G450C. Adrian Maynes and Frank Robertson, G450C, Albany, NY.

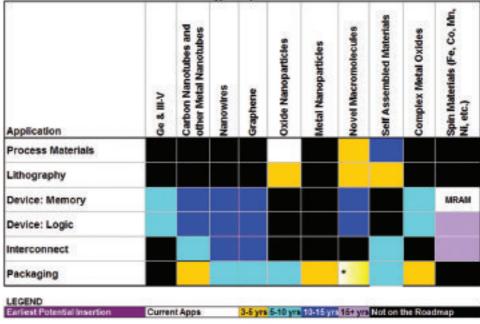

#### **MATERIALS** Scouting report for materials at the end of the road: 2013 ITRS

When pavement ends the terrain gets rough, as documented in Emerging Research Materials chapter of newest ITRS. *Ed Korczynski, Senior Technical Editor.*

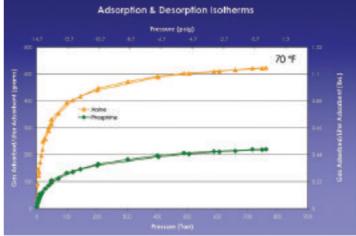

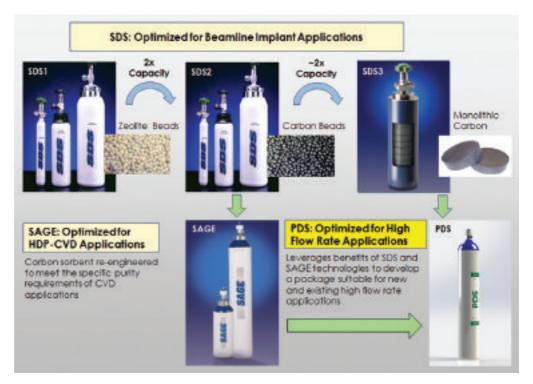

#### **ION IMPLANT** Subatmospheric gas storage and delivery: Past, present and future

Storing gas on a sorbent provides an innovative, yet simple and lasting solution. *Karl Olander, Ph.D., and Anthony Avila, ATMI, Inc., an Entegris company, Billerica, MA*.

#### **ALD** HVM production and challenges of UHP PDMAT for ALD-TaN

For sub-22nm device generations, device manufacturers are likely to adopt PDMAT precursor for ALD-TaN barrier films for copper interconnect structures. *Leijun Hao, Ravi K. Laxman and Scott A. Laneman, Digital Specialty Chemicals, Toronto, Ontario, Canada.*

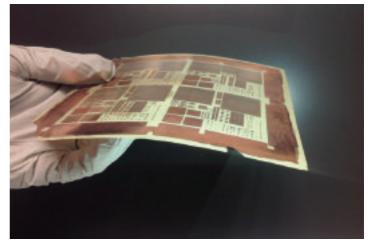

#### **INTERPOSERS** Flexible glass firms branch into new applications

Ultrathin glass is well suited for use as interposers in semiconductor packaging applications. *Juila Goldstein, Senior Associate Analyst, NanoMarkets, Glen Allen, VA.*

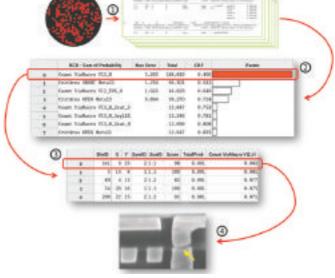

#### **TEST** Noise cancellation: The new failure and yield analysis superpower

Root cause deconvolution is a quick and cost effective way to determine the underlying root causes represented in a population of failing devices from test data alone. *Geir Eide, Mentor Graphics, Wilsonville, OR.T*

#### COLUMNS

- 3 Editorial The next big thing: IoT, Pete Singer, Editor-in-Chief

- 12 Packaging SEMI's 3DIC standards activities, Phil Garrou, Contributing Editor

- 13 Semiconductors Challenges of EUVL HVM, Vivek Bakshi, EUV Litho, Inc.

**41** Industry Forum The sustainable manufacturing imperative, *Karen Savala, President, SEMI Americas*

#### DEPARTMENTS

- 2 Web Exclusives

- 4 News

- 39 Ad Index

# Online@www.solid-state.com

#### Web Exclusives

#### First quarter semiconductor trends

Industry trends show the first quarter of this year being generally stronger than the first quarter of one year ago. SEMI's Dan Tracy reviews the trends and updates.

http://bit.ly/1wlVbRR

#### DAC panels tackle giga-scale design

The ProPlus blog here on Solid State Technology has looked at giga-scale design challenges and, this year, so will the Design Automation Conference (DAC). Dr. Lianfeng Yang of ProPlus Design Solutions blogs on the upcoming DAC.

http://bit.ly/1kpMctq

#### Improving financial predictability: Chasing a mirage?

Prakash Arunkundrum, PwC Strategy and Operations Consulting Director, says there is continued evidence that despite spending several millions on IT transformations, improving internal planning processes, maturing supply chains, and streamlining product development processes- several companies still struggle with predicting their financial and operational performance. http://bit.ly/OZOZxV

#### Can legacy fabs keep up with IoT demand?

The Internet of Things (IoT) is set to drive demand and innovation in the semiconductor market over the next decade. While some consumer IoT applications will require semiconductors manufactured using cutting-edge technologies to deliver fast performance and low power consumption, the vast majority of chips for IoT applications will be utilized in client-side applications. These chips, such as a sensor monitoring room temperature in a connected HVAC system, require processing capabilities that can be met using legacy process (90 and 45nm) technologies manufactured on 200mm wafers. Applied Materials' Jeremy Read writes on this opportunity and challenge for legacy manufacturing. http://bit.ly/1tVGaFc

#### Insertion of EUVL into fab: Challenges for 7nm insertion

While two chipmakers are reported to be working on inserting EUVL into fabs for manufacturing at the 10nm node, many others expect to insert EUVL into manufacturing at the 7nm node or later. It takes a large infrastructure to make EUVL a manufacturing technology. So many tool suppliers, large and small, want to know when EUVL will be inserted into fabs for production and how and how much it will be used. Vivek Bakshi and Sushil Padiyar discuss the challenges of EUVL insertion in this SST blog. http://bit.ly/1qxeC9N

#### Insights from the Leading Edge: More on IBM / GF; SEMI Singapore part 3: Nanium, Fujitsu, EVG

Dr. Phil Garrou blogs on the latest news from GLOBALFOUNDRIES and IBM, and continues his review of Semicon Singapore.

http://bit.ly/1knO7zn

#### Thoughts on MIG Conference Japan

MIG Executive Director Karen Lightman is finally over her jet lag and shares her thoughts from the MEMS Industry Group Conference Japan, MIG's inaugural conference in Asia that was held on April 24. http://bit.ly/lixng2G

#### editorial

#### The next big thing: IoT

The semiconductor industry has greatly benefited from the push to mobile technology, but what's next? It could well be the Internet of Things (IoT), which includes smart homes, smart cars, smart TVs, wearable electronics and beacons. According to an analysis by Business Insider, the Internet of Things alone will surpass the PC, tablet and phone market combined

#### "The future IoT will need better image sensors, embedded DRAMs, high-voltage power ICs, RF, analog, and embedded flash."

by 2017, with a global internet device installed base of around 7,500,000,000 devices.

In a keynote talk at the Advanced Semiconductor Manufacturing Conference (ASMC), John Lin gave some insight into the technology challenges the IoT will create. John is the Vice President and General Manager of Operation of G450C Consortium. Prior to joining G450C, Dr. Lin was the Director of Manufacturing Technology Center in TSMC.

"What is the next big thing?," he asked? In 2014, after mobile computing, we believe it is the Internet of things. Many of the devices needed to connect to the internet will grow very fast. We need to prepare the technology for that." John said the ultra-low power will be a primary concern. Processors, sensors and connectivity will also be key. "To support this at TSMC, we will continue with our ultra-low power efforts and continue to support advanced nodes, from 28, 20, 16 to 10nm." He also said the company will focus on "special" technologies such as image sensors, embedded DRAMs, high-voltage power ICs, RF, analog, and embedded flash. "All this will support all of the future Internet of Things," he said.

The Business Insider report also notes that the wearables, connected car and tv markets will equal the tablet market by 2018. Smart appliances are already going mass market. More than 250,000 Nest thermostats, for example, have already shipped this year. Connected TVs are overtaking traditional TVs: A connection to the internet will become common in fully loaded cars. US regulators are slowly allowing more aerial drones. Also expect to see more "beacons" in retailer establishments, such as Apple's iBeacons, which are used to communicate with shoppers in-store. And the list goes on... are you ready?

-Pete Singer, Editor-in-Chief

#### Solid State TECHNOLOGY.

John Blyler, Vice President, Chief Content Officer Ph: 503.614.1082, jblyler@extensionmedia.com

Pete Singer, Editor-in-Chief Ph: 978.470.1806.

psinger@extensionmedia.com Shannon Davis, Editor, Digital Media Ph: 603.547.5309

sdavis@extensionmedia.com Phil Garrou, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design

#### CREATIVE/PRODUCTION/ONLINE

Spryte Heithecker, Production Manager Yishian Yao, Media Coordinator

- Nicky Jacobson, Senior Graphic Designer

- Caldin Seides, Graphic Designer

Slava Dotsenko, Senior Web Developer

MARKETING/CIRCULATION Jenna Johnson, jjohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, Business Development msterling@extensionmedia.com

John Blyler, Vice President and Chief Content Officer iblyler@extensionmedia.com

June 2014, Volume 57, Number 4 • Solid State Technology ©2014 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmait; \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$200 delsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2343. (8 am – 5 pm, PST).

#### For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816;

Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2014 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107 Please send news articles to sdavis@extensionmedia.com

#### worldnews

**USA GLOBALFOUNDRIES** introduced an optimized semiconductor manufacturing platform aimed specifically at meeting the stringent and evolving needs of the automotive industry.

**USA** | **Avago** completed its acquisition of LSI.

ASIA | SMIC, Wuhan Xinxin, Tsinghua University, Beijing University, Fudan University and the Chinese Academy of Sciences and Microelectronics have collaborated to setup the "IC Advanced Technology Research Institute" to create the most advanced IC technology research and development institution in China.

**USA** | **BASF** opened facility in Hillsboro, Oregon. The new facility is a strategic step towards establishing a North American footprint to supply materials for semiconductor manufacturing applications related to the electronics industry.

**EUROPE** | **Brooks Automation** announced a definitive agreement to acquire Dynamic Microsystems Semiconductor Equipment, based in Radolfzell, Germany.

**EUROPE** | Element Six announced that its Gallium Nitride (GaN)on-Diamond wafers have been proven by Raytheon Company to significantly outperform industry standard Gallium Nitride-on-Silicon Carbide (GaN-on-SiC) in RF devices.

#### **USA** | Mentor Graphics

announced that it has acquired Nimbic, Inc., a provider of Maxwell-accurate, 3D full-wave electromagnetic (EM) simulation solutions.

Applied Materials introduces the biggest materials change to interconnect technology in 15 years

In May, Applied Materials, Inc. announced its Applied Endura Volta CVD Cobalt system, the only tool capable of encapsulating copper interconnects in logic chips beyond the 28nm node by depositing precise, thin cobalt films. The two enabling applications, a conformal cobalt liner and a selective cobalt capping layer, provide complete enclosure of the copper lines, improving reliability by an order of magnitude. The introduction of cobalt as a superior metal encapsulation film marks the most significant materials change to the interconnect in over 15 years.

"The reliability and performance of the wiring that connects the billions of transistors in a chip is critical to achieve high yields for device manufacturers. As wire dimensions shrink to keep pace with Moore's Law, interconnects are more prone to killer voids and electromigration failures," said Dr. Randhir Thakur,

Continued on page 6

#### Google Glass is far more than the sum of its parts, IHS Teardown reveals

Teardown analysis is a useful tool for understanding the component and manufacturing cost of electronics devices—but it doesn't always tell the whole story of the value of a product.

Case in point is Google Glass, which sells for \$1,500—but has hardware and manufacturing costs that amount to just \$152.47, according to a dissection of the product conducted by the Teardown Analysis Service at IHS Technology. Does that mean that Google is pocketing a sky-high margin of 90 percent on each Glass sale? Not by a long shot.

"As in any new product—especially a device that breaks new technological ground—the bill of materials (BOM) cost of Glass represent only a portion of the actual value of the system," said Andrew Rassweiler, senior director, cost benchmarking services for IHS. "IHS has noted this before in other electronic devices, but this is most dramatically illustrated in Google Glass, where the vast majority of its cost is tied up in non-material costs that include non-recurring engineering (NRE) expenses, extensive software and platform development, as well as

Continued on page 7

#### SEMATECH achieves breakthrough defect reduction in EUV mask blanks

SEMATECH announced this month that researchers have reached a significant milestone in reducing tool-generated defects from the multi-layer deposition of mask blanks used for extreme ultraviolet (EUV) lithography, pushing the technology another significant step toward readiness for high-volume manufacturing (HVM).

Following a four-year effort to improve deposition tool hardware, process parameters and substrate cleaning techniques, technologists at SEMATECH have, for the first time, deposited EUV multi-layers with zero defects per mask at 100nm sensitivity (SiO2 equivalent). Eliminating these large "killer" defects is essential for the use of EUV in early product development. These results were achieved on a 40 bi-layer Si/Mo film stack and measured over the entire mask blank quality area of 132×132 mm2.

#### Continued on page 8

#### SRC and UC Berkeley pursue more cost-effective approach to 3D chip integration

University of California, Berkeley researchers sponsored by Semiconductor Research Corporation (SRC) are pursuing a novel approach to 3D device integration that promises to lead to advanced mobile devices and wearable electronics featuring increased functionality in more low-profile packages.

The research focuses on integrating extra layers of transistors on a vertically integrated 3D monolithic chip using printing of semiconductor "inks" as compared to the current method of

Continued on page 8

#### **news**cont

#### Strengthening recovery: Fab equipment spending

After two years of decline, fab equipment spending for Front End facilities in 2014 is expected to increase 24 percent in 2014 (US\$35.7 billion) and about 11 percent (US\$39.5 billion). In terms of equipment spending, 2015 may reach or even surpass historic record year 2011 (about US\$39.8 billion). For the May 2014 SEMI World Fab Forecast publication, SEMI tracked more than 200 major projects involving equipment spending for new equipment or upgrades, as well as projects to build new facilities or refurbish existing facilities. In the last three months, 265 updates were made to the database (Figure 1).

In 2014, the three largest regions for fab equipment spending will be Taiwan with over US\$10.3 billion, the Americas with over US\$6.8 billion, and Korea with over US\$6.3 billion. In 2015, these same regions will lead in spending: Taiwan will spend over US\$11 billion, Korea over US\$8 billion, and the Americas almost US\$7 billion.

|                  | 2012 | 2013 | 2014 | 2015 |

|------------------|------|------|------|------|

| Americas         | -15% | -34% | 36%  | 2%   |

| China            | -40% | 32%  | 69%  | -6%  |

| Europe & Mideast | -38% | -33% | 79%  | 21%  |

| Japan            | -43% | 8%   | 11%  | 15%  |

| Korea            | 0%   | -37% | 23%  | 27%  |

| SE Asia          | -49% | 53%  | -43% | 44%  |

| Taiwan           | 4%   | 13%  | 11%  | 7%   |

| SUM              | -18% | -12% | 24%  | 11%  |

(For Front End Facilities includes new, used, in-house).

Source: SEMI World Fab Forecast reports (May 2014)

Although in sixth in regional equipment spending this year, the Europe/Mideast region will show the strongest rate of growth, about 79 percent compared to the previous year. The same region will continue to grow fast in 2015, with an increase of about 20 percent.

Worldwide installed capacity is very low for both 2014 and 2015 and the SEMI data does not suggest that this will change over the next four years. Because of the increased complexity of leading-edge nodes, such as more process steps and multiple patterning, fabs experience a decline in capacity as the same fab space produces less. Worldwide, installed capacity grew by less than 2 percent in 2013 and is expected to grow just 2.5 percent in

Continued on page 10

#### Continued from page 4

executive vice president and general manager of the Silicon Systems Group at Applied Materials. "The Endura Volta system builds on Applied's precision materials engineering leadership by delivering CVD- based cobalt liner and selective cobalt capping films that overcome these yield-limiting issues to enable our customers to scale copper interconnects to beyond the 28nm node."

The Endura Volta CVD system, with its two new process steps, represents a major technology extension for copper interconnects beyond 28nm. The first step involves the deposition of a thin, conformal CVD cobalt liner to increase the gap fill window of copper in narrow interconnects. This process improves the performance and yield of the device by integrating the pre-clean, PVD barrier, CVD cobalt liner and copper seed processes under ultra-high vacuum on the same platform. capping step, is deposited after CMP to encapsulate the copper lines for enhanced reliability performance. Complete envelopment of copper lines with cobalt creates an engineered interface that demonstrates over 80x improvement in device reliability.

"Applied's unique CVD cobalt processes represent an innovative materials-enabled scaling solution," said Dr. Sundar Ramamurthy, vice president and general manager of Metal Deposition Products at Applied Materials. "It is deeply satisfying that these materials and process innovations in development for almost a decade are now being adopted by our customers for their high-performance mobile and server chips."  $\diamond$

The second step, a new "selective" CVD cobalt

Continued from page 4

tooling costs and other upfront outlays. When you buy Google Glass for \$1,500, you are getting far, far more than just \$152.47 in parts and manufacturing."

#### Looking through the Glass

Google Glass carries a BOM of \$132.47. When the \$20.00 manufacturing expense is added, the cost to produce the head-mounted computer rises to \$152.47.

The attached table presents the preliminary BOM of Google Glass. Note that this teardown assessment is preliminary in nature, accounts only for hardware and manufacturing costs, and does not include other expenses such as software, licensing, royalties or other expenditures.

#### Prototypical

Although thousands of units are in the hands of users, Google Glass is not yet generally available through retail. The pre-mass-market status of Google Glass is evident by examining its design.

"Today's Google Glass feels like a prototype," Rassweiler said. "The design employs many off-the-shelf components that could be further optimized. If a mass market for the product is established, chip makers are expected to offer more integrated chipsets specific to the application that will greatly improve all aspects

Continued on page 9

#### reduce soft errors

#### Deliver more density on flip chip IC packages without increasing soft errors, using low alpha plating anodes.

Honeywell RadLo<sup>™</sup> low alpha packaging materials help minimize soft errors and single event upsets by reducing alpha emissions, a significant source

of these problems. Our low alpha plating anodes are used in wafer bumping applications for today's high-performance, high-density devices. We provide Pb and Sn-based plating anodes in various low alpha grades, helping you meet critical alpha emission levels.

**Honeywell reliability. Reliable low alpha.** In addition to plating anodes, Honeywell RadLo products include plating solution materials and solder feedstock—all backed by our robust supply chain and industry-leading expertise in low alpha refining and metrology.

#### Find out more by visiting us at www.honeywell-radlo.com

Although all statements and information contained herein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information are results obtained. Statements or suggestions concerning the use of metrials and processes are made without representation or warranty that any such use is free of patent infringement and are not recommendations to infringe any patent. The user should not assume that all toxicity data and safety measures are indicated herein or that other measures may not be required. ©2014 Honeywell International Inc. All rights reserved.

#### Continued from page 5

In addition, by subtracting out incoming substrate defects, SEMATECH has demonstrated that the multilayer deposition process itself can achieve zero defects down to 50nm sensitivity. Coupled with novel improvements to the mask substrate cleaning process to remove incoming defects, this represents the capability to both extend EUV to future nodes by eliminating smaller "killer" defects, and as a step to reducing smaller defects (which can be mitigated) to a level where improved yield and mask cost make EUV a more cost-effective HVM technology.

"SEMATECH's comprehensive programs continue to produce the results that our members and the industry need to show that EUV lithography is manufacturable," said Kevin Cummings, SEMATECH's Lithography manager. "Our Advanced Mask Development program continues to demonstrate practical results for mask blank defect reduction, more efficient deposition and cleaning, effective reticle handling, and other areas that the industry will need for successful EUV lithography manufacturing."

Defects are generally created by the deposition process or formed by decoration of substrate defects during the multilayer deposition process. These types of defects have prevented the quality of mask blanks from keeping pace with roadmap requirements for the production of pilot line and high-volume manufacturing EUV reticles. Reducing defects in the EUV mask blank multilayer deposition system is one of the most critical technology gaps the industry needs to address to enable cost-effective insertion of this technology at the 16nm half-pitch.

"A low defect density reflective mask blank is considered to be one of the top two critical technology gaps for the commercialization of EUV," said Frank Goodwin, manager of SEMATECH's Advanced Mask Development program. "Through sophisticated defect analysis capabilities and processes, the goal of our work is to enable model-based prediction and data-driven analysis of defect performance for process improvement and component learning. We then use these models to feed into the new deposition tool design." ◆

#### Continued from page 5

chip-stacking through 3D interconnect solutions.

The new process technology could help semiconductor manufacturers develop smaller and more versatile components that are less expensive and higher performing by enabling cost-effective integration of additional capabilities such as processing, memory, sensing and display. The low-temperature process is also compatible with polymer substrates, enabling potential new applications in wearable electronics and packaging.

Current efforts on 3D integration have used transfer of thin single crystal semiconductor layers, polycrystalline silicon deposited by chemical vapor disposition, or other growth techniques to realize integrated devices.

"Compared to these approaches, we believe our approach is simpler and potentially with significantly lower cost," said Vivek Subramanian, professor of Electrical Engineering and Computer Sciences at UC Berkeley. "Our goal in this work is to maximize performance, with the hope that this will make the cost versus performance tradeoff worthwhile relative to other approaches."

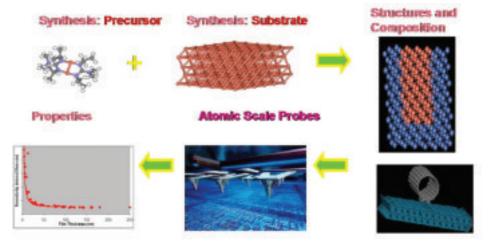

Specifically, the UC Berkeley team is developing directly-printed transparent oxide transistors as a path to realizing additional layers of active devices on top of CMOS metallization.

To fabricate such devices, new material and process methodologies are needed for depositing nanoparticles for semiconductors, dielectrics and conductors. The research is particularly focused on solution-based processing due its low temperature compatibility with CMOS metallization as well as the potential for lower cost manufacturing.

"Initial results from the Berkeley team show that reasonably high performance can be obtained from ink-jet printed devices with process temperatures that are compatible with post-CMOS metallization, thus enabling a new route to monolithic 3D integration," said Bob Havemann, Director of Nanomanufacturing Sciences at the SRC.  $\triangleleft$

Continued from page 7

of performance, including processing speed, energy efficiency, weight and size. Future product revisions are sure to make strides in all of these areas."

#### Last year's model

Most of the integrated circuits (ICs) in Google Glass are mature when compared with recent flagship smartphone designs. For example, the Texas Instruments Inc. OMAP4430 apps processor used in Google Glass is made with 45nm semiconductor manufacturing technology—two generations behind the 28nm chips employed in the latest flagship smartphones.

The use of more cutting-edge ICs could yield future Google Glass products that are smaller, lighter, more energy-efficient and less costly to produce than the current model.

#### **High cost for LCOS**

The second most expensive single component in Google Glass is also its most defining feature: its head-mounted liquid-crystal on silicon (LCOS) projector display. IHS estimates the cost of the Himax Technologies Inc. LCOS projection element made by Taiwan's Himax Technologies Inc. at \$20.00, accounting for 15 percent of the total Glass BOM.

"The LCOS display is the sine qua non of the Glass," Rassweiler noted. "Just as e-readers wouldn't exist without their e-lnk screens, Glass wouldn't be possible with the LCOS display. The display is pretty slick, providing a near-eye viewing experience that must be seen to be believed."

#### **Texas Instruments inside**

Texas Instruments components dominate the Glass design, with the semiconductor supplier contributing the apps processor, power management IC, audio codec, battery fuel gauge and regulator ICs. Altogether, TI accounts for an estimated \$37.90 worth of components identified so far in the Glass, representing 29 percent of the BOM.

IHS Figure: Major Components in Google Glass (Preliminary Pricing in US Dollars)\*

| <b>Direct Material Costs</b> |            | \$                                                                                                                            | 132.47         |

|------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|

| Conversion Costs             |            | \$                                                                                                                            | 20.00          |

| Total Cost                   |            | \$                                                                                                                            | 152.47         |

| Price                        |            | Description                                                                                                                   |                |

| \$                           | 22.00      | Frame assembly, titanium assumed                                                                                              |                |

| s                            | 20.00      | LCOS panel, color sequential, 0.22 inch, 640 x 3<br>with embedded timing controller and thermal se                            |                |

| s                            | 12.50      | Budget estimate for all box contents including st<br>case, premium USB cable, custom charger, ear<br>packaging and literature |                |

| \$                           | 10.00      | Flash, eMMC NAND, 16GB, MLC                                                                                                   |                |

| \$                           | 8.85       | Apps processor, TI OMAP4, Dual                                                                                                |                |

| \$<br>\$                     | 8.35       | Prism optics and LCOS-related films, plus budg<br>for hinge assembly and plastic case<br>SDRAM, mobile DDR2, 1GB, PoP         | etary subtotal |

| 3                            | 7.50       | Budget estimate for plastics and other mechani                                                                                | and alkall     |

| \$                           | 6.65       | components                                                                                                                    | Gai srieli     |

| \$                           | 5.25       | Camera module, 5MP                                                                                                            |                |

| \$                           | 4.10       | Budget estimate for rest of PCB components and PCB<br>substrate                                                               |                |

| 2000 000                     | 1010103303 |                                                                                                                               |                |

Source: IHS Technology, May 2013

\*Consists only of top 10 components

#### Sensory overload

Glass includes two accelerometers: one from STMicroelectronics and another from InvenSense Inc. Accelerometers are commonly used to detect motion in electronic devices, such as smartphones and video-game controllers. Given that smartphones generally incorporate just one multiaxis accelerometer, the use of two of these devices represents an interesting and unusual design choice that must be further investigated to be understood.

#### **Premium rush**

The frame of the Glass represents the single most expensive component of the device, at \$22.00, or 17 percent of the BOM. The frame is made of titanium, a highly durable and expensive material used in high-performance military aircraft and in some eyeglass frames. However, titanium is rarely used in commercial electronic devices analyzed by the IHS Teardown Analysis Service.

"The frame is just one aspect of how Google is presenting Glass as a premium product," Rassweiler noted. "The quality of the packaging and accessories, along with how the box contents are staged, gives the whole Google Glass experience a very high-end feel and appeal."

Continued from page 6

2014 and 3 percent in 2015.

SEMI's detailed data predict that Foundry capacity continues to grow at 8-10 percent yearly (a steady pace since 2012) and Flash is up 3 to 4 percent for 2014. Although DRAM equipment spending is expected to grow by 40 percent in 2014 as many fabs upgrade to a leading-edge process, installed capacity for DRAM is expected to stay flat or even drop 2 percent. SEMI's reports also cover capacity changes for other product segments: MPU, Logic, Analog/ Mixed signal, Power, Discretes, MEMS, and LED and Opto.

The SEMI World Fab Forecast uses a bottom-up approach methodology, providing high-level summaries and graphs, and in-depth analyses of capital expenditures, capacities, technology and products by fab. Additionally, the database provides forecasts for the next 18 months by quarter. These tools are invaluable for understanding how the semiconductor manufacturing will look in 2014 and 2015, and learning more about capex for construction projects, fab equipping, technology levels, and products.

#### The SEMI Worldwide

Semiconductor Equipment Market Subscription (WWSEMS) data tracks only new equipment for fabs and test and assembly and packaging houses. The SEMI World Fab Forecast and its related Fab Database reports track any equipment needed to ramp fabs, upgrade technology nodes, and expand or change wafer size, including new equipment, used equipment, or in-house equipment.  $\triangleleft$

#### Synopsys, STMicroelectronics and Samsung to collaborate on adoption of 28nm FD-SOI

Synopsys extended its collaboration with STMicroelectronics to include Samsung Electronics, enabling broader market adoption of ST's 28nm FD-SOI technology for SoC design. This collaboration extends the Galaxy design flow to Samsung in support of their strategic agreement to offer dual sourcing of ST's 28nm FD-SOI technology. Developed over a multiyear collaboration with ST, the design flow enables concurrent area, power and timing optimizations to enable engineers to optimize their designs for the ST 28nm FD-SOI process. "The close collaboration between ST design teams and Synopsys led to advanced silicon-proven design enablement solutions that fully leverage the performance and power promise of FD-SOI technology and provide the foundation needed to meet tight time to market windows," said Philippe Magarshack, executive vice president, Design Enablement and Services, STMicroelectronics. "Our close collaboration with Synopsys has already enabled many successful tapeouts with mutual customers using Synopsys' Galaxy Design Platform and Lynx Design System." The Synopsys design flow for ST's 28nm FD-SOI is compatible with the Lynx Design System, a fullchip design environment providing innovative automation and visualization capabilities that enable higher designer productivity and faster design closure. A technology plug-in using ST's 28nm FD-SOI Process Design Kit (PDK), standard cells and memories, adapts the productionproven Galaxy Design Platformbased RTL-to-GDSII flow for 28nm

FD-SOI SoC designs, accelerating project setup and execution. Lynx automation simplifies and accelerates many critical implementation and validation tasks, including backbias management across the flow, special connection checks, In-Design physical verification for well connections and UPF supply set management for N-wells and P-wells. Faster electronic device architectures are in the offing with the unveiling of the world's first fully two-dimensional field-effect transistor (FET) by researchers with the Lawrence Berkeley National Laboratory (Berkeley Lab). Unlike conventional FETs made from silicon. these 2D FETs suffer no performance drop-off under high voltages Ali Javey, a faculty scientist in Berkeley Lab's Materials Sciences Division and a UC Berkeley professor of electrical engineering and computer science, led this research in which 2D heterostructures were fabricated from layers of a transition metal dichalcogenide, hexagonal boron nitride and graphene stacked via van der Waals interactions. "Our work represents an important stepping stone towards the realization of a new class of electronic devices in which interfaces based on van der Waals interactions rather than covalent bonding provide an unprecedented degree of control in material engineering and device exploration," Javey says. "The results demonstrate the promise of using an all-layered material system for future electronic applications." Javey is the corresponding author of a paper describing this research in ACS Nano titled "Field-Effect Transistors Built from All

Two-Dimensional Material Components". Co-authors are Tania Roy, Mahmut Tosun, Jeong Seuk Kang, Angada Sachid, Sujay Desai, Mark Hettick and Chenming Hu. FETs, so-called because an electrical signal sent through one electrode creates an electrical current throughout the device, are one of the pillars of the electronics industry, ubiquitous to computers, cell phones, tablets, pads and virtually every other widely used electronic device. All FETs are comprised of gate, source and drain electrodes connected by a channel through which a charge-carrier either electrons or holes - flow. Mismatches between the crystal structure and atomic lattices of these individual components result in rough surfaces - often with dangling chemical bonds - that degrade charge-carrier mobility, especially at high electrical fields. "In constructing our 2D FETs so that each component is made from layered materials with van der Waals interfaces, we provide a unique device structure in which the thickness of each component is well-defined without any surface roughness, not even at the atomic level," Javey says. "The van der Waals bonding of the interfaces and the use of a multi-step transfer process present a platform for making complex devices based on crystalline layers without the constraints of lattice parameters that often limit the growth and performance of conventional heterojunction materials." Javey and his team fabricated their 2D FETs using the transition metal dichalcogenide molybdenum disulfide as the electroncarrying channel, hexagonal boron nitride as the gate insulator, and graphene as the source, drain and gate electrodes. All of these constituent materials are single crystals held together by van der Waals bonding. For the 2D FETs produced in this study, mechanical exfoliation was used to create the layered components. In the future, Javey and his team will look into growing these heterogeneous layers directly on a substrate. They will also look to scale down the thickness of individual components to a monolayer and the lengths of the channels to molecular-scale dimensions.

#### Global semiconductor industry posts highest-ever first quarter sales

The Semiconductor Industry Association this month announced that worldwide sales of semiconductors reached \$78.47 billion during the first quarter of 2014, marking the industry's highest-ever first quarter sales. Global sales reached \$26.16 billion for the month of March 2014, an increase of 11.4 percent from March 2013 when sales were \$23,48 billion and a slight uptick of 0.4 percent compared to last month's total of \$26.04 billion. Regionally, sales in the Americas increased by 16.1 percent compared to last March, and year-to-year sales increased across all regions. All monthly sales numbers are compiled by the World Semiconductor Trade Statistics (WSTS) organization and represent a threemonth moving average.

"The global semiconductor market has demonstrated consistent momentum in recent months, and sales are well ahead of last year's pace through the first quarter of 2014," said Brian Toohey, president and CEO, Semiconductor Industry Association. "Perhaps most impressively, sales in March increased across all regions and every semiconductor product category compared to last year, demonstrating the market's broad and diverse strength."

Regionally, year-to-year sales increased in the Americas (16.1 percent), Asia Pacific (12.9 percent), Europe (8 percent), and Japan (0.4 percent), marking the first time in more than three years that year-to-year sales increased across all regions. Sales were up compared to the previous month in Europe (3.9 percent), Asia Pacific (1.4 percent), and Japan (0.3 percent), but down slightly in the Americas (-4.3 percent).

"Although recent semiconductor sales are encouraging, one threat to the semiconductor market's continued growth and America's overall economic strength is the innovation deficit the gap between needed and actual federal investments in research and higher education," Toohey continued. "Policymakers should act swiftly to close the innovation deficit by committing to robust and sustained investments in basic scientific research and higher education."

#### SEMI's 3DIC standards activities

I have said many times that it will be impossible for a complicated technology like 3DIC to ever become commercial without standardization. SEMI has been working on this now for 3+ years. Let's take a look at their recent update from their SEMICON Singapore presentation. So far, they have published the following standards: SEMI 3D1-0912, Terminology for Through Silicon via Geometrical Metrology

Clear and commonly accepted definitions are needed for efficient communication and to prevent misunderstanding between buyers and vendors of metrology equipment and manufacturing services.

The purpose of this Document is to provide a consistent terminology for the understanding and discussion of metrology issues important to through silicon vias (TSV).

#### SEMI 3D2-1113, Specification for Glass Carrier Wafers for 3DS-IC

- This Specification describes dimensional, thermal, and wafer preparation characteristics for glass starting material that will be used as carrier wafers in a temporary bonded state;

- Methods of measurements suitable for determining the characteristics in the specifications indicated.

SEMI 3D3-0613, Guide for Multi-Wafer Transport and Storage Containers for 300 mm, Thin Silicon Wafers on Tape Frames

-Address the methods for shipping thin wafers on tape frames.

SEMI 3D4-0613, Guide for Metrology for Measuring Thickness, Total Thickness Variation (TTV), Bow, Warp/Sori, and Flatness of Bonded Wafer Stacks

– Control of bonded wafer stack (BWS) thickness, total thickness variation (TTV), bow, warp/sori, and

flatness metrology, is essential to successful implementation of a wafer bonding process.

man more

Packaging

This std provides a description of tools that can be used to determine these key parameters before, during, and after the process steps involved in wafer bonding.

SEMI 3D5-0314, Guide for Metrology Techniques to be used in Measurement of

**Dr. Phil Garrou,** Contributing Editor

Geometrical Parameters of Through- Silicon Vias (TSVs) in 3DS-IC Structures

– This std assists in the selection and use of tools for performing measurements of geometrical parameters of an individual TSV (through-silicon via), or of an array of TSVs.

SEMI 3D6-0913, New Standard: Guide for CMP and Micro-bump Processes for Frontside Through Silicon Via (TSV) Integration

- This std provides a generic middle-end process flow to define acceptable TSV and CMP quality criteria as well as to develop methodology and measuring procedures for micro-bump.

#### SEMI 3D7-0913, New Standard: Guide for Alignment Mark for 3DS-IC Process

Photo alignment mark configuration is the key to ensure consistent and precise alignment of layers, chips and wafers.

- This standard provides an alignment mark strategy for chip to chip, chip to wafer, and wafer to wafer stacking.

SEMI also has organized task forces in North America, Taiwan and Japan focused on various aspects of 3DIC manufacturing and testing. The North America task force is focused on:

*Bonded Wafer Stacks* – Create and/or modify specifications that reflect bonded wafer stacks parameters and the wafer bonding process.

Inspection & Metrology – Develop standards for metrology and inspection methods to be used for measuring TSV properties, bonded wafer stacks, and dies used in the 3DIC manufacturing process. Thin Wafer Handling – Develop standards for reliable handling and shipping of thin wafers, dies (e.g., Micropillar Grid array -MPGA) used in 3DIC high-volume manufacturing (HVM). ◆

# Challenges of EUVL HVM

Most of the papers at this year's EUVL Conference during SPIE's 2014 Advanced Lithography program focused on topics relating to EUVL's entrance into high volume manufacturing (HVM).

In their paper, GLOBALFOUNDRIES compared EUVL and ArF immersion scanners for 20/14nm metal lines and found equal yields for both lithography techniques. They did note an additional issue of EUV mask backside contamination, which I believe can be addressed. For 10/7nm metal lines, they believe they need to address issues of overlay, mask defects, integration and line width roughness (LWR) through focus, in order to bring EUVL into production.

Imec presented a preliminary cost of ownership (COO) study that concluded that at the 7 nm node, 75 wafers per hour (WPH) throughput will be needed for EUVL to show better COO than ArF immersion (ArFi) multiple patterning (MP). This throughput corresponds to 100 W of source power at the intermediate focus.

HVM-related metrics such as yield and availability (mean time to failure [MTTF], mean time to repair [MTTR], etc.) are now the focus. It was evident from the talk by TSMC, which reported ~10 W of power instead of the expected 30 W for their planned insertion of EUVL into the 10 nm node. A laser misalignment caused a source breakdown and a two-week unexpected downtime for the tool. Although some saw this as a setback, a brand new tool's first installation in the field can be expected to have glitches and downtime. TSMC reconfirmed their commitment to bring EUVL into HVM at the 10 nm node.

Mark Philips of Intel, in his talk, outlined the

#### Semiconductors

1-D grating and cuts approach of Yan Borodovsky. EUVL is the preferred choice for cuts as EUVL offers advantages in terms of number of masks and edge placement error (EPE). Intel still plans to insert EUVL at the 7 nm node in 2017, but needs a mature COO for EUVL. It will be either mix and match with ArFi MP or EUVL alone, depending upon the cost drivers.

Vivek Bakshi, EUV Litho, Inc.

As the mix and match approach faces the issue of overlay, he presented a detailed model, developed with Mike Hanna of ASML, that identifies the root cause of machine to machine overlay values and will help minimize it. Current machine to machine overlay (EUVL and ArFi) is 5 nm but needs to be 3.5 nm at 10 nm nodes and 3.0 nm at 7 nm node. My perception is that with the amount of effort going into it, those goals can be achieved.

Hynix, in their paper on EUVL development efforts, made a comment that self-aligned quadruple patterning (SAQP) has 5x more steps than EUVL and that many multiple patterning steps take away any benefit that one can expect from it, and hence are not beneficial.

ASML currently has three NXE 3300B, HVM level scanners being installed in the field, including one at TSMC. They reported 30 W power (down from 50 W reported in the lab last year) with 100 W planned for this year and 250 W for next year. We know that TSMC had only 10 W at the time of conference. With ASML acquiring Cymer, I expected a change in how data is presented, with more realistic roadmaps. I understand that to predict the readiness of source is very hard, as there are many new technologies that may do well in the lab with a dozen PhDs fine-tuning them, but aren't necessarily ready for the field where they have to perform 24 x 7 while being operated by technicians.

My personal opinion is that if we can get 50 W with decent availability in the field this year for 3300 B, it will be a great achievement. 100 W will follow over the coming years and I cannot predict yet when 250 W sources will be ready. With the data that I currently have seen, I will stick with my predictions. ◆

#### Scaling to 5nm: A plethora of paths

#### DEBRA VOGLER, SEMI, San Jose, CA

Continued shrinks will require a mix of different approaches to lithography, device structures and 3D integration.

revious semiconductor technology generations developed more clearly defined "winners" in terms of process technologies and materials choices. As the industry goes below 14nm, however, it appears that there will be multiple technologies used along the way. For lithography, that includes the further extension of 193i, plus the inclusion of EUVL, directed selfassembly (DSA), maskless lithography (ML2), and more. For transistor scaling, it could be some combination of nonplanar device structures and non-silicon materials (e.g., III-V), but it could also mean that, depending on the application, a company might want to choose a nontraditional scaling path such as 3D integration.

#### Lithography: keeping all options open

Immersion lithography at 193nm is still very much alive - and while the industry works to ready EUVL for highvolume manufacturing (HVM), Nikon's position has been to maintain the 193 infrastructure and keep improving 193 tools to support multiple patterning and other technologies that are coming into play. "It was premature to declare 193i dead," according to Stephen Renwick, senior research scientist at Nikon Research Corporation of America. "It's still very much alive and a viable option as we go into 10nm and 7nm (FIGURES 1, 2)." As part of its immersion lithography extension pipeline, the company's model S622D is shipping now and is being used at 14nm, with end users looking to extend it to the 10nm logic node. "The S630D is coming soon and is intended to be used at 10nm and extended to the 7nm logic node," said Renwick, who will present at the "Readiness of Advanced Lithography Technologies for HVM" session (part of the new Semiconductor Technology Symposium) at SEMICON West 2014 (www.semiconwest.org).

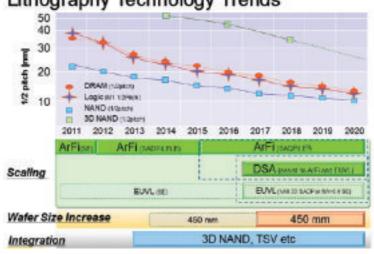

#### Lithography Technology Trends

FIGURE 1. Lithography technology trends. Source: Nikon

One next-generation lithography (NGL) technology that Nikon has been evaluating is directed self-assembly (DSA). It is the scanners that make the guide patterns used to guide the block copolymers that self-assemble, so the company was interested in anticipating what might be needed in terms of additional performance requirements on 193 immersion scanners (e.g., overlay, CD uniformity) to make the guide patterns. Rathsack, et al., (Adv. Litho. 2012, Proc. SPIE, #8323) have achieved 12.5nm lines/spaces using 100nm guide patterns, which are approximately the 7nm node requirements. According to Renwick, to meet these DSA requirements at 7nm, a 193i scanner needs an overlay ≤2nm and single-digit CDU — requirements the company can fulfill. The company's S630D is already able to meet the requirements and the S622D is coming along, noted Renwick.

Also working to extend 193i lithography with complementary solutions such as DSA and maskless lithography (ML2) is CEA-Leti, with its IMAGINE (for ML2)

LITHOGRAPHY

and IDEAL (for DSA) programs. The IMAGINE Program is charged with developing and industrializing electron beam high-throughput maskless lithography developed by MAPPER Lithography. Members include: MAPPER, TSMC, STMicroelectronics, Nissan Chemical, TOK, JSR Micro, Sokudo, TEL, Mentor Graphics, and Aselta Nanographics. According to Serge Tedesco, lithography program manager at CEA-Leti, ML2 offers a production price reduction for low- and mid-volume applications. "This technique appears quite attractive for coping with the increasing difficulties relative to the patterning of critical levels, such as contact layers, and the cut level in the case of complementary lithography," Tedesco told SEMI.

At the present time, the IMAGINE program's pre-production Matrix 1.1 platform is making steady progress. The installation at Leti began in July 2013 and the first exposure is scheduled for June 2014. The Matrix 1.1 comprises 1300 x 49 beams to reach a throughput target of 1wph. The specifications on this pre-production platform are identical to the production version (i.e., 32nm L/S, 10nm overlay). To build up the infrastructure to support the platform, Leti has interfaced the tool

with the Sokudo DUO track. Work is on-going with resist suppliers and the data base infrastructure for e-beam proximity correction (EPC) is being handled by Aselta — a Leti start-up. Additionally, Mentor Graphics and Mapper announced a partnership to support the Matrix data format.

The next phase of the pre-production IMAGINE program is getting the platform to 10wph (Matrix 10.1) using 13000 beams. The Matrix platform roadmap places the 10.1 phase starting at about Q4/14 and going until Q1/15. After that comes development of an HVM tool the Matrix 10.10 — that will have 10 clustered 10wph/module modules for a throughput of 100wph (FIGURE 3).

Regarding Leti's DSA activities, Tedesco reports that its IDEAL program is making progress on both the materials and process integration fronts. "Resolution, CD control and defectivity are in the range of what will be needed for implementation of the technology," said Tedesco. He added that the addition of partners such as TOK, ASML, and Mentor Graphics will ensure the infrastructure will be ready. Tedesco will also present at the "Readiness of Advanced Lithography Technologies for HVM" session.

Also on the DSA front, another European project called PLACYD was launched earlier this year by Arkema, Leti, and 9 other European partners. The project will set up a dedicated materials pilot line at Arkema (in Lacq, France) to supply block copolymers for DSA lithography. The objective is to provide such materials that are precisely defined, with high purity, and that are highly reproducible on an industrial scale.

Regarding ML2 and DSA, Tedesco is rather upbeat about the future. "Complementary and cost-effective

|           | Fin/Act                     | Gate                 | Metal         | Via           |

|-----------|-----------------------------|----------------------|---------------|---------------|

| 193i 10nm | SADP+Cut<br>SAQP+Cut<br>DSA | SAQP+Cut<br>LELE     | SADP          | LELE<br>DSA   |

| 193i 7nm  | SAQP+Cut<br>DSA             | LELE+Cut<br>SADP+Cut | SAQP<br>DSA   | LELELE<br>DSA |

| EUV 7nm   | SADP+Cut<br>DSA             | SE+Cut               | SE+Cut<br>DSA | SE DSA        |

FIGURE 2. Options for different nodes. Source: Nikon

# <section-header><section-header><section-header><section-header><text><text><text>

TO LEARN MORE, VISIT WWW.PLASMAETCH.COM

\$ 5,900 USD

LITHOGRAPHY

solutions, such as DSA and ML2 could help extend 193i much further than originally anticipated," he said.

#### Scaling transistors: a matter of function

It may be less clear what will be sorted out for transistor scaling as the industry gets closer to the 5nm node. There are many choices that will need to be made just for materials, i.e., substrate, channel, and gate. Add in the different types of device architectures — FinFET, gate-all-around, and even unconventional choices such as tunnel FETs and nanowires — and you have a toss-up delimited by device application. An Chen, senior member of the technical staff

FIGURE 3. IMAGINE roadmap. Source: CEA-Leti

at GLOBALFOUNDRIES and Chair of the ITRS Emerging Research Devices Working Group, told SEMI that there is no consensus on the device/material choices. Will building a consensus even make sense? It seems unlikely. "Companies may run into different challenges and reach different conclusions on the same technology," said Chen. "The maturity level of technology development among different companies will also affect their opinions on technology options." Adding to the mix is the fact that different applications require different device characteristics, so a particular company's focus could affect its preferences on technology options, he observed. Chen will present at the "Getting to 5nm Devices: Evolutionary Scaling to Disruptive Scaling and Beyond" STS session at SEMICON West.

The plethora of directions and choices is not the only wrench in the works. "The increasing cost of R&D and decreasing return in the semiconductor industry do not appear to be sustainable," stated Chen. Still, he doesn't think that development will slow down because of funding challenges, though he does believe that fewer and fewer companies will be able to afford the high cost of R&D for scaling. Indeed, even some consortia are collaborating with each other and more companies may start looking for alternatives, he observed. "There is a lot of research on beyond-CMOS technologies, but they seem to be more suitable to augment CMOS rather than to replace CMOS. And low power has been a common feature of many beyond-CMOS devices, which could become increasingly useful because of applications driven more and more by portability and mobility." Chen further observed that functional diversification or enhancement — e.g., 3D integration — may enable better system functionalities without relying on scaling.

The term "functional diversification" has been used by ITRS participants when they started to look into the "More than Moore" (MtM) directions the industry could take, explained Chen. "Instead of being driven by scaling (or nodes), MtM focuses more on functionalities that may be enabled by technologies beyond digital computing," said Chen. Examples of such functionalities are analog, sensing, and energy harvesting.

Regarding funding sources and possible disruptive technologies, Chen noted that a few years ago, the industry was talking about what technology can be found to extend scaling substantially beyond extreme CMOS. Research funded by programs such as DARPA, SRC, etc., might not be the most appropriate uses for such technologies. "Many of them may be better used — together with a CMOS platform — to create new functions or improve efficiency," said Chen. But such programs might not necessarily help with physical scaling.

Hear from the experts — live! This year, SEMI announced the new Semiconductor Technology Symposium (STS), to be held July 8-10 as part of the SEMICON West 2014 technical and business program agenda. The new paid program addresses the most important and critical issues facing the future of semiconductor manufacturing in a new and more technical conference format. More information and pricing for the STS sessions is available at www.semiconwest.org/sts.

Learn more about the new Semiconductor Technology Symposium sessions and other front-end programs at SEMICON West 2014 (www.semiconwest.org). Free registration for SEMICON West is available — includes free access to the exhibition hall plus all TechXPOT sessions, keynotes and executive panels. Register for SEMICON West 2014: www.semiconwest.org/register. ◆

# Wafer-level packaging of ICs for mobile systems of the future

ED KORCZYNSKI, Senior Technical Editor

Wafer-level packaging continues to gain slow IC market share, and novel fan-out redistribution drives the need for improvements in existing packaging materials within tight cost and reliability constraints.

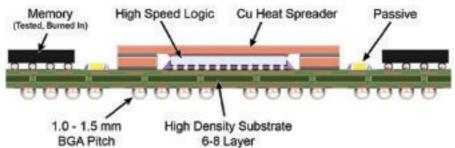

he most functionality at the least cost is the promise of wafer-level packaging (WLP) when dealing with complex integrated circuits (IC) with a high number of input/output connections to the outside world. Integration of heterogeneous circuit functions -- such as micro-

and graphics-processing, field-programmable gate array (FPGA) logic, dynamic and static memory, radio-frequency (RF) and analog, and sensing and actuating --may also be needed at the package-level to be able to deliver complete systems (FIGURE 1).

In particular, electronic systems for high-growth mobile applications require low-power and low-volume per element which dis-allows circuit integration at the printed-circuit board

(PCB) level. Instead, heterogeneous integration must occur as either a system-in-package (SIP) or a system on-chip (SOC). Dr. Eric Mounier of Yole Développement, presented at the recent European 3D TSV Summit 2014 held in Grenoble, and showed Yole forecasts that total world-wide semiconductor IC wafers packaged at the wafer-scale will be 19% this year, raising to 20% in 2015.

One way of looking at the history of the IC industry is to examine the dynamic between SIP and SOC approaches. New functionalities tend to be first integrated into hardware as dedicated additional chips, to be connected in to the rest of the system as part of a PCB or SIP. Since different functionalities often require different fab processes, it is generally less expensive at the chip-level to divide functionalities into different chips, but then the packaging costs tend to be higher. Relatively low-volume parts

**FIGURE 1.** Heterogeneous System-in-Package (SiP) as an extension of proven flip-chip (FC) packaging technology. (Source: Amkor)

may be most economically delivered as SIP, while higher-volume parts can often justify the additional design and test expenses of delivering the same functionality as a single SOC.

The other major reason to go with an SIP is to improve the yield of large area chips at the leading edge of fab processing. Since defects/area tend to be relatively high with a new fab process, very large chip designs will have relatively low yield at first but then will improve as the fab learns how to reduce both random and systematic yield limiters. The recent

ED KORCZYNSKI is the Senior Technical Editor for Solid State Technology and Semiconductor Manufacturing & Design (SemiMD.com).

excellent example of this trend is the Xilinx Vertex-7 FPGA which splits the chip into four sub-chips and then uses a silicon interposer for SIP re-integration. We may expect that a next-generation of the

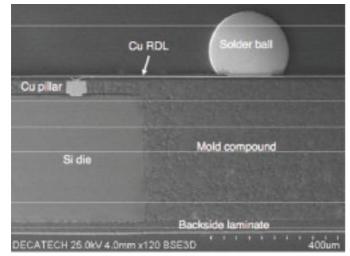

**FIGURE 2.** Cross-section of edge of FO-WLP using Cu-pillars and over-mold approach. (Source: Deca Technologies)

product would be built in a single SOC after the yield improves, at which point Xilinx would be expected to extend the product line with additional functionality added in using multi-chip SIP.

#### Fan-Out WLP

Steffen Kroehnert, director of technology for Nanium S.A., gave a recent presentation at SEMICON/Singapore 2014 titled "Wafer Level Fan-Out as Fine-Pitch Interposer." Fan-In WLP uses layout package connections within the chip area, and when the scale and count of on-chip bond pads does not match with standard packaging scales, a Re-Distribution Layer (RDL) of metal interconnect can be used to Fan-In to ball-grid or pillar-grid arrays (BGA/PGA) within the chip-area. However, when the needed number of connections cannot be made within the chip area, packaging filler materials can be used to provide physical area adjacent to an original chip such that package connections can be arranged to Fan-Out WLP solutions use "Fan-Out" out from the chip center when seen from above.

Chip-Package-Board simultaneous co-design and co-development are becoming important instead of serial work, according to Kroehnert. The penalty for re-design costs and losing strategic time-to-market for a new SiP is too high for allow for iterative R&D, such that products must be co-designed properly the first time.

#### FO-WLP leveraging PV fab tricks

Deca Technologies, the electronic interconnect solutions provider to the semiconductor industry owned by Cypress Semiconductor, recently announced that it has shipped its 100-millionth component. The company attributes this milestone to strong demand from portable electronics manufacturers for wafer-level chip scale packages (WLCSP) manufactured using Deca's unique, integrated Autoline production platform, which is designed to achieve faster time-to-market at lower cost.

Leveraging volume production technologies from leading silicon PV manufacturer SunPower Corp., Deca quickly achieved this milestone by addressing cycle time and capital cost challenges that semiconductor device manufacturers have struggled with using conventional approaches to WLCSP manufacturing. Deca claims that other FO-WLP technologies suffer from inherent manufacturing and reliability issues due to discontinuity at the silicon:mold-compound interface, which are avoided by the company's use of copper-pillars and an over-mold approach (FIGURE 2).

Demand for WLCSP is being driven by manufacturers of wireless connectivity, audio, and power management components for mobile markets. Demand fluctuations in these markets can lead to challenges in managing inventories. "Congratulations to the Deca team on achieving this significant milestone," said Brent Wilson, senior vice president of the Global Supply Chain Organization at ON Semiconductor. "Deca's innovative technologies and focus on customer service have made the company a valuable part of our supply chain."

"Reaching 100 million units is an important milestone for Deca because it validates our unique approach to WLCSP manufacturing," said Chris Seams, CEO of Deca Technologies. "Based on the demand forecasted by our customers, we anticipate passing the half-billion mark in unit shipments this year."

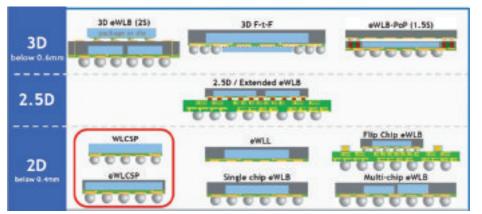

**FIGURE 3.** Schematic cross-sections of various Fan-Out WLP packages. (Source: STATSChipPAC).

#### **FO-WLP for the future**

STATSChipPAC (SCP) recently announced FlexLine<sup>™</sup> FO-WLP. The FlexLine flow dices and reconstitutes incoming wafers of various sizes to a standard size, which results in wafer level packaging equipment becoming independent of incoming silicon wafer size. The SCP FlexLine process flow is based on the SCP commercial eWLB FO-WLP process (FIGURE 3). Single and multi-die fan-out package solutions have been in high-volume manufacturing since 2009 with more than a half-billion units shipped.

Earlier this year, Digitimes provided a brief English translation of some Chinese-language Economic Daily News (EDN) saying that Taiwan Semiconductor Manufacturing Company (TSMC) plans to increase IC packaging revenues to US\$1 billion in 2015 and to US\$2 billion in 2016. TSMC co-CEO C.C. Wei reportedly acknowledged that the production cost for silicon-substrate SIP (TSMC's variant termed "chipon-wafer-on-substrate" or "CoWoS") packages is relatively high, and so the world's leading IC foundry intends to invest in FO-WLP technologies to be able to offer advanced packaging at a reduced price.

Wafer-level packaging continues to gain slow IC market share, and novel fan-out redistribution drives the need for improvements in existing packaging materials within tight cost and reliability constraints. With silicon-interposers and copper-interconnects part of WLP technology, the lines between chip and package have never been less clear. Managing all of this complexity is business as usual when designing mobile systems of the future. ◆

# 450mm transition toward sustainability: Facility and infrastructure requirements

ADRIAN MAYNES and FRANK ROBERTSON, G450C, Albany, NY.

450mm

Design and construction professionals are showing unprecedented levels of collaboration through the G450C.

ard data and strong collaboration are proving effective in solving the challenges inherent in building 450mm semiconductor fabs. In the past year, the Facilities 450mm Consortium (F450C) -- the facilities-focused off-shoot of the Global 450mm Consortium — has provided the unified forum to test and analyze utility requirements, overhead conveyance systems and energy-efficiency strategies. The Global 450mm Consortium (G450C), a New York-based public/private program with leadership from GLOBAL-FOUNDRIES, IBM, Intel, Samsung, TSMC and the College of Nanoscale Science and Engineering is housed on SUNY's University at Albany campus and maintains focus on 450mm process and equipment development (FIGURE 1). Combined, preliminary results from these consortia are building the framework for this next-generation fab.

The F450C came into existence in 2013 facing a series of significant technical hurdles.

The purpose of the 450mm fab is to manufacture more advanced integrated circuits at lower cost with a lighter environmental footprint. However, the initial 450mm tool guidelines point to a greater cost per square foot (meter) of cleanroom space, much heavier structural loads and significantly larger tool sizes, which can detract from the manufacturing flexibility the industry seeks. The potential for competing visions among industry leaders and the cyclicality of semiconductor demand in the marketplace add head winds on the path toward widespread 450mm adoption. These factors pose challenges that will need to be managed to ensure 450mm program objectives are achieved.

• All key players are coming together

• CNSE is providing a uniquely neutral and technologically advanced home for critical research

• Work of the F450C is being guided by a strict application of an inside-out design approach

• Key advances have been made in utility requirements, overhead conveyance systems and energy-efficiency strategies

Data are pointing to promising advantages of the 450mm model, which may support broad industry adoption

#### A collaborative approach

When the complexity of the semiconductor manufacturing process adds the scale of a 450mm wafer, the facility requirements can seem immense. The current scale of today's 300mm factories indicates that managing the size and complexity is key to attaining the efficiencies needed for 450mm adoption. Driving to GLOBALFOUNDRIES' massive facility in upstate New York, for example, feels more like approaching a coliseum than a manufacturing fab (FIGURE 2).

Naturally, the industry is closely examining impacts

**ADRIAN MAYNES** was appointed as the M+W U.S., Inc. Program Manager for the Facility 450mm Consortium (F450C) in August of 2013. **FRANK ROBERTSON** is an Intel Corporation assignee to G450C.

to the facility infrastructure along with the increase in wafer size, since merely scaling the manufacturing process is not practical. The size of the 450mm fab and its associated utility consumption projections would exceed affordability and exacerbate sustainability concerns without close focus on potential efficiencies.

The facility experts involved in establishing and implementing 450mm infrastructure requirements are facing a similar degree of challenges as the integrated circuit and equipment manufacturers.

Design and construction professionals are showing unprecedented levels of collaboration through the G450C to deconstruct semiconductor facility matter associated with 450mm adoption. This consortium formed in the summer of 2013 to unite collective industry expertise to tackle pressing 450mm facility

and infrastructure issues. With a special focus on safety, cost, schedule, sustainability and environmental footprint, this group aims to: reduce production cost; increase manufacturing productivity; and reduce the environmental load associated with each chip manufactured.

#### **Everything starts at the process level**

Early development of 450mm silicon and infrastructure began before the turn of the decade, yet it wasn't until 2013 that 450mm and 300mm process tools began to progress synchronously through technology development at CNSE. The function, operation and shape of a semiconductor facility are driven by the process technology and its corresponding manufacturing requirements. Design progresses from the inside out, starting with the process, in this sequence:

1. Process: the early development of silicon and infrastructure defines the utility process requirements

2. Equipment & Automation: process requirements dictate the process equipment/ tools

3. Production Environment: process equipment defines the manufacturing environment and critical process systems (power,

**FIGURE 1.** The College of Nanoscale Science and Engineering NanoFab Xtension, which houses 25,000 ft2 of cleanroom for 450mm research and development. Source: CNSE.)

FIGURE 2. GlobalFoundries Fab8.1 located in Malta, NY.

water, vacuum, chemicals and gases)

4. Site Infrastructure: the facility and its corresponding site requirements are developed

Equipment suppliers have begun providing tools so that G450C can create a 450mm baseline. Industry guidance is for some 450mm tools to maintain 300mm footprint normalized to throughput. Through working with original equipment manufacturers (OEMs) and suppliers, it becomes clear that some tools required to manufacture wafers are bigger and many components are heavier than their 300mm counterparts. This led members of Semiconductor Equipment and Materials International (SEMI) to prioritize the topic of "cranes and hoists" in a survey of potential 450mm standardization focus areas in late 2012. Members of the G450C agreed that industry alignment was needed to deal with the handling of components for 450mm equipment that might be larger and heavier than those currently lifted manually.

In March 2014, a multifaceted work group consisting of IC makers, OEMs, and facility systems suppliers published an initial set of component lifting systems for 450mm fab equipment. The Component Lift working group addressed a number of IC maker concerns around interference with overhead track automation systems, ceiling loading and fab layout flexibility. This led to almost immediate determination that ceiling-mounted cranes generally would not work for wafer fabs. Three broad classes of component lifting were then identified:

1. Generally light-duty custom fixtures integrated with and often mounted on the tools for specific component handling operations

2. Aisle-based mobile lift mechanisms operating from

the periphery of the tools, capable of multiple configurations for somewhat heavier payloads

3. Gantry-like structures addressing the full span of large (e.g., cluster) tools, capable of heavy lifting and conveying payloads beyond the tool periphery

In a 10-month span, the Component Lift working group published a cost of ownership model, safety imperatives, productivity suggestions and other key considerations in their March 2014 guidelines. While more work awaits, this effort is indicative of a new era in which industry collaboration lays the foundation for 450mm success.

#### **Correctly sizing utilities**

Vital to the 450mm program's success is the ability to create an efficient manufacturing facility that builds upon industry know-how and lessons learned from prior technologies. Yesterday's approach of examining singular utility systems and then searching for ways to improve their individual efficiency is not sufficient. Facility designers must consider how process equipment and facility systems interact as a whole.

In the fall of 2013, the F450C conducted a survey with all aforementioned 450mm consortium member companies to build a roadmap based on the industry's priority focus areas. A plurality of polled members identified 450mm factory utility right-sizing as the top priority for the F450C. Simply stated, we want smarter utility consumption data to enable more efficient 450mm factories, not singular systems, but as a whole factory.

A "utility right-sizing" focus group was created and has been working since the fall of 2013 to characterize true 450mm utility consumption and requirements. Using the inside-out design process, the first step is to conduct real-time measurements for all critical 450mm process tools.

A critical step in the semiconductor manufacturing process is that of wet process, in which liquid chemicals remove materials from a wafer. This step is well known for its high usage of power, water, drains and chemicals. The G450C and F450C members are installing a series of monitoring devices on CNSE's first 450mm wet process tool.

Haws Corporation, a F450C member company, has donated a series of effluent monitoring systems

that enable utility characterization for acid waste neutralization drains, HF drains and exhaust. By characterizing drain effluents, the industry can more intelligently identify opportunities for reuse, reclaim and recycling. M+W Group, CH2M Hill and the G450C are collaborating to install power and flow meters on this same tool. In the second quarter of 2014, the group will conduct real-time utility measurements at idle, operational and peak modes, and combine the data with 300mm benchmarks to assemble the most comprehensive factory utility model in the history of our industry.