**JUNE 2015**

# State

Conductive **Filaments** in Resistive Memories P. 20

**Cutting-edge** Displays

P. 23

**Better Forecasting Drives Profitability**

P. 33

### **Cu CMP Cleans with Reduced Defects and Lower CoO** P 15

### Fast, Smart, Flexible

### One unified platform for the entire machine!

At Omron, we deliver a comprehensive range of products and services designed to increase the speed, versatility, and safety of your machines.

Empower your production with highly advanced solutions that have the proven reliability to maximize your customers' loyalty. If you are developing a new machine or upgrading an existing model, look to Omron as your knowledgeable partner for superior automation.

# Discover how we can increase your packaging profitability.

OMRON AUTOMATION AND SAFETY • Toll free: 800.556.6766 • www.omron247.com

# **Solid State TECHNOLOGY**

JUNE 2015 VOL. 58 NO.4

The Applied Reflexion® LK Prime<sup>™</sup> CMP system provides superior wafer polishing performance with nanometer-level precision for FinFET and 3D NAND applications.

#### FEATURES

20

#### PLANARIZATION | Reduced defectivity and cost-of-ownership copper CMP cleans

A new, low pH, BTA free, noble-bond chemistry produced equivalent yield at substantially lower costs. Christopher Eric Brannon, Texas Instruments, Dallas, TX

#### MEASUREMENT | A novel characterization technique unveils the 3D structure of conductive filaments in resistive switching memories

Imec researchers have developed a novel technique - termed conductive atomic force microscopy tomography (or scalpel C-AFM) – that enables a three-dimensional characterization of emerging logic and memory devices. Umberto Celano, imec, Leuven, Belgium

#### **DISPLAYS** The impact of consumer demand for cutting-

#### edge display technology on the gases market

How gases are used in the manufacture of displays is being impacted by new technologies, consumer demand, and the burgeoning China market.

Eddie Lee, Linde Electronics, Hsin Chu, Taiwan

### 28

#### DISPLAYS | Going organic: The cost-down route to foldable display manufacture

Organic semiconductors now offers the performance, cost and route to adoption, for foldable displays, from ultra-thin, conformal, wearables to truly foldable smartphones and tablets. Dr. Michael Cowin, SmartKem Ltd., St Asaph, Wales.

578

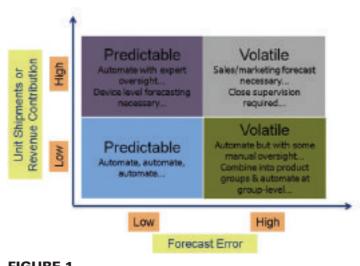

#### FORECASTING | Drive profitability through better forecasting

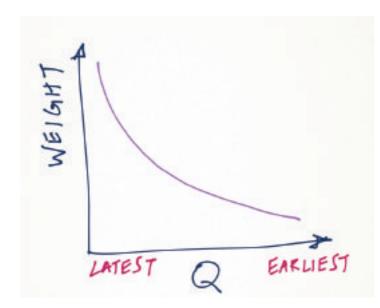

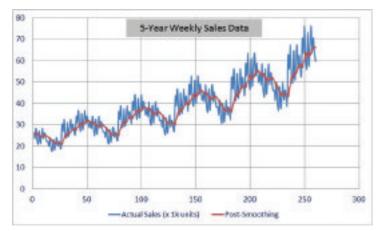

Different forecasting algorithms are highlighted and a framework is provided on how best to estimate product demand using a combination of qualitative and quantitative approaches. Jitesh Shah, Integrated Device Technology, San Jose, CA

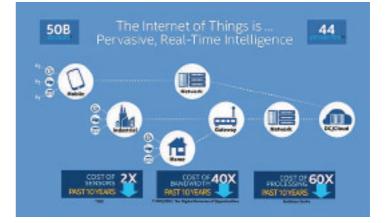

#### SEMICON WEST | How emerging IoT impacts the semiconductor sector

At Semicon West in July, a big focus will be on how the Internet of Things explosion could potentially impact the semiconductor industry.

Paula Doe, SEMI, San Jose, CA

#### COLUMNS

- 2 Editorial IoT, Healthcare and 5G: Are We Ready?, Pete Singer, Editor-in-Chief

- Packaging FOWLP and embedded packaging, Phil Garrou, Contributing Editor 13

- Semiconductors | Safe CMP slurries, Ed Korczynski, Sr. Technical Editor 14

- 41 Industry Forum 50 Years of Moor's Law, Dr. Randhir Thakur, Executive Vice President, General Manager, Silicon Systems Group, Applied Materials, Inc.

#### DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 40 Ad Index

### editorial

### IoT, Healthcare and 5G: Are We Ready?

Imagine the world in 2020, only five years from now. If predictions hold true, more than 50 billion devices will be connected to the Internet (creating the Internet of Things), through smart homes, smart cities, smart factories, smart everything.

Two recent Cisco studies show that \$19 trillion in IoT value is at stake in the private (\$14.4 trillion) and public (\$4.6 trillion) sectors. The studies see, for example, \$2.5 trillion in value from better use of assets, improving execution and capital efficiency, and reducing expenses and cost of goods sold.

In 2020, cars could be driving themselves and people could be monitoring their health through a variety of smartwatches and other wearables. And, of course, smartphones will continue to proliferate.

5G could also become a reality as early as 2020 (some estimate it will be later, perhaps 2025). Carriers' base stations can handle hundreds of simultaneous users now, but that's not enough to accommodate the billions of new devices that will hook into the Internet of Things. Some estimate that equipment makers will need to increase base station connectivity capacity by a factor of 1,000. How all of this will impact the semiconductor industry remains to be seen. Certainly, it will be a boon to the trailing-edge technology (i.e., 65nm and above). It will also be beneficial to the RF and microwave arena. Consider RF chips in smartphones. Instead of 30-40 cents for RF chips in a 2G phone, chipmakers will see \$2 to \$3 in a lower-end 3G smartphone. It then rises to \$4 to \$6 for a mid-tier LTE smartphone and \$10-plus for high-end global LTE smartphones. No estimate yet on 5G smartphones, but it's sure to be more.

It's almost sure to create even more demand for the very leading edge semiconductor chip, such as those found in the high end servers used to crunch huge amounts of data in "the cloud."

Where companies seem to be struggling now is with integration and packaging. It's not yet clear if the existing infrastructure will be able to adequately address the rapidly evolving needs of new markets, such as wearables. But that's a good kind of problem to have.

-Pete Singer, Editor-in-Chief

### **Solid State** TECHNOLOGY.

Pete Singer, Editor-in-Chief Ph: 978.470.1806, psinger@extensionmedia.com

Shannon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczynski, Senior Technical Editor, edk@extensionmedia.com

Jeff Dorsch, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design CREATIVE/PRODUCTION/ONLINE Spryte Heithecker, Production Manager Stephanie Bradbury, Media Coordinator Nicky Jacobson, Senior Graphic Designer Caldin Seides, Graphic Designer

Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION Jenna Johnson,

jjohnson@extensionmedia.com

#### June 2015, Volume 58, Number 3 • Solid State Technology ©2015 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for air mail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2342.(8 am − 5 pm, PST).

#### **CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, Business Development msterling@extensionmedia.com

#### For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2015 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

### Expertise in Wet Etch & Clean System

Visit us at SEMICON West 2015, Booth 433 - South Hall

#### 300mm Single Spin Wet Etching & Cleaning System

#### APOLLON

- High throughput (up to 330 WPH)

- Multi-chemical process (maximum 3 chemicals)

- Reduced chemical consumption by recycling

- Small footprint (2200mm  $\times$  4000mm)

- Individually controlled chamber

- 8-chamber double-decker (SS-D Type)

#### 300mm HDI Non-ashing & Resist-stripping System

#### **HTS-300S**

- Minimum consumption of chemical (≤ 150cc/wafer)

- Temperature control by IR heater ( $\leq 240^{\circ}$ C)

- Reduced chemical fumes by flip-over processing

- Minimum process time for stripping ( $\leq 30$  seconds)

- Contamination control with separate chambers

- 4 SPM + 4 cleaning-chamber double-decker

#### 300/200mm Wet Batch Station

#### **BW SERIES 3000/2000**

- Photo resist stripping / nitride removing / wet etching

- High throughput (up to 500 WPH)

- High-temperature processing ( $\leq 165^{\circ}$ C)

- Nitride pullback in 3D flash memory

- 50 wafers/batch, immersion type

#### 4"/6" Lift-off Process Technology for LED

#### **EVOLUTION**

- Vertical wafer loading into immersion bath

- Single spin processing with multi-level chamber

- Easy and efficient chemical reclaim

- Simultaneously clean the both sides of wafer

- Combining dip and spin process technologies

# online@www.solid-state.com

### Web Exclusives

## Trends in Materials: The Smartphone Driver

View on-demand this free webcast where John Borland reviews the current doping and Fin/channel mobility enhancement techniques used for 22nm FinFET production by Intel for both high performance logic and SOC devices and the changes they made for their 2nd generation 14nm FinFET. Apple A6 and A7 used Samsung/Foundry's 32nm and 28nm technology while the A8 uses TSMC's 20nm technology. Later this year, Apple will introduce the A9 which will switch from 2-D planar to 3-D FinFET using both Samsung's 14nm FinFET and TSMC's 16nm FF+ technologies.

#### http://bit.ly/1HoYOMt

# Apple Watch launch confirms WiFi and NFC inside

Dick James at Chipworks takes a look at what's inside the new Apple Watch. He says they won't be going for the gold Edition model, even so some of us here would like to; the Sport version should be quite good enough.

#### http://bit.ly/1El99z0

### Insights from the Leading Edge

Eighteen months after announcing a deal to Tokyo Electron, Applied Materials has announced that the \$7B deal will not go through due to regulatory concerns. The two companies said the decision for terminating the deal came after the U.S. Department of Justice told the companies that their proposals for a combined business were not good enough to replace the competition lost from a merger.

http://bit.ly/1bY6l3y

### Moore's Law to keep on 28nm

Scaling is now bifurcating – some scaling on with 28/22nm, while other push below 14nm. In his famous 1965 paper Cramming more components onto integrated circuits, Moore wrote: "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year". Dimensional scaling below 28nm will only increase the 'component cost' as we described in Moore's Law has stopped at 28nm and is detailed in the following tables published recently by IBS. http://bit.ly/1A0vM5k

# news and blogs

### Innovation in semiconductors provides hope

A new study coauthored by Wellesley economist, Professor Daniel E. Sichel, reveals that innovation in an important technology sector is happening faster than experts had previously thought, creating a backdrop for better economic times ahead. http://bit.ly/1F2Ath0

### IEDM announces 2015 Call for Papers

The 61st annual IEEE International Electron Devices Meeting (IEDM) has issued a Call for Papers seeking the world's best original work in all areas of microelectronics research and development. The paper submission deadline is Monday, June 22, 2015 at 23:59 p.m. Pacific Time. http://bit.ly/1FbOebp

### It's blue skies for Jabil and its customers

While making printed circuit boards is still a big business for the St. Petersburg, Fla.-based Jabil, which boasts 90 plants in 24 countries around the world, the Blue Sky Center emphasizes that Jabil has progressed from being a board manufacturer to a full-service supply chain management firm. (From SemiMD) http://bit.ly/1JhYErC

#### SEMICON® JULY 14–16 West2015 MOSCONE CENTER SAN FRANCISCO

# **Register Now**

SEMICON West is brought to you by

65 HOURS of Technical Programs

### The Marketplace for Microelectronics Innovation

**SEMICON® West** is the premier destination for the people, products, and companies driving the future of microelectronics design and manufacturing and is the global marketplace for microelectronics innovation.

#### **Program Topics**

#### General

- Industry forecasts and business outlook

- Update on 450 mm

- IoT opportunties and challenges for semiconductor manufacturing

- Industrial IoT and 3D printing for semiconductor manufacturing

- Emerging memory technology: update on MRAM, ReRAM and 3DNAND

- What's next for MEMS?

- Flexible hybrid electronics for wearable applications

- Current challenges and future opportunities for the semiconductor supply chain

- Sustainable manufacturing

#### Wafer Processing/Front-end

- Interconnect technology for high-performance computing

- Materials and contamination control in the sub-20 nm era

- Role of subsystems and components at future technology nodes

- Lithography cost and productivity issues below 14 nm

- Transistor scaling solutions for high-volume manufacturing

- The role of secondary equipment in IoT

- CMP technical and market trends

#### Assembly and Test/Back-end

- The future of semiconductor packaging technology

- Packaging of digital health devices

- Packaging of devices for automotive applications

- Automating semiconductor test productivity

- Test Vision 2020—The Road to the Future of Test

www.semiconwest.org

semi

Use #SEMICONWest and join the conversation on Twitter and Facebook!

Please send news articles to sdavis@extensionmedia.com

#### worldnews

**EUROPE – imec** and **JSR Corporation** signed a letter of intent to partner in enabling manufacturing and quality control of EUV lithography materials.

USA – Micron Technology announced that the company has appointed Ernie Maddock as Chief Financial Officer and Vice President, Finance, effective June 1, 2015.

ASIA – A\*STAR's Institute of Microelectronics has formed a High-Density Fan-Out Wafer Level Packaging (FOWLP) consortium.

**USA – Microchip** signed a definitive agreement to acquire **Micrel** for \$14.00 per share.

**USA – SEMATECH** and **Exogenesis Corp.** announced an agreement to commercialize Exogenesis' Accelerated Neutral Atom Beam (ANAB) technology and their nAcceltm accelerated particle beam equipment platform.

ASIA – GaN Systems Inc. announced it has signed an agreement with Japanese semiconductor and electronic component distributor, Value Integrated Technology.

**EUROPE – Cambridge Nanotherm** appointed Howard Ford as chairman.

**USA – Applied Materials** announced the Applied Centura Tetra Z Photomask Etch system for etching next-generation optical lithographic photomasks.

ASIA – MagnaChip Semiconductor Corporation announced that Tae Young Hwang has resigned as the company's president and CEO, and Young-Joon Kim, the company's Interim CEO and general manager, will assume Mr. Hwang's duties.

# news

# Applied Materials and Tokyo Electron terminate merger

Applied Materials, Inc. and Tokyo Electron Limited today announced that they have agreed to terminate their Business Combination Agreement (BCA). No termination fees will be payable by either party.

The decision came after the U.S. Department of Justice (DoJ) advised the parties that the coordinated remedy proposal submitted to all regulators would not be sufficient to replace the competition lost from the merger. Based on the DoJ's position, Applied Materials and Tokyo Electron have determined that there is no realistic prospect for the completion of the merger.

"We viewed the merger as an opportunity to accelerate our strategy and worked hard to make it happen," said Gary Dickerson, president and chief executive officer of Applied Materials. "While we are disappointed that we are not able to pursue this path, our existing growth strategy is compelling. We have been relentlessly driving this strategy forward and we have made significant progress towards our goals. We are delivering results and gaining share in the semiconductor and display equipment markets, while making meaningful advances in areas that represent the biggest and best growth opportunities for us.

"I would like to thank our employees for their focus on delivering results throughout this process. As we move forward, Applied Materials has tremendous opportunities to leverage our differentiated capabilities and technology in precision materials engineering and drive a significant increase in the value we create for our customers and investors."  $\diamond$

### Top 10 2015 semiconductor sales leaders forecast to include NXP/Freescale

IC Insights released its April Update to the 2015 McClean Report, and the update includes the final 2014 company sales rankings for the top 50 semiconductor and top 50 IC companies, and the leading IC foundries. Also included are 2014 IC company sales rankings for various IC product segments (e.g., DRAM, MPU, etc.).

In 2014, there were only two Japanese companies—Toshiba and Renesas—that were among the top 10 semiconductor suppliers (Figure 1). Assuming the NXP/Freescale merger is completed later this year, IC Insights forecasts that Toshiba will be the lone Japanese company left in the top 10 ranking. Anyone who has been involved in the semiconductor industry for a reasonable amount of time realizes this is a major shift and a big departure for a country that once was feared and revered when it came to its semiconductor

# Novel cellular sensing platform for biotech applications

Researchers from the Georgia Institute of Technology have developed a novel cellular sensing platform that promises to expand the use of semiconductor technology in the development of next-generation bioscience and biotech applications.

The research is part of the Semiconductor Synthetic Biology (SSB) program sponsored and managed by Semiconductor Research Corporation (SRC). Launched in 2013, the SSB program concentrates on synergies between synthetic biology and semiconductor technology that can foster exploratory, multidisciplinary, longer-term university research leading to novel, breakthrough solutions for a wide range of industries.

The Georgia Tech research proposes and demonstrates the world's first multi-modality cellular sensor arranged in a standard low-cost CMOS process. Each sensor pixel can concurrently monitor multiple different physiological parameters of the same cell and tissue samples to achieve holistic and real-time physiological characterizations.

"Our research is intended to fundamentally revolutionize how biologists and bioengineers can interface with living cells and tissues and obtain useful information," said Hua Wang, an assistant professor in the School of Electrical and Computer Engineering (ECE) at Georgia Tech. "Fully understanding the physiological behaviors of living cells or tissues is a prerequisite to further advance the frontiers of bioscience and biotechnology."

Wang explains that the Georgia Tech research can have positive impact on semiconductors being used in the development of healthcare applications including the more cost-effective development of pharmaceuticals and point-of-care devices and low-cost home-based diagnostics and drug testing systems. The research could also benefit defense and environmental monitoring applications for low-cost fielddeployable sensors for hazard detections.

## THE POWER of TWO.

## two lasers | one station the IX-280-ML

higher efficiency

greater flexibility

lower cost of ownership

+1 (603) 518-3200 www.ipgphotonics.com sales.ipgm@ipgphotonics.com

PHOTONICS

Continued on page 8

## **NEWS**cont

Continued from page 6

sales presence in the global market.

Figure 1 traces the top 10 semiconductor companies dating back to 1990, when Japanese semiconductor manufacturers wielded their greatest influence on the global stage and held six of the top 10 positions. The six Japanese companies that were counted among the top 10 semiconductor suppliers in 1990 is a number that has not been matched by any country or region since (although the U.S. had five suppliers in the top 10 in 2014). The number of Japanese companies ranked in the top 10 in semiconductor sales slipped to four in 1995, fell to three companies in 2000 and 2006, and then to only two companies in 2014.

#### FIGURE 1.

Figure 1 also shows that, in total, the top 10 semiconductor sales leaders are making a marketshare comeback. After reaching a marketshare low of 45 percent in 2006, the top 10 semiconductor sales leaders held a 53 percent share of the total semiconductor market in 2014. Although the top 10 share in 2014 was eight points higher than in 2006, it was still six points below the 59 percent share they held in 1990. As fewer suppliers are able to achieve the economies of scale needed to successfully invest and compete in the semiconductor industry, it is expected that the top 10 share of the worldwide semiconductor market will continue to slowly increase over the next few years.

#### Continued from page 7

FIGURE 1. A CMOS multimodality cellular sensor array chip being developed at Georgia Tech is hosted on a standard printed circuit board (PCB) and is packaged using lowcost polydimethylsiloxane (PDMS) material to ensure biocompatibility and electrical insulation. A standard 35 mm cell culture dish with drilledout bottom is mounted on the PCB to host the cells and medium, and expose cells to the CMOS sensing surface. (Georgia Tech Photo: Rob Felt) Specifically, in the case of the more cost-effective development of pharmaceuticals, the increasing cost of new medicine is largely due to the high risks involved in the drug development. As a major sector of the healthcare market, the global pharmaceutical industry is expected to reach more than \$1.2 trillion this year. However, on average, only one out of every ten thousand tested chemical compounds eventually become an approved drug product.

In the early phases of drug development (when thousands of chemical candidates are screened), in vitro cultured cells and tissues are widely used to identify and quantify the efficacy and potency of drug candidates by recording their cellular physiology responses to the tested compounds, according to the research.

Moreover, patient-to-patient variations often exist even under the administration of the same type of drugs at the same dosage. If the cell samples are derived from a particular patient, patient-specific drug responses then can be tested, which opens the door to future personalized medicine.

"Therefore, there is a tremendous need for low-cost sensing platforms to perform fast, efficient and massively parallel screening of in vitro cells and tissues, so that the promising chemical candidates can be selected efficiently," said Wang, who also holds the Demetrius T. Paris Junior Professorship in the Georgia Tech School of ECE. "This existing need can be addressed directly by our CMOS multi-modality cellular sensor array research."

Among the benefits enabled by the CMOS sensor array chips are that they provide built-in computation circuits for in-situ signal processing and sensor fusion on multi-modality sensor data. The chips also eliminate the need of external electronic equipment and allow their use in general biology labs without dedicated

# **news**cont

electronic or optical setups.

Additionally, thousands of sensor array chips can operate in parallel to achieve high-throughput scanning of chemicals or drug candidates and real-time monitoring of their efficacy and toxicity. Compared with sequential scanning through limited fluorescent scanners, this parallel scanning approach can achieve more than 1,000 times throughput enhancement.

The Georgia Tech research team just wrapped its first year of research under the 3-year project, with the sensor array being demonstrated at the close of 2014 and presented at the IEEE International Solid-State Circuits Conference (ISSCC) in February 2015. In the next year, the team plans to further increase the sensor array pixel density while helping improve packaging solutions compatible with existing drug testing solutions.

"Georgia Tech's research combines semiconductor integrated circuits and living cells to create an electronics-biology hybrid platform, which has tremendous societal and technological implications that can potentially lead to better and cheaper healthcare solutions," said Victor Zhirnov, director of Cross-Disciplinary Research and Special Projects at SRC. ◆

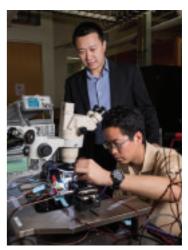

**FIGURE 2.** Georgia Tech Ph.D. student Jong Seok Park (right) is performing electrical testing of the CMOS sensor chip with Assistant Professor Hua Wang (left). (Georgia Tech Photo: Rob Felt)

- Chemical resistant sensor

- Wide range ppb to saturation

http://www.horiba.com

Explore the future Automotive Test Systems | Process & Environmental | Medical | Semiconductor | Scientific

## **news**cont

#### SRC names former Freescale CTO Ken Hansen as new president and CEO

Semiconductor Research Corporation (SRC) announced that Ken Hansen has been appointed SRC's new President and Chief Executive Officer (CEO), effective June 1.

Hansen's professional experience includes serving as Vice President and Chief Technology Officer (CTO) at Freescale Semiconductor since 2009. Hansen replaces retiring SRC President and CEO Larry Sumney who guided the organization for more than 30 years since its inception in 1982. SRC's many accolades over the years include being the recipient of the National Medal of Technology in 2007.

"SRC under Larry Sumney's leadership has made an indelible impact on the advancement of technology during the past three decades, and we congratulate Larry on his retirement and salute him for his contributions to the semiconductor industry," said Mike Mayberry, Intel Corporate Vice President and Director of Components Research who is SRC Board Chairman. "We also welcome Ken Hansen to his new role guiding SRC, and we look forward to Ken's leadership helping SRC reach new heights in an era where basic research and development is as critical as ever."

Prior to his CTO role at Freescale, Hansen led research and development teams for more than 30 years in multiple senior technology and management positions at Freescale and Motorola. Hansen holds Bachelor and Master of Science degrees in Electrical Engineering from the University of Illinois where he has been recognized as an ECE (Department of Electrical and Computer Engineering) Distinguished Alumni.

In his new role at SRC, Hansen intends to build on the consortium's mission of driving focused industry research to both advance state-of-the-art technology and continue to create a pipeline of qualified professionals who will serve as next-generation leaders for the industry.

"SRC also has an opportunity to strengthen its core by recruiting new members to gain more leverage to fund industry wide solutions for some of the challenging technology roadblocks that are ahead of us," said Hansen. "The model that SRC has developed is unmatched in the industry and has proven to be extremely significant. The industry would not be where it is today without the contributions of SRC under the leadership and vision of Larry Sumney," Hansen continued.

Meanwhile, Sumney's decorated career began in 1962 at the Naval Research Laboratory. He later directed various other research programs at Naval Electronics Systems Command and the Office of the Undersecretary of Defense — including the Department of Defense's major technology initiative, Very High Speed ICs (VHSIC) —before agreeing to lead SRC following its formation by the Semiconductor Industry Association.

Under his leadership, SRC has also formed wholly owned subsidiaries managing the Nanoelectronics Research Initiative (NRI), the Semiconductor Technology Advanced Research network (STARnet) and the SRC Education Alliance, among other programs. Sumney received a Bachelor of Physics from Washington and Jefferson (W&J) College, which recognized him with the 2012 Alumni Achievement Award, and a Master of Engineering Administration from George Washington University.

"I have enjoyed a front row seat in the development of today's technology-based economy and advancement of humanity through the semiconductor industry," said Sumney. "I am completely confident that SRC is well positioned and will continue to flourish, to seed breakthrough innovation and help provide the people and ideas to keep the U.S. semiconductor industry competitive and prosperous in years to come."  $\triangleleft$

# IBM's silicon photonics technology ready to speed up cloud and Big Data applications

IBM announced a significant milestone in the development of silicon photonics technology, which enables silicon chips to use pulses of light instead of electrical signals over wires to move data at rapid speeds and longer distances in future computing systems.

For the first time, IBM engineers have designed and tested a fully integrated wavelength multiplexed silicon photonics chip, which will soon enable manufacturing of 100 Gb/s optical transceivers. This will allow datacenters to offer greater data rates and bandwidth for cloud computing and Big Data applications.

"Making silicon photonics technol-

ogy ready for widespread commercial use will help the semiconductor industry keep pace with ever-growing demands in computing power driven by Big Data and cloud services," said Arvind Krishna, senior vice president and director of IBM Research. "Just as fiber optics revolutionized the telecommunications industry by speeding up the flow of data - bringing enormous benefits to consumers - we're excited about the potential of replacing electric signals with pulses of light. This technology is designed to make future computing systems faster and more energy efficient, while enabling customers to capture insights from Big Data in real time."

Silicon photonics uses tiny optical components to send light pulses to transfer large volumes of data at very high speed between computer chips in servers, large datacenters, and supercomputers, overcoming the limitations of congested data traffic and high-cost traditional interconnects. IBM's breakthrough enables the integration of different optical components side-byside with electrical circuits on a single silicon chip using sub-100nm semiconductor technology.

IBM's silicon photonics chips uses four distinct colors of light travelling within an optical fiber, rather than

Continued on page 12

# **A4 SERIES**

#### Energy-efficient dry multi-stage process pumps for all applications in semiconductor industry

- Low energy consumption

- Improved temperature management to optimize the pump according to your process

- Protection of the pump against precursor cracking or condensable deposition

- Corrosion resistant and high particle tolerance

- Extended monitoring functionalities

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com

## **NEWS**cont

#### Continued from page 11

traditional copper wiring, to transmit data in and around a computing system. In just one second, this new transceiver is estimated to be capable of digitally sharing 63 million tweets or six million images, or downloading an entire high-definition digital movie in just two seconds.

The technology industry is entering a new era of computing that requires IT systems and cloud computing services to process and analyze huge volumes of Big Data in real time, both within datacenters and particularly between cloud computing services. This requires that data be rapidly moved between system components without congestion. Silicon photonics greatly reduces data bottlenecks inside of systems and between computing components, improving response times and delivering faster insights from Big Data.

IBM's new CMOS Integrated Nano-Photonics Technology will provide a cost-effective silicon photonics solution by combining the vital optical and electrical components, as well as structures enabling fiber packaging, on a single silicon chip. Manufacturing makes use of standard fabrication processes at a silicon chip foundry, making this technology ready for commercialization.

Silicon photonics technology leverages the unique properties of optical communications, which include transmission of high-speed data over kilometer-scale distances, and the ability to overlay multiple colors of light within a single optical fiber to multiply the data volume carried, all while maintaining low power consumption. These characteristics combine to enable rapid movement of data between computer chips and racks within servers, supercomputers, and large datacenters, in order to alleviate the limitations of congested data traffic produced by contemporary interconnect technologies.

#### Silicon photonics will transform future datacenters

By moving information via pulses of light through optical fibers, optical interconnects are an integral part of contemporary computing systems and next generation datacenters. Computer hardware components, whether a few centimeters or a few kilometers apart, can seamlessly and efficiently communicate with each other at high speeds using such interconnects. This disaggregated and flexible design of datacenters will help reduce the cost of space and energy, while increasing performance and analysis capabilities for users ranging from social media companies to financial services to universities. Most of the optical interconnect solutions employed within datacenters as of today are based upon vertical cavity surface emitting laser (VCSEL) technology, where the optical signals are transported via multimode optical fiber. Demands for increased distance and data rate between ports, due to cloud services for example, are driving the development of cost-effective single-mode optical interconnect technologies, which can overcome the bandwidthdistance limitations inherent to multimode VCSEL links.

IBM's CMOS Integrated Nano-Photonics Technology provides an economical solution to extend the reach and data rates of optical links. The essential parts of an optical transceiver, both electrical and optical, can be combined monolithically on one silicon chip, and are designed to work with with standard silicon chip manufacturing processes.

IBM engineers in New York and Zurich, Switzerland and IBM Systems Unit have demonstrated a reference design targeting datacenter interconnects with a range up to two kilometers. This chip demonstrates transmission and reception of high-speed data using four laser "colors," each operating as an independent 25 Gb/s optical channel. Within a full transceiver design, these four channels can be wavelength multiplexed on-chip to provide 100 Gb/s aggregate bandwidth over a duplex single-mode fiber, thus minimizing the cost of the installed fiber plant within the datacenter.

Further details will be presented by IBM at the 2015 Conference on Lasers and Electro Optics (May 10-15) in San Jose, California, during the invited presentation entitled "Demonstration of Error Free Operation Up To 32 Gb/s From a CMOS Integrated Monolithic Nano-Photonic Transmitter," by Douglas M. Gill, Chi Xiong, Jonathan E. Proesel, Jessie C. Rosenberg, Jason Orcutt, Marwan Khater, John Ellis-Monaghan, Doris Viens, Yurii Vlasov, Wilfried Haensch, and William M. J. Green.

IBM Research has been leading the development of silicon photonics for more than a decade, announcing a series of technology milestones beginning in 2006. Silicon photonics is among the efforts of IBM's \$3 billion investment to push the limits of chip technology to meet the emerging demands of cloud and Big Data systems.

### FOWLP and embedded packaging

At the recent IMAPS conference, Yole's Jerome Alzemer updated the audience on the Fan Out and Embedded die marketplace, based on his new report "Fan out and Embedded Die: Technology and Market Trends."

Embedded packaging refers to many different concepts, IP, manufacturing infrastructures and related technologies. The two main categories of embedded packages are (1) those based on a molded wafer infrastructure such as FOWLP and (2) those based on a PWB/ PCB laminate panel infrastructure.

Fan-out WLP are "re-configured" by placing known good ICs active face down on a foil and by over-molding them. These wafers are then flipped and processed in the wafer fab with RDL/ball placing and diced.

For chip embedding in laminate, known good ICs are picked and placed on top of an organic layer of Printed circuit board and subsequent layers are laminated on top. Regular PCB manufacturing operations then take place on the panel containing the embedded ICs.

#### Fan Out WLP (FOWLP)

Unlike Fan In WLP, which has been commercialized since the late 1990's, FOWLP is not constrained by die size, and thus can offer an unlimited number of interconnects for maximum connection density. One can also achieve finer line/spacing, improved electrical and thermal performance and small package dimensions to meet the relentless form factor requirements and performance demands of the mobile market.

Commercialization of the Infineon e-WLB (embedded wafer level BGA) technology started in 2009 with single die packages for cell phone baseband chips. The Infineon technology was later licensed to OSATS Nanium, STATSChipPAC and ASE, thus creating a multi-sourced infrastructure.

### Packaging

A similar process called Redistributed Chip Packaging (RCP) was developed by Freescale during the same time period. It was subsequently licensed to NEPES but has not yet reached HVM. Other developing FOWLP technologies -- including those of TSMC (called InFO), SPIL and J- Devices -- are approaching commercialization but will initially lack the multisourcing available with eWLB.

**Phil Garrou,** Contributing Editor

The second generation of FOWLP are multichip packages including PoP and SiP configurations. These are generating increased interest in this packaging approach.

As of 2014 Yole estimates that the market is ~ \$174MM. With the expected entry of several major players like TSMC, Yole envisions the market growing at a 30% CAGR to > \$600MM by 2020.

Technical challenges such as warpage, die shift, chipto-mold non planarity and topography remain significant limitations.  $\clubsuit$

For more information, visit www.yieldengineering.com or call 925-373-8353

www.solid-state.com

## Safe CMP slurries

New chemical-mechanical planarization (CMP) processes for new materials planned to be used in building future IC devices are now in research and development (R&D). Early data on process trade-offs as well as on environmental, health, and safety (EHS) aspects were presented at the CMP Users Group (of the Northern California Chapter of The American Vacuum Society) meeting, held in Albany, New York on April 16 of this year in collaboration with the College of Nanoscale Science and Engineering (CNSE) SUNY Polytechnic Institute and SEMATECH.

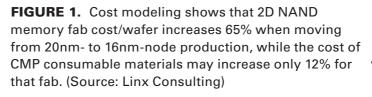

Mike Corbett, principle with Linx Consulting, presented his company's forecast on CMP consumable materials growth for both logic and memory. "We're no longer in the era of 2D scaling. Right now the semiconductor industry is scaling through the use of novel materials and 3D structures. It started with memory cells going vertical for storage

structures. All of these technologies rely on CMP as a key enabler: for 3D NAND there'll be new tungsten, TSV need new copper, and transistors need CMP for high-k/metal-gate processing."

Corbett estimates the current global market for pre-interconnect CMP consumablesslurries, pads, and conditioning disks—at >\$US1.5B annually with steady growth on the horizon. While the fabricated cost/wafer at the leading edge is estimated to increase by 25-60% when moving to the next leadingAlternate channel materials toxicity in CMP

With alternate channel materials on the horizon for future logic transistor, III-V materials such as galliumarsenide (GaAs), gallium-indiumphosphide (GaInP), and indiumphosphide (InP) are now in R&D which leads to questions regarding direct process costs as

Ed Korczynski, Sr. Technical Editor

well as indirect EHS costs. Hsi-An Kwong, SEMATECH EHS Program Manager, provided an important overview of these issues in his presentation on "Out-gassing from III-V Wafer Processing." Much of the concern involves the possible reaction and release of toxic hydrides such as arsine, and phosphine. SEMATECH worked with imec to monitor hydrides produced during CMP processes for

\$1.000

edge node, the cost of CMP consumables should only increase by 12-14%. FIGURE 1 shows the specific example of 2D NAND wafer cost increasing by 60% in moving from 20nm- to 16nm-node production, while the fab's CMP costs increase just ~12%. Until the IC HVM industry begins using

#### Semiconductors

14

materials other than Si/ SiGe for transistor channels it seems that CMP costs will be well controlled.

larly when moving to HVM we need to study the layers on the wafer and the slurry used to evaluate if outgassing will be an issue," explained Kwong. "FTIR is the metrology instrument needed to be able to distinguish between different evolved hydride species." HVM fab personnel working on or near CMP tools would have to wear personal breathing apparatus if processes evolve hydrides; for example, the SEMATECH/CNSE continuous exposure EHS specification allows a maximum human exposure level of just 1.25 ppb arsine. 🔶

high-mobility compound semiconductors.

With 1.5% H<sub>2</sub>O<sub>2</sub> in a relatively low-pH slurry, phosphine was measured on the tool from InP but not from GaInP. Use of higher pH with the same 1.5% H<sub>2</sub>O<sub>2</sub> resulted in no phosphine from InP, but arsine outgassing from GaAs. Use of the highest pH resulted in no outgassing of phosphine or arsine. "When we develop the CMP process, particu-

# Reduced Defectivity and Cost of Ownership Copper CMP Cleans

CHRISTOPHER ERIC BRANNON, Texas Instruments, Dallas, TX

A new, low pH, BTA free, noble-bond chemistry produced equivalent yield at substantially lower costs.

he 2010 economic downturn affected many industries, semiconductor manufacturing notwithstanding. Many fabrication facilities had to layoff employees and curtail spending, all the while managing lower wafer output. This effect caused many semiconductor companies to rethink how they spend on resources. Everything was considered, from the cost of the wafers to the cost of the tool consumables and chemistries.

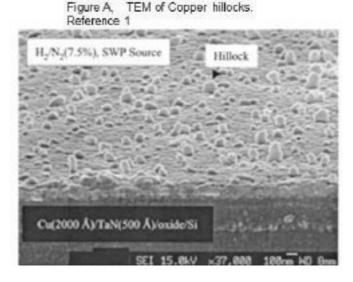

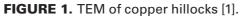

Texas Instruments (TI) copper chemical-mechanical planarization (Cu CMP) was no different. All spending had to be reduced and copper hillock defect had to be eliminated. The CMP Team proposed developing a process based on the new third generation clean chemistry on the market for a number of economic and logistical reasons. The first rationale for this strategy was cost and second was time - most of the clean chemistries on the market were considerably cheaper than the current process of record (POR). CMP had also seen many defects due to via-to-via shorts caused by Cu hillocking (localized Cu protrusion into the above interlayer dielectric; see **FIGURE 1**).

#### A successful Cu cleaning CMP process

There were two key reasons that TI succeeded in developing a Cu cleaning process: detailed engineering work and strong vendor support. Process development went through four generations of refinement before it was ready for high volume manufacturing. The first version focused on new clean chemistry improvements such as third generation low pH, high acid clean chemistry and

FIGURE 1. TEM of copper hillocks [1].

an array of design of experiments (DOE) continuous improvement through optimization of the process controls and equipment modification followed in the second. The third generation attempted to adapt an existing Mirra-Desica process using a previous qualified process. A final successful attempt was made during the fourth cycle to develop a lower cost, higher throughput multi-copper platen cleaning process using a commercial chemistry from Air Products, COPPEREADY®CP72B. This paper will discuss the work that went into building TI's successful Cu cleaning CMP process.

#### **TI Cu CMP**

Neutral pH clean chemistries using Benzotriazole (BTA) were the first generation application on most

Cu CMP dual damascene back end of the line process at TI. This was dependent on using dry-in wet-out Cu CMP AMAT tools with spray acid Vertec hoods for cleaning and drying. It was also very high in cost and low in consumable life compared to most conventional CMP clean process (e.g. Tungsten, STI, Oxide). The TI POR was no different, a first generation Cu clean using three different chemistries, BTA, Electra Clean<sup>™</sup> and ESC774<sup>™</sup>. These chemistries were very expensive to use and were not very efficient at cleaning or passivating the polished copper surface. They were able to passivate the copper surface but were prone to leave many types of incompatible carbon residue defects on the wafers. Cu hillocking was very prevalent with this type of cleaning solution and via-to-via shorts in the back end of the line (BEOL) were the top defect pareto for TI.

#### **Clean chemistry identification**

To reduce the time to develop a new Cu CMP clean process, most of the development cycle focused on Cu cleans leveraging a Mirra-Desica<sup>™</sup> DIDO Cu polishing process using existing pads, conditioning pucks, and

heads. Early on, it was decided that to achieve maximum throughput, the wafers would need to be processed through the tool's onboard scrubber and dry station as quickly as possible. With time running out, the Cu CMP team had contacted the major players in Cu clean chemistry to obtain their specific information and prepare a white paper screening to determine

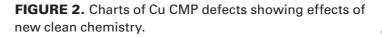

(FIGURE 2).

to do lifetime experiments with consumables at their facilities. The data that was collected revealed many issues with each candidate, one more so than the other Chemistry A was a second generation Cu clean that had high pH but had chemical additives that would aid in cleaning, still a very basic approach to wafer cleaning. The overall defectivity was sufficient on the product test wafers but would degrade after a short time window after polish. It also had

were blanket test wafer performance (Cu, Teos, Ta, and

Nitride): etch rate, passivation, cleaning tunability via

recipe parameter windowing, and defectivity. Experi-

mental designs were run on the basic process controls

with these chemistry's with respect to the polish process:

carrier speed, table speed, down-force, carrier position,

performed well on the blanket experiments and were

advanced to short loop, patterned wafer tests. These patterned wafer tests were used to study product

behavior in the polisher and brush cleaner. A significant

amount of time was spent adjusting recipe parameters

to eliminate defects. The team contacted both vendors

carrier oscillation, and chemical flow. Both cleans

to be paired with another chemistry to achieve the same Cu passivation as the POR. This chemistry was disgualified due to this reason.

Chemistry B is a third generation Cu clean that had low pH (about ~2.1) and it is BTA-free, unlike any other Cu cleans on the market at that time. This chemistry is an organic acid blend, which helps ionize

the correct path. The four candidates were evaluated on chemistry type, makeup, pH, passivation (BTA), cost, and compatibility to our current Cu and barrier slurry. Two of the chemistries fit the bill for the criteria and were selected for further testing. Chemistry 1 was a novel approach for Cu CMP and was from our current clean chemistry vendor, Chemistry 2 was similar to the current TI process of record.

The initial criteria used to judge the chemistries

Cu2O and CuO to form water and soluble Cu complex, used for passivation. This forms a strong bond with the Cu to make the surface nobel. The low pH helps to dissolve the surface defects resulting in a step function decrease in defectivity compared to baseline (see Figure B). The chemistry was also scalable, depending on concentration making cost of ownership low. This chemistry was selected for qualification at TI Cu CMP.

#### Vendor support

TI's internal polishing engineering staff was augmented with exceptional support from several consumable vendors during development. Together TI engineers developed proprietary and patent-pending technologies to enhance the Mirra Desica cleaner performance on Cu BEOL CMP. TI also benefited from strong relationships with its contact clean brush suppliers. Rippy<sup>™</sup> was instrumental in brush evaluations and consultation on process developments. To improve the tool's performance, DOW<sup>™</sup> was pivotal in adding additional functionality to the process through end of life evaluations. Perhaps most important of all relationships that developed was with Air Products, who provided an invaluable education into Cu cleaning process development.

#### Solving defect issues

During process development, TI engineers encountered several defect related issues. Some issues like photoinduced corrosion were resolved quickly after some technical research. There were two others that took more troubleshooting: carbon residue defects and Cu hillock formation.

The presence of gross surface defects, like carbon residue is an obvious yield killer. The Cu CMP Engineers come to the conclusion through EDX (Energy-dispersive X-ray spectroscopy) and much lab analysis that the current Cu slurry still had traces of BTA in it and were causing this residue defect to form on the wafers after polish. Many DOE later determined that extending the clean chemistry buff polish would eliminate this defect.

With residue defects effectively eliminated, the next major technical challenge was Cu hillock formation. TI had been experiencing higher defectivity due to back end of the line via to via shorts on the previous Cu CMP clean chemistry process. It was understood that the formation of Cu hillocks were the cause for this signature. To solve this problem, a completely different wafer cleaning chemistry was needed to passivate the copper surface. TI Cu CMP Engineers looked for one that did not use BTA or other

Figure C. Menal 3 Via Rule Contact Pitting Chart (data takkend by copper billion

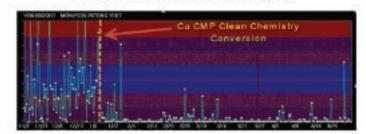

**FIGURE 3.** Metal 1 via etch contact pitting chart (dark vias induced by copper hillock).

high pH chemistries, but, would coat the wafer surface and not allow native oxides to grow on the Cu. The new chemistry (CoppeReady®CP72B) proved to form a nobel bond with the Cu (CuO2) and eliminated hillock growth formation, thereby reducing via-to-via shorts (see **FIGURE 3**).

#### **Further process development**

One of the last stages of development on the new process was a project to develop a faster throughput process. Although this work was successful, it highlights some of the challenges in pursuing this type of strategy. The motivation for this work was to dramatically boost the throughput and to further cut process expense. The POR process was limited by the cleaner and was much slower causing higher cost and higher wafer-per-hour rates. To maximize throughput, the new process would have two components: speed up the on board cleaner, brush box 1&2 throughput, as well decrease the platen 2&3 process times but include a clean chemistry buff. Because of the high down forces employed to achieve a flat removal profile, the Cu polishing component of this work, platen 1, was surprisingly fast but was the intended bottle neck. These changes allowed for a 10 percent increase in overall wafer through put compared to the baseline process. This had an alternate effect on the Cu polish process. TI's current Cu slurry is thermally driven, with making platen 1 the bottle neck it kept that platen at one constant temperature throughout the lot, causing the overall end point times (EPD) to be reduced and streamlined. This further increased the tools throughput by 2 percent and reduced wafer to wafer EPD variation down to 2 to 3 seconds; previous was 10 to 12 sec between wafers (see FIGURE 4).

Figure D, Ca CMP Tool Point charts, variation reduction, close chemistry and therpart reducement

**FIGURE 4.** Cu CMP end point charts, variation reduction, clean chemistry and throughput enhancements.

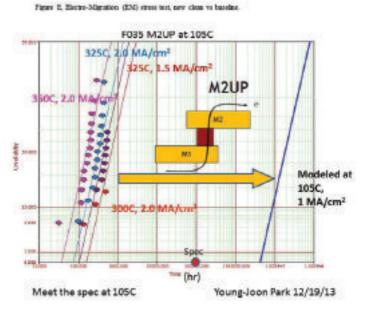

**FIGURE 5.** Electromigration (EM) stress test, new clean vs baseline.

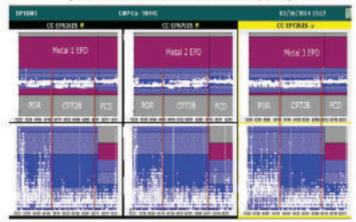

#### **Benchmarking performance**

For initial qualification and benchmarking, TI installed and setup the best known method (BKM) Cu polishing process on an Applied Materials Mirra-Desica<sup>™</sup>. To bring the new clean process into production, Cu Polish engineers needed to demonstrate equivalent or better yield between the two competing process. The new clean chemistry needed to be tested for EM (electro migration), which is a stress test of Cu interconnects between two metal lines. This test had to be outsourced to a third party company that specializes in oven-baking stress tests (**FIGURE 5**). After extensive electrical and yield testing, the new clean process was fully released. Sample yield comparisons consistently demonstrated that the

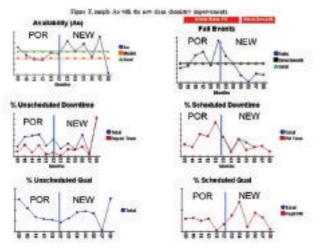

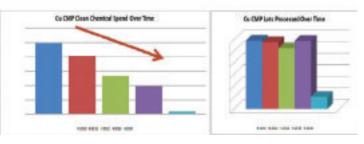

performance is equivalent to slightly better and the new process has higher through-put (~12 percent). The chemical costs (dilute 60 to 1 CP72B®) are 68 percent less per wafer pass than the competing process. The pad/ conditioner life had increased by 13 percent from the previous process due to thermal driven Cu slurry through put modification (**FIGURES 6 AND 7**).

#### Conclusion

TI engineers developed a Cu CMP cleaning process using new third generation low pH Cu chemistry. Despite the tool's many limitations, the engineering staff successfully delivered an integrated process capable of producing equivalent yield at substantially lower costs over the best alternative method. There were undoubtedly challenges along the way, only a fraction of which have been described in this paper. By leveraging an existing deep reservoir of engineering, maintenance, and operational talent, an existing and efficient supply chain, and the outstanding support of numerous vendors, TI Polish module was able to realize its goal of making efficient use of its assets to achieve a competitive advantage.

#### References

Tsung-Kuei Kanga, and Wei-Yang Choub Author. Avoiding Cu Hillocks during the Plasma Process' Journal of The Electrochemical Society, 151 ◆

Figure F, Clean Chemistry cost-over time in Co CMP, with respect to lots processed.

**FIGURE 7.** Clean chemistry cost over time in Cu CMP in terms of lots processed.

## Advancing technology today that will change everything tomorrow.

#### Right now, Air Products is busy advancing the future.

We're working with the world's biggest technology companies to develop the next generation of semiconductors, tablets, screens, computers and smart devices. Our CMP Slurries, cleaning products and deposition materials are helping to push the boundaries, expand the possibilities and change the game for our customers–all to create the technology that will revolutionize tomorrow.

What can we help you advance?

tell me more airproducts.com/advancing

**MEASUREMENT**

# A novel characterization technique unveils the 3D structure of conductive filaments in resistive switching memories

#### UMBERTO CELANO, imec, Leuven, Belgium

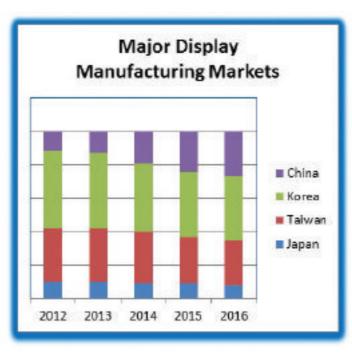

Imec researchers have developed a novel technique – termed conductive atomic force microscopy tomography (or scalpel C-AFM) – that enables a three-dimensional characterization of emerging logic and memory devices.

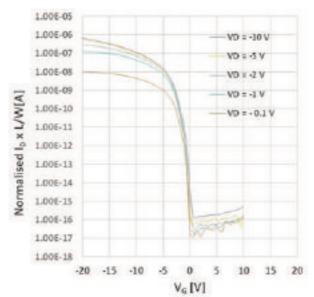

ith the introduction of three-dimensional devices (such as FinFETs) and stackable architectures (such as vertical NAND Flash memories), there is a growing need for 3D characterization techniques. These techniques should not only be capable of probing in three dimensions and examining the topological properties. They should also enable an analysis of the electrical properties of the 3D nano-sized volumes.

A shining example illustrating the need for this technique are conductive bridging random access memory (or CBRAM) devices. These devices belong to the emerging class of resistive RAM (or RRAM) memories which exhibit a fast operation, low power consumption, high endurance and high scalability. They are currently seen as a candidate memory technology for application in storage class memories and embedded non-volatile memories. Their operation basically relies on the formation of a highly conductive path, the conductive filament, in a poorly conductive medium. But the formation of this filament in an integrated device has so far never been observed with the techniques available today. A full 3D characterization of the conductive

Umberto Celano, using the novel scalpel C-AFM tool.

filament would considerably enhance our understanding of the filament growth dynamics and the underlying physical mechanisms. And it would enable a further optimization of the memory device.

### Scalpel C-AFM, extending the 2D capabilities of C-AFM

A well-known characterization technique for advanced logic and memory devices is scanning probe microscopy

UMBERTO CELANO is PhD student in the Material and Component Analysis (MCA) group at imec, Leuven, Belgium.

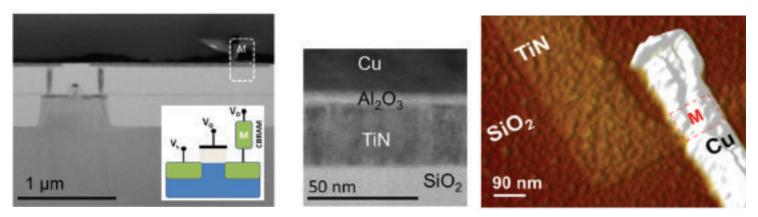

**FIGURE 1.** CBRAM device: Cross-section transmission electron microscopy (TEM) image of the CBRAM memory device (left) and the device stack (middle), and AFM image of the cross-point area (right).

(or SPM), where a sharp tip slides on a flat surface. The 2D-maps of electrical properties provided by this technique have for many years enabled the understanding and development of advanced planar technologies at the nanoscale. SPM comes in several flavors, such as scanning tunnel microscopy (STM), atomic force microscopy (AFM), and a whole range of secondary analysis modes such as conductive AFM (or C-AFM). C-AFM is based on contact-mode AFM using a (biased) conductive tip. The topography is measured in contactmode, while the current flowing between the biased sample and the tip is recorded simultaneously.

Researchers at imec have now evolved the C-AFM technique into a 3D characterization tool, suited to probe very confined volumes at the nanoscale. The new method consists in collecting the C-AFM images of the sample at different depths. The sectioning is induced by a controlled material removal. This is done by applying a strong pressure (GPa) between the (biased) conductivediamond tip and the sample during the C-AFM scan. This way, sub-nm vertical removal rates are obtained. Since the diamond tip acts as a scalpel, the new method is referred to as scalpel C-AFM. The technique can be used for a wide variety of materials, and can be extended to other contact-mode AFM methods such as scanning spreading resistance microscopy.

#### **Case: CBRAM memory devices**

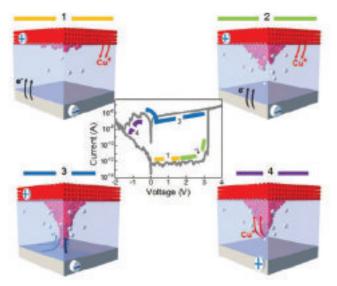

The imec researchers have used the scalpel C-AFM technique for studying the conductive filament formation in CBRAM memory devices. In these devices, an abrupt change in electrical resistance occurs when the device is subjected to a voltage pulse. The different resistance states are induced by the formation or dissolution of a highly conductive filament into a poorly conductive medium.

The heart of the CBRAM memory cell is a thin dielectric (e.g.,  $Al_2O_3$ ) that is sandwiched between the active electrode (Cu or Ag) and an inert counter electrode (e.g., TiN). When a positive voltage is applied to the active electrode, a field-assisted injection and transport of cations begins. This leads to the creation of the conductive filament inside the Al<sub>2</sub>O<sub>3</sub> oxide layer. The presence of this filament dramatically lowers the resistance of the device, leaving it in a low resistive state (LRS). The conductive filament can be dissolved by applying a negative voltage to the active electrode and thus restoring a high resistance state (HRS). The two different resistance states are used as the logic values 1 or 0 for data storage applications. The overall performance of the device is highly related to the properties of the conductive filament, which has so far not been observed in 3D on scaled devices.

#### **Observation of the conductive filament**

The memory device under investigation is a Cu/5nm Al2O3/TiN-based memory, integrated in a one-transistor-one-resistor configuration. The device is placed at the cross-point between the bottom and top electrode. The scalpel C-AFM technique was applied to memory devices programmed in both the low and high resistive state. An in-house fabricated conductivediamond tip was used for probing and removing the material.

By using the scalpel C-AFM technique, the researchers were able to observe, for the first time ever, the conductive filament formation which is responsible for the resistive switching behavior in CBRAM devices

**FIGURE 2.** filament growth model: Illustration of the eletrochemical processes during resistive switching. (1) First, the Cu oxidizes and Cu+ ions are injected in the  $Al_2O_3$ . Second, the high electric field might lead to the formation of oxygen vacancies in the dielectric layers (white balls in the cartoon). (2) The slow migration of Cu+ ions in the switching layer implies that a reduction reaction occurs before the Cu+ reaches the inert-electrode. (3) The conductive filament (CF) growth continues and the CF eventually shorts the two electrodes thereby creating the low resistive state. (4) When the bias is reversed, a Joule-heating assisted electrochemical reaction is responsible for the rupture of the CF in the point of max power dissipation, that is, CF constriction.

(**FIGURE 1**). The observed conductive filament, embedded in the  $Al_2O_3$  oxide, shows a conical shape: it shrinks moving from the active electrode (Cu) towards the inert electrode (TiN). The low resistive state is created when the conductive filament eventually shorts the two electrodes.

The experiments suggest that the dynamics of the conduction filament growth are limited by the mobility of the Cu cations in the electrolyte (**FIGURE 2**). When the bias is reversed, a Joule-heating assisted electro-chemical reaction is responsible for the rupture of the conductive filament (the high resistive state).

The study also demonstrates the close correlation between the programming current, the physical volume of the conductive filament and the resistance. A larger programming current induces a larger physical volume and a lower resistance value of the conductive filament. Hence, by controlling the programming current, the resistance can be modulated. This opens the possibility of creating multiple resistance sates in one single memory cell, which can considerably enhance the memory density of non-volatile CBRAM devices.

Scalpel C-AFM will rapidly find applications in other emerging technologies as well. At imec, the technique is currently being used for investigating vertical NAND Flash memory devices and oxide-based RRAM memory devices.

#### Suggested additional reading

'Three-dimensional observation of the conductive filament in nanoscaled resistive memory devices', U. Celano et al., Nano Letters, 2014. http://pubs.acs.org/ doi/abs/10.1021/nl500049g.

'The memory roadmap, a paradigm shift from 2D to 3D', interview with imec's Jan Van Houdt in imec magazine, March issue. http://magazine.imec.be/ data/57/reader/reader.html#preferred/1/package/57/ pub/63/page/4. ◆

# The impact of consumer demand for cutting-edge display technology on the gases market

EDDIE LEE, Linde Electronics, Hsin Chu, Taiwan

How gases are used in the manufacture of displays is being impacted by new technologies, consumer demand, and the burgeoning China market.

hile the display market is no longer enjoying double-digit annual growth rates, it is experiencing resurgence due to increasing customer demands for larger flat-panel displays, OLED and 4K technology, ultra-slim form factor, curved and wearable displays, automotive displays, and more. This growth is particularly conspicuous in China, a late comer to the market, which is now the fastest growing region in display manufacturing.

These new technologies and markets require very large quantities of ultra-high purity bulk and electronic specialty gases and a dependable supply chain for these gases. This article will explore the impact of these technol-

ogies, consumer demand, and the burgeoning China market on the gases used in the manufacture of display.

#### **Display market**

According to IHS DisplaySearch, in 2014 the global display market saw revenue of \$134 billion and is expected to grow 6% in 2015. The demand is being driven in large part due to new technologies and new uses for existing display technologies such as 4K, OLED, curved, and flexible displays.

#### Gases used in display

This love affair that consumers have of interacting with devices large and small not only increases the volume of displays to be manufactured, it also increases the volume of gases needed to make the displays. In the 20 years since the initial development and commercialization of the first Thin Film Transistor (TFT) LCD display panel, the gases market for the display sector has grown to around \$450 million.

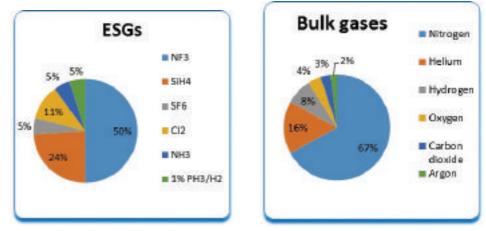

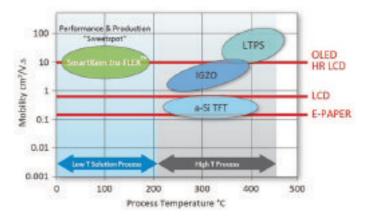

As shown in **FIGURE 1**, display manufacturing today uses a wide variety of gases, which can be categorized into two types: Electronic specialty gases (ESGs) and Electronic bulk gases (EBGs).

EDDIE LEE is Head of Global Market Development and OEMs Display, Linde Electronics, Hsin Chu, Taiwan

#### TABLE 1.

|        | <ul> <li>= nominal amount</li> <li>= less than<br/>nominal</li> <li>X = not typically used</li> </ul> | a-Si | LTPS  | мо    |

|--------|-------------------------------------------------------------------------------------------------------|------|-------|-------|

| Thin   | SiH <sub>4</sub> (Silane)                                                                             | 0    | ٥     |       |

| Film   | NH3 (Ammonia)                                                                                         | 0    |       |       |

|        | N <sub>2</sub> O (Nitrous oxide)                                                                      | х    | 0     | 0     |

|        | TEOS (Tetraethyl                                                                                      | 0    | 0     |       |

|        | orthosilicate)                                                                                        | ×    | ×.,   | - 682 |

| Doping | 1% B2H6/H2                                                                                            | x    | •     | ×     |

|        | (Diborane/Hydrogen)                                                                                   | ~    |       |       |

|        | 15% B <sub>2</sub> H <sub>6</sub> /H <sub>2</sub>                                                     | x    | 0     | x     |

|        | (Diborane/Hydrogen)                                                                                   | 1156 | 10315 | 13572 |

|        | 1% PH <sub>3</sub> /H <sub>2</sub>                                                                    | 0    | 0     | ×     |

|        | (Phosphine/Hydrogen)                                                                                  |      |       | 11.52 |

|        | 20% PH <sub>3</sub> /H <sub>2</sub>                                                                   | 0    | •     | ×     |

|        | (Phosphine/Hydrogen)<br>1% PH <sub>3</sub> /SiH <sub>4</sub>                                          |      |       |       |

|        | (Phosphine/Silane)                                                                                    | 0    | 0     | ×     |

| Clean  | NF <sub>3</sub> (Nitrogen trifluoride)                                                                | 0    | 0     | 0     |

| cicuit | F <sub>2</sub> (Fluorine)                                                                             | 0    | 0     | 0     |

| Etch   | CF4 (Carbon<br>tetrafluoride)                                                                         | 0    | 0     | 0     |

|        | C2HFs (Ethyl chloride)                                                                                | x    | 0     | ×     |

|        | SF6 (Sulfur hexafluoride)                                                                             | 0    | 0     | 0     |

|        | Cl <sub>2</sub> (Chlorine)                                                                            | 0    |       |       |

|        | C <sub>6</sub> F <sub>8</sub><br>(Octafluorocyclobutane)                                              | x    | 0     | x     |

|        | BCl <sub>3</sub> (Boron tricholoride)                                                                 | 0    |       |       |

| Laser  | 4.5% HCl/1% H <sub>2</sub> /Ne<br>(Hydrogen<br>chloride/Hydrogen/Neon)                                | x    | 0     | ×     |

|        | Xe (Xenon)                                                                                            | x    | 0     | ×     |

|        | Ne (Neon)                                                                                             | х    | •     | ×     |

|        | 5% F <sub>2</sub> /He<br>(Fluorine/Helium)                                                            | x    | •     | ×     |

|        | Kr (Krypton)                                                                                          | х    | 0     | ×     |

| Bulk   | H <sub>2</sub> (Hydrogen)                                                                             | 0    | 0     | 0     |

|        | O <sub>2</sub> (Oxygen)                                                                               | 0    | 0     | 0     |

|        | N <sub>2</sub> (Nitrogen)                                                                             | 0    | 0     | 0     |

|        | He (Helium)                                                                                           | 0    | 0     | 0     |

|        | Ar (Argon)                                                                                            | 0    | 0     | 0     |

|        | Co <sub>2</sub> (Carbon dioxide)                                                                      | 0    | 0     | 0     |

#### Electronic specialty gases (ESGs)

Silane, nitrogen trifluoride, fluorine (on-site generation), sulfur hexafluoride, ammonia, and phosphine mixtures make up 52% of the gases used in the manufacture of displays and are available in both cylinder and bulk supply.

Of the major countries that manufacture displays, Taiwan and China import most of their ESGs while Korea and Japan have robust domestic production of ESGs.

Silane:  $SiH_4$  is one of the most critical molecules in flat panel manufacturing. Silane is used for deposition of amorphous Si (silicon), the most critical layer in the TFT transistor.

**Nitrogen trifluoride:**  $NF_3$  is the single largest Electronic Material from spend and volume standpoint for flat panel display (FPD) production.  $NF_3$ is used for cleaning the PECVD (plasma-enhanced chemical vapor deposition). This gas requires scalability to get the cost advantage necessary for the highly competitive market. Over 70% of the global capacity of  $NF_3$  comes from Korea and Japan.

#### **Electronic bulk gases (EBGs)**

Nitrogen, hydrogen, helium, oxygen, carbon dioxide, and argon make up 48% of the gases used in the manufacture of displays.

*Nitrogen:* For a typical large TFT-LCD fab, nitrogen demand can be as high as 30,000 Nm<sup>3</sup>/ hour so an on-site generator, such as the Linde SPECTRA®-N 30,000, is a cost-effective solution that has the added benefit of an 8% reduction in CO<sub>2</sub> footprint over conventional nitrogen plants.

*Helium* is used for cooling the glass during and after processing. Manufacturers are looking at ways to decrease the usage of helium because of cost and availability issues due it being a non-renewable gas.

#### New technologies and implications for gases

Currently about 20% of smartphones – the ones with lower resolution displays – use a-Si display process. Higher resolution devices and new effects such as curved displays require higher performance transistors and improvements in electron mobility. This can be achieved by switching from amorphous silicon (a-Si) transistors to low temperature

silicon deposition to change the silicon structure to polysilicon. High-performance laser gases, such as Ne, Xe, and Kr from Linde, are well-suited for this process.

*Transparent Conductive Films (TCF) and ITO Replacements*: TCFs are used in most high-tech displays and touchscreens, and particularly in displays that are bent or curved. Currently the electronics industry relies primarily on Indium Tin Oxide (ITO) to make

electro-conductive films for display. ITO presents

challenges: it is brittle and cracks so new TCFs are

mesh, Ag nanowire (agNW), and carbon nanotube

(CNT), which are all highly flexible with comparable

good for large displays, but is restricted on small and

transparency and resistance to ITO. Metal mesh is

medium displays due to its wire width (typically 6

New materials to potentially replace ITO are metal

needed for structural flexibility.

#### TABLE 2.

| Transistor<br>type | Electron mobility<br>(m²/Vs) | Cost | Manufacturing<br>challenges |

|--------------------|------------------------------|------|-----------------------------|

| a-Si               | <1                           | low  | low                         |

| MO                 | 1-50 (typically<br>5-10)     | low  | high                        |

| LTPS               | 50-300                       | high | medium                      |

polysilicon (LTPS) or metal oxide (MO), also known as transparent amorphous oxide semiconductor (TAOS).

LTPS is used in about 44% of high-end LCD smartphone displays as it has the highest performance. Due to its higher costs and scalability limitations, LTPS is less suited for large screen displays.

Small displays with very high pixel resolution are produced with LTPS. High-definition large displays can be made using MO. Metal oxide semiconductors

can remain in an active state longer than traditional LCD and can cut power consumption by up to 90%, which is a huge benefit.

#### New process requirements

*Metal Oxide TFT and LTPS:* To meet the changes in technology, N2O, C2HF5, C4F8, BF3, and laser gases are replacing or at least reducing the requirement of NH3, BCl3, and SiH4.

The use of  $N_2O$  is expected to double from

and flexibility with small wire diameter (20 – 100 nm), but haze is an issue. CNT has excellent conductivity, transmittance, and flexibility, but the supply chain needs to be developed. Single walled carbon nanotubes (SWNT) technology from Linde uses liquid ammonia to produce solubilized carbon nanotubes in the form of inks, which can then be deposited as films and has

μm). AgNW demonstrates

excellent transmittance

5,000 TPA (tons per annum) in 2013 to 10,000 TPA in 2017. Why nitrous oxide? The move from a-Si to MO requires a change in the TFT device structure where the a-Si layers (g-SiNx, a-Si, n+) are being replaced by the MO layers (g-SiOx + indium gallium zinc oxide). This requires a change from  $NH_3$  to highvolume, high-purity N<sub>2</sub>O.

LTPS process also uses  $\rm N_2O$  for its oxide layer deposition. In addition, LTPS uses XeCl (xenon monochloride) excimer lasers for annealing after the

the added benefit of zero carbon footprint.

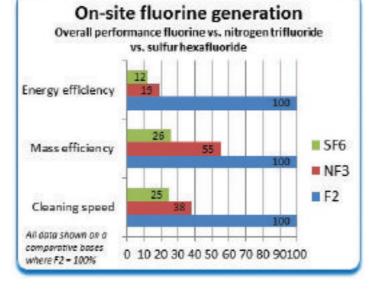

$F_2$  as replacement for  $NF_3$  and  $SF_6$ : For a typical large TFT-LCD fab, chamber cleaning gas demand can exceed 300 tons per year. Traditionally  $NF_3$  has been used. The GWP100 (100-year Global Warming Potential) for  $NF_3$  is 17,200; for the replacement  $F_2$ , the GWP100 is 0.

Switching to fluorine not only significantly reduces environmental footprint, but also leads to material DISPLAYS

cost savings and up to 50% reduction in cleaning time, increasing productivity (**FIGURE 2**).

Fluorine can also be used to replace Sulfur hexafluoride (SF<sub>6</sub>), which is used in dielectric etching. The GWP<sub>100</sub> for SF<sub>6</sub> is 22,800, which surpasses that of NF<sub>3</sub>. Significant improvements in etch rate and etch uniformity have been measured with the shift to F<sub>2</sub>.

On-site fluorine generation, like that available from

Linde, eliminates largevolume, high-pressure storage, and modular generators meet all flow and volume requirements for the largest scale fabs.

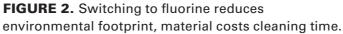

#### **The China factor**

Currently Korea is the leader in display manufacturing, with Taiwan and China on its heels and Japan a distant fourth (FIGURE 3). This is changing, though, as China rapidly gains market share. China, which started in most traditional manufacturing industries as "factory to the world," is a relative late comer in the display sector due to technology barriers.