SEMICONDUCTORS • PACKAGING • MEMS • LEDS •

MARCH 2013

DISPLAYS

## Sold State TECHNOLOGY Insights for Electronics Manufacturing

Today's Top Reliability Challenges P. 18

Exploring the Dark Side P. 21

Automated CMP Inspection P. 23

www.solid-state.com

**ECHNOLOGY**

## Vertical Throughwafer Insulation R 13

PennWell

## Qmags

# What new opportunities will you **CREATE** after The ConFab?

## How The ConFab Works

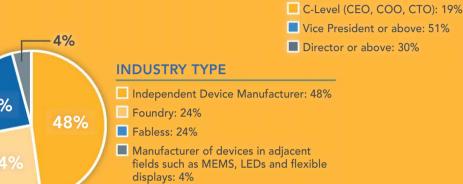

Influential manufacturing decision makers consistently attend The ConFab to collaborate about pressing challenges in the industry and how to achieve their future goals.

Executive roundtable discussions and private one-on-one meetings during The ConFab allow attendees and sponsors to create lasting strategic partnerships.

The conference attracts executives with strategic responsibilities who are looking for solutions to complex problems and new opportunities for collaboration.

Well-attended evening receptions and meals help attendees connect with each other and sponsors as they look for opportunities to have deeper discussions.

Conference & Networking Events June 23-26, 2013 Encore at the Wynn, Las Vegas

Presented by:

Space is limited. **REGISTER NOW** to qualify for the **early bird rate of \$1,595** for The ConFab's 2-day manager's conference.

## CONNECT. COLLABORATE. CREATE.

Owned & Produced by:

PennWell

www.theconfab.com

Zoom out

For navigation instructions please click here

LEDS

MEMS

Search Issue

DISPLAYS

Next Page

**MARCH 2013**

SEMICONDUCTORS •

Zoom in

Sold State TECHNOLOGY Insights for Electronics Manufacturing

PACKAGING

Today's Top Reliability Challenges P. 18

Exploring the Dark Side P. 21

Automated CMP Inspection P. 23

## Vertical Throughwafer Insulation P. 13

PennWell

Contents

www.solid-state.com

Zoom in

Zoom out

Search Issue

Next Page

### Omags

### 2013 MRS SPRING MEETING & EXHIBIT

April 1–5, San Francisco, CA

#### **PREREGISTRATION DEADLINE MARCH 15, 2013**

ECHNOLOGY

- ENERGY

- А Film Silicon Science and Technology

- В Organic and Hybrid Photovoltaic Materials and Devices

- С Thin-Film Compound Semiconductor Photovoltaics

- From Molecules to Materials-D

- Pathways to Artificial Photosynthesis Materials and Integration Challenges for Energy Generation Е

- and Storage in Mobile Electronic Devices

- F Materials for Vehicular and Grid Energy Storage

- G Electrochemical Interfaces for Energy Storage and Conversion-Fundamental Insights from Experiments and Computations

- Н Nanoscale Thermoelectrics-

- Materials and Transport Phenomena II

- Т Materials for Solid-State Refrigeration

- J In-Situ Characterization Methods in Energy Materials Research

- Κ Materials for Sustainable Development

#### NANOMATERIALS

- Nanoparticle Manufacturing, Functionalization, Assembly, L and Integration

- Μ Solution Synthesis of Inorganic Functional Materials-Films, Nanoparticles, and Nanocomposites

- Ν Nanomaterials in the Subnanometer-Size Range

- 0 Beyond Graphene-2D Atomic Layers from Layered Materials

- Р Graphene and Related Carbon Nanomaterials

- Q Surfaces of Nanoscale Semiconductors

- R Nanostructured Semiconductors and Nanotechnology

- S Nanostructured Metal Oxides for Advanced Applications

- Electrical Contacts to Nanomaterials and Nanodevices Т

- П Measurements of Atomic Arrangements and Local Vibrations in Nanostructured Materials

- ٧ Nanoscale Heat Transport—From Fundamentals to Devices

- W Piezoelectric Nanogenerators and Piezotronics

- Advances in Scanning Probe Microscopy Υ

- for Imaging Functionality on the Nanoscale

- Ζ Nanotechnology and Sustainability

#### **ELECTRONICS/PHOTONICS**

- Advanced Interconnects for Micro- and Nanoelectronics-AA Materials, Processes, and Reliability

- BB Evolutions in Planarization-Equipment, Materials, Techniques, and Applications

- CC Gate Stack Technology for End-of-Roadmap Devices in Logic, Power, and Memory

- DD Emerging Materials and Devices for Future Nonvolatile Memories

- Phase-Change Materials for Memory, Reconfigurable EE Electronics, and Cognitive Applications

- Compound Semiconductors for Generating, Emitting, FF and Manipulating Energy II

- Single-Dopant Semiconductor Optoelectronics GG

- Materials for High-Performance Photonics II HH

- Resonant Optics in Metallic and Dielectric Structures-Ш Fundamentals and Applications

- JJ Fundamental Processes in Organic Electronics

- Charge and Spin Transport KK

- in Organic Semiconductor Materials

#### BIOMATERIALS

- 11 Hybrid Inorganic-Biological Materials

- New Tools for Cancer Using Nanomaterials, MM Nanostructures, and Nanodevices

- ΝN Multifunctional Biomaterials

- 00 Design of Cell-Instructive Materials

- Adaptive Soft Matter through Molecular Networks PP

- QQ Conjugated Polymers in Sensing and Biomedical Applications

- Lanthanide Nanomaterials for Imaging, Sensing, RR and Optoelectronics

- SS Bioelectronics-Materials, Interfaces, and Applications

- ΤT Materials and Processes for Electronic Skins

#### GENERAL

- Plasma and Low-Energy Ion-Beam-assisted Processing UU and Synthesis of Energy-related Materials

- VV Materials Applications of Ionic Liquids

- WW Nuclear Radiation Detection Materials

- ΧХ Oxide Thin Films and Heterostructures

- for Advanced Information and Energy Technologies YΥ

- Titanium Dioxide—Fundamentals and Applications

- Carbon Functional Interfaces II ΖZ

- AAA Superconducting Materials-From Basic Science to Deployment

- BBB Size-Dependent and Coupled Properties of Materials

- CCC Novel Functionality by Reversible Phase Transformation

- DDD Extreme Environments—A Route to Novel Materials

- EEE Materials Education—Toward a Lab-to-Classroom Initiative

#### www.mrs.org/spring2013

#### 2013 MRS SPRING MEETING CHAIRS

Mark L. Brongersma Stanford University Vladimir Matias iBeam Materials, Inc. Rachel Segalman University of California, Berkeley Lonnie D. Shea Northwestern University Heiji Watanabe Osaka University

#### Don't miss these future MRS meetings!

2013 MRS Fall Meeting & Exhibit - December 1-6, 2013 Hynes Convention Center & Sheraton Boston Hotel Boston, Massachusetts

2014 MRS Spring Meeting & Exhibit - April 21-25, 2014 Moscone West & San Francisco Marriott Marguis San Francisco, California

506 Keystone Drive - Warrendale, PA 15086-7573 Tel 724.779.3003 - Fax 724.779.8313 info@mrs.org • www.mrs.org

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page **CHNOLOGY**

MARCH 2013 VOL. 56 | NO. 2

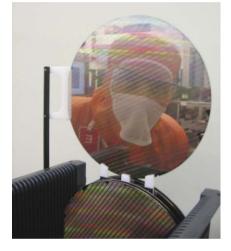

Wafers await processing inside Silex's MEMS fab.

#### FEATURES

**ADVER**

#### PACKAGING | Vertical through-wafer insulation: Enabling integration and innovation

Through-wafer insulation has been used to develop technologies such as Sil-Via TSV and Zero-Crosstalk. Peter Himes, Silex Microsystems AB, Järfälla SWEDEN

#### **RELIABILITY** | Today's top reliability challenges

BTS, BTI, soft errors, dielectric breakdown and other reliability challenges will be addressed at the upcoming International Reliability Physics Symposium. Pete Singer, Editor-in-Chief.

#### **INSPECTION** | Exploring the dark side

A look at the impact of back side particles on front side defectivity. Rebecca Howland, Ph.D. and Marc Filzen, KLA-Tencor, Milpitas, CA.

### **CMP** | Automatic wafer inspection system

#### replaces eyeballs with cameras

A fully automated RDS inspection system to replace human inspectors is a game changer. Christopher Eric Brannon, Texas Instruments, Inc., Dallas, TX

#### **RELIABILITY** | Insights into low frequency noise in high-mobility transistors

The impact of high-mobility channel materials and novel device architectures on the lowfrequency noise behavior of 22nm and below CMOS transistors is reviewed. Eddy Simoen, et al, imec, Leuven, Belgium.

#### COLUMNS

25

- Editorial | Filling the fabs of the future, Pete Singer, Editor-in-Chief 3

- **11** LEDs | Worldwide LED component market grows 9%, *Ella Shum*, Strategies Unlimited

- **13** Packaging | 3D IC with TSV: Status and developments, Jan Vardaman, TechSearch International

- **33** Industry Forum | Managing process variations, Dr. Zhihong Liu, Executive Chairman, ProPlus Design Solutions

www.solid-state.com

#### EPARTMENTS

- Web Exclusives

- News 4

- **30** New Products

- 32 Ad Index

SOLID STATE TECHNOLOGY **MARCH 2013**  1

Omag

Contents | Zoom in | Zoom out | Refer a Friend | Search Issue

## Qmags

## Online@www.solid-state.com

### Web Exclusives

### **ISSCC 2013**

Trends unveiled at the International Solid State Circuits Conference (ISSCC) are described by subcommittee chairs, focusing on high-performance digital, memory, analog, wireless, RF, energyefficient digital, large-area displays, MEMS, medical and imagers. http://bit.ly/1335ed9

## Intel foundries MEMS for fuel cell start-up Nectar

Chipworks' Dick James reports on how Intel manufactured a fuel-cell based USB charging system on a 200mm wafer for a start-up called Nectar. The Nectar generator chip contains the fuel processor, fuel cell stack, and catalytic converter. The fuel processor cracks the butane into hydrogen and carbon monoxide by using a lean mixture of air

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue

and butane to give incomplete combustion; then O<sub>2</sub>- ions from the air feed on the other side of the SOFC stack migrate through the stack and combine to give water and carbon dioxide; then the exhaust gases exit through a catalytic converter. The fuel processor uses a mechanically suspended reaction zone formed in silicon, with a heat exchanger adjacent to the reaction zone. http://bit.ly/Wlw0aD

## Looking for an integrated post-tapeout flow

Dr. Steffen Schulze, the Product Management Director for the Mentor Graphics' Calibre Semiconductor Solutions, says the issue of platforms has been on his mind. He notes that a platform not only provides the integration and efficient operation at the workflow level, but it also enables efficiency at the data-center level, considering the simultaneous and sequential execution of many different designs and computational tasks. <u>http://bit.ly/Y2DxQh</u>

#### EUV source roadmaps: Physics vs Engineering

Dr. Vivek Bakshi tackles the question of when EUV sources will be ready to support high volume manufacturing. He notes that it is a difficult question to answer, partly because readiness metrics have been a moving target. http://bit.ly/XgaKJO

#### MEMS: The first prototype

MEMS-developer David DiPaola blogs about MEMS new product development, including the importance of the first prototype. He notes that nothing shows proof of principle and sells a design like a working prototype. http://bit.ly/12YNnbB

#### Insights from the Leading Edge

Dr. Phil Garrou reports on SEMI Europe's first European 3D

TSV Summit in Grenoble, held in late January with a theme of "On the Road towards TSV Manufacturing". ST showed wide IO bandwidth capability the same as LPDDR3 although the DDR memory takes a significant hit in power efficiency. http://bit.ly/XINT5J

2

CHNOLOGY

www.solid-state.com

## editorial

## Filling the fabs of the future

At press time, the sessions for The ConFab 2013 (www. theconfab.com) are being finalized. The overall theme of the conference is "Filling the fabs of the future," with a focus on the types of products that will drive demand for semiconductors in the next decade, the technologies and processes that will be required to meet this demand, and the manufacturing and operational challenges that will arise as a result of this demand and how to meet them.

We'll kick things off on Tuesday morning with a keynote talk by Y.W. Lee, vice chairman of Samsung. Session 1 will focus on major economic trends, with talks from Jim Feldhan of Semico, Bill McClean of IC Insights, Mark Thirsk of Linx Consulting and Dan Hutcheson of VLSI Research.

"Join us for The ConFab 2013 by registering now on our website, <u>www.theconfab.com</u>"

Next, we'll look at the design/manufacturing/ packaging/testing supply chain, including collaboration between fabless/product design companies and foundries. Mike Campbell of Qualcomm and Jae Cho of Xilinx will present in this session. In the afternoon on Monday, we'll hear from a panel of experts on 3D integration, including Mike Ma of SiliconWare, Subu Iyer of IBM (who will also be keynoting on Tuesday morning), HoMing Tong of ASE, and Bob Patti of Terazzon. A special thanks to Phil Garrou and IEEE CPMT, the technical sponsor of this session and another session on Advanced Packaging.

Tuesday will begin with a keynote from Subu Iyer, followed by a panel session moderated by Scott Jones of Alix Partners. The session will focus on R&D Portfolio Management and Improving R&D Efficiency. Jones will share the results of a AlixPartners' study of the 72 largest semiconductor companies globally over the past six years that found that companies with a higher degree of R&D efficiency show greater profitability.

We'll then get into a status report on advanced packaging, with an excellent line-up of speakers, including: Devan Iyer from Texas Instruments, Bob Lanzone from Amkor, Steve Anderson from STATS ChipPAC, and Ted Tessier from FlipChip International.

In the afternoon on Tuesday, we'll hear from Sanjay Rajguru of ISMI and a panel of speakers assembled by ISMI, focusing on accelerating manufacturing productivity. I hope you can join us! —**Pete Singer**, Editor-in-Chief

### Solid State TECHNOLOGY.

Susan Smith, Group Publisher Ph: 603/891-9447, susans@pennwell.com Pete Singer, Editor-in-Chief

Ph: 603/891-9217, psinger@pennwell.com

Shannon Davis, Editor, Digital Media Ph: 603/891-9145, shannond@pennwell. com

Robert C. Haavind, Editor-at-Large Ph: 603/891-9453, bobh@pennwell.com

Phil Garrou, Contributing Editor Michael Fury, Contributing Editor

Justine Beauregard, Marketing Manager Cindy Chamberlin, Editorial Graphic Designer

Sheila Ward, Production Manager Dan Rodd, Illustrator

www.solid-state.com

ECHNOLOGY

Debbie Bouley, Audience Development Marcella Hanson, Ad Traffic Manager EDITORIAL ADVISORY BOARD John O. Borland, J.O.B. Technologies

Michael A. Fury, The Techcet Group, LLC Rajarao Jammy, SEMATECH William Kroll, Matheson Tri-Gas Ernest Levine, Albany NanoTech Lars Liebmann, IBM Corp. Dipu Pramanik, Cadence Design Systems Inc. Griff Resor, Resor Associates A.C. Tobey, ACT International

#### EDITORIAL OFFICES

PennWell Corporation, Solid State Technology 98 Spit Brook Road LL-1, Nashua, NH 03062-5737; Tel: 603/891-0123; Fax: 603/891-0597; www.ElectroIO.com

#### PennWell

#### **CORPORATE OFFICERS**

1421 South Sheridan Rd., Tulsa, Ok 74112 Tel: 918/835-3161 Frank T. Lauinger, Chairman Robert F. Biolchini, President and CEO Mark Wilmoth, Chief Financial Officer

TECHNOLOGY GROUP Christine A. Shaw, Senior Vice President and Publishing Director

For subscription inquiries: Tel: (847) 559-7500; Fax: (847) 291-4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com We make portions of our subscriber list available to carefully screened companies that offer products and services that may be important for your work. If you do not want to receive those offers and/or information, please let us know by contacting us at List Services, Solid State Technology, 98 Spit Brook Road, Nashua, NH 03062. All rights reserved. No part of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval system, without written permission of the copyright owner. Prices for bulk reprints of articles available on request. Solid State Technology articles are indexed in Engineering Information and Current Contents, and Applied Science & Technology Index and abstracted by Applied Science & Technology Abstrats.

AMERICAN BUSINESS MEDIA

3

Qmags

SOLID STATE TECHNOLOGY

MARCH 2013

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

Please send news articles to peters@pennwell.com

### worldnews

WORLD STMicroelectronics and Hyundai Autron plan to jointly develop integrated products for next-generation vehicles.

WORLD | Singaporebased A\*STAR's Institute of Microelectronics and Stanford University will develop switch technology for efficiency in mobile devices.

USA Cabot Microelectronics Corp. will collaborate with SEMATECH to develop advanced solutions for emerging CMP applications.

**EUROPE** | **Tronics** launched a new large-scale MEMS project to industrialize **CEA-Leti's** technology.

**USA** Araca and ISMI are partnering to deliver CMP processing and productivity solutions.

ASIA Renesas and J-Devices signed a MoU regarding the transfer of the semiconductor backend production business of three facilities.

ASIA STATS ChipPAC and UMC demonstrated aTSV-enabled 3D IC chip stacking technology developed under an open ecosystem collaboration.

JAPAN | Mitsubishi Electric Corp. developed a prototype multi-wire electrical discharge processing technology to cut SiC ingots.

**EUROPE** | Imec and PVA Tepla achieved void detection in throughsilicon vias at wafer level.

USA | SRC and DARPA dedicated \$194 million to six new university microelectronics research centers.

ECHNOLOGY

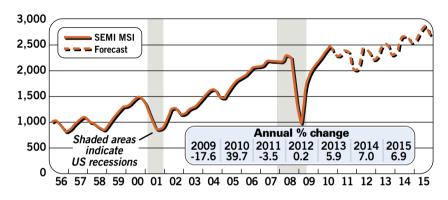

## Econometric Forecast: Semiconductor growth should recover by 2014

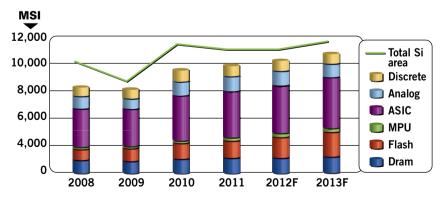

The weakness in economic growth spills into end products containing semiconductors in 2012 and early 2013, according to a new report from Linx Consulting. Their model relating final demands to up at a modest pace that averages slightly less than 6% for the full year. By 2014, growth should recover to long-term potential growth for MSI of approximately 7%/year. Key assumptions driving this

aggregate semiconductor production (measured by SEMI's Million Square Inches of silicon processed, MSI) suggests weak demand was anticipated in 2012, and that by early 2013, enough improvement in end markets occurs to push growth forecast include some solution to the fiscal cliff dilemma that permits US consumers and businesses to begin to return to more normal conditions. Removing uncertainty drives a modest expansion US spending on technology goods of

Figure 2. The difference between Segment Demand and Total Silicon Area (includes test and monitor wafers).

4 MARCH 2013 SOLID STATE TECHNOLOGY

www.solid-state.com

around 2.3%, up from the anemic 0.8% growth anticipated for 2012. Most of that growth will occur in the second half of 2013, as it will take some time for businesses to analyze the new policy environment and then implement investment plans. Inventoryshipment ratios for technology goods, which are spiking in the last half of 2012, are assumed to recede on a steady pace to more typical levels through 2013. If shipments in IT goods do not develop as expected, the quarterly pattern above would most likely show a steeper decline in 2012Q4 and a further decline in 2013Q1. followed by strong gains in Q2 or Q3.

The overall picture of MSI growth breaks down into the expected performance of device segments and technology nodes. Despite the shift to consumer electronics and mobile platforms, we expect growth to be concentrated in CMOS products with a continuing slowing of unit growth and analog and discrete devices. Strongest growth will remain with flash memories, and advanced foundry logic devices targeted at tablets and phones.

In contrast with advanced memory and logic processing, approximately 56% of the market continues to be produced at design dimensions in excess of 100 nm on wafer sizes at 200 mm or smaller. This market segment is extremely sensitive to economic volatility and has slowed significantly in the last four years. Manufacturers of these devices are often capital constrained and extremely cost sensitive, leading to little process innovation and limited capacity expansion. On a technology basis, despite tight capital budgets, the introduction of devices at 28 and 22nm half pitches continues apace, *Continued on page 8*  Omac

www.solid-state.com

ECHNOLOGY

SOLID STATE TECHNOLOGY MARCH 2013

5

## **news**cont

#### GaN use growing in power semiconductors

GaN has turned out to be the choice for most of the power semiconductor applications and is quickly replacing the existing silicon technology, according to a new report from Research and Markets. The various properties of GaN, such as wider bandgap, high break-down voltage, larger critical electric field, and higher thermal conductivity, let the GaN devices operate at higher voltages, high switching frequencies, handle higher power density, and offer enhanced power efficiency than the pure Si devices. These properties allow the GaN discretes like Schottky diodes, MOSFETs, and the other advanced transistors to operate at much higher voltage levels, which are difficult for the counterpart Si devices. GaN power semiconductors also help in reducing the conduction and switching losses. The major application segments are the inverters (and converters), RF devices, power supply modules, and motor drives. ◆

### 10 IC product segments to exceed total IC market growth in 2013

Ten product categories, led by tablet MPUs and cellphone application MPUs, are forecast to exceed the 6% growth rate forecast for the total IC market this year, according to IC Insights' 2013 McClean Report. This report identifies and segments the total IC market into 34 major IC product categories. Five categories are forecast to enjoy double-digit growth. The number of categories with positive growth is expected to more than double to 22 in 2013 from 10 in 2012.

Consumer-driven mobile media devices, particularly smartphones and tablet computers, are forecast to keep the tablet MPU (50%) and cellphone application MPU (28%) segments at the top of the growth list for the third consecutive year. Other IC categories that support mobile systems—including NAND flash (12%) and special-purpose logic devices—are expected to enjoy better-than-industry-average growth in 2013, as well.

Due to increasing demand for higher levels of precision in embedded-processing systems and the growth in connectivity using the Internet, the market for 32-bit MCUs is also forecast to outpace total IC market growth in 2013. Embedded applications in medical/health systems and smartcards have helped boost the 32-bit MCU market. In the automotive world, demand for

| Product Category                             | 2012 Growth | 2013F Growth |

|----------------------------------------------|-------------|--------------|

| Tablet MPUs                                  | 60%         | 50%          |

| Cellphone App MPUs                           | 41%         | 28%          |

| Wired Telecom – Special Purpose Logic/MPR    | 17%         | 13%          |

| NAND Flash                                   | 6%          | 12%          |

| Wired Telecom – App-specific Analog          | 24%         | 11%          |

| DRAM                                         | -10%        | 9%           |

| Wireless Telecom – Special Purpose Logic/MPR | 9%          | 9%           |

| Auto – Special Purpose Logic/MPR             | 2%          | 7%           |

| Consumer – Special Purpose Logic/MPR         | 12%         | 7%           |

| 32-bit MCU                                   | 4%          | 7%           |

| Total IC Market                              | -2%         | 6%           |

|                                              |             |              |

32-bit MCUs is being driven by "intelligent" car systems such as driver information systems and semi-autonomous driving features such as self-parking, advanced cruise controls, and collision-avoidance systems. In the next few years, complex 32-bit MCUs are expected to account for over 25% of the processing power in vehicles.

After back-to-back years of steep declines in 2011 and 2012, the DRAM market is forecast to increase 9% in 2013, three points more than the total IC market. DRAM unit growth is expected to increase only 2%, but the overall average selling price is forecast to jump 7% this year. In five of the past six years (2007-2012) the DRAM

5 MARCH 2013 SOLID STATE TECHNOLOGY

CHNOLOGY

www.solid-state.com

market declined, which took its toll on weaker suppliers. Fewer suppliers in the marketplace mean fewer competitors trying to undercut each other's prices in order to

MPR and wired telecom-application-specific analog. To a lesser degree, the wired telecom segments are growing on account of developing country markets.

gain marketshare and enhances the likelihood of a more stable pricing environment in the coming year.

Interestingly, in a world that is increasingly wireless, two IC categories of "wired" telecom ICs are forecast to grow faster than the total IC market. Wired telecom-special purpose logic/ MPR and wired telecom-application-specific analog are forecast to grow by 13% and 11%, respectively.

Telecom companies and network operators have been upgrading their long-haul and metropolitan-wide communications systems, which require many high-speed transmission ICs and other circuits. New 100Gb/s technology has been ready for deployment since 2009 and is being deployed now. Next-generation transmission technology and ICs for 1 trillion bits per second ("Terabit") networks are in development.

Telecom and network operators say data traffic is increasing more than 50% per year due to growing use of the Internet and video transmissions. All wireless traffic eventually goes through high-speed cable transmission "backbone" networkscommunications are routed over long distance via optical cable before getting to the cellular network on the other end. All the mobile Internet, data, and video traffic has to go through a cable network and that is driving up the market for wired telecom-special-purpose logic/

## **POWER SOLUTIONS FOR** SEMICONDUCTOR DESIGN, MANUFACTURE AND TEST

Previous Page | Contents | Zoom in | Zoom out | Refer a Friend | Search Issue | Next Page

- ► Fan cooled

- Multi output

- Redundant systems

www.tdipower.com | 908.850.5088

www.solid-state.com

ECHNOLOGY

Qmags

7

## **EVVS**cont

### China's top 10 packaging and assembling facilities

Packaging and assembly are key segments of the growing semiconductor supply chain in China. SEMI China reports that, based on their tracking of 139 companies, and considering numerous small companies not tracked in detail, there are over 200 companies competing in the packaging and assembly market in China. Although many are small companies manufacturing low-pin count devices, all of the world's "Top 10" OSAT, **Outsourced Semiconductor Assembly** and Test, players have one or more assembly and testing facilities in China. Eight of the world top 10 IDM companies have assembly and test manufacturing facilities in China, and most entered into China earlier than the OSAT players, in the mid-1990s.

Top Ten OSAT Facilities in China

- 1. ASE

- 2. Amkor

- 3. SPIL

- 4. STATS ChipPAC

- 5. Powertech

- 6. UTAC

- 7. ChipMOS

- 8. JCET

- 9. KYEC

- 10. Unisem

#### Forecast Continued from page 5

**MARCH 2013**

2

**ECHNOLOGY**

and significant process challenges are driving increased complexity and resultant challenges in patterning, cleaning, CMP and deposition throughout the device

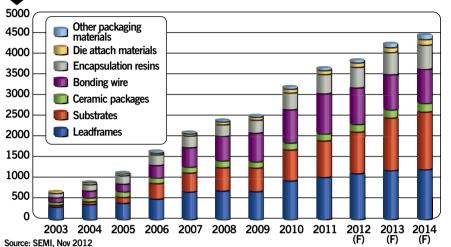

#### China packaging material market (\$M)

companies, domestic subcontractor companies are increasingly joining the global outsourcing market. The assembly of smallsize optoelectronic chips like CMOS image sensors is the most mature 3D through-silicon via platform at the moment and China players occupy an important place through transferring authorized technology from oversea partners. Also, domestic semiconductor equipment suppliers that previously focused on front-end tool development are applying their products in wafer level package and TSV assembly.

In addition to the international

manufacturing process. 2012 is forecast to have produced more silicon area at 32nm than any other node, and the introduction of low 20nm half pitches and flash has continued to grow startling rates.

With the growth of semiconductor packaging industry in China, domestic packaging material suppliers are emerging with the industry and are now starting to serve the worldwide leading packaging houses. Given the emphasis on low-cost manufacturing, packaging houses will continue to evaluate China-based suppliers to realize lower material cost. On the other hand, to enhance their competitive power, stabilize sales and marketing channels, and reduce operational risk, China-headquartered material suppliers are forming partnerships with leading packaging houses.

In total devices manufactured at 65nm and below continued to show strong area growth in 2012 of 14%, with devices at 90nm and above largely offsetting declines from 2011 with 8% growth in 2012. (

www.solid-state.com

SOLID STATE TECHNOLOGY

### MEMS devices shape medical industry

MEMS devices are shaping the competitive landscape in the global medical device industry. According to a new report from Global Information, several factors are behind the increasing demand for and innovation in MEMS devices in the medical industry: growing number of MEMS applications in healthcare; innovations, revolution and growth in the personal healthcare market, including wireless implants; and rising awareness and affordability of healthcare.

The use of MEMS devices by different stakeholders is driving market growth by adding to the demand of devices from different medical market segments as discussed above. This is also indirectly encouraging for medical sector market players (particularly big ones) that have diverse customer bases composed of different stakeholders and diverse product portfolios (such as diagnostics, research, and medical devices), as they can capitalize on the MEMS market by leveraging their existing resources to some extent. Moreover, a diverse set of devices catering to the needs of different stakeholders encourages new entrants into sectors of their choice to complement or suit their capabilities and potentials.

Integrated devices and advancements in inertial sensors, such as products for human motion analysis, are meeting the needs of the modernized healthcare delivery model,

especially for the elderly patient sector, by adding the element of prevention. An example of product innovation is microneedles for drug delivery, which is gaining popularity by offering a pain-free and enhanced, accurate method of drug delivery. Similarly, the diagnostic devices have significantly reduced the sample testing time from hours to a few minutes, thus significantly adding value to the healthcare delivery model from different perspectives such as time efficiency, convenience, patient satisfaction, and ease of operations.

Microfluidic/lab on chip (LOC) is considered a revolutionary technology for the life sciences and healthcare industry. This technology enables the integration of assay operations, such as sample pretreatment and sample preparation, on a single chip. This is radically changing the pharmaceutical and life-sciences research sector by changing the way procedures, such as DNA analysis and proteomics, are conducted.

The microfluidic/lab on chip (LOC) segment is expected to rise to 72% of the market share of MEMS devices by 2017. Major growth drivers of this sector are research tools, which are expected to achieve significant growth of CAGR 28.8% from 2012 to 2017. A surge from 2012 to 2017 in research applications, such as proteomics, genomics, and cellular analysis, is also expected to boost this sector.

In terms of applications, the macro segments of the market include pharmaceutical and lifesciences research, in vitro diagnostics, home healthcare, and medical devices. Among all of these applications, research is expected to grow at the highest CAGR of 28.3% from 2012 to 2017.

Expected to triple in size over the next five years, the bioMEMS market is expected to grow from \$1.9 billion in 2012 to \$6.6 billion in 2018. Microsystem devices have applications in four key healthcare markets: pharmaceutical, in-vitro diagnostics, medical devices and medical home care. Microsystem devices have become increasingly visible in the healthcare market by serving as solutions adapted to the requirements of various applications. The usefulness of these devices is two-fold: they improve medical device performance for the patient; and secondly, they offer competitive advantages to system manufacturers. For example, the introduction of accelerometers in pacemakers has revolutionized the treatment of cardiac diseases.

www.solid-state.com

SOLID STATE TECHNOLOGY

**MARCH 2013**

## **IEV/S**cont.

### Silicon Innovation Forum to bridge funding gaps

SEMI, in collaboration with strategic investing groups throughout the global semiconductor industry, has announced the Silicon Innovation Forum, or SIF, to bridge funding gaps for new and early-stage companies with valuable semiconductor manufacturing and technology solutions. SIF will be held in conjunction with SEMICON West, on July 9, 2013 at the Moscone Center in San Francisco, Calif. The event will consist of a one-half day conference highlighted by investment presentations from new and emerging companies with innovative technology solutions targeted at next generation semiconductors. The Silicon Innovation Forum is being organized by leading strategic investment groups in the industry including Applied Ventures, Dow Chemical Company, Intel Capital, Micron Ventures, TEL Venture Capital, and Samsung Ventures.

"At a time when the need for new ideas and technologies has never been greater, venture capital and private funding sources for advanced semiconductor technology development has significantly declined over the past decade, threatening the future of Moore's Law and the economic engine of today's connected, electronic society," said Denny McGuirk, president and CEO of SEMI. "The Silicon Innovation Forum will address these funding gaps by providing a platform for new and emerging innovators, strategic investors, and venture capitalists to discuss the needs and requirements for next-generation technologies, and provide insights into technology, capital, partnership, and collaboration strategies necessary for mutual success."

This collaboration of leading strategic investor groups from throughout the world has formed to streamline and accelerate partnership opportunities for technology entrepreneurs to bridge the gap between R&D and product development funding. The Forum will provide short-term business opportunities for early / mid-stage companies, R&D entrepreneurs from larger companies, and other industry innovators - while addressing long-term structural changes to the industry necessary to foster a healthy innovation pipeline.

New and emerging companies can showcase their innovations through table top and/or poster displays for one-on-one meetings with qualified investors, plus showcase their ideas during short pitches during the SiF Conference. The SIF Conference will be free to all SEMICON West attendees, but the Innovation Showcase and Reception for one-on-one presentation and meeting opportunities will be restricted to qualified partnership and investor groups.

#### **Tronics to produce** submicron MEMS technology of CEA-LETI

Tronics launched a new large-scale MEMS project to industrialize CEA-Leti's breakthrough M&NEMS, or Micro and Nano Electro-Mechanical Systems, technology. This technology is based on piezoresistive nanowires rather than pure capacitive detection, which will advance device performance and chip size. This project sets the stage for a new generation of combo sensors for motion sensing applications.

Within two years, the team will develop 6 DOF, 9 DOF and higher DOF devices, where all sensing elements are using the same M&NEMS technology. The goal is to achieve both significant surface reduction and performance improvement of the multi-DOF sensors. Beyond the smaller die size and the ultra-low power consumption, M&NEMS technology allows manufacturing of all the sensor's axes with one unique technology platform. This high level of integration and commonality simplifies the associated control and readout electronic circuits, both in terms of design and operational efficiency.

In addition to investments by Tronics and its partners, a substantial portion of the project's cost is supported by a 6.5 million euros grant provided by the French Ministry of Industry within its Nanoelectronique Industrial Support program.

To generate the volumes required by consumer applications, Tronics plans to support the technology all the way to high volume eight inch production maturity.

www.solid-state.com

10 **MARCH 2013** SOLID STATE TECHNOLOGY

ECHNOLOGY

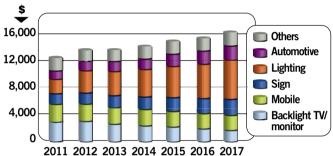

## Worldwide LED component market grows 9%

LED component revenue for lighting applications reached \$3.11 billion in 2012, narrowly dethroning the large area display backlight segment at \$3.06 billion. The worldwide market for LED components was \$13.7 billion and is expected to grow to \$15 billion in 2017, for a CAGR of 1.8%.

The total illumination market for 2012 is estimated at \$14.52 billion. LED lighting includes LED replacement lamps and luminaires is estimated at \$11.72 billion an increase of 26% between 2011 and 2012—and it is forecast to grow at a CAGR of 12% over 2012-2017.

LEDs used in large display (TV and monitors) backlights also reached a new record at \$3.06 billion in 2012. This is chiefly due to the success in penetrating the CCFL stronghold of the 32-inch TV. "Chubby" TVs will spread from 32 inches in both directions in size. It is expected to reach TVs 42 to 50 inches size in 2013-2014. With drastic reduction in number of LEDs used and rapid price erosion, the large display market for LEDs is expected to decline to \$1.7 billion in 2017.

The total market for LEDs in the automotive segment was \$1.4 billion in 2012 and is projected to grow to \$2.1 billion in 2017. The number of cars with LED headlights nearly doubled in 2012. Revenue for 2012 was \$97 million and the five-year CAGR is projected to be 36%.

While LED revenue from tablets grew 54% to \$578

million, the overall mobile segment dropped 3%. The drop in notebook LEDs

backlight demand, the OLED success in smart phone display, and the general demand decline for other small and medium display will take the segment down to \$958 million in 2017, for a 5 year CAGR of -7%.

The signage segment is expected to grow to \$2.4 billion in 2017, for a CAGR of 7%. Use of LEDs in signage and channel

letters grew 7% to \$1.7 billion in 2012. Full-color signs contributed more than 80% of the revenue.

On the supply side, 11 companies accounted for more than 72% of the LED market. We arrived at these figures after analyzing market demand as well as the supply-side activity of more than 54 LED component

Worldwide market for LED components. Source: Strategies Unlimited.

suppliers. Their rank by revenue of packaged LED components, is:

- 1. Nichia

- 2. Samsung LED

- 3. Osram Opto Semiconductors

- 4. LG Innotek

- 5. Seoul Semiconductor\*

- 6. Philips Lumileds\*

- 7. Cree

- 8. TG

- 9. Sharp

- 10. Everlight\*

- 11. Lumens\*

(\*Companies have the same ranking when the difference in revenue is within the margin of error. Revenue includes sales of packaged LEDs of 30 lm/W or more.)

The LED packaging industry is expected to grow modestly at a CAGR of 1.8% in the next five years. 2013 should see less severe price drops as excess capacity is slowly absorbed by the rise of lighting applications.

CHNOLOGY

SOLID STATE TECHNOLOGY **MARCH 2013** 11

Strategies Unlimited

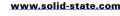

## 3D IC with TSV: Status and developments

While the drivers for 3D ICs remain performance and form factor, the time line for its adoption keeps shifting out into the future. Several technical challenges and infrastructure issues such are delaying high volume manufacturing of TSV technology for 3D ICs. Until these issues can be resolved, alternative packages will continue to be used.

On the technical side while there has been a lot of progress in via formation and filling, there are still some process steps that impact yield and have low throughput such as the debonding step during wafer thinning. The problem is combo material and equipment problem. New materials are being introduced and show promise, but engineering requires time. Stacking memory would seem to be the first step, but has proved to be challenging. 3D IC solutions without a debond step have been introduced by Tezzaron using its architecture and a novel process to stack memory was introduced by Elpida before it went in bankruptcy.

Many companies show a silicon interposer or 2.5D solution on their packaging roadmaps where a logic device is mounted next to a stack of memory and the through silicon vias are in the substrate. The problem is that this assumes stacked memory with TSV is commercially available at a cost/performance ratio that matches the requirements. With the stacked memory unavailable this pushes out the adoption of even 2.5D. Some companies

also indicate that the cost of the

silicon interposer is too high

### Packaging

**ECHNOLOGY**

MARCH 2013 SOLID STATE TECHNOLOGY

and they would like to consider a glass interposer or even a highdensity organic substrate. At this time, glass interposers with TSVs are not commercially available and organic substrates with fine features are still in development.

For stacks of memory and logic the industry still needs thermally

**E. Jan Vardaman**, TechSearch International, Inc.

aware design tools and even new thermal solutions for stacks that contain logic and memory. Where there has been progress on test methodology development, additional work is still needed. Commercialization of EDA tools will benefit the industry greatly.

Once the 3D IC technical challenges are resolved and the technology becomes cost-effective, business challenges will remain until the industry settles on a model. According to ASE, the industry will use multiple models depending on the customer and the foundry.

Effect of Interposers on 3D IC Forecast

Many approaches to 3D packages exist, including stacked die with wire bond or wire bond/flip chip, stacked packages, package-on-package (PoP), and chipon-chip (CoC). Companies plan to continue the use of today's 3D packages with evolutionary improvements and adopt a 2.5D or interposer solution until 3D IC challenges can be met. It is important to remember that new package technology introduction takes time and the process and infrastructure have to be well developed: Xilinx spent 6 years to develop its now famous FPGA partitioned die on silicon interposer with TSV solution. ◆

www.solid-state.com

Next Page

#### PACKAGING

## Vertical through-wafer insulation: Enabling integration and innovation

PETER HIMES, Silex Microsystems AB, Järfälla SWEDEN

Through-wafer insulation has been used to develop technologies such as Sil-Via TSV and Zero-Crosstalk.

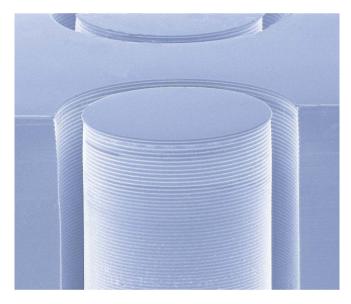

SI, or through-silicon insulation, is the processing of silicon wafers by MEMS techniques to create dielectrically isolated areas of the silicon. By taking advantage of the high aspect ratio and vertical sidewall capabilities of deep reactive ion etching (DRIE), trenches can be formed in silicon which extend all the way through the silicon wafer (FIGURE 1).

The final wafer after TSI processing exhibits islands of single crystal silicon separated by high quality isolation. This structure is the basis of TSI, and forms the building block of many of Silex's offered technologies.

TSI has been compared to either a dielectric isolation (DI) or silicon-on-insulator (SOI) process, and the comparisons are fairly close. TSI has, in fact, been called a "vertical SOI" process because of its similarity to SOI in creating an insulator-based separation between sections of single-crystal silicon. Unlike SOI, of course, TSI goes vertically through the wafer to create islands of silicon joined by insulating bands. In this second way, it is similar to a DI process where dielectrically isolated islands are created on a SOI device layer, which are then used in device manufacture like diode arrays. Unlike DI, though, TSI extends completely through the wafer: the standard thickness for a TSI processed wafer is  $430\mu m$ , thick enough to be processed through all MEMS or CMOS steps without the need for special carriers or handling. It is this mechanical strength which makes TSI so useful as a wafer level feature.

MEMS is, of course, a mechanical structure and

| Search Issue

FIGURE 1. SEM image of TSI DRIE etch through silicon.

MEMS structures can use the entire bulk of the silicon as elements in its construction. This is unlike ICs which are primarily concerned with the surface 10 or 20µm of silicon area where the circuit elements are formed. And yet MEMS wafers undergo wafer processing which has all the requirements of IC processing (in terms of implants, diffusions, thermal or deposited films, thermal budgets, etc.) plus additional challenges of deep etching, forming complex 3D structures, wafer to wafer bonding, debonding, oxide or silicon release, and noble metal processing. Any TSI process, then, would have to hold up to the full range of processing challenges.

#### Sil-Via TSV

TSI was developed in the 2003-4 timeframe when a working through-silicon via (TSV) approach was

PETER HIMES is Vice President, Marketing & Strategic Alliances, Silex Microsystems AB, Bruttovägen 1, Järfälla SWEDEN, peter. himes@silexmicrosystems.com, www.silexmicrosystems.com.

www.solid-state.com

| Search Issue

needed for a major customer. This customer needed a TSV solution which was via-first (the TSV patterned and formed prior to any other wafer processing), high density (small footprint of the device was critical), and high reliability (the end application was a smartphone.)

Traditional approaches to TSVs at the time were poly-fill (which didn't offer the low resistance or reliability that the customer needed) or metal-filled (which suffer from reliability concerns due to TCE mismatch with the silicon), but our engineers recognized that a new approach was needed. Their solution was to take a highly doped substrate, typically

FIGURE 2. SEM of the TSI etch to form the Sil-Via TSV.

**FIGURE 3.** Example of two Sil-Via TSVs with oblong shape. Note the tight via pitch possible with TSI processing.

phosphorous doped down to 1-3 m $\Omega$ -cm or less, and use the TSI approach to form a via out of the single crystal silicon (**FIGURES 2 and 3**).

The resulting structure is a single crystal, full wafer thickness TSV exhibiting typical resistances of  $0.5-1\Omega$ for a 100µm diameter x 430µm thick via. The single crystal construction (formed out of the native wafer material) is perfectly matched thermally to the wafer, eliminating any TCE concerns or reliability issues. The gap formed by the TSI etch is filled by a proprietary insulating material, and gives TeraOhm level DC isolation of the via post to the surrounding substrate.

The Sil-Via TSV went into production in 2005 and eventually ramped up to a peak of 2000 wafers per month. Since then, the Sil-Via has been in continuous production and implemented on over 50 different products on both 6" and 8" wafers. With over 50,000 wafers shipped across all products, we have seen zero field failures for the TSV making it one of the most widely recognized and reliable TSV technologies on the market.

Sil-Via TSVs have been used in bulk MEMS applications, wafer capping, and advanced silicon interposers for 2.5D and 3D packaging, as will be discussed below. They can support via pitches down to  $50\mu$ m and continuous via formation across the entire wafer. As we shall discuss later as well, Sil-Via provides an intriguing platform for higher functional integration, such as ESD protection diodes and functional interposer solutions.

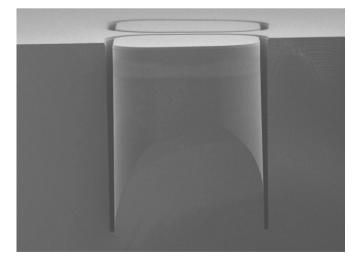

#### **Met-Via TSV**

While Sil-Via addressed the production, cost, and reliability needs of the market when it was released, TSI has been adapted to support metal through-silicon vias since then. Using the vertical isolation for sidewall protection of the TSV, Silex has brought to market an all-metal TSV that meets the low resistance and high frequency needs of our customers. Licensing the XiVia™ technology from ÅAC Microtec, another Swedish company creating packaging solutions for space-level reliability applications, the Met-Via utilizes two connected DRIE TSVs and double sided copper RDL plating with hermetically sealed vias to create a high reliability metal TSV. The XiVia approach creates a 'locking pin' which protects against thermal cycling concerns, and the hollow-plated TSV gives additional flexion for the TCE mismatch (FIGURE 4).

www.solid-state.com

Omage

14 MARCH 2013 SOLID STATE TECHNOLOGY

#### PACKAGING

**FIGURE 4.** Microphotograph of Met-Via interposer test structure with close-up of Met-Via cross-section showing the XiVia feature. (some metal smearing evident due to wafer saw).

#### Zero-Crosstalk substrate isolation

The Sil-Via TSV is in essence a round post through the silicon wafer, but the beauty of TSI's flexibility is that it doesn't have to be like that. TSI is patterned by lithography, so any geometry or shape can be formed as a TSI structure (There is a practical limit to this: first there are processing challenges relating to the percent of silicon being etched away across the entire wafer, and second the trench width has to be consistent in order to have a complete and reliable fill).

Taking a clue from the "Vertical SOI" image of TSI, Silex developed and also offers a substrate isolation platform called Zero-Crosstalk<sup>™</sup>. This uses either chains of Sil-Via type structures, or continuous trench rings to define the isolated areas of the silicon. Each silicon island then is completely DC isolated from its neighbors,

**FIGURE 5.** Zero-Crosstalk<sup>M</sup> concept CAD drawing.

www.solid-state.com

CHNOLOGY

making them act as physically distinct pieces of silicon. A common application for Zero-Crosstalk is to create separate analog and digital grounds for mixed-signal applications (**FIGURES 5 and 6**).

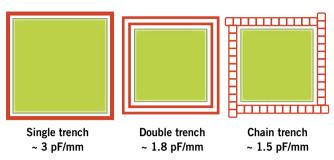

**FIGURE 6.** Three different options for Zero-Crosstalk showing typical capacitance figures for a 20µm trench – 350µm wafer thickness implementation.

Zero-Crosstalk can be implemented on low resistivity or high resistivity substrates, making it a viable technology for IC substrate isolation as well (**FIGURE 7**).

SOLID STATE TECHNOLOGY

**MARCH 2013**

15

PACKAGING

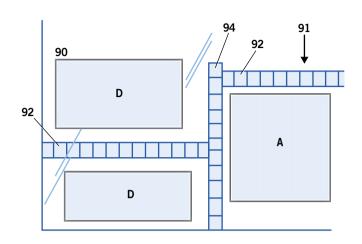

**FIGURE 7.** CAD drawing showing separate analog/ digital substrate areas defined by Zero-Crosstalk.

In the MEMS area, Zero-Crosstalk has among other applications been used for LED interposers to provide isolated substrates for diode arrays, X-Ray detectors to isolate individual detection elements, and in the following example.

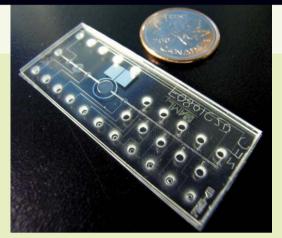

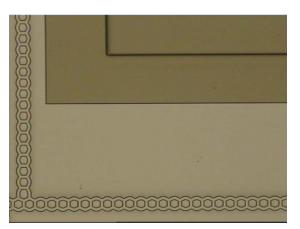

In this product example of a microbattery array from mPhase Technologies, TSI is used to create electrically isolated microbattery cells which also act as electrical interconnects through the cell layers. This is an example of the flexibility of TSI, where arbitrary geometries can be defined which can act both as Zero-Crosstalk areas and Sil-Via TSVs (**FIGURES 8-10**):

#### The rigid interposer approach

The application which drove the development of TSI and the Sil-Via TSV was for a 2.5D interposer with Zero-Crosstalk for cellphone microphones, with the CMOS ASIC mounted side-by-side. MEMS has, in fact, always been involved with advanced packaging requirements because of the need to package the MEMS and IC in the same package.

Interposers for package-level integration of multichip ICs is an emerging hot topic and an area that most major OSATs, one where packaging houses are looking to provide complete solutions. MEMS foundries like Silex have a critical role to play in this emerging supply chain, as the interposer foundry for either the IC company or the OSAT directly, as neither entity nor the traditional IC foundry has the infrastructure or expertise to build these 3D structures reliably and in high volume. Yole Developpement refers to this emerging supply chain element as the "Mid-End Foundry," and predicts it will service a \$1.7B market by 2017 as interposer packaging hits the mainstream.

And yet, despite all the press about 3D integration, the engineering challenges of 3D packaging have presented a substantial barrier to companies pursuing this packaging path. This is because each element of the package presents engineering challenges, and the current focus of the 3D industry (ultra thin wafers, specialty wafer handling, organic substrates, chip to chip signal routing, thermal and electrical optimi-

**FIGURE 8.** Cross section diagram of the 5-layer bonded mPhase microbattery structure.

**FIGURE 9.** Photomicrograph of the TSI chain structure defining the Zero-Crosstalk TSV structures for the mPhase microbattery.

FIGURE 10. Photomicrograph of the final mPhase microbattery (image courtesy mPhase Technologies, Inc.).

www.solid-state.com

16 MARCH 2013 SOLID STATE TECHNOLOGY

CHNOLOGY

#### PACKAGING

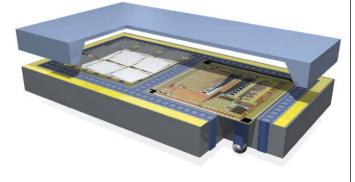

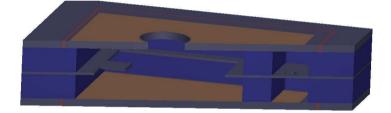

FIGURE 11. Graphic of a Sil-Via based interposer.

zation, and yield loss ownership by the supply chain) make the challenges to adoption more daunting. This focus is also concentrating on the very bleeding edge of technology (like the highest cost FPGAs), technologies which are overkill for the majority of ICs being produced in the market.

Our approach is to leverage our full wafer thickness TSI technology to provide rigid interposers to the marketplace, simplifying the engineering and supply chain challenges. "Rigid Interposers" means interposers from 300 to  $430\mu$ m thick, with enough mechanical strength to support the microbump, mounting and molding steps of the assembly process. By eliminating the ultrathin wafer requirements and associated bonding, debonding, and carrier handling steps, not only is the assembly process simplified but the organic substrate used in the 2.5D package can be eliminated. What results is an all-silicon package which is reliable, mechanically strong, and thermally stable for advanced IC use (**FIGURE 11**).

2.5D packaging technologies offer integration and footprint reduction advantages to a wide range of IC uses, yet the extreme costs and engineering challenges of the mainstream approach effectively removes it from consideration for the majority of the market. We believe that rigid interposers not only simplifies the engineering challenges, but makes 2.5D a viable option for a much broader IC market.

#### **Future TSI-enabled markets**

Even though it was created to solve a specific need, TSI remains a platform for innovation in bringing new customer-integratable features to the market. Among the technologies being worked on by Silex or with customers today are:

- Full DI substrates for IC processing the application of Zero-Crosstalk for IC applications, taking the concept of full dielectric isolation all the way to the IC fab.

- CMOS TSVs TSVs as interconnects which allow stackable components has long made technological and economical sense for MEMS components. Extending this to the IC world as a via-first or via-middle technology which can support full IC processing is the natural progression of this capability.

- Metal IC TSVs Many ICs require the performance of an all-metal TSV, and foundries want to avoid the cost and expense of thin wafer handling. Integrating the Met-Via TSV as a via-middle process into the customer's design and IC flow affords the advantages of all metal TSVs without the limitations of thin wafer handling (which are only available at the highest and most costly technology nodes)

- TSVs with Integrated Diodes since Sil-Via is a doped substrate silicon TSV, the via can be constructed to incorporate blocking or steering diodes directly into the via, thereby giving active component capability integrated directly into the via.

- TSVs with ESD protection a variant of the integrated diodes, especially for interposers where multiple chips can be interconnected and protected at the same time

- Through-silicon 3D inductors making use of the copper TSV technology of Met-Via to create a true wound inductor, using the silicon wafer itself as the inductor spool. A mag core element can be integrated to boost Q value, as well.

#### Summary

The TSI platform has proven to be a very reliable and production worthy technology. In continuous production for over six years, it has been integrated in one form or another in over two dozen different projects. Customers, working with Silex engineers, continue to find innovative ways to take what's available in TSI and re-purpose it for another use. By providing higher value customer-integratable features, both Silex and the customers stay ahead in the MEMS and packaging games. TSI truly allows all true semiconductor integration options to be "more than Moore." ◆

www.solid-state.com

| Next Page

#### RELIABILITY

## Today's top reliability challenges

#### PETE SINGER, Editor-in-Chief.

BTS, BTI, soft errors, dielectric breakdown and other reliability challenges will be addressed at the upcoming International Reliability Physics Symposium. HfO<sub>2</sub> with a

double challenge faces today's reliability engineers. They not only must understand the physics behind a complex set of mechanisms, such as bias temperature instability (BTI), but they must accurately simulate those mechanisms through modeling to predict device performance over time and estimated end-of-life.

These challenges will be front and center at the upcoming International Reliability Physics Symposium (IRPS), to be held April 14-18, 2013 at the Hyatt Regency Monterey Resort & Spa in Monterey, CA. The conference begins with tutorials on Sunday that run through Monday afternoon (40% of attendees are first time attendees). A plenary session on Monday afternoon after the tutorials is a "Year in Review" where experts highlight work published over the last year. Tuesday morning starts with a keynote by Berkeley's Chenming Hu who will talk about compact modeling as well as tri-gate scaled reliability challenges. Krishnan said that compact modeling is one of the main themes of this year's conference. "There has been a lot of work on how do we take reliability into the circuits and how do we model, not only at the SPICE level, but from a compact modeling perspective," he said. The Compact Modeling Council will have a meeting immediately following IRPS at the same location. Tuesday's keynote is followed by 19 sessions in three tracks, with a panel session, workshop and a combined poster session and buffet at Chateau Julien wine estate on Wednesday evening.

In terms of the overall reliability concerns now facing the industry, Krishnan said the number one thing people are worried about is the tri-gate finFET.

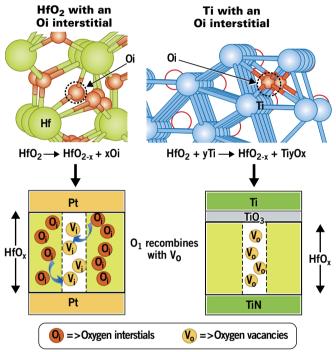

**FIGURE 1.** Atomistic structure of HfO2 with an  $O_i$  intersitials leading the the recombination of Oi+Vo in Pt/Pt during reset (left). Atomistic structure of Ti awith an  $O_i$  interstitial creating more  $V_o$  in HfO<sub>2</sub> (right).

"Our devices have been planar but now all of the sudden you have three sides to it. How do you reject the heat from a finFET?" he asks. "The second concern is basically electromigration. How do we scale EM?" The third main challenge lies in gallium nitride and HEMT structures. "What is the reliability of these GaN FETs in the field when you have some of these trapping effects that go on?" Krishnan asks. "The switch is good on day one but it slowly degrades over time. That's why you're seeing a lot on GaN FETs."

A few examples that will be presented at this year's IRPS will serve to highlight the reliability issues facing the industry.

**18 MARCH 2013** SOLID STATE TECHNOLOGY

ECHNOLOGY

www.solid-state.com

**FIGURE 2.** Examples of different erratic bit signatures (left). Normal and erract states are highlighted for clarity. Erratic bits percentage per signature classification in delay time cycling experiments are shown on the right.

#### **Reliability in memories**

Researchers from Mila Polytechnic, Micron and Intel will present a paper titled "Resolving Discrete Emission Events: a New Perspective for Detrapping Investigation in NAND Flash Memories." Charlie Slayman, IRPS Vice Technical Program Chair, said that researchers looked at the effects of individual discrete traps in the tunnel oxide for 30nm NAND flash. "Looking at the threshold voltage over time, you can actually see the threshold voltage change in discrete quantized steps. They've analyzed this and determined these are individual traps in the device that are trapping and detrapping. This will have an impact on future flash technologies where single electron and defects become increasingly important," Slayman said.

In a second paper on resistive RAM, authors are from Minatec and coauthors from the Center for Semicon-

**FIGURE 3.** 22nm BTI is comparable to 32nm. NMOS is significantly improved due to gate optimization and WF scaling.

ductor Components at the University of Campinas Brazil and the department of electrical engineering at Stanford studied the retention time -- the ability of a resistive RAM device to maintain its resistance state. The RAM consists of two metal electrodes and a hafnium oxide between those, where the hafnium oxide acts as a variable resistor. The authors look at the use of different metal materials. In one case they use platinum for the electrode, and in a second example they use a TiN-Ti to sandwich the hafnium oxide. They showed that the Pt/ Pt electrode device loses its on-state resistance sooner than the TiN/Ti device. "They attribute the phenomenon to oxygen interstitials in the HfO<sub>2</sub>, and TiN-Ti's ability to basically getter those interstitials and pin them at the surface," Slayman said. This is illustrated in **FIGURE 1.**

A third paper on memory focuses on flash, specifically erratic bit classification in flash devices used in automotive applications. The authors studied error correction code and redundant addresses, both of which are widely used in flash as well as SRAM and DRAM memory. "What's new with this paper is the authors have classified these erratic or bad bits," Slayman said. FIGURE 2 shows three different types of erratic bits and their behavior over time. "In the first case, they are looking at the read current of one type of erratic bit where it will periodically spike to a higher read current. Then there's another type of erratic bit they observed where about half the time, it's in a low read current state and the other half of the time it's in a high read current state. Then they have a third class of erratic bits where it's just going back and forth constantly between the high read state and the low read state," Slaymain explained.

Typically, redundant address repair would be used

www.solid-state.com

SOLID STATE TECHNOLOGY MARCH 2013

19

#### RELIABILITY

when these bad bits are created, after so many readwrite cycles, but that can be an expensive fix. "For a certain class of bad bits -- such as the erratic bits on the top of Fig. 3, that are most of the time good and only infrequently bad -- don't bother using redundant address, just use your error correction code and that's sufficient," Slayman said. "Save your redundant addresses for the really bad erratic bits." The authors demonstrated that they can save 35% of their redundancy space by using this classification scheme.

#### **FinFET concerns**

At the device level, Giuseppe Larosa, IRPS Technical Program Chair, said the focus in squarely on FinFETs. "For future nodes, 14nm and down to 10nm, FinFETs will be the device design of choice," he said.

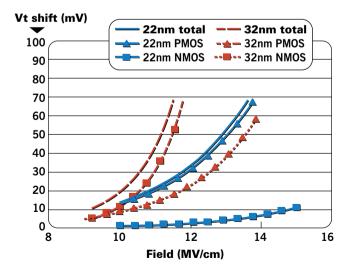

Larosa said one of the key questions people ask is how BTI is actually scaling when we go to finFETs. "Key information is coming from Intel, suggesting that NBTI seems to be an issue because it's increasing with finFET scaling." At IRPS, Intel will present a comparison of 32nm planar technology to a 22nm finFET technology, as shown in **FIGURE 3** (32 in red and 22nm in blue). "You can see they can manage to really reduce the PBTI but the NBTI is actually getting worse with scaling," he said.

The second item on the list for finFETs is selfheating. "Self-heating is always there," said Larosa. "Anytime you drive current through a channel you produce some self-heating. But if you have a bulk technology, the self-heating will just move away down into the bulk. But in finFETs, because it's a threedimensional structure, this self-heating is a bottleneck in scaling down."

Another Intel paper talks about the effect of selfheating in accelerating aging, not only at the level of the device in terms of finFETS, but also in terms of metal wires that are sitting on top of the finFET. "You may have some impact on electromigration in the metal wires. You can have enhanced electromigration simply because the self-heating of the finFET can locally increase the temperature in the metal wires above," Larosa explained. "A key issue here is how to calibrate the self-heating to make sure that you have a good understanding of the local temperature of the structure, and then how to take that into account in

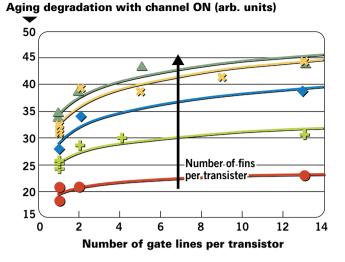

**FIGURE 4.** Self-heat manifests as a sensitivity to the fin or gate count in switching aging degradation. Here, switching conditions are accelerated to enhance the sensitivity.

your models that predict end-of-life aging, specifically finFETs and metal lines," he said.

**FIGURE 4** shows how self-heating at the device level is affecting aging of a given FET: It's a function of the number of fins and the number of active lines per transistor. "It looks like through optimization of the gate stack with appropriate oxide scaling and metal gate work function tuning and so on, you can achieve reliability similar to previous nodes," Larosa said.

Another reliability concern to be discussed at IRPS: High-k dielectrics. "There are two aspects of high k dielectrics that people have to face," Larosa said. "BTI is again a concern with continued scaling. Contrary to nitride oxides, high-k bring a higher sensitivity to the NFET devices to PBTI. This is mostly due to the fact that the high-k material can be sensitive to electron trap activation or generation, producing PBTI effects that you will not see in standard nitride oxide technologies."

At IRPS, GLOBALFOUNDRIES will present the first large-scale stochastic BTI (particularly PBTI) study in metal gate/high-k technology confirming fundamental BTI area scaling trends derived from conventional  $SiO_2$ technologies, and IBM will report on TDDB in high-k, and how it will lead to more accurate models. "Without this model you cannot be confident in predicting end of life, and having this type of simulation can help in making a projection that will be relevant for product level of circuit level reliability," Larosa said.  $\blacklozenge$

www.solid-state.com

#### **INSPECTION**

## Exploring the dark side

**REBECCA HOWLAND, Ph.D.** and **MARC FILZEN**, KLA-Tencor, Milpitas, CA.

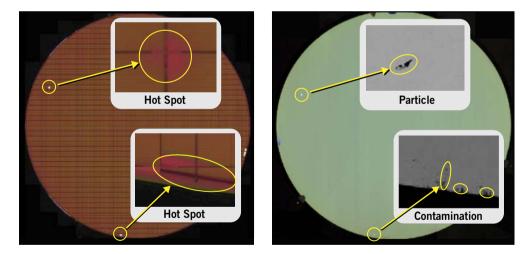

A look at the impact of back side particles on front side defectivity.

hen a 300mm wafer is vacuum mounted onto the chuck of a scanner, it needs to be flat to within about 16nm over a typical exposure field, for wafers intended for 28nm node devices.[1] A particle as small as three microns in diameter, attached to the back side of the wafer—the dark side, if you will—can cause yield-limiting defects on the front side of the wafer during patterning of a critical layer. The impact of back side particles on front side defec-

opens from the defective feature to its neighbors.

A particle on the back side of the wafer may remain attached to the wafer, affecting the yield of only that wafer, or it may be transferred to the scanner chuck, where it will create similar defects on the next wafer or wafers that pass through the scanner.

At larger design nodes, back side defects were not much of an issue. The scanner's depth of focus was sufficient to accommodate a few microns of localized change in the height of the top surface of the wafer. At

tivity becomes even more challenging as design rules decrease.

Studies have shown that a relatively incompressible particle three microns in diameter or an equivalent cluster of smaller particles, trapped between the chuck and the back surface of the wafer, can transmit a localized height change on the order of 50nm to the front side of the wafer.[2] With the scanner's depthof-focus reduced to 50nm for the 28nm node, the same back side particle or cluster can move the top

FIGURE 1. Caption: Correlation between front side (left) and back side (right) results is evident in the wafer defect maps and patch images

wafer surface outside the sweet spot for patterning. The CD of the features may broaden locally; the features may be misshapen. The result is often called a *defocus defect* or a hotspot (FIGURE 1). These defects are frequently yieldlimiting because they will result in electrical shorts or

larger design nodes, then, inspection of the back side of the wafer was performed only after the lithography track and only if defects were found on successive wafers, indicating that the offending particle remained on the scanner chuck, poised to continue to create

REBECCA HOWLAND, Ph.D., is a senior director in the corporate group, and MARC FILZEN is a product marketing manager in the SWIFT division at KLA-Tencor.

www.solid-state.com

SOLID STATE TECHNOLOGY **MARCH 2013** 21

INSPECTION

vield issues for future wafers. In this case corrective measures were undertaken on the track to remove any suspected contamination. The track was re-qualified by sending another set of wafers through it and looking for defectivity at the front side locus of the suspected back side particle. This reactive approach was economically feasible for most devices throughout volume production of 32nm devices.

At the 28nm node, however, lithography process window requirements are such that controlling back side particles requires a more proactive approach. Advanced fabs now tend to inspect the wafer back side before the wafer enters the scanner, heading off any potential yield loss. Scanner manufacturers are also encouraging extensive inspection of the back side of wafers before they enter the track. As we see what lithography techniques unfold for the 16nm, 10nm nodes and beyond, it's entirely possible that 100% wafer sampling will become the best-known method.

As with inspection of the front side of the wafer,

sensitivity to defects of interest (DOI) and the ability to discriminate between DOI and nuisance events are important. Even though particles need to be two to three microns in diameter before they have an impact on front side defectivity, the inspection system ought to be able to detect submicron defects, since small defects can agglomerate to form clusters of critical size. Submicron sensitivity is beneficial for identifying process tool issues based on the spatial signature of the defects—while high-resolution back side review enables imaging of localized defects, so that appropriate corrective actions can be taken to protect yield. Submicron sensitivity also serves to extend the tool's applicability for nodes beyond 28nm. 🔶

#### **References**

- 1. Assuming 193nm exposure wavelength, NA = 1.35 and K2 = 0.5, then depth of field = 50nm. Normally 30% of the DOF is budgeted for wafer flatness.

- 2. Internal studies at KLA-Tencor.

**MARCH 2013** SOLID STATE TECHNOLOGY 22

СМР

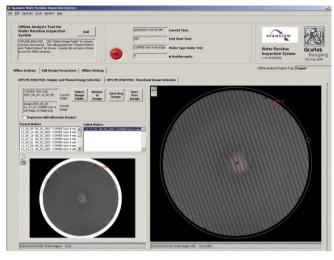

## Automatic wafer inspection system replaces eyeballs with cameras

CHRISTOPHER ERIC BRANNON, Texas Instruments, Inc., Dallas, TX

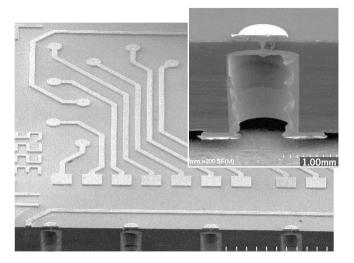

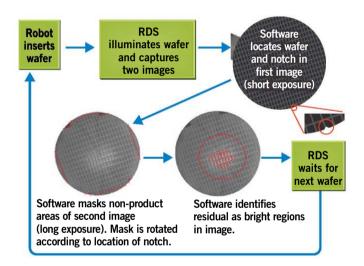

A fully automated RDS inspection system that replaces human inspectors is a game changer.

he chemical-mechanical polishing (CMP) process in the fabrication of silicon wafers is exceedingly labor intense. As a result, automating a critical aspect of CMP - namely, the physical inspection of wafers for metal residue following CMP - cannot only improve CMP cycle times, but it also can be integrated into a quality control system that improves wafer yields and maintains those yields at a high level.

The typical method for inspecting

wafers as they emerge from CMP has involved a technician visually examining one wafer at a time as it is raised on an H-bar wafer elevation tool (FIGURE 1). The inspector would try to detect metal residue left on the wafer following an incomplete polishing process. If undetected, this metal residue can damage the devices made from the silicon. In other words, undetected metal residue can cause wafer and chip yields to plummet.

Of course, manual inspection processes have inherent limitations. Technicians may not perform a thorough inspection of the entire wafer or miniscule remnants of residue may elude human vision. Microscopes are also difficult to employ at today's technology nodes. And, expanding wafer sizes, from

FIGURE 1. Manually inspecting a wafer on an H-bar tool.

200mm to 300mm, doubles the area that must be inspected, increasing the chances that residue somewhere on the wafer will elude the human eve.

As a result of this situation, research was begun to develop a low-cost, single-step automated process that would inspect 100 percent of all wafers after the CMP polishing process. Improved yields would be achieved by detecting residue more effectively and by incorporating the results of the inspection into a closed-

loop feedback system that would control and dynamically fine tune the CMP process. At the heart of this automated residue detection system (RDS) would be

a high-resolution imaging capture and compare process.

**Capturing the** golden wafer First the RDS's camera must scan a

FIGURE 2. A grayscale image of a wafer.

CHRISTOPHER ERIC BRANNON, is a DMOS5 Copper CMP Manufacturing Engineer Texas Instruments, Inc., Dallas, TX.

www.solid-state.com

СМР

fully polished and fully metalized wafer. This image will become the golden wafer or reference wafer for subsequent inspections. A grayscale map of the golden wafer is stored and reference values are associated with various characteristics of the wafer, such as the thickness variations in metals and dielectrics, the number and orientation of detectors, edge exclusions and the metals detected, usually tungsten or copper.

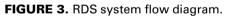

With the image of the golden wafer stored, the RDS can begin inspecting production wafers. Each production wafer is scanned and a grayscale image captured (**FIGURE 2**) which is compared to the golden wafer. The differences in the gray levels between the image of the production and that of the golden wafer will reveal any residual metal remaining on the production wafer (**FIGURE 3**).

As mentioned, the data gathered by the RDS following CMP polishing can be fed back into a control mechanism that can adjust the parameters of the CMP process itself and thereby improve its effectiveness. This is best illustrated by citing several brief case studies:

#### **Erroneous CMP recipe**

ECHNOLOGY

A set of 25 wafers was inspected with the RDS tool and residual metal was detected on every wafer (FIGURE 4). Manual inspection with a microscope confirmed the presence of the metal residue.

The consistent location of the residue and the fact that it was present on each wafer indicated a systemic

**FIGURE 4.** The RDS detected residual metal on the wafer.

fault of some sort. This knowledge assisted in the troubleshooting exercise that ensued. Eventually, it was determined that the software controlling the CMP process had employed an incorrect polish recipe with shorter polish times and other erroneous process parameters.

#### **Flow problems**

In another case, the polish used in the CMP process began to exhibit random or non-linear behavior result patterns. Specifically, some, but not all, of the wafers inspected by RDS had a considerable amount of residual metal at the center of the wafer (**FIGURE 5**). The erratic polishing patterns led to an examination of the CMP slurry flow on the polishing pad. It was concluded that the flow of slurry to the pad was interrupted intermittently; hence, the erratic behavior patterns of the polishing process.

#### **Operator error**

Subsequent to the polishing of a batch of wafers, inspection by the RDS system revealed that five wafers were inexplicably left unpolished. Fortunately, the relatively fast cycle time of RDS allows for 100 percent inspection of all wafers. Eventually, the mysterious five unpolished wafers were attributed to operator error. Had RDS not been capable of inspecting every wafer, the five unpolished wafers might have been missed completely.

Continued on page 32

www.solid-state.com

Next Page

#### RELIABILITY

## Insights into low frequency noise in high-mobility transistors

EDDY SIMOEN, imec, Leuven, Belgium

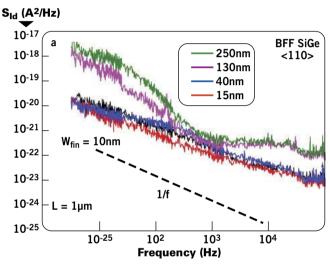

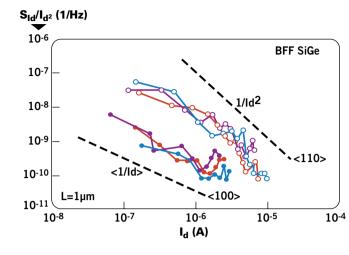

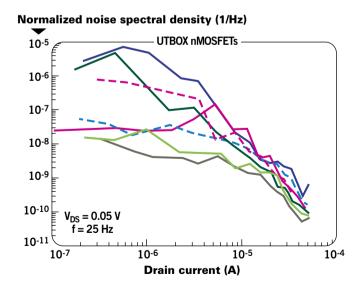

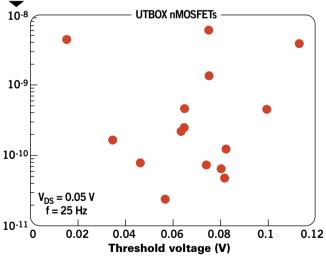

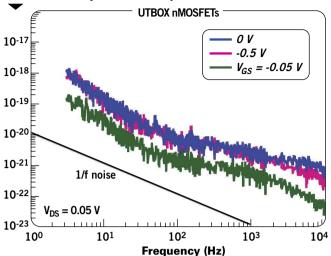

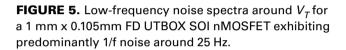

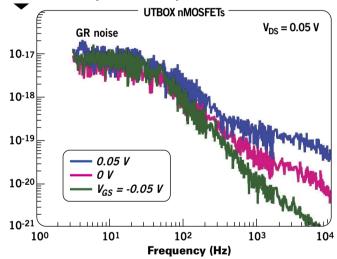

The impact of high-mobility channel materials and novel device architectures on the low-frequency noise behavior of 22nm and below CMOS transistors is reviewed.