MARCH 2014

Solid State TECHNOLOGY Insights for Electronics Manufacturing

SiC Power Device Advantages P. 16

Improving Efficiency in Semiconductor R&D P. 21

FinFETs on SOI P. 27

## Reducing Polymer Defects in Metal

P. 12

M E D M

www.solid-state.com

## Who Will You CONNECT with at The ConFab?

Gain access to an audience of <u>pre-qualified</u> purchasing decision makers and influencers from the world's leading semiconductor and device manufacturers, OEMs, OSATs and fabless companies.

Influential Attendees. World-Class Conference. Unparalled Networking Opportunities. Your Opportunity.

**BOOK TODAY** to reserve your spot at The ConFab. The event features a wide variety of options and **special offers for first-time participants** from equipment, material and service suppliers, but availability is extremely limited. For more information, please contact Sabrina Straub at sstraub@extensionmedia.com.

Conference & Networking Event June 22-25, 2014 Encore at the Wynn, Las Vegas

Presented by:

## CONNECT.COLLABORATE.CREATE.

Owned & Produced by

Extension M E D I A www.TheConFab.com

# Solid State

MARCH 2014 VOL. 57 NO. 2

On the bonnie banks: An aerial view of TI's Greenock, Scotland facility, the work home to the authors of this month's cover story.

### FEATURES

#### **ETCH** | Solutions for polymer defects at plasma metal etch

Equipment Engineers at Texas Instruments' GFAB facility in Greenock, Scotland have developed a method for polymer defect reduction in plasma metal etch systems that increases the preventive maintenance interval and correspondingly reduces associated pm costs. *Allan O'Brien and Robert Adams, Texas Instruments, Greenock, Scotland*

**POWER ELECTRONICS** SiC power device advantages enhance power conversion systems Compared to silicon, SiC has ten times the dielectric breakdown field strength, three times the bandgap and three times the thermal conductivity. *Taku Hamaguchi, ROHM Semiconductor, Santa Clara, CA*.

#### BUSINESS Cashing in with chips: Improving efficiency in semiconductor R&D

Companies have achieved a 30% or greater increase in R&D efficiency—as measured by the return on invested R&D dollars—through the implementation of proper planning processes and the better allocation of resources. *Scott Jones, Alix Partners, San Francisco, CA*

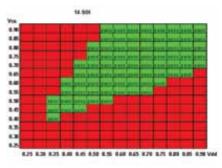

#### SILICON ON INSULATOR FinFET on SOI: Potential becomes reality

By using SOI-based FinFET technology, the need for doping in the body has been effectively minimized, resulting in excellent matching characteristics in the undoped DRAM transfer device, and truly remarkable minimum operating voltage in the SRAM. *Terence B. Hook, I. Ahsan, A. Kumar, K. Mcstay, E. Nowak, S. Saroop, C. Schiller and G. Starkey, IBM Semiconductor Research and Development Center, Burlington, VT.*

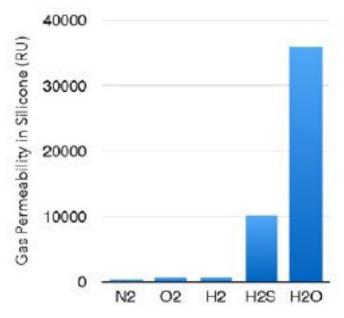

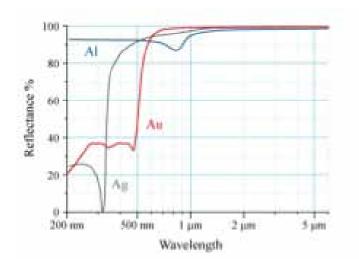

#### LED MANUFACTURING Ag plating in HBLED packaging improves reflectivity and lowers costs

Various types of Ag plating technology along with the advantages and limitations of each plating approach are discussed. Potential issues with Ag as a packaging metallization, and some of the steps that need to be taken to mitigate risks, are also reviewed. *Jonathan Harris, President, CMC Laboratories, Inc., Tempe, AZ*

#### **SEMIMD** 3D NAND: To 10nm and beyond

The transition to 3D NAND is inevitable, but there is still plenty to be squeezed from 2D NAND technology. An Applied Materials-sponsored panel at IEDM discussed where the industry is today and where it's headed. *Sara Ver-Bruggen, contributing editor*

#### COLUMNS

- 3 Editorial Mission accomplished. Now what?, Pete Singer, Editor-in-Chief

- 10 Packaging | IMAPS wrap-up, Phil Garrou, Contributing Editor

- **11 Semiconductors** No technical barriers seen for 450mm, *Pete Singer, Editor-in-Chief*

- **40** Industry Forum Trends shaping modern product delivery, *Eric Linquist Founder and CEO*, Jama Software

#### DEPARTMENTS

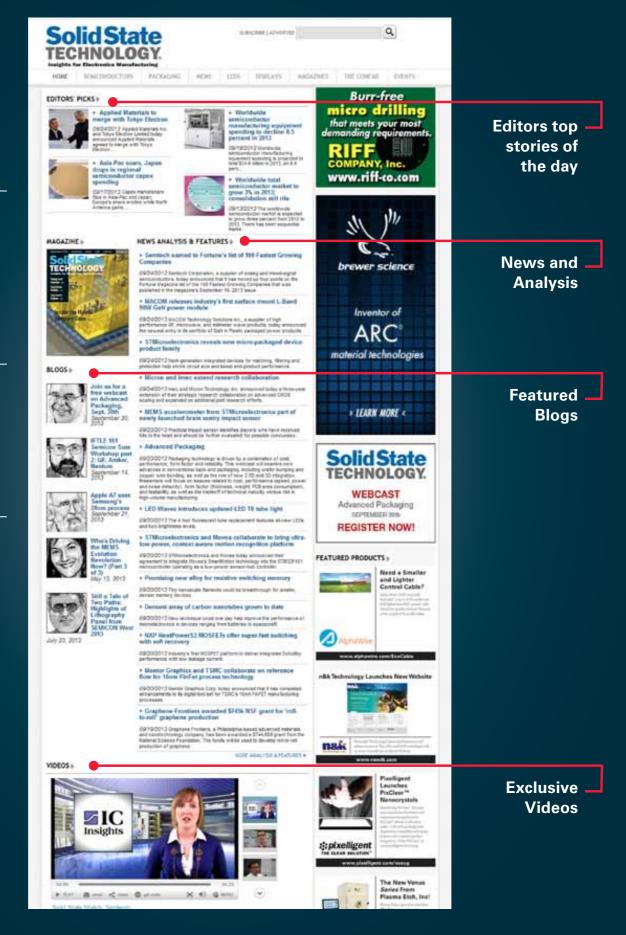

- 2 Web Exclusives

- 4 News

- 39 Ad Index

## online@www.solid-state.com

### **Web Exclusives**

### The need for high sigma yield

Dr. Bruce McGaughy, Chief Technology Officer and Senior Vice President of Engineering, ProPlus Design Solutions, Inc., says the move to state-of-the-art 28nm/20nm planar CMOS and 16nm FinFET technologies present greater challenges to yield than any previous generation.

http://bit.ly/1hjln7H

## The most expensive SRAM in the world -2.0

ISSCC 2014 illuminated the impeding problem – embedded SRAM scaling. Embedded SRAM scaling is broken and, with it, Moore's Law. Zvi Or-Bach, President and CEO of MonolithIC, and Ben Louie, Zeno Semiconductors share insights from ISSCC 2014. http://bit.ly/1dSDmBH

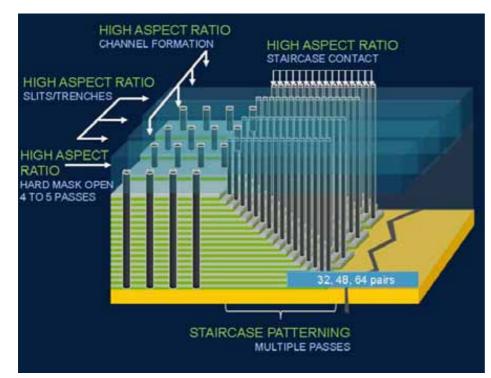

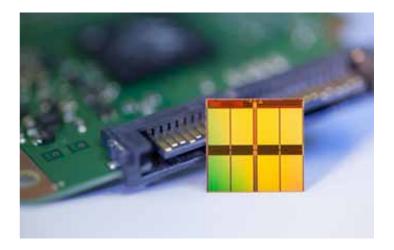

# Experts at the Table: Commercial potential and production challenges for 3D NAND memory technology

The last six months have seen several developments concerning 3D memory concepts moving into production, from companies such as Samsung, Micron, Toshiba and Sandisk. What follows are excerpts from a roundtable discussion with SemiMD, Samsung Electronics (SE) in South Korea, which has begun production of its proprietary 3D NAND technology, Bradley Howard, Vice President of Advanced Technology Group, Etch Business Unit, at Applied Materials and Jim Handy from Objective Analysis, which specializes in coverage of the memory industry. From SemiMD **http://bit.ly/J2FZUR**

### Tune in to the Solid State Watch

Get caught up on industry headlines each with Solid State Technology's exclusive newscast.

http://bcove.me/fnppomc7

### Insights from the Leading Edge

Dr. Phil Garrou finishes up his look at the IEEE 3DIC meeting with a review of presentations by Tohoku University, Fujistu, ASE and RTI.

http://bit.ly/1k60iOG

#### If you fear change, ECO fill can help

Jeff Wilson of Mentor Graphics describes how an effective ECO fill strategy must be accurate and fast, concentrating only on the portion of the design affected by the ECO. By removing and replacing only the fill in that area, and re-verifying timing only in the affected area, we can reduce runtime, manage file size, and minimize timing impacts. By restricting the ECO fill operation to only the same locations where actual mask-making changes occur, we can limit the size of the region that must be evaluated for errors, edited, and refilled. http://bit.ly/1ne56Dq

## Is the chip industry as important as we think? Depends on whom you ask

Vivek Bakshi asks the question: "Are we as leading-edge industry making a difference in the world?"

#### http://bit.ly/1dtqBZH

### Exploring the MEMS-enabled life

Munich, Germany is one of Karen Lightman's favorite cities in the world. If you agree or if you've never been there, she has the perfect opportunity for you to join her: MEMS Industry Group's (MIG's) MEMS Executive Congress Europe 2014 will be held at the beautiful Sofitel Hotel Bayerpost on March 10-11. http://bit.ly/1ewpCs7

### editorial

## Mission accomplished. Now what?

In the late '80s and '90s, when our magazine staff gathered for dinner we often made a toast: "Here's to chip silicon!" I really believed (and still do) that making electronics more affordable would increase their use and make our lives better and the world a better place to be.

I haven't toasted to cheap silicon for a while. Why? Because that mission has been accomplished.

I haven't toasted to cheap silicon for a while. Why? Because that mission has been accomplished.

At SEMI's ISS, Paul Farrar, manager of the G450C consortium put the industry progress over the last 40+ years in perspective. "1 Megabyte of memory in 1970 was \$750,000. It was sold as an IBM add-on," he said. "The great technology was made of 57mm wafers, five masking levels, and one level of metal. Today, it's is less than a penny. That is a 100 million X improvement."

Of course, most people would like to see this trend continue, but it's highly unlikely that we'll see such dramatic progress. Scaling is getting too expensive. The transition to 450mm looks feasible from a technical standpoint (see my column on pg. 10) but it's not yet clear if it will be less expensive than 300mm, particularly when you factor in 450mm lithography.

So if the scaling mission is accomplished, what's next? There's exploding interest in the "Internet of Things" where almost everything is tagged and connected. That will require some big upgrades in the server/network infrastructure, but that can be done with existing technology. It will also require inexpensive sensors and wireless communication. By some estimates, the technology to achieve that is not ready. We need about a 10X improvement in price/performance. Ditto for wearable electronics and a whole host of applications in medical, automotive and the smart grid.

In the future, perhaps electronics will be printed like potato chip bags on roll-to-roll machines with ink-jet-like deposition of materials. Perhaps tiny MEMS with integrated sensors, thin-film batteries, energy harvesting, microprocessors and other functions will be produced for less than a penny. Perhaps everyone will have inexpensive body area networks embedded in their clothing that constantly monitor their health.

It's all possible, but it will take some innovation in processing equipment and materials.

-Pete Singer, Editor-in-Chief

## Solid State

John Blyler, Vice President, Chief Content Officer Ph: 503.614.1082, jblyler@extensionmedia.com

Pete Singer, Editor-in-Chief Ph: 978.470.1806, psinger@extensionmedia.com

Shannon Davis, Editor, Digital Media Ph: 603.547.5309

sdavis@extensionmedia.com

Phil Garrou, Contributing Editor Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design CREATIVE/PRODUCTION/ONLINE Spryte Heithecker, Production Manager Yishain Yao, Media Coordinator Nicky Jacobson, Senior Graphic Designer Jacob Ewing, Graphic Designer Slava Dotsenko, Senior Web Developer

MARKETING/CIRCULATION Jenna Johnson, jjohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

**Clair Bright**, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, Business Development msterling@extensionmedia.com

John Blyler, Vice President and Chief Content Officer jblyler@extensionmedia.com For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2014 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107 Please send news articles to sdavis@extensionmedia.com

#### worldnews

EUROPEGLOBALFOUNDRIESand Fraunhofer Institute forIntegrated Circuits IIS announcedthe extension of their long-term collaboration, focusingon 40nm and 28nm processes.GLOBALFOUNDRIES will also jointhe European Multi Product WaferProgram EUROPRACTICE.

USA | MACOM acquired Nitronex, LLC.

ASIA SPTS Technologies announced the opening of a new office in Panyo, Korea.

**USA** | **Soraa** announced the world's most efficient LEDs, using third generation GaN-on-GaN LEDs.

ASIA | International Rectifier opened a new ultra-thin wafer processing facility in Singapore.

USA | Epoxy Technology, Inc. and John P. Kummer Group, a distributor of instruments and materials for the microelectronics and related industries, announce the formation of a new specialty adhesive packaging company, Epoxy Technology Europe Ltd.

**EUROPE** | **PLACYD**, an EU funded consortium of industrial and academic collaborators and led by **Arkema** will establish a dedicated material manufacturing facility that allows the production of block copolymers meeting the rigorous standards required for their use in industry as nanolithographic templates. Partners include: **CEA-Leti**, **STMicroelectronics**, **Intel IPLS**, **Mentor Graphics**, **ASML** and other leading EU companies and research organizations.

# news

### IBM continues to evolve: Semiconductor business up for sale; moving into the cloud

The Financial Times (FT) is reporting that IBM Corp is exploring the sale of its semiconductor business and has hired Goldman Sachs to find potential buyers. The FT report continues that another financial option may be to find a partner for a JV to jointly run its semiconductor business.

FT projects that the most likely buyers would be Global Foundries or TSMC since it is likely that these two foundry giants along with Samsung and Intel will be the only players left in advanced chip manufacturing as the cost of 20nm and lower fabs now exceeds \$6B.

This should not come as a shock to readers of SST's IFTLE blog (Insights From the Leading Edge) which reported early rumors of such a sale back in the summer of 2010.

While the semiconductor business has become an increasingly less important part of IBM's operations in recent years as it has expanded in IT software and services, any sale or joint venture would surely have to ensure that IBM still had a guaranteed supply of the advanced chips required for its mainframe and high end server businesses.

GlobalFoundries is the most likely candidate for sale or JV since they are a member of the IBM common platform, have been working with IBM for over a decade and have placed their latest fab (Fab 8) in IBMs back yard in upstate NY.

This report comes two weeks after the announcement that, pending government approval, IBM will sell its low-end server business for \$2.3 billion to Chinese PC maker Lenovo. Some may recall that a decade ago Lenovo bought IBM's ThinkPad PC business for \$1.75B.

This low end server decision was likely driven by the trend for many major corporations to move their IT requirements to "the cloud" with companies such as Amazon web services. With customers having more choices for handling their IT, they will be reluctant to get locked into client-server service contracts with IBM.

In fact IBM has just announced [link] plans to commit over \$1.2B to significantly expand its global cloud footprint. IBM plans to deliver cloud services from 40 data centers worldwide in 15 countries and five continents globally, including North America, South America, Europe, Asia and Australia. IBM will open 15 new centers worldwide adding to the existing global footprint of 13 global data centers from SoftLayer, which it acquired in July of 2013, and 12 from IBM.  $\triangleleft$

By Dr. Phil Garrou, Contributing Editor

### Entegris to acquire ATMI

In a merger that will bring together two key suppliers in the semiconductor industry, Entegris, Inc. and ATMI today announced Entegris will acquire ATMI for approximately \$1.15 billion, or approximately \$850 million net of cash acquired, including the net cash proceeds from the sale of ATMI's LifeSciences business of \$170 million. The companies anticipate closing the transaction in the second guarter of 2014.

"Upon closing, approximately 80 percent of our product sales will be unitdriven and focused on the most rapidly growing and critical areas of the semiconductor fab," said Bertrand Loy, President and CEO of Entegris. "We are excited about the opportunities ahead and look forward to quickly realizing the significant benefits of this transaction for our shareholders, customers and employees."

"Throughout this process, our goal has been to enter into a transaction that not only maximizes shareholder value, but also places our business with the right partner for our valued customers and employees," said Doug Neugold, President and CEO of ATMI. "We are pleased to merge our microelectronics business into Entegris. Entegris' global platform and complementary products represents a great opportunity for ATMI stakeholders, including our shareholders, who will receive an immediate premium for their investment."

ATMI shareholders will receive \$34.00 in cash, without interest or dividends, for each share of ATMI common stock they hold at the time of closing. The price represents a premium of 26.3 percent to ATMI's closing price of \$26.93 on February 3, 2014. Entegris expects to fund the all-cash transaction with a combination of existing cash balances and additional committed debt financing.

Goldman, Sachs & Co. is serving as the exclusive financial advisor, and Ropes & Gray LLP is serving as legal counsel to Entegris. Barclays Capital is serving as the financial advisor and Weil, Gotshal & Manges LLP is serving as legal counsel to ATMI. Goldman Sachs Bank USA has been appointed to act as the lead arranger and bookrunner for the committed financing that has been obtained by Entegris in connection with the merger and the related transactions.

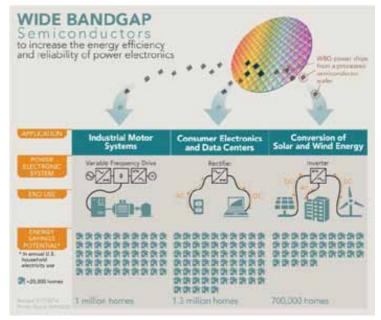

### North Carolina State University to lead research consortium on power electronics

The Obama Administration announced the selection of North Carolina State University to lead a publicprivate manufacturing innovation institute for next generation power electronics. Called the Next Generation Power Electronics Institute, the new consortium will provide shared facilities, equipment and testing to companies from the power electronics industry. focusing on small and medium-sized companies. The 18 companies already committed to the consortium include: ABB, APEI, Avogy, Cree, Delphi, Delta Products, DfR Solutions, Gridbridge, Hesse Mechantronics, II-VI, IQE, John Deere, Monolith Semiconductor, RF Micro Devices, Toshiba International, Transphorm, USCi and Vacon.

The institute, backed by a \$70 million investment from the Department of Energy, will focus on power electronics using wide bandgap (WBG) semiconductors, bringing together over 25 companies, universities and state and federal organizations.

This \$140 million manufacturing hub in Raleigh has the potential to fastforward development of some products by at least a decade," said Greg Scheu, president and CEO of ABB Inc., a Raleigh-based power electronics manufacturer. "We expect that consumers will start to see some low-voltage products, like residential solar, coming out the quickest and within five years. The highpower products like industrial motors and drives and hog-voltage gear will take a few more years to come to market, mainly due to the rigorous reliability testing requirements of the electric utility industry."

Power electronics – such as inverters, transformers and transistors - help control and convert electricity and are playing a growing role in electricity generation, distribution and transmission. According to a study by the Oak Ridge National Laboratory, approximately 30 percent of all power generation today utilizes power electronics between the point of generation and its end use. By 2030, this is expected to jump to 80 percent of generated electricity - supporting greater renewable energy integration and increased grid reliability. WBG semiconductor-based power

electronics will be able to better withstand the power loads and switching frequencies required by next generation utility technologies.

Power electronics that use WBG semiconductors will also be smaller, more efficient and cost less. A WBG semiconductor-based inverter, which switches electricity from direct current to alternating current, could be four times more powerful, half the cost and one-fourth the size and weight of a traditional inverter. At a largerscale, WBG semiconductors could help reduce the size of an 8,000 lbs. substation to 100 lbs. and the size of a suitcase - ultimately helping to lower the cost of electricity and build a stronger, more reliable grid.

WBG semiconductors such as silicon carbide and gallium nitride can operate at higher temperatures and have greater durability and reliability at higher voltages and frequencies.

The state of North Carolina is expected to contribute at least \$10 million to the new consortium, which is expected to help bolster employment in North Carolina, as well as to help focus on manufacturing as a potential source of economic growth.

According to the official statement from the Obama administration, The Next Generation Power Electronics Institute supports President Obama's vision for a full national network of up to 45 manufacturing innovation institutes that help make America a magnet for jobs

and manufacturing and ensure that U.S. workers have the training they need to lead in the global economy.

"I see it this way," said Mr. Scheu, "the president asked the industry to work together and see where we can replace silicon with other semiconductor materials to reduce energy loss - meaning huge energy efficiency - for equipment that can handle higher voltages, higher temperatures and higher frequencies. To me, this is the goal. And this is where the imagination takes off." ◆

### SRC and MIT extend high-resolution lithography capabilities

MIT researchers sponsored by Semiconductor Research Corporation have introduced new directed self-assembly (DSA) techniques that promise to help semiconductor manufacturers develop more advanced and less expensive components.

The MIT study demonstrates that complex patterns of lines, bends and junctions with feature sizes below 20nm can be made by block copolymer self-assembly guided by a greatly simplified template. This study explained how to design the template to achieve a desired pattern.

## **NEWS**cont

Electron-beam lithography was used to produce the template serially, while the block copolymer filled in the rest of the pattern in a parallel process. This hybrid process can be five or more times faster than writing the entire pattern by electron beam lithography.

"We believe our research will help Moore's Law to be continued," said Caroline Ross, MIT professor of Materials Science and Engineering. "To increase the density of transistors in a given area, the pitch of the features in a transistor should be scaled down, but the increasing time and cost of manufacturing such fine and dense features becomes more problematic. Our research suggests a solution to this problem."

Leveraging block copolymer self-assembly to produce dense, high-resolution patterns was proposed and demonstrated several years ago, but there was no systematic way to design templates to achieve a complex block copolymer pattern. The MIT study developed a simple way to design a template to achieve a specific block copolymer

pattern over a large area. Although the work used electron-beam lithography to define the template, other methods such as photolithography with trimming could be used to produce the templates.

Block copolymer lithography is already on the semiconductor industry roadmap as directed self-assembly, but the process is still in its infancy. Although DSA patterning has been demonstrated on 300mm wafers, these early trials used templates fabricated by photolithography with limited resolution and limited control of the feature geometry. The MIT process offers a path to far more complicated geometries using relatively simple templates. Next steps involve the research being shared with semiconductor companies for further studies.

"The demand for computing processors with higher bandwidth and memories of larger capacity continues to grow, but the manufacturing cost of these devices is also increasing as the transistor and associated interconnect dimensions shrink," said Bob Havemann, Director of Nanomanufacturing Sciences at SRC. "Lithography research such as the work completed by the MIT team is critically important as the required feature sizes in semiconductor manufacturing scale below what is achievable with conventional lithography techniques."

## Silicon-germanium chip sets new speed record

A research collaboration consisting of IHP-Innovations for High Performance Microelectronics in Germany and the Georgia Institute of Technology has demonstrated the world's fastest silicon-based device to date. The investigators operated a silicon-germanium (SiGe) transistor at 798 gigahertz (GHz) fMAX, exceeding the previous speed record for silicon-germanium chips by about 200 GHz.

TO LEARN MORE, VISIT WWW.PLASMAETCH.COM OR CALL US TODAY AT 775-883-1336

## **news**cont

Although these operating speeds were achieved at extremely cold temperatures, the research suggests that record speeds at room temperature aren't far off, said professor John D. Cressler, who led the research for Georgia Tech. Information about the research was published in February of 2014, by IEEE Electron Device Letters.

"The transistor we tested was a conservative design, and the results indicate that there is significant potential to achieve similar speeds at room temperature – which would enable potentially world changing progress in high data rate wireless and wired communications, as well as signal processing, imaging, sensing and radar applications," said Cressler, who hold the Schlumberger Chair in electronics in the Georgia Tech School of Electrical and Computer Engineering. "Moreover, I believe that these results also indicate that the goal of breaking the so called 'terahertz barrier' – meaning, achieving terahertz speeds in a robust and manufacturable silicon-germanium transistor – is within reach."

Meanwhile, Cressler added, the tested transistor itself could be practical as is for certain cold-temperature applications. In particular, it could be used in its present form for demanding electronics applications in outer space, where temperatures can be extremely low.

IHP, a research center funded by the German government, designed and fabricated the device, a heterojunction bipolar transistor (HBT) made from a nanoscale SiGe alloy embedded within a silicon transistor. Cressler and his Georgia Tech team, including graduate students Partha S. Chakraborty, Adilson Cordoso and Brian R. Wier, performed the exacting work of analyzing, testing and evaluating the novel transistor. "The record low temperature results show the potential for further increasing the transistor speed toward terahertz (THz) at room temperature. This could help enable applications of Si-based technologies in areas in which compound semiconductor technologies are dominant today. At IHP, B. Heinemann, H. Rücker, and A. Fox supported by the whole technology team working to develop the next THz transistor generation," according to Bernd Tillack, who is leading the technology department at IHP in Frankfurt (Oder), Germany. Silicon, a material used in the manufacture of most modern microchips, is not competitive with other materials when it comes to the extremely high performance levels needed for certain types of emerging wireless and wired communications, signal processing, radar and other applications. Certain highly specialized and costly materials – such as indium phosphide, gallium arsenide and gallium nitride – presently dominate these highly demanding application areas.

But silicon-germanium changes this situation. In SiGe technology, small amounts of germanium are introduced into silicon wafers at the atomic scale during the standard manufacturing process, boosting performance substantially.

The result is cutting-edge silicon germanium devices such as the IHP Microelectronics 800 GHz transistor. Such designs combine SiGe's extremely high performance with silicon's traditional advantages – low cost, high yield, smaller size and high levels of integration and manufacturability – making silicon with added germanium highly competitive with the other materials.

Cressler and his team demonstrated the 800 GHz transistor speed at 4.3 Kelvins (452 degrees below zero, Fahrenheit). This transistor has a breakdown voltage of 1.7 V, a value which is adequate for most intended applications.

The 800 GHz transistor was manufactured using IHP's 130-nanometer BiCMOS process, which has a cost advantage compared with today's highly-scaled CMOS technologies. This 130 nm SiGe BiCMOS process is offered by IHP in a multi-project wafer foundry service.

The Georgia Tech team used liquid helium to achieve the extremely low cryogenic temperatures of 4.3 Kelvins in achieving the observed 798 GHz speeds.

"When we tested the IHP 800 GHz transistor at room temperature during our evaluation, it operated at 417 GHz," Cressler said. "At that speed, it's already faster than 98 percent of all the transistors available right now." ◆

## Global semiconductor industry posts highest-ever January sales

The Semiconductor Industry Association announced that worldwide sales of semiconductors reached \$26.28 billion for the month of January 2014, an increase of 8.8 percent from January 2013 when

## **news**cont

sales were \$24.15 billion, marking the industry's highest-ever January sales total and the largest year-toyear increase in nearly three years. Global sales from January 2014 were 1.4 percent lower than the December 2013 total of \$26.65 billion, reflecting normal seasonal trends. Regionally, sales in the Americas increased by 17.3 percent compared to last January. All monthly sales numbers are compiled by the World Semiconductor Trade Statistics (WSTS) organization and represent a three-month moving average.

"The global semiconductor industry has built on its record revenues from 2013 with an impressive start to 2014, led largely by continued strength in the Americas market," said Brian Toohey, president and CEO, Semiconductor Industry Association. "Sales in January were up across most regions and nearly all product categories compared to last January, which bodes well for continued growth during the rest of 2014."

Regionally, year-over-year sales increased in the Americas (17.3 percent), Europe (11.3 percent), and Asia Pacific (8.3 percent), but decreased in Japan (-4.7 percent). Sales were flat in Europe compared to the previous month, but decreased slightly in Asia Pacific (-0.6 percent), Japan (-2.3 percent), and the Americas (-3.5 percent). January sales historically are lower than December sales due to seasonal trends. ◆

## reduce soft errors

## Deliver more density on flip chip IC packages without increasing soft errors, using low alpha plating anodes.

Honeywell RadLo $^{\rm m}$  low alpha packaging materials help minimize soft errors and single event upsets by reducing alpha emissions, a significant source

of these problems. Our low alpha plating anodes are used in wafer bumping applications for today's high-performance, high-density devices. We provide Pb and Sn-based plating anodes in various low alpha grades, helping you meet critical alpha emission levels.

Honeywell reliability. Reliable low alpha. In addition to plating anodes, Honeywell RadLo products include plating solution materials and solder feedstock—all backed by our robust supply chain and industry-leading expertise in low alpha refining and metrology.

#### Find out more by visiting us at www.honeywell-radlo.com

Although all statements and information contained herein are believed to be accurate and reliable, they are presented without guarantee or warranty of any kind, express or implied. Information provided herein does not relieve the user from the responsibility of carrying out its own tests and experiments, and the user assumes all risks and liability for use of the information and results obtained. Statements or suggestions concerning the use of materials and processes are made without representation or warranty that any such use is free of patent infringement and are not recommendations to infringe any patent. The user should not assume that all toxicity data and safety measures are indicated herein or that other measures may not be required. ©2014 Honeywell International Inc. All rights reserved.

## IMAPS wrap-up

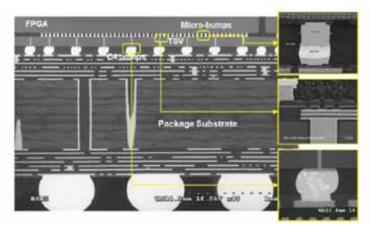

Last summer, at The ConFab, Siliconware (SPIL) announced the instillation of a dual damascene line for fabrication of high density interposers. At the fall IMAPS meeting, Xilinx and SPIL shared results from their 2.5D 28nm FPGA program.

THE SPIL/XILINX 2.5D 28NM FPGA

The high performance FPGA die (manufactured by TSMC) is a 4 slice 28nm chip mounted on a 25 x 31mm 100 $\mu$ m thick Si interposer with 45um pitch microbumps. The interposer is assembled onto a 45 x 45mm organic BGA with 180 $\mu$ m C4 bumps. The figure above shows the structure in cross section. SPIL is manufacturing the interposer and doing the assembly.

SPIL is the first OSAT to propose an OSAT centric model where the interposer is fabricated by the OSAT who then assembles and tests modules made with chips from multiple sources. The impediment to this route in the past has been the lack of OSAT capability to fabricate the fine pitch interposers, which require dual damascene processing capability, which until now was only available in the foundries. SPIL has now announced the equipment for fine pitch interposer capability (>2 layers, 0.4-3 $\mu$ m metal line width and 0.5 $\mu$ m TSV ) has been purchased and is in place.

Nanyang University and IME also presented at

### Packaging

IMAPS. They reported how copper TSVs exert thermomechanical stress on silicon due

**Dr. Phil Garrou,** Contributing Editor

to the CTE mismatch. This stress can result in variability of the device mobility and

mechanical reliability issues. This can be alleviated by using an oxide liner that has a lower elastic modulus such as some of the "low-k" dielectric materials (e.g., Black Diamond). This would reduce the keep out zone and in addition such materials will lower the parasitic capacitance of the circuit.

These Singapore institutions looked at the use of low-k carbon doped oxides to serve as a more compliant layer TSV insulator layer due to its lower modulus (7.2 GPa vs plasma enhanced TEOS with modulus of 75GPa). The FEA analysis shown below indicates that the low-K materials "should" lower the stress exerted by the Cu TSV on the silicon. Micro raman spectroscopy on samples verifies that the use of a low-k liner results in less compressive stress exerted by the Cu TSV on the silicon between the TSV.

As a side note, I saw no discussion of mechanical reliability comparisons. Since low-k is known for being very fragile, I wonder whether the TSV stress will fracture the low-k material which would show up as less stress on the silicon?

Also at IMAPS, Canon, normally associated with front end (FE) lithography addressed "Lithography Process Optimization for 3D and 2.5D Applications." Canon has developed the FPA-5510iV and FPA-5510iZ TSA steppers to support high density processes and to support implementation of 2.5 & 3D technology.

In a typical backside manufacturing process, patterned wafers are bonded face down to a support wafer before being ground and thinned. The bonding and thinning process causes shape distortion in the wafer. Downstream processes require lithography that produces patterns that can overlay such distortions with high accuracy. These systems also employ vacuum assist functions to compensate for large wafer warpage. ◆

## No technical barriers seen for 450mm

Paul Farrar, general manager of the G450C consortium, said early work has demonstrated good results and that he sees no real barriers to implementing 450mm wafers from a technical standpoint. Speaking at the SEMI ISS meeting in January, Farrar showed impressive results from, etch, CVD, PVD, CMP, furnaces, electroplating, wet cleans and lithography processes and said the inspection/metrology tools were in place to measure results. "I don't believe we will find fundamental technology limiters," he said. "But we will have to keep working to find ways to maximize the efficiency." Gaining such efficiencies are critical in order to meet the cost-saving goals of the program. "In the end, if this isn't cheaper, no one is going to do it," he said.

G450C is a consortium based at the CNSE campus in Albany, NY. It is financed by Intel, TSMC, Samsung, IBM, GLOBALFOUNDRIES, and New York State (CNSE). "Our job is to make it as easy as possible to innovation and be collaborative between the semiconductor makers and our key friends in the industry who enable the 450 work to be done in an economic way," Farrar said.

At the end of 2013, G450C at 34 tools delivered to its 50,000ft2 fab in Albany, with another 7 tools in place at partner's facilities. "The FOUPS are going, the overhead transport is well underway and some of the cleanroom is actually starting to look like a cleanroom," Farrar said.

Farrar started with etch results, saying they were "starting to see some pretty good data – 3 sigma at about 2%. Yes, there's still some work to get to the very edge of the wafer but relatively good progress

### Semiconductors

and good jobs on gas delivery, etc.

He showed good results with both oxide

and silicon nitride CVD, with close to 1.5mm edge exclusion. "It's very representation data from early in the program," Farrar said, noting that they were starting to pattern some of the more complex oxides.

He said the goal for PVD was to demonstrate better than

5% uniformity. "We know we have step coverage challenges for both the 10 and 7nm nodes. There's tremendous work going on in the injection rings for gases, high density plasmas from multiple RF sources, but again some progress to me made but pretty good data for right out of the chute," he said.

CMP results demonstrated repeatability less than 4%. "Very good job done by our suppliers," Farrar said. Farrar described data from furnaces as reasonably good. "We still need to do more characterization at what I call the micro level," he said. "We see some hot spots on the edge, but we're starting to work on those." Also "pretty good data" from electrochemical plating (ECP) of copper. "Well done here," Farrar said. "The challenge is thermal and pattern loading effects, and gap fill."

More of the same with wet cleans. "We're starting to see some pretty good particle data. We're cleaning wafers relatively well. We are seeing a few things like what I would call micro-metallic contamination that can grow some things so we're still working on that. But from a particle removal standpoint, pretty good unit process work," Farrar said.

Farrar acknowledged that lithography remained as one of the biggest challenges in the 450mm transition, but showed good results from directed self assembly across a 450mm wafer, and said the consortium had a very strong partnership with Nikon. "We're working with them and we've seen some tremendous progress at their factory," he said. "I'm fully confident that we'll have capability by July to run patterned wafers. Immersion is going to be the workhorse. I think that's a key enabler to get to 450mm." He said the industry would have to see how the economics of EUV played out later in time. "I don't think it's going to be early in time," he said. ◆

**Pete Singer,** Editor-in-Chief

www.solid-state.com

# Solutions for polymer defects at plasma metal etch

Equipment Engineers at Texas Instruments' GFAB facility in Greenock, Scotland have developed a method for polymer defect reduction in plasma metal etch systems that increases the preventive maintenance interval and correspondingly reduces associated PM costs.

#### ALLAN O'BRIEN and ROBERT ADAMS, Texas Instruments, Greenock, Scotland

he problem of polymer flaking on plasma metal etch systems in wafer fabs is a common long standing issue which impacts three key fab metrics: Fab Yield (PY), Tool Availability (Ao) and Cost of Ownership (CoO). With each occurrence of flaking, there is a risk of reduced PY losses due to short circuits caused by metal bridging. When defects are detected on product lots at post-process inspection at the tool, this induces unplanned maintenance interventions which have an associated Ao and CoO impact.

Our team focused on the equipment related causes for polymer flaking and monitored the performance of the equipment in running consistently between consecutive preventive maintenance (PM) events (sometimes known as PM hit rate) as a figure of merit. We took the view that there is a direct and proportional relationship between PM hit rate and PY, Ao and CoO. However, it is also worth noting that the extent of this problem is dependent not only on equipmentinfluencing factors but also on the processes for which the equipment is used. In this case a typical aluminum with titanium/tungsten barrier structure using a chlorinated chemistry for the aluminum etch and a fluorinated chemistry for the barrier etch. Some plasma metal etch equipment use periodic plasma cleaning in an attempt to minimize polymer

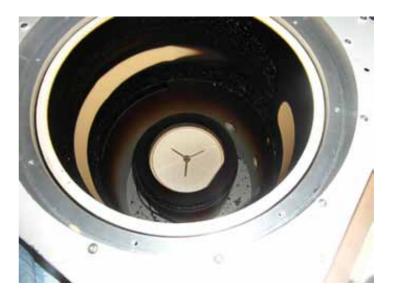

**FIGURE 1.** Typical chamber condition of a system which has failed for polymer defects detected on product post-processing.

flaking. However, this method needs to be tuned to a particular process regime and finding a "one size fits all" has in some cases been found limited in its success.

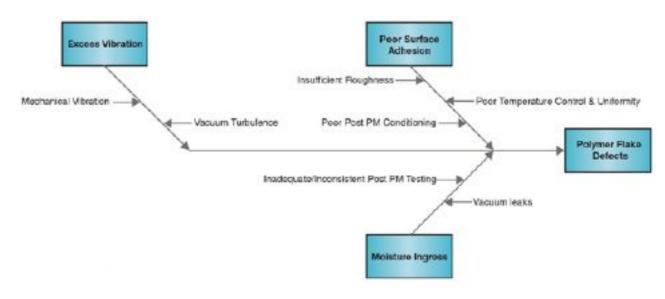

**FIGURE 1** shows the typical chamber condition of a system which has failed for polymer defects detected on product post-processing. The Ishikawa analysis (**FIGURE 2**) of possible equipment-related causes was generated to form an action plan to audit, correct and prevent these causes where applicable and possible.

**ALLAN O'BRIEN** is the Equipment Engineering Section Manager for Ion Implant, Thin Films and Plasma. **ROBERT ADAMS** is GFAB's Plasma Etch Equipment Engineer.

FIGURE 2. Ishikawa analysis.

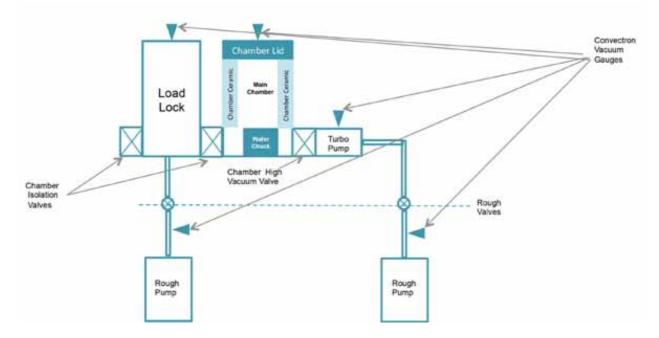

FIGURE 3. Vacuum schematic.

The analysis determined that there were three likely causes: poor surface adhesion, moisture ingress and excess vibration.

#### **Poor surface adhesion**

For poor surface adhesion, three sub-causes were considered, namely insufficient surface roughness (Ra), poor temperature control and poor post PM conditioning practices.

In the case of surface roughness, it was thought that insufficient surface roughness in the chamber surfaces, on which multiple films of process byproducts are deposited, would have a high likelihood of flaking. This is because the stress on these films, if developed across large areas, particularly when subjected to thermal cycles, would cause the films to crack and flake off. This is in contrast to a film whose stress is developed across multiple smaller areas and would have a lower likelihood of cracking and flaking. Chamber ceramics manufactured from aluminum oxide and the chamber lid manufactured from stainless steel were already being cleaned, baked and vacuum packaged by an external contractor. The Ra of these components was measured on the existing clean method and then an alumina bead blast was incorporated into the cleaning process to ascertain if this Ra value could be improved. The results were encouraging in that the surface roughness of chamber parts could effectively be doubled. The chamber ceramic Ra improved from  $1.5-2.5\mu m$  to  $4-5\mu m$  and the chamber lid Ra improved from  $3-4\mu m$  to  $6-9\mu m$ .

On poor temperature control, plasma metal etch equipment systems typically maintain process chamber temperatures between 60 and 70°C using heater cartridges integrated into the chamber body. The emphasis in the study was to ensure the accuracy of this temperature control and more importantly the functionality of all heater cartridges to ensure the desired temperature is uniform across all chamber surfaces. This is to avoid temperature gradients which, when subjected to multiple temperature cycles, would expand and contract at different rates and possibly flake. The investigation uncovered one such open circuit chamber heater cartridge that could have been causing a cool spot.

Poor maintenance practices were also discovered. Specifically, when resist-coated conditioning wafers were ran by equipment technicians after the post-PM leak up rate test failed. This practice was flawed from the beginning, as in effect it trapped moisture between the chamber surfaces, resulting in poor polymer adhesion.

#### **Moisture ingress**

The three influencing factors supposed for moisture ingress were atmospheric exposure duration of the process chamber, vacuum leaks and inadequate/inconsistent post-PM testing.

In the case of atmospheric exposure duration, high variation was noted and was minimized by an update to PM specifications. This stipulates that process chambers should only be exposed to atmosphere when a dedicated technician is available to complete the PM and return the chamber under vacuum in the shortest possible time.

On vacuum leaks, historical assumptions that a leak up rate (or rise over base) check was an adequate measure of vacuum integrity. However, when a helium leakcheck was carried out, several small leaks were discovered on multiple tools. These were corrected and helium leak checking was incorporated into the specified PM procedure to prevent recurrence.

Furthermore, all tools run what is known as a post PM recipe that serves to pump down the chamber to a base pressure then backfill with nitrogen a fixed number of times (known as a pump/purge). This is followed by a leak up rate test. It was discovered that not all tools had the same recipe parameters. So a best known method (BKM) for these parameters was defined and specified.

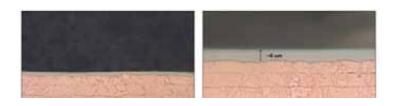

FIGURE 4. Beneficial results can be distinguished in chamber conditions where no discernable flaking is evident.

ETCH

FIGURE 5. PM hit rate.

### Excess vibration

Finally for excess vibration, the two root causes considered were mechanical vibration and vibration form vacuum turbulence.

The first root cause is mechanical vibration from assemblies within the tool that frequently actuate as part of normal operation. Upon further investigation, several tools were found to have high vacuum isolation valves (shown in **FIGURE 3**) with incorrectly adjusted or missing pneumatic dampers. This results in mechanical vibration which could dislodge polymer from the chamber surfaces.

Vacuum turbulence transpires when two isolated chambers are perceived by the tool to be at the same pressure but, in reality, are not. If the respective vacuum gauges (in this case convectron gauges again shown in Fig. 3) are not calibrated precisely, a degree of turbulence occurs when these chambers are exposed to each other until actual equilibrium is established. Similarly, when chambers are roughed down from atmosphere it is important to have a suitable low crossover pressure at which the chamber is exposed to a high vacuum pump. Typical crossover pressures range from 50mTorr to 200mTorr depending on the equipment in question. FIGURE 6. PM interval.

#### **Results and conclusion**

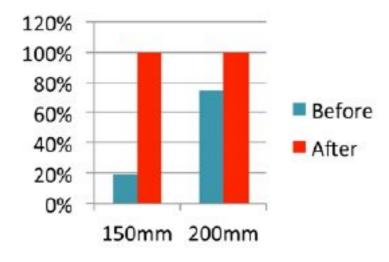

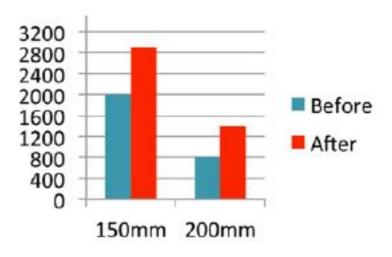

As a result of responding to the aforementioned findings, the beneficial results can be distinguished firstly in the observed chamber conditions as shown in **FIGURE 4** where no discernable flaking was evident. In terms of key fab metrics, PM hit rate was sustained at 100 percent (**FIGURE 5**) which provided confidence to enable a PM interval increase by 45 percent on 150mm tools and 75 percent on 200mm tools (**FIGURE 6**). From a PY perspective, losses from polymer flake defects were eliminated, and with fab cost being a perennial challenge, resulted in a reduction in PM-related CoO by 19 percent. This was realized by eliminating unplanned PMs and increasing PM interval.

For so long, polymer flake defects have been considered and accepted somewhat as a trait associated with plasma metal etch. But we have found that these defects can in fact be significantly mitigated by a thorough approach to analyzing contributory factors in the equipment such as surface adhesion, moisture ingress and vibration. This can help a manufacturer deliver a high yielding process through equipment that is reliable, predictable and has low CoO.  $\blacklozenge$

## SiC power device advantages enhance power conversion systems

TAKU HAMAGUCHI, ROHM Semiconductor, Santa Clara, CA.

Compared to silicon, SiC has ten times the dielectric breakdown field strength, three times the bandgap and three times the thermal conductivity.

hree major factors are influencing the evolution and implementation of next-generation power semiconductor devices: regulatory requirements for ongoing improvements to efficiency in power conversion systems; market demands for lighter, smaller, more cost-effective systems with more integrated features and emerging new applications such as electric vehicles (EVs) and solid state transformers (SSTs). Up until recently, silicon has been the primary material used in power electronics, and although silicon technology continues to improve, it does have certain limitations that must be taken into consideration when designing for the growing list of essential power system requirements.

Device manufacturers have proven during the last ten years that wide bandgap (WBG) materials such as silicon carbide (SiC) and gallium nitride (GaN) provide multiple advantages in the development of next-generation power semiconductor devices. WBG-based devices offer dramatic improvements in performance, operating temperature, power handling efficiency and the ability to deliver new capabilities, which are not possible with silicon-based devices. For this reason, WBG power devices are now considered the future of power semiconductor devices.

The growing popularity of SiC devices can be traced to the availability of all components needed to build complete power systems, namely SiC diodes, switches and modules. This increased availability is the result of an expanded supply chain with a growing number

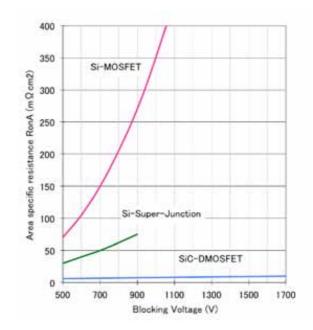

**FIGURE 1.** Comparison of specific on-resistance of Si-MOSFET and SiC-MOSFET.

of suppliers that can offer more economically viable pricing. GaN power devices have been available commercially for a much shorter period of time. Because of this varying state of maturity, SiC and GaN devices have evolved to support separate but complementary functions in different market segments.

SiC is being used for power systems because it has been proven to be more efficient than silicon. The primary advantage of SiC MOSFETs is their very

TAKU HAMAGUCHI is the Director of Technology Marketing at ROHM Semiconductor, Santa Clara, CA.

| Properties                                                  | Si      | 4H-SiC    | GaAs       | GaN       |

|-------------------------------------------------------------|---------|-----------|------------|-----------|

| Crystal Structure                                           | Diamond | Hexagonal | Zincblende | Hexagonal |

| Energy Gap : E <sub>G</sub> (eV)                            | 1.12    | 3.26      | 1.43       | 3.5       |

| Electron Mobility : $\mu_n$ (cm <sup>2</sup> /Vs)           | 1400    | 900       | 8500       | 1250      |

| Hole Mobility : $\mu_{p} (cm^{2}/Vs)$                       | 600     | 100       | 400        | 200       |

| Breakdown Field : E <sub>B</sub> (V/cm) X10 <sup>6</sup>    | 0.3     | 3         | 0.4        | 3         |

| Thermal Conductivity (W/cm°C)                               | 1.5     | 4.9       | 0.5        | 1.3       |

| Saturation Drift Velocity : $v_{s}$ (cm/s) X10 <sup>7</sup> | 1       | 2.7       | 2          | 2.7       |

| Relative Dielectric Constamt : $\varepsilon_{s}$            | 11.8    | 9.7       | 12.8       | 9.5       |

| p, n Control                                                | 0       | 0         | 0          | Δ         |

| Thermal Oxide                                               | 0       | 0         | х          | х         |

**TABLE 1.** Physical Characteristics of major wide bandgap materials.

low switching losses, which increase efficiency and enable higher-frequency operation.

Because the wide bandgap discussion can be a lengthy topic, this article will focus primarily on the advantages of SiC technology in power conversion systems.

#### SiC material advantages

The wide bandgap material properties shown in **TABLE 1** explain why SiC-based power devices can outperform silicon. SiC's breakdown field strength is ten times higher than that of silicon, plus SiC devices can be constructed to withstand the same breakdown with a much smaller drift region. In theory, SiC can reduce the resistance per unit area of the drift layer to 1/300 compared to silicon at the same silicon breakdown voltage.

Compared to silicon, SiC has ten times the dielectric breakdown field strength, three times the bandgap and three times the thermal conductivity. Both p-type and n-type regions, which are necessary to fashion device structures in semiconductor materials, can be formed in SiC. These devices can be produced with a much thinner drift layer and have very high breakdown voltage (600V and up), but provide very low resistance relative to silicon devices. Resistance of high-voltage devices is predominantly determined by the width of the drift region. Compared to silicon, the resistance per unit area of the drift layer can be reduced up to 1/300at the same breakdown voltage with SiC materials. These properties make SiC an optimal power device material that can far exceed the performance of their silicon counterparts.

The first commercial SiC Schottky Barrier Diodes (SBDs) were introduced more than ten years ago and have been designed into many power systems, most notably into power factor correction (PFC) circuits of switch mode power supplies. Technology maturity, performance and dramatic cost reduction due to increasing volume and competition are the main reasons SiC MOSFETs have been adopted in more and more applications. SiC SBDs are currently available with breakdown voltage ratings of 600V-1700V and 1A-60A current ratings. Thus, SiC devices tend to compete with silicon MOSFETs in the 600V-900V range and with IGBTs in the 1kV+ range.

SiC MOSFETs are now experiencing greater demand with power designers for its normally-off operation and voltage controlled device advantages. Plus, SiC MOSFETs offer gate drive simplicity versus that of junction gate field-effect transistors (JFETs) and bipolar junction transistors (BJTs).

High temperature advantages

The high temperature capabilities of SiC power devices have not been fully exploited because of limitations in packaging technology and the associated lower operating temperatures of other components in systems. Currently available products are rated only at 150°C to 175°C, and SiC power modules that use special die bonding technology can operate at 250°C. R&D tests on SiC have shown operation up to 650°C is possible, whereas the upper limit of silicon semiconductors is 300°C.

Additionally, SiC's thermal conductivity is three times higher than that of silicon. These properties contribute to lower cooling needs, making it simpler

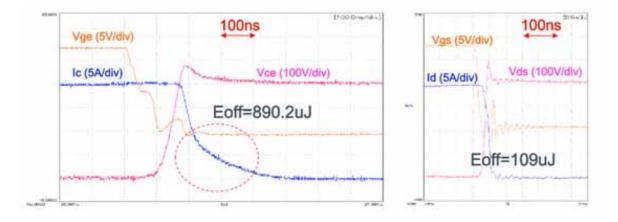

FIGURE 2. Shows 88% reduction of turn-off loss: SiC-MOSFET + SiC SBD v. Si IGBT + FRD.

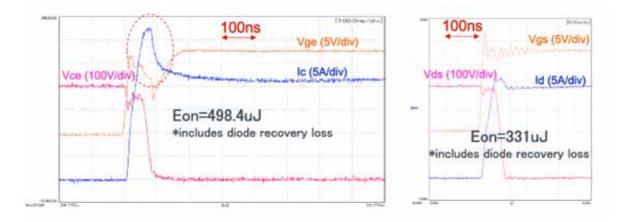

FIGURE 3. 4% reduction of turn-on loss: SiC-MOSFET + SiC SBD v. Si IGBT + FRD.

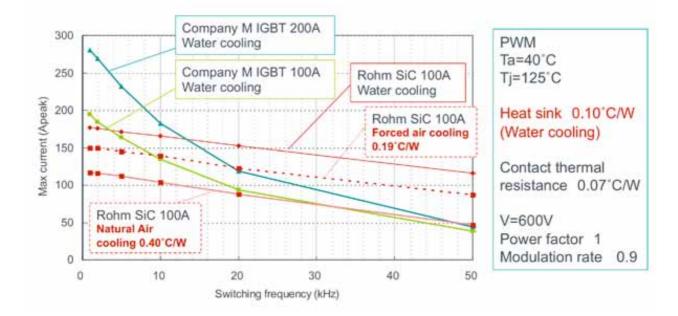

FIGURE 4. Lower switching losses allow 100A SiC module to replace 200A IGBT module.

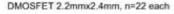

FIGURE 5. (L) Constant Current - Time Dependent Dielectric Breakdown Measurements FIGURE 6. (C) Vth increases due to extended application of positive gate voltage. FIGURE 7. (R) Vth decreases due to extended application of negative gate voltage.

to cool SiC components. This results in supporting thermal systems that can be smaller, lighter and lower cost.

#### Enablers of improved power switches

An ideal power switch is able to carry large current with zero voltage drop in the on-state, blocks high voltage with zero leakage in the off-state and

incurs zero energy loss when switching from off- to on-state and vice versa. In silicon-based devices, it is difficult to combine these desirable but diametrically opposed characteristics, especially at high voltage and current. To address this problem, many designs have employed Insulated Gate Bipolar Transistor (IGBT) devices. With IGBTs, low resistance at high

### Don't miss out on the industry's premier event!

#### www.solid-state.com

breakdown voltage is achieved at the cost of switching performance using minority carriers injected into the drift region to reduce conduction (on-) resistance. Therefore, when the transistor is turned off, it takes time for these carriers to recombine and "dissipate" from the base region, thus increasing switching loss and time.

Contrary to IGBTs, MOSFETs are majority carrier devices so they have no "tail" current. SiC MOSFETs, therefore, can deliver all three requirements of power switch -- high breakdown voltage, low on-resistance and fast switching speed (**FIGURE 1**). For example, compared with silicon IGBTs and fast recovery diodes (FRDs), ROHM combines a SiC MOSFET and SiC SBD in one package, which provides 88 percent lower turn-off loss and 34 percent lower turn-on loss enabling switching frequency in hundreds of kHz range. The improvement in turn-off is due to absence of tail current in the MOSFET. The improvement in turn-on is due to the much lower recovery loss of the SiC diode.

Power systems designs can gain significant benefits through low switching losses:

- Less heat generated translates into simpler, cheaper, smaller, and/or lighter cooling systems and ultimately higher power density.

- Allows switching frequency to increase to reduce sizes of passive components (capacitors, inductors), reducing system cost, size, and weight.

- Enables lower operating temperatures so components do not have be derated as much, allowing smaller, less expensive components to be used. At the system level, this means a lower-rated SiC system can replace higher-rated silicon system.

The tests shown in **FIGURE 2** and **3** were conducted at Vdd = 400V, Icc = 20A, and  $25^{\circ}C$ , and diode recovery losses are included.

**FIGURE 4** shows that at 20 kHz switching frequency, a 100-A SiC half bridge module that is forced-air cooled can replace a 200-A IGBT module that is water cooled.

#### SiC MOSFET reliability

Reliability is a one of the most important considerations in power electronics design. Therefore, one of the first questions from power system engineers is: "Is SiC as reliable as silicon?" The three most important aspects related to overall reliability are gate oxide reliability, stability of gate threshold voltage Vt, and the robustness of the body diode with reverse conduction.

Electrical overstressing of the gate oxide is a common failure mode of MOS devices. Gate oxide quality, consequently, directly affects SiC MOSFET's reliability. The good news is that manufacturers have solved the problem of developing high-quality oxide on SiC substrates to minimize defect density (interface and bulk traps) without compromising device life or electrical characteristics stability.

A standard test that measures the quality of gate oxide MOS is the Constant Current Stress Time-Dependent Dielectric Breakdown (CCS TDDB), shown in **FIGURE 5**. The accumulated charge QBD is a quality indicator of the gate oxide layer. The value of 15-20°C/ cm2 is equivalent to that of silicon MOSFETs.

**FIGURE 6** shows that when a positive voltage is applied to the gate for an extended period of time, crystal defects at the oxide-SiC interface trap electrons and cause Vth to increase.

In **FIGURE 7**, when a negative voltage is applied, trapped holes cause Vth to decrease -- the shift in Vth is 0.3V or less. These tests are performed on the ROHM Semiconductor SCT2080KE SiC MOSFET.

The results are comparable to that of a silicon MOSFET. However, the shift would be much smaller in practical usage since MOSFETs are alternately switched on and off. This allows trapped electrons and holes to "escape" between switching cycle. Thus, the accumulated trapped carriers, which cause shift in Vth, are much less.

#### A new era of power conversion systems

Even though there have been many significant technology advances in the last decade, and the supply chain continues to expand, the wide bandgap technology industry for SiC devices has a long way to go to reach its full potential. Making great strides is the next generation of SiC power devices, which are well-positioned to enable new era of high-volume power conversion applications such as EVs and solid state transformers. SiC can also be a positive catalyst for future technology development that enhances application capabilities while continuing to stimulate market demand.  $\blacklozenge$

## Cashing in with chips: Improving efficiency in semiconductor R&D

**SCOTT JONES,** Alix Partners, San Francisco, CA

Companies have achieved a 30% or greater increase in R&D efficiency—as measured by the return on invested R&D dollars—through the implementation of proper planning processes and the better allocation of resources.

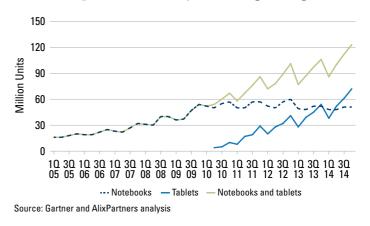

he semiconductor industry showed a sign of recovery in 2013: revenue growth returned to positive territory, although it remained well below historical averages. Still, research and development (R&D) investment stayed at historically high levels for the industry, at nearly \$50 billion [1]. That was largely because R&D investment is a crucial lever for maintaining high operating margins through cost improvements and for integrating new capabilities into silicon to support new applications in growing markets such as smartphones and tablets. The industry as a whole appears to be at a crucial turning point; the next two years could be make-or-break for several vital

technologies that have been in development for a decade 50% 40 30

1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 20112013E2015E Annual growth — Five-year rolling average

or more. The ways semiconductor companies react to those challenges may determine their own futures as well as the future of the industry as a whole. Individual companies need to achieve greater returns on their necessarily large R&D investments, and we see a need for greater R&D alignment across the industry.

#### Revenue growth is back, just not as strong as before

In 2013, industry revenue was estimated to have grown by 5%. We expect revenue to grow by 6 to 7% in 2014 before 2015, when we expect it to return to levels well below the long-term average. Despite lower actual growth and due to the roll-off of 2009 data, we should observe in 2014 a spike in the five-year rolling average. When

Source: Semiconductor Industry Association and AlixPartners research

**SCOTT JONES** is a director at Alix Partners, San Francisco, CA; ajones@alixpartners.com.

Growth YOY

20

10 ٥

-10 -20

-30 \_40 the 2010 growth spike rolls off in 2015, the five-year rolling average will return to its previous range of 5% and below (**FIGURE 1**).

Since the sharp recovery in 2010, the industry saw zero to negative growth for two years and began only a mild recovery in 2013.

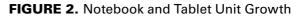

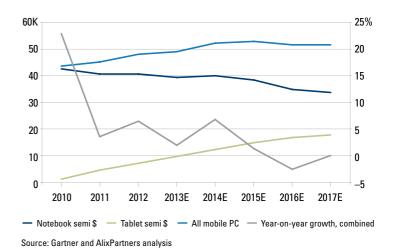

#### Shifting market demand

The shift from personal computers to tablets and smartphones is causing more demand for leading-edge foundry capacity as well as a temporary decrease in semiconductor content. We expect that trend to continue through 2017. The industry enjoyed a momentary boost from the introduction of tablets in 2010, but since then the growth of semiconductor content in the combined, notebook-plustablet market is up only marginally, even though unit demand continues to increase at historical rates (FIGURE **2**). We expect growth in the industry to bottom out in 2017, after which the combined PC and tablet markets should return to more-traditional growth patterns of 8 to 10% per year as the transition from consumer notebooks to tablets stabilizes with converged platforms. We believe that at that point, the industry could begin to see increased growth from a multitude of end markets such as the Internet of Things and medical devices.

Further evidence that the growth engine for semiconductors is shifting from PCs to tablets and smartphones can be found in the list of the largest consumers of semiconductors. Apple's and Samsung's consumption of semiconductors has grown dramatically during the past five years, whereas the largest PC original equipment manufacturers have seen relatively little growth (**FIGURE 3**).

#### Leading-edge R&D spend rising rapidly

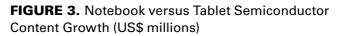

Revenue growth may be slowing, but the same cannot be said of the cost of R&D for leading-edge technologies. The cost of developing next-generation products and chip-manufacturing processes is increasing at higher rates with each generation.

Figures released by the Common Platform consortium have consistently shown that integrated device manufacturers (IDMs) and foundries are experiencing 35% cost increases from one process technology to the next and that fabless semiconductor companies are seeing even greater cost increases—of roughly

60%—for designs and tape-outs of next-generation process technologies.

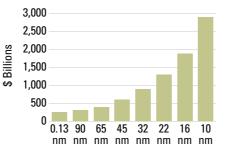

Leading-edge fabrication costs have increased at an average rate of roughly 30% per generation in the past decade, and we expect at least the same rate of increase at the 16nm generation or higher due to increased photolithography costs and the challenges of a new transistor technology necessary at 16nm and 14 nm (**FIGURE 4**). Currently, Intel is expected to be the first company to release products with 16nm technology in early to mid-2014.

#### **Process technology development:** higher costs, fewer customers

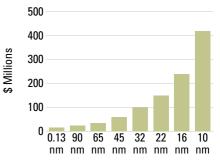

The R&D costs of development of a next-generation process manufacturing technology are increasing at nearly 40% per generation—a rate that has remained relatively steady for the past decade (FIGURE 5) and been caused mostly by the high cost of the test wafers and development tools necessary to deliver a new process technology. More-expensive test wafers and tools mean that foundries and IDMs cannot afford to invest in as many customer-specific or variant technologies. And that puts more pressure on foundries and IDMs to deliver a leading-edge technology platform that can address more of the market, which means placing large bets on industry trends and partnering with customers that will design into a particular manufacturing technology. If that foundry or IDM is unable to partner with customers that have significant volume demand on the leading edge, then the foundry or IDM

BUSINESS

Source: Common Platform Technology Forum 2012 and AlixPartners analysis

**FIGURE 4.** (L) Fab Costs by Node (in US\$ billions) **FIGURE 5.** (C) Process Technology Development Costs by Node (US\$ billions) **FIGURE 6.** (R) Chip Design Costs by Node (US\$ millions)

may never achieve a positive return on its substantial investment in the fab and design technology.

Risk is higher on investment in process technology largely because the cost of chip design for leading-edge products is rising rapidly. The cost of designing a chip for a leading-edge process has increased at nearly 60% per generation over the past decade (FIGURE 6), which is twice the level of the increase in the costs of leading-edge fabs and new process technologies. As a result, fabless semiconductor companies can afford fewer chip designs for the leading-edge processes, which makes it even more crucial that the leading development programs (1) have the features that end-market customers require and (2) target the market segments with the highest values. The upstream impact on the foundries is that fewer designs on the leading edge result in a higher concentration of volumes on a small number of products. That again highlights the importance of partnering with the right customer—one that can provide significant volumes on leading-edge process technologies. With fewer and fewer designs on each generation, bets on the winning technology trends will likely only get bigger.

#### R&D spending drivers and technology challenges

Regardless of whether we look at IDMs, foundries, or fabless semiconductor design companies, we observe a consistent increase in R&D costs across the industry. The slowed revenue growth of the past six years jeopardizes companies' ability to gain on the leading edge or even maintain current levels of financial return. That trend seems to put more pressure on semiconductor companies to seek higher returns on R&D investments so as to maintain the pace of innovation needed. For many companies, 2014 will be a pivotal year, as new technologies reach critical points in their applications to products and manufacturing. In the first half of 2014, Intel is expected to introduce its first product based on trigate transistors, which will be the company's first product based on nonplanar transistors. Other companies—such as Taiwan Semiconductor Manufacturing Company (TSMC), Samsung, and GlobalFoundries—are developing their own process technologies based on FinFET transistors [4]. The ability to ramp up those technologies at 16 nm and 14 nm will be crucial to the continued scaling necessary to drive the cost reductions consistent with Moore's law.

Beyond the technology issues that have to be faced at 16nm and 14nm are more-significant challenges, such as extreme ultraviolet lithography (EUVL) technology. Lithography is the most expensive and most crucial portion of the semiconductor manufacturing process, and the technology's current application is unable to continue in the same manner at 16nm and below. Currently, the approach for 16 nm does not use EUVL, instead calling for double patterning, which means that lithography costs will double on the current generation based on the need to go through the steps two times to get the same result as in previous generations. This will add roughly 10% to wafer costs beyond the normal cost increases from one generation to the next, as well as add increased quality concerns and yield concerns to the manufacturing process.

And the problem only worsens in the 12 nm generation:

foundries and IDMs would have to use triple patterning if EUVL technology has not become an economically viable alternative by that time. Triple patterning would require roughly \$2.5 billion additional capital spending to devise a typical fabrication capable of producing 600,000 wafers per year and would add more than \$400 million to product costs per year for the fabrication [5]. If EUVL can be successfully introduced at adequate throughputs, it would be able to mitigate those additional costs and keep semiconductors scaling on the same path as during the past 30 years. For EUVL to be viable for high-volume manufacturing, the costs per wafer will have to be significantly lower than those involved in the double- and triplepatterning approaches. This would likely be necessary to drive adoption of a new technology, with significant R&D and capital investment required to integrate it into a manufacturing line.

Because the traditional advances in lithography have not achieved scaling, the industry has begun looking to other solutions. Many companies are considering different types of 3D integration -- such as multiple chips in a package or wafer-to-wafer bonding -- to achieve more flexibility in their supply chains and to improve performance without increasing the scaling on a single-chip design. But 3-D technology has not been able to gain traction with high-volume chip manufacturers because of its high costs and yield concerns, although many firms are still evaluating the options (3-D integration might help mitigate other challenges such as double and triple patterning on advanced process technologies). There is also a push to move the industry from 300mm wafers to 450mm wafers, which historically has improved the average cost per die by 30% based on the transitions to 200mm and 300mm wafer sizes. Currently, Intel seems to be the dominant force behind that push, but others such as Samsung, TSMC, and GlobalFoundries are also part of the consortium to explore the move to 450mm wafers [6].

#### Why R&D efficiency is crucial

Companies' major risk during periods of slower revenue growth is that pressured R&D budgets prevent the product development necessary to spur future revenue growth, thereby leading companies to miss major product cycles. This creates a so-called death spiral, whereby a company's inability or unwillingness to fund necessary R&D programs leads to further market share erosion

Sources: S&P Capital IQ and AlixPartners analysis

and greater revenue declines. How does that downward spiral begin? When a company has missed market signals and its products are not aligned with end-market needs, the company is likely to lose key market share or become too heavily exposed to a shrinking market. That can lead to obvious negative impacts on revenue and earnings. A common reaction to such a scenario is to constrain R&D spending as part of overall retrenchment, but if such R&D cutbacks are not carried out in a careful and thoughtful way, the company risks accelerating its losses through continued market share declines that would result from lack of innovation.

One of the major effects of R&D efficiency is the ability to get products to market on time. For leadingedge products when power and performance count, time to market can mean the difference between success and failure. Not only must companies deliver individual programs on time, but also they must balance a portfolio of R&D resources and deliver multiple programs on time—and do it generation after generation. Having the proper balance of resources is crucial; one program that goes over budget could affect the development of the next generation of products by delaying the roll-off of resources onto that program. Sometimes organizations take on too many programs and stretch their resources too thin in an effort to capture every incremental opportunity, and that can jeopardize the delivery of programs serving the core business. Without proper discipline, chasing multiple incremental opportunities can delay key programs and can snowball into multiple generations of delayed programs. That may lead to market share loss and/

**BUSINESS**

FIGURE 8. Developing a Road Map

or more-aggressive discounting and pricing, leaving fewer margin dollars to fund future R&D investment.

#### How spending affects profitability

Certainly, R&D is a crucial lever for maintaining competitive advantage, but simply increasing R&D spend does not necessarily lead to increased revenue growth and profitability. In fact, AlixPartners' study of the 86 largest semiconductor companies globally found no significant difference in operating margins among those companies that increased R&D spend and those that maintained or reduced spend.

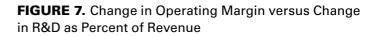

What matters more, in terms of profitability, is the relationship between spending increases and revenue increases. We have consistently seen that those companies whose revenue growth exceeded their R&D spending growth outperformed their competitors by a wide margin. Such companies saw operating margins increase 85% of the time; their operating margin increases were three times higher than those of companies that had grown R&D spend more quickly than revenue (**FIGURE 7**).

Companies that achieve higher returns on their R&D investments, as demonstrated through higher revenue growth, are much more likely to achieve higher levels of profitability over time. And although there are many paths to improved profitability, we believe that improved R&D efficiency is one of the surest bets.

How do semiconductor firms improve R&D efficiency?

Companies have achieved a 30% or greater increase in R&D efficiency—as measured by the return on invested R&D dollars—through the implementation of proper planning processes and the better allocation of resources.

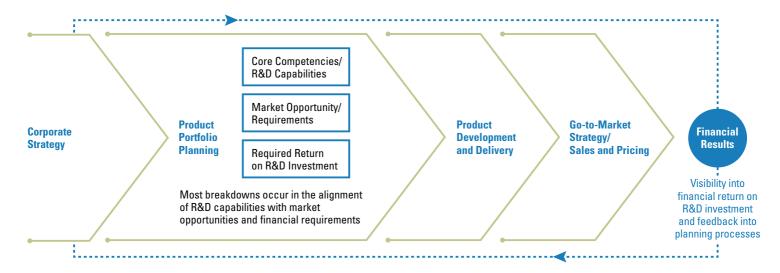

In turn, those improvements can lead to top-line growth through market share gains in key segments and to lower R&D costs per program through faster time to market. Companies with poor R&D efficiency often suffer more from lack of proper planning than from inability to innovate. The areas of greatest importance are alignment of R&D investment with market needs, allocation of the right amount of resources, and stipulation of sufficient financial requirements for the programs to meet. Those areas require integrated planning processes, with inputs from sales and marketing, R&D, operations, and finance. Such processes should be able to capture market requirements in a specified time frame based on end-market customer feedback and be aligned with the R&D organization's ability to deliver based on its capabilities.

Aligning R&D capabilities with opportunities from the marketing organization can enable management to create a list of potential programs the company could pursue to meet market needs. After financial requirements and analysis have been provided, management can then rank the potential programs based on the company's strategic priorities and on the expected return on investment. Once program execution has begun, management should ensure that the highest-rated priority programs get fully resourced and brought to market on time, with all of the key features necessary to make the offering successful.

That approach, known as the zero-based-budget method, has been successful in the semiconductor industry as applied by such industry leaders as Texas Instruments and Intel [7]. Linkages among the marketing, R&D, and finance organizations are important in the development of a road map that aligns company strategy with the company's go-to-market approach (**FIGURE 8**). The proper channels must be in place to ensure alignment of the different organizations at all key junctures of program development and execution; this enables the organization to course correct if market forces change and thereby affect the program's business case. Early identification of those changes can make the difference between achieving a profitable return on investment in a program and taking a substantial loss.

Several benefits result from proper program planning and proper resource allocation. For instance, delivering a predictable road map that has credibility with the customer base is essential to maintaining and growing market share in product market segments. And it makes available certain key resources for the next-generation programs necessary to keep semiconductor companies on the leading edge of the industry.