MARCH 2015

Insights for Electronics Manufacturing

Multi-patterning Lithography

P. 13

Supplier Hub answers changing industry needs

P. 18

Advanced Analytics for Yield Improvement P. 20

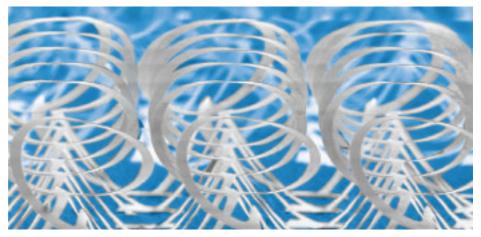

**3D 'Pop-up' Silicon Structures RG**

Extension MEDIA

www.solid-state.com

What's the driving force behind the performance and profitability of your packaging machines?

At Omron, we deliver a comprehensive range of products and services designed to increase the speed, versatility, and safety of your machines.

ECHNÓLOGY

Empower your production with highly advanced solutions that have the proven reliability to maximize your customers' loyalty. If you are developing a new machine or upgrading an existing model, look to Omron as your knowledgeable partner for superior automation.

# Discover how we can increase your packaging profitability.

OMRON AUTOMATION AND SAFETY • Toll free: 800.556.6766 • www.omron247.com

## Solid State TECHNOLOGY.

MARCH 2015 VOL. 58 NO.2

On the cover: 3D microstructures of devicegrade silicon formed using concepts similar to those in children's 'pop-up' books. Source: University of Illinois.

#### FEATURES

#### LITHOGRAPHY | Changes and challenges abound in multi-patterning lithography

Experts in the fields of electronic design automation and lithography address the issues associated with the technology. *Jeff Dorsch, contributing editor*

#### BUSINESS | Supplier Hub answers the needs of a changing semiconductor industry

YIELD Advanced analytics for yield improvement and zero defect in semiconductors

The industry may indeed stand at an inflection point, but the future is bright. Innovation cannot be stifled. And collaboration remains the consensus of an industry focused on the next new thing. *Luc Van den hove, imec, Leuven, Belgium*

## 20

18

Machine learning based advanced analytics for anomaly detection offers powerful techniques that can be used to achieve breakthroughs in yield and field defect rates. Anil Gandhi, Ph. D. and Joy Gandhi, Qualicent Analytics, Inc., Santa Clara, CA

**PACKAGING** | Consider packaging requirements at the beginning, not the end, of the design cycle Consider these eight issues where the packaging team should be closely involved with the circuit design team. *John T. Mackay, Semi-Pac, Inc., Sunnyvale, CA*

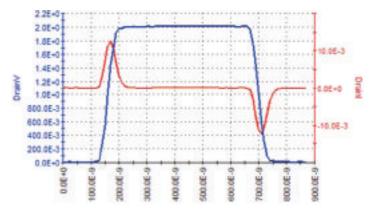

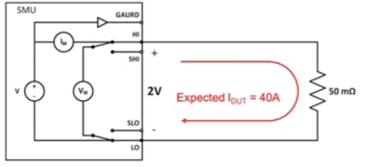

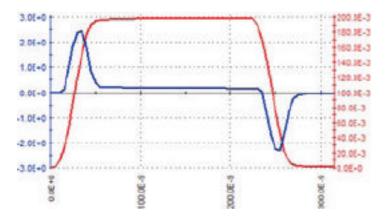

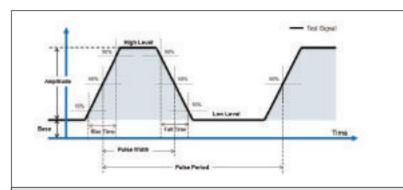

#### TEST AND MEASUREMENT | Techniques for Simplifying Pulsed Measurements: Part 2

Common pulsed measurement challenges are defined. David Wyban, Keithley Instruments, a Tektronix Company, Solon, Ohio

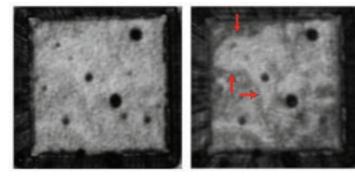

**INSPECTION** Imaging tomorrow's components, acoustically

Tom Adams, Sonoscan, Inc., Elk Grove Village, IL

Packages are changing. Acoustic methods provide a way to image and analyze them.

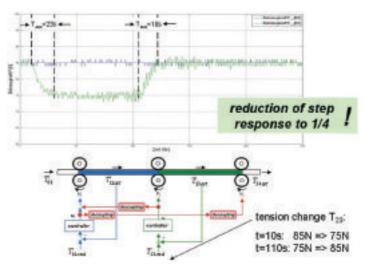

#### FLEXIBLE DISPLAYS | Web tension control in roll-to-roll web processing

Achieving precise registration accuracy is a factor of two related variables: web tension and transport velocity. *Bipin Sen, Bosch Rexroth, Hoffman Estates, IL*

#### COLUMNS

- 2 Editorial The ConFab 2015, Pete Singer, Editor-in-Chief

- 11 Packaging Battling over Apple, Phil Garrou, Contributing Editor

- **12 Semiconductors** Proponents of EUV, immersion lithography face off at SPIE, *Jeff Dorsch, Contributing Editor*

- **41 Industry Forum** Flexible facilities for 450mm wafer fabs, Joe Cestari, Total Facility Solutions, Plano, Texas

#### www.solid-state.com

#### DEPARTMENTS

- 4 Web Exclusives

- 6 News

### editorial

## The ConFab 2015

I'm delighted to announce the keynotes and other key speakers for The ConFab 2015, to be held May 19-22 at The Encore at The Wynn in Las Vegas.

Our first keynote, on Wednesday, will be Ali Sebt, President and CEO of Renesas America, who will provide his insight on monetizing the Internet of Things. He'll discuss how intelligent and connected platforms will enable new value chains based on a platform play, or an associated ecosystem play.

"What are some of the enabling technologies necessary to make IoT a reality? Come to The ConFab 2015 and find out!"

Our second keynote, on Thursday, will be Paolo Gargini, Chairman of the ITRS. The newly "re-framed" ITRS roadmap process has been extended with studies of key requirements from a system-level perspective that includes heterogeneous integration, new revolutionary devices and new ways of physical and wireless connectivity. Paolo will describe what is known as the ITRS 2.0.

Also slated to speak is Subramani Kengeri, Vice President, Global Design Solutions at GLOBALFOUNDRIES, who will talk about how the design eco-system is a critical enabler for semiconductor growth. Subi says that the rapid evolution of applications in the consumer and mobile space coupled with the emergence

of the IoT are driving innovations that push the limits of power, performance, cost, and time-to-volume. At the same time, next generation SoCs are demanding stronger design and technology co-optimization solutions—some of which are optimal in main-stream technologies—to support complex design integration functions.

Lode Lauwers, Vice President Business Development, at imec will continue the IoT theme, focusing on how it is driving technology trends on system scaling and semiconductor manufacturing effectiveness. Lode says to realize the promises of an augmented, connected sustainable world, promised by the IoT, the IC industry faces significant challenges both at a distributed level, with the development of ultralow power sensor and radio technologies, as well as in the cloud, with huge computational requirements to store and process data.

Jim Feldhan, president of Semico, will present the outlook for key components of the IoT market. Wearables, electronic health care, smart home, cities and cars all promise to be high volume semiconductor markets. What will these markets look like? What are some the enabling technologies necessary to make IoT a reality? Come to The ConFab 2015 and find out! See www.theconfab.com for more info.

#### -Pete Singer, Editor-in-Chief

# **Solid Sta**

Pete Singer, Editor-in-Chief Ph: 978.470.1806 psinger@extensionmedia.com Shannon Davis, Editor, Digital Media

Ph: 603.547.5309 sdavis@extensionmedia.com

Ed Korczvnski, Senior Technical Editor, edk@extensionmedia.com

Jeff Dorsch, Contributing Editor

Phil Garrou, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design

#### CREATIVE/PRODUCTION/ONLINE

Spryte Heithecker, Production Manager Yishian Yao, Media Coordinator

Nicky Jacobson, Senior Graphic Designer

Caldin Seides, Graphic Designer

Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION Jenna Johnson. jjohnson@extensionmedia.com

2343. (8 am - 5 pm, PST)

#### **CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, **Business Development** msterling@extensionmedia.com

March 2015, Volume 58, Number 2 • Solid State Technology ©2015 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00, You will continue to receive your subscription free of charge. This fee is only for airmail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-2742 (9 m. 6 m. PST)

#### For subscription inquiries: Tel: 847.559.7500; Fax: 847.291.4816;

Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2015 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

Conference & Networking Event MAY 19-22, 2015 Encore at the Wynn Las Vegas www.theconfab.com

#### FEATURED SPEAKERS

**Ali Sebt** CEO Renesas America

**Paolo Gargini** Chairman ITRS

Subramani Kengeri VP, Global Design GLOBALFOUNDRIES

Dr. William Chen Fellow ASE

Lode Lauwers VP, Business Development imec

#### PURCHASE YOUR TOTAL ACCESS PASS TODAY

## Exploring the Edges of Semiconductor Technology & Business

Attend the Premier Annual Conference & Networking Event for Semiconductor Manufacturing Executives

#### **EVENT HIGHLIGHTS**

- Hear marketing insights, technology forecasts and strategic assessments of the challenges & opportunities facing the industry

- Attend multiple, well-attended networking events

- Connect with key executives from the world's top foundries, OEMs, IDMs, OSATs and fabless/design companies

- Join in strategic discussions with pre-qualified decision makers and influencers

#### Visit www.theconfab.com for more information

Owned and Produced by:

www.theconfab.com

# Online@www.solid-state.com

#### **Web Exclusives**

## Applied's merger with TEL: Still a work in progress

Applied Materials reported that its proposed merger with Tokyo Electron Ltd. (TEL) is still under way, without giving a deadline or expected date of conclusion. President and CEO Gary Dickerson said the company is "making progress with regulators" and plans to "complete the merger as soon as possible." He declined to elaborate on that point, on advice of its attorneys. http://bit.ly/1LkbMdp

# SEMICON show highlights chip manufacturing in South Korea

The SEMICON Korea conference and exhibition was held in Seoul for a threeday run. The show highlighted the importance of semiconductor manufacturing in South Korea, home to two of the biggest memory chip makers in the world, Samsung Electronics and SK Hynix. (From SemiMD) http://bit.ly/1DBsWUE

### 5nm node needs EUV for economics

At IEDM 2014 last month in San Francisco, Applied Materials sponsored an evening panel discussion on the theme of "How do we continue past 7nm?" Given that leading fabs are now ramping 14nm node processes, and exploring manufacturing options for the 10nm node, "past 7nm" means 5nm node processing. There are many device options possible, but cost-effective manufacturing at this scale will require Extreme Ultra-Violet (EUV) lithography to avoid the costs of quadruple-patterning. (From SemiMD)

http://bit.ly/1tFK2NA

# Directed Self Assembly Hot Topic at SPIE

Jeff Dorsch reports from the SPIE Advanced Lithography Symposium in San Jose, Calif. The hottest three-letter acronym is less EUV and more DSA, as in directed self-assembly.

http://bit.ly/1K913r3

#### EUVL – Remaining challenges and preview of topics for the 2015 SPIE EUVL Conference

With the 2015 SPIE Advanced Lithography (AL) conference around the corner, some people have asked me what remaining EUVL challenges need to be addressed to ensure it will be ready for mass production later this year or next. Here are Vivek Bakshi's thoughts on this topic and what he expected to hear at the conference. http://bit.ly/1vlVPl0

#### Insights from the Leading Edge: Semi Industry Strategy Symposium 2015

The SEMI ISS (Industry Strategy Symposium) brings together industry leaders to share their opinions on where our industry is going. The US meeting is held each January in Half Moon Bay, CA. The new darling of the microelectronics industry is obviously the Internet of Things (IoT). Many of the speakers focused on this topic though there was far more predicting than there was hard data.

http://bit.ly/1AUyXeN

#### Oscar for DMD Inventor Hornbeck

Hornbeck has been awarded an Academy Award of Merit (Oscar statuette) for his contribution to revolutionizing how motion pictures are created, distributed, and viewed using DMD technology (branded as the DLP chip for DLP Cinema display technology from TI). (From SemiMD)

http://bit.ly/1w6iylM

2015 MRS<sup>®</sup> FALL MEETING & EXHIBIT November 29 – December 4, 2015 | Boston, Massachusetts

CALL FOR PAPERS Abstract Submission Opens May 18, 2015 Abstract Submission Deadline June 18, 2015

LL

ΝN

PP

00

RR

SS

A Engaged Learning of Materials Science and Engineering in the 21<sup>st</sup> Century

#### **BIOMATERIALS AND SOFT MATERIALS**

- B Stretchable and Active Polymers and Composites

- for Electronics and Medicine C Tough, Smart and Printable Hydrogel Materials

- Biological and Bioinspired Materials in Photonics and Electronics— Biology, Chemistry and Physics

- E Engineering and Application of Bioinspired Materials

- F Biomaterials for Regenerative Engineering

- G Plasma Processing and Diagnostics for Life Sciences

- H Multifunctionality in Polymer-Based Materials, Gels and Interfaces

I Nanocellulose Materials and Beyond—

- Nanoscience, Structures, Devices and Nanomanufacturing J Wetting and Soft Electrokinetics

- K Materials Science, Technology and Devices for Cancer Modeling, Diagnosis and Treatment

- L Nanofunctional Materials, Nanostructures and Nanodevices for Biomedical Applications

#### NANOMATERIALS AND SYNTHESIS

- M Micro- and Nanoscale Processing of Materials for Biomedical Devices

- N Magnetic Nanomaterials for Biomedical and Energy Applications

- 0 Plasmonic Nanomaterials for Energy Conversion

- P Synthesis and Applications of Nanowires and Hybrid 1D-0D/2D/3D Semiconductor Nanostructures

- Q Nano Carbon Materials—1D to 3D

- R Harsh Environment Sensing—Functional Nanomaterials and Nanocomposites, Materials for Associated Packaging and Electrical Components and Applications

#### **MECHANICAL BEHAVIOR AND FAILURE OF MATERIALS**

- S Mechanical Behavior at the Nanoscale

- T Strength and Failure at the Micro- and Nanoscale— From Fundamentals to Applications

- U Microstructure Evolution and Mechanical Properties

- in Interface-Dominated Metallic Materials V Gradient and Laminate Materials

- V Gradient and Laminate Materials

- W Materials under Extreme Environments (MuEE)

- Y Shape Programmable Materials

#### **ELECTRONICS AND PHOTONICS**

- Z Molecularly Ordered Organic and Polymer Semiconductors— Fundamentals and Devices

- AA Organic Semiconductors-Surface, Interface and Bulk Doping

- BB Innovative Fabrication and Processing Methods for Organic

- and Hybrid Electronics CC Organic Bioelectronics—

- From Biosensing Platforms to Implantable Nanodevices

- DD Diamond Electronics, Sensors and Biotechnology— Fundamentals to Applications

- EE Beyond Graphene—2D Materials and Their Applications

- FF Integration of Functional Oxides with Semiconductors

- GG Emerging Materials and Platforms for Optoelectronics

- HH Optical Metamaterials-

- From New Plasmonic Materials to Metasurface Devices II Phonon Transport, Interactions and Manipulations

- in Nanoscale Materials and Devices—Fundamentals and Applications

- JJ Multiferroics and Magnetoelectrics KK Materials and Technology for Non-Volatile Memories

####

Biological and Functional Nanomaterials, Metrology and Modeling UU Frontiers in Scanning Probe Microscopy

**ENERGY AND SUSTAINABILITY**

for Next-Generation Photovoltaics

**Rechargeable Batteries**

Catalytic Materials for Energy

00 Nanomaterials-Based Solar Energy Conversion

Wide-Bandgap Materials for Energy Efficiency-

Power Electronics and Solid-State Lighting

Progress in Thermal Energy Conversion-

Materials and Architectures for Safe and Low-Cost

MM Advances in Flexible Devices for Energy Conversion and Storage

Thin-Film and Nanostructure Solar Cell Materials and Devices

Materials, Interfaces and Solid Electrolytes for High Energy Density

Thermoelectric and Thermal Energy Storage Materials and Devices

Electrochemical Energy Storage Technologies

VV In Situ Study of Synthesis and Transformation of Materials

THEORY, CHARACTERIZATION AND MODELING

- WW Modeling and Theory-Driven Design of Soft Materials

- XX Architected Materials—Synthesis, Characterization, Modeling and Optimal Design

- YY Advanced Atomistic Algorithms in Materials Science

- ZZ Material Design and Discovery via Multiscale Computational Material Science

- AAA Big Data and Data Analytics for Materials Science

- BBB Liquids and Glassy Soft Matter—Theoretical and Neutron Scattering Studies

- CCC Integrating Experiments, Simulations and Machine Learning to Accelerate Materials Innovation

- DDD Lighting the Path towards Non-Equilibrium Structure-Property Relationships in Complex Materials

- X Frontiers of Material Research

#### www.mrs.org/fall2015

The MRS/E-MRS Bilateral Conference on Energy will be comprised of the energy-related symposia at the 2015 MRS Fall Meeting.

#### **Meeting Chairs**

T. John Balk University of Kentucky Ram Devanathan Pacific Northwest National Laboratory George G. Malliaras Ecole des Mines de St. Etienne Larry A. Nagahara National Cancer Institute Luisa Torsi University of Bari "A. Moro"

#### **Don't Miss These Future MRS Meetings!**

2016 MRS Spring Meeting & Exhibit March 28 - April 1, 2016 Phoenix, Arizona

2016 MRS Fall Meeting & Exhibit November 27 - December 2, 2016 Boston, Massachusetts

#### MRS MATERIALS RESEARCH SOCIETY® Advancing materials. Improving the quality of life.

506 Keystone Drive • Warrendale, PA 15086-7573 Tel 724.779.3003 • Fax 724.779.8313 info@mrs.org • www.mrs.org lelationships

Please send news articles to sdavis@extensionmedia.com

#### worldnews

**EUROPE imec** reported a breakthrough results in directed self-assembly (DSA) process development.

USA **GLOBALFOUNDRIES** announced a partnership with imec for joint research on future radio architectures and designs for highly integrated mobile devices and IoT applications.

ASIA Gigaphoton Inc. announced that it has successfully achieved continuous operation of 140W EUV light source at 50 percent duty cycle on its prototype laser-produced plasma light sources for EUV lithography scanners.

**USA** Amkor Technology, Inc. announced that Susan Y. Kim has been appointed as a new member of the Company's Board of Directors.

**EUROPE** | Scientists from **Ghent University** and **imec** announced that they demonstrated interaction between light and sound in a nanoscale area. Their findings elucidate the physics of light-matter coupling at these scales – and pave the way for enhanced signal processing on mass-producible silicon photonic chips.

**USA** | **Micron** appointed Robert Peglar as Vice President of Advanced Storage Solutions.

ASIA Qualcomm Incorporated announced that it has reached a resolution with China's National Development and Reform Commission regarding the NDRC's investigation of Qualcomm under China's Anti-Monopoly Law. Qualcomm has agreed to implement a rectification plan that modifies certain of its business practices in China and that fully satisfies the requirements of the NDRC's order.

# news

### 3D 'Pop-up' silicon structures

Researchers at the University of Illinois at Urbana-Champaign have developed a unique process for geometrically transforming two dimensional (2D) micro/ nanostructures into extended 3D layouts by exploiting mechanics principles similar to those found in children's 'pop-up' books.

3D microstructures of device-grade silicon formed using concepts similar to those in children's 'pop-up' books. The image shown is a colorized scanning electron micrograph. The silicon has a thickness of 2 microns.

Complex, 3D micro/nanostructures are ubiquitous in biology, where they provide essential functions in even the most basic forms of life. Similar design strategies have great potential for use in a wide variety of man-made systems, from biomedical devices to microelectromechanical components, photonics and optoelectronics, metamaterials, electronics, energy storage, and more.

Continued on page 8

## Global semiconductor industry posts record sales in 2014

The Semiconductor Industry Association (SIA) announced that the global semiconductor industry posted record sales totaling \$335.8 billion in 2014, an increase of 9.9 percent from the 2013 total of \$305.6 billion. Global sales for the month of December 2014 reached \$29.1 billion, marking the strongest December on record, while December 2014 sales in the Americas increased 16 percent compared to December 2013. Fourth quarter global sales of \$87.4 billion were 9.3 percent higher than the total of \$79.9 billion from the fourth quarter of 2013. Total sales for the year exceeded projections from the World Semiconductor Trade Statistics (WSTS) organization's industry forecast. All monthly sales numbers are compiled by WSTS and represent a three-month moving average.

Continued on page 10

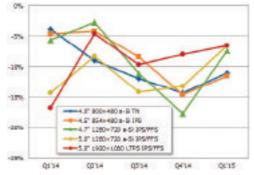

# Smartphone display manufacturers facing pressure to further reduce prices in 2015

Even as smartphone panel resolution continues to rise, and as display sizes continue to grow, panel manufacturers are facing pressure to reduce prices. According to the Quarterly Mobile Phone Display Shipment and Forecast Report from IHS, a global source of critical information and insight, total mobile phone display shipments are estimated to reach a new record high of 2 billion units in 2014. Average smartphone display prices declined nearly 14 percent year-overyear (YoY) from \$22 per module in 2013 to \$19 in 2014. IHS Technology forecasts another double-digit fall for smartphone display prices in 2015, resulting in a blended ASP of about \$17.

Continued on page 11

# KLA-Tencor extends its 5D patterning control solution with new metrology systems

KLA- Tencor Corporation introduced two advanced metrology systems that support the development and production of 16nm and below IC devices: Archer 500LCM and SpectraFilm LD10. The Archer 500LCM overlay metrology system provides accurate overlay error feedback through all stages of the yield ramp, helping chipmakers resolve overlay issues associated with innovative patterning techniques, such as multi-patterning and spacer pitch splitting. Through reliable, precise measurement of film thickness and stress, the SpectraFilm LD10 films metrology system enables qualification and

Continued on page xx

May 26-29, 2015 Sheraton San Diego Hotel & Marina • San Diego, CA • USA

2015

The only event that encompasses the diverse world of integrated systems packaging.

#### The 65th Electronic Components and Technology Conference

2200

#### Don't Miss Out on the Industry's Premier Event!

For more information, visit

WWW.ectc.net

**Conference Sponsors:**

#### MORE THAN 300 TECHNICAL PAPERS COVERING: 3D/TSV

Advanced Packaging

- Modeling & Simulation

- Optoelectronics

- Interconnections

- Materials & Processing

**Applied Reliability**

Assembly & Manufacturing Technology

High-Speed, Wireless & Components

**Emerging Technologies**

#### HIGHLIGHTS

- 41 Technical sessions including:

- 5 Interactive presentation sessions, including one featuring student presenters

- I 6 CEU-approved Professional Development Courses

- Technology Corner Exhibits, featuring more than 100 industryleading vendors

- 6 Special invited sessions

- Several evening receptions

- 3 Conference luncheons

- Multiple opportunities for networking

- Great location

## **NEWS**cont

#### Continued from page 6

Researchers noted that existing methods for forming 3D structures are either highly constrained in the classes of materials that can be used, or in the types of geometries that can be achieved.

"Conventional 3D printing technologies are fantastic, but none offers the ability to build microstructures that embed high performance semiconductors, such as silicon," explained John Rogers, a Swanlund Chair and professor of materials science and engineering at Illinois. "We have presented a remarkably simple route to 3D that starts with planar precursor structures formed in nearly any type of material, including the most advanced ones used in photonics and electronics. A stretched, soft substrate imparts forces at precisely defined locations across such a structure to initiate controlled buckling processes that induce rapid, large-area extension into the third dimension. The result transforms these planar materials into welldefined, 3D frameworks with broad geometric diversity."

Potential applications range from battery anodes, to solar cells, to 3D electronic circuits and biomedical devices.

"The 3D transformation process involves a balance between the forces of adhesion to the substrate and the strain energies of the bent, twisted elements that make up the planar precursors," explained Sheng Xu, a postdoctoral fellow and co-author of the research paper. "Basically, we print 2D structures onto a pre-strained elastomer substrate with selected bonding points. Releasing the substrate to its original shape induces buckling processes that lift the weakly bonded regions of the 2D structure out of contact with the surface. The resulting spatially dependent deformations occur in an ordered sequence to complete the 3D assembly."

These motions follow precisely the predictions of 3D computational models of the mechanics. These models, in turn, serve as rapid, inverse design tools for realizing a wide range of desired shapes.

Compatibility with the most advanced materials (e.g. monocrystalline inorganics), fabrication methods (e.g. photolithography) and processing techniques (e.g. etching, deposition) from the semiconductor and photonics industries suggest many possibilities for achieving sophisticated classes of 3D electronic, optoelectronic, and electromagnetic devices. "With this scheme, diverse feature sizes and wide-ranging geometries can be realized in many different classes of materials," stated postdoctoral fellow and co-author Zheng Yan. "Our initial demonstrations include experimental and theoretical studies of more than forty representative geometries, from single and multiple helices, toroids and conical spirals, to structures that resemble spherical baskets, cuboid cages, starbursts, flowers, scaffolds, fences and frameworks, each with single and/or multiple level configurations, constructed in various materials, including semiconductors, conductors and dielectrics."

"This work establishes the concepts and a framework of understanding. We're now exploiting these ideas in the construction of high performance electronic scaffolds for actively guiding and monitoring growth of tissue cultures, and networks for 3D electronic systems that can bend and shape themselves to the organs of the human body. We're very enthusiastic about the possibilities." Rogers added.

Rogers is the director of the Frederick Seitz Materials Research Laboratory and an affiliate of the Beckman Institute for Advanced Science and Technology at Illinois. He also holds affiliate appointments in the departments of bioengineering, chemistry, electrical and computer engineering, and mechanical science and engineering. With his research teams, Rogers has pioneered flexible, stretchable electronics, creating pliable products such as cameras with curved retinas, medical monitors in the form of temporary tattoos, a soft sock that can wrap an arrhythmic heart in electronic sensors, and LED strips thin enough to be implanted directly into the brain to illuminate neural pathways. His work in photovoltaics serves as the basis for commercial modules that hold the current world record in conversion efficiency. This research was supported by the U.S. Department of Energy Office of Science.

Rick Kubetz, Engineering Communications Office, University of Illinois ◆

## **NEWS**cont

Continued from page 6

"The global semiconductor industry posted its highest-ever sales in 2014, topping \$335 billion for the first time thanks to broad and sustained growth across nearly all regions and product categories," said John Neuffer, president and CEO, Semiconductor Industry Association. "The industry now has achieved record sales in two consecutive years and is well-positioned for continued growth in 2015 and beyond."

Several semiconductor product segments stood out in 2014. Logic was the largest semiconductor category by sales, reaching \$91.6 billion in 2014, a 6.6 percent increase compared to 2013. Memory (\$79.2 billion) and micro-ICs (\$62.1 billion) - a category that includes microprocessors - rounded out the top three segments in terms of sales revenue. Memory was the fastest growing segment, increasing 18.2 percent in 2014. Within memory, DRAM performed particularly well, increasing by 34.7 percent year-overyear. Other fast-growing product segments included power transistors, which reached \$11.9 billion in sales for a 16.1 percent annual increase, discretes (\$20.2 billion/10.8 percent increase), and analog (\$44.4 billion/10.6 percent increase).

Annual sales increased in all four regional markets for the first time since 2010. The Americas market showed particular strength, with sales increasing by 12.7 percent in 2014. Sales were also up in Asia Pacific (11.4 percent), Europe (7.4 percent), and Japan (0.1 percent), marking the first time annual sales in Japan increased since 2010.

"The U.S. market demonstrated particular strength in 2014, posting double-digit growth to lead all regions," continued Neuffer. "With the new Congress now underway, we urge policymakers to help foster continued growth by enacting policies that promote U.S. innovation and global competitiveness."

#### Continued from page 7

monitoring of the films and film stacks used in fabrication of FinFETs, 3D NAND and other leading-edge devices. The new systems are key products in KLA-Tencor's unique 5D patterning control solution, which drives optimal patterning results through the characterization and monitoring of fab-wide processes.

"As the industry leader in non-destructive optical metrology, we have closely collaborated with our customers to understand their challenges in optimizing pattern overlay, critical dimensions and films quality," stated Ahmad Khan, group vice president of KLA-Tencor's Parametric Solutions Group. "Across foundry, logic and memory, our customers require production-capable metrology systems that produce the data necessary to decipher complex process issues. Full-featured metrology systems, such as our new Archer 500LCM and SpectraFilm LD10 platforms, implement multiple innovations that facilitate measurement flexibility across a broad range of applications, helping our customers drive current-node yield and investigate next-node technologies."

With both imaging and unique laser-based scatterometry measurement technologies, the Archer 500LCM overlay metrology system offers a wide range of measurement options and supports a diverse range of overlay measurement target designs, such as in-die, small pitch and multi-layer targets. This flexibility enables cost-effective generation of accurate overlay error data that can be used for scanner corrections or for identification of inline excursions, helping engineers determine when to re-work wafers or adjust processes to meet strict patterning requirements. Multiple Archer 500LCM systems are in use at foundry, logic and memory manufacturers worldwide where they provide an independent assessment of overlay performance for advanced development and high volume production.

The SpectraFilm LD10 introduces a laser-driven plasma light source, producing reliable, high-precision film measurements for a broad range of film layers, including the thin, multilayer film stacks used in forming complex device structures such as FinFETs. Characterization of the thick, multilayer film stacks found in 3D NAND flash devices is enabled with a new infrared-based subsystem. With a significant increase in throughput compared to the previous-generation Aleris® platform, the SpectraFilm LD10 maintains high productivity while qualifying and monitoring the increased number of film layers associated with multi-patterning and other leading-edge fabrication techniques. Multiple SpectraFilm LD10 orders have been placed for use in advanced IC development and production. ◆

## **news**cont

#### Continued from page 7

"While smartphone display resolution and sizes reach new milestones, panel makers are still being challenged to reduce display module prices," said Terry Yu, analyst for small and medium displays and display technologies for IHS Technology, formerly with DisplaySearch. "Shipment and manufacturing of panels using various display technologies like a-Si, Oxide, LTPS and AMOLED continues to rise. while pricing continues to decline. The sharpest smartphone average panel price declines occurred in 2014, and this trend of double-digit declines is expected to continue in 2015."

Panel makers (like Tianma, BOE, InfoVision, and Japan Display Inc. (JDI) via their subsidiary TDI) are all promoting their products to Chinese smartphone makers with aggressive pricing strategies. Chinese smartphone makers are agile enough to use economies of scale and their strong market position to better negotiate display prices. On the supply side, LTPS LCD manufacturing capacity is increasing in all regions. Taiwanese panel suppliers are aggressively shifting production of smartphone panels to Gen 5 fabs, as well. These factors are adding pressure to reduce prices.

According to the Monthly Smartphone and Tablet PC FPD Pricing Report, 5-inch LTPS TFT LCD FHD (1920×1080) smartphone panels with IPS/FFS LCD technology, experienced a decline of 30 percent YoY, from \$30 in December 2013 to \$21 in December 2014.

"Smartphone ASPs will continue to drop substantially in the first quarter of 2015, which is a traditionally slow

season for smartphone display panel purchasing," Yu said.

The 5-inch 720 HD (1280×720 pixels) module is the most popular smartphone display size in China, helping the format to gain over 40 percent market share in the market global 5.x-inch space during 2014.

"Most brands are promoting lowpriced, high-specification models with these displays, especially on e-commerce platforms," Yu said. "China is the major battlefield for 5-inch smartphone displays. Demand for these displays is very strong, but they face strong competitive price pressure in the set market."

In China's open market, prices for 5-inch 720HD panels declined significantly to just under \$12 in December 2014. Business agreements aside, market pricing for low-specification 5.x-inch panels is expected to decline to about \$11 by March 2015. Prices of some low-grade specifications panels (lower brightness requirement) could decline to below \$10 by the same period.

Due to the booming demand for LTPS LCD in China, panel makers are expected to continue expanding their LTPS manufacturing capacities & shipment. "By the end of 2016, new fab investments by AUO, BOE, China Star, Tianma, and Foxconn will result in at least five Gen 6 LTPS fabs running in China and Taiwan, which may induce more pressure to reduce smartphone ASPs in the future," Yu said.

Another price-reduction pressure in the smartphone display market comes from aggressive smartphone endmarket pricing by Chinese smartphone brands. According to the Monthly Smartphone and Tablet PC FPD Pricing Report, after the introduction of the iPhone 6 Plus with its 5.5-inch FHD display, more Android-based premium models are expected to come equipped with wide-quad high-definition (WQHD) (2560×1440) displays driving FHD models down into the mid-range segment with lower pricing.

On December 23, 2014, Meizu, a rising brand in China, introduced its new "No Blue Note" smartphone, which was equipped with a 5.5-inch FHD display from Taiwan, which sells for just CNY 999 (\$161). This model and pricing has been cited by many in the industry as a warning for upcoming price competition in 2015.

"Facing ASP pressures, display cost reduction will be the top priority for the panel makers, especially through more effective production yield rate management and improvements in component performance," Yu said.

## Battling over Apple

Not since the Garden of Eden have we seen so much activity generated by an apple?

Recall, Apple signed up TSMC back in 2013 to produce its future A series processor chips while undergoing legal battles with Samsung their current provider. However, Apple has not been unable to completely disengage from Samsung. Both TSMC and Samsung produced the 22nm A8 processors for the iPhone 6, though TSMC had the majority of the order.

Now, according to South Korea's Maeil Business Newspaper, Apple has turned back to Samsung to manufacture its A9 chip. Reports are that Samsung will

get 75% of the chip production for the next iPhone.

Samsung reportedly began production of Apple's A9 in their Austin TX plant using the 14nm FinFET technology. Samsung has 14nm FinFET production capability in both Austin, and Giheung, Korea,

but will produce A9 only in Austin initially. I guess that this "technically" makes the chips "made in the USA."

Samsung also is putting significant pressure on Qualcomm with the pervasive rumors that Samsung will use its own microprocessors in the next version of the Galaxy S smartphone. Both Qualcomm and Samsung have declined comment.

Citing "people with direct knowledge of the matter," Bloomberg has reported that that Samsung, "... tested the new version of Qualcomm's Snapdragon chip, known as the 810, and decided not to use it". Qualcomm's Snapdragon processors, combined with its cellular baseband chips, have dominated the market for smartphones in recent years.

Qualcomm has faced rumors in recent months about potential overheating in the 810. While it is believed that Qualcomm has solved the 810's overheating

#### Packaging

problems, the issue has put Snapdragon 810 production a few

months behind schedule. Qualcomm has publically confirmed that it will no longer supply chips for a "large customer's flagship device". While the company did not confirm that this was Samsung,

the firm in question is big enough

for Qualcomm to lower its 2015

**Dr. Phil Garrou,** Contributing Editor

outlook in its first quarter fiscal financial results. It remains possible that Qualcomm will convince Samsung that they have fixed the overheating problem and be reinserted into the Samsung phone.

Samsung mass producing high-density ePoP memory Samsung has announced that the company will be mass producing the extremely thin ePoP (embedded package on package) memory, a single memory package

> consisting of 3GB LPDDR3 DRAM, 32GB eMMC and a controller for use in high-end smartphones (see photo).

> The 3GB LPDDR3 mobile DRAM inside the ePoP operates at an I/O data transfer rate of 1,866Mb/s, with a 64-bit I/O bandwidth.

Because of its "thinness and special heat-resistant properties," Samsung claims that the smartphone ePoP does not need any space beyond the 225 square millimeters (15 x 15mm x 1.4mm high) taken up by the mobile application processor. A conventional PoP (also 15 x 15mm), consisting of the mobile processor and DRAM, along with a separate eMMC (11.5mm by 13mm multimedia card) package, takes up 374.5 square millimeters. Replacing that set-up with a Samsung ePoP reportedly decreases the total area used by approx. 40%.

Samsung is basically stacking all the memory, both RAM and NAND, on a single ePoP module that's then positioned on top of the processor, rather than beside it.

The use of such ePoP chips seems to be a likely choice for the upcoming Galaxy S6. It is intended to be used in mobile devices packing 64-bit processors and 3GB of RAM which is what's rumored to be spec'ed in the Galaxy S6 and other top mobile devices later this year. ◆

## Proponents of EUV, immersion lithography face off at SPIE

The two main camps in optical lithography are arrayed for battle at the SPIE Advanced Lithography Symposium in San Jose, Calif.

Extreme-ultraviolet lithography, on one side, is represented by ASML Holding, its Cymer subsidiary, and ASML's EUV customers, notably Intel, Samsung Electronics, and Taiwan Semiconductor Manufacturing.

On the other side is 193i immersion lithography, represented by Nikon and its customers, which also include Intel and other leading chipmakers.

There are other lithography technologies being discussed at the conference, of course. They are bit players in the drama, so to speak, although there is a lot of discussion and buzz about directed self-assembly technology this week.

ASML broke big news on Tuesday morning, reporting that Taiwan Semiconductor Manufacturing was able to expose more than 1,000 wafers in one day this year with ASML's NXE:3300B EUV system. "During a recent test run on an NXE:3300B EUV system we exposed 1,022 wafers in 24 hours with sustained power of over 90 watts," Anthony Yen, TSMC's director of research and development, said at SPIE.

While ASML was obviously and justifiably proud of this milestone, after achieving its 2014 goal of producing 500 wafers per day, it cautioned that more development remains for EUV technology.

"The test run at TSMC demonstrates the capability of the NXE:3300B scanner, and moves us closer to our stated target of sustained output of 1,000 wafers per day in 2015," ASML's Hans Meiling, vice president service and

#### Semiconductors

product marketing EUV, said in a statement. "We must continue to increase source power, improve system availability, and show this result at multiple customers over multiple days."

The day before, Cymer announced the first shipment of its XLR 700ix light source, which is said to improver scanner throughput and process stability for manufacturing chips with 14-nanometer features. The company also debuted DynaPulse as an upgrade option

for its OnPulse customers. The XLR 700ix and DynaPulse together are said to offer better on-wafer critical dimension uniformity and provide stable on-wafer performance.

Another revelation at SPIE is that SK Hynix has been working with the NXE:3300, too, and is pleased with the system's capabilities. According to Chang-Moon Lim, who spoke Monday morning, SK Hynix was recently able to expose 1,670 wafers over three days, with uptime of 86.3 percent over that period.

"Progress has been significant on various aspects, which should not be overshadowed by the delay of [light] sources," he said of ASML's EUV systems.

The Korean chipmaker is exploring how it could work without pellicles on the EUV reticle, Lim noted. ASML has been developing a pellicle, made with polycrystalline silicon, in cooperation with Intel and others.

Nikon Precision and other Nikon subsidiaries didn't issue any press releases at SPIE. The companies presented much information at Sunday's LithoVision 2015 event, held at the City National Civic auditorium, across the street from the San Jose Convention Center, where SPIE Advanced Lithography is staged.

On offer at the Nikon conference was the claimed superiority of 193i immersion lithography equipment to EUV systems for the 14nm, 7nm and future process nodes. Donis Flagello, Nikon Research Corp. of America's president, CEO, and chief operating officer, emphasized that message on Tuesday morning with an invited paper on "Evolving optical lithography without EUV."

Nikon's champion machine is the NSR-S630D immersion scanner, which was touted throughout the LithoVision event. The system is capable of exposing 250 wafers per hour, according to Nikon's Yuichi Shibazaki.

www.solid-state.com

**Jeff Dorsch,** Contributing Editor

# Changes and challenges abound in multi-patterning lithography

#### JEFF DORSCH, contributing editor

Multi-patterning lithography is a fact of life for many chipmakers. Experts in the fields of electronic design automation and lithography address the issues associated with the technology. Providing responses are David Abercrombie, Design for Manufacturing Program Manager, Mentor Graphics; Gary Zhang, Vice President Marketing, ASML Brion; and Dr. Donis Flagello of Nikon Research Corporation of America.

# 1. What are the significant considerations in semiconductor manufacturing and design with multi-patterning lithography?

David Abercrombie: Like most process/design trade-offs moving from one node to another it comes down to cost vs area and performance. Without multi-patterning or EUV you will struggle do design at 20nm or below limiting the opportunity to take advantage of design area and performance scaling. Essentially, Moore's Law slows to a crawl without it. Multi-patterning affects almost all aspects of design and manufacturing. For physical design it adds additional design rule constraints and constrains cell placement and routing depending on cell architecture. For electrical design it adds additional parasitic variability to consider in timing analysis. For DFM it adds additional requirements for fill and lithographic checking. In manufacturing it adds additional masks, process steps and increases stepper utilization. All of these increase complexity and have an associated cost. It ultimately has to make business sense. Because of this you are seeing fewer companies moving to these advanced nodes as quickly as before, as they must have the volume and profit margins to justify the increased

cost. Fortunately, there are products that do need the newest and most advanced process nodes, and because of those needs we continue to move forward into these new technology nodes on a regular schedule.

**Gary Zhang:** Multiple patterning (MPT) using immersion lithography is required for the semiconductor industry to continue device scaling until extreme ultraviolet (EUV) comes into full production (EUV is expected for a mid-node insertion in the 10nm logic node, and for 7nm node development and production in the 2015-2017 time frame). Multiplepatterning lithography brings the following new challenges from design to manufacturing. ASML has been collaborating with the chipmakers in a holistic lithography framework to tackle these challenges with innovative hardware and software solutions, including scanner systems, computational lithography, metrology and process control.

Integrated circuit designs have to be multiple patterning compatible. Industry has been developing methods to enable MPT-compatible designs via layout decomposition (coloring) and conflict resolution using multiple patterning rules as constraints. This applies to standard-cell libraries, cell boundaries, and placement and route to ensure full chip layouts meet all manufacturing requirements and can be decomposed into separate masks without any postcoloring MPT conflicts. Structured layouts with highly restricted design rules seem to be a key enabler for MPT-compliant designs.

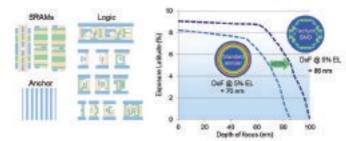

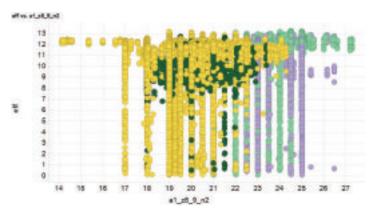

The rule-based approach to MPT compatible designs tends to run the risk of pattern defects from design hot spots, especially when design rules are pushed aggressively for competitive die size. The lithography process window of these design hot spots can be enlarged using source-mask optimization (SMO). Brion's Tachyon SMO has been routinely used to co-optimize scanner optics such as illumination source and projection lens wavefront and mask enhancements including sub-resolution assist features (SRAF) and optical proximity correction (OPC) for any given designs. Take triple patterning of a 10nm node metal layer as an example. Tachyon SMO enables a 23% larger process window for the selected SRAM and logic designs (FIGURE 1). By evaluating a range of design variations, SMO can help optimize design rules and MPT coloring rules to eliminate design hot spots in the technology development stage. For production mask data preparation, Brion's multiple patterning OPC and LMC (Lithography Manufacturability Check) are widely used by the leading chipmakers to deliver the best full chip process window in wafer manufacturing. A combination of SMO, OPC and LMC makes up ASML's process window enhancement solutions to the design hot spot problem.

Source-mask optimization improves triple patterning IMEC example: logic 10 nm node triple patterning metal 1 layer

- + 10 nm node metal 1: 48 nm min pitch, 3 splits, NTD and M3D models used

- + One common source optimized for all 3 splits, only imaging is considered

- · Overlapping process window depth of focus increased 23% with Tachyon SMD

**FIGURE 1.** Source-mask optimization (SMO) of a 10 nm node metal layer in triple patterning lithography. Overlapping process window of all three splits (masks) is improved by 23% for selected SRAM and logic patterns imaged with the same illumination setup. Source: ASML.

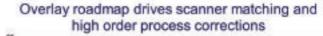

to be met for the exponentially increasing number of critical masks and metrology steps at 14nm and 10nm nodes. To deliver the required overlay control on product wafers, scanner matching and process control have to include high order corrections (**FIGURE 3**). ASML's latest generation of immersion scanners have a large number of flexible actuators and are capable of sub-3 nm matched-machine overlay, dynamic lens heating and reticle heating corrections, and high-order interfield and intrafield corrections for imaging, focus and overlay.

With the introduction of multiple patterning below 28 nm node, the increasing number of masks and metrology steps translates to lower wafer throughput per scanner and longer wafer cycle time from start to finish. This then leads to cost per wafer significantly

and overlay requirements to account for more process variations from the additional processing steps. Overlay is used here as an example to show the increasing complexity in multiple patterning process control from single exposure at 28nm node, to double patterning at 14nm node, to triple patterning at 10nm node (**FIGURE 2**). Tighter overlay specification has

higher than the historical cost scaling trend from the previous technology nodes. ASML has been continuously driving the scanner innovation to increase the throughput and improve productivity in terms of wafer output per day. ASML's YieldStar integrated metrology is another innovative solution to reduce wafer cycle time and improve

Multiple patterning drives tighter CD, focus

process control delivers

turability and yield in

volume production.

patterning brings a

host of issues due to

the added complexity

the most robust manufac-

Donis Flagello: Multiple

on-product performance for effective productivity gain and overall cost benefit.

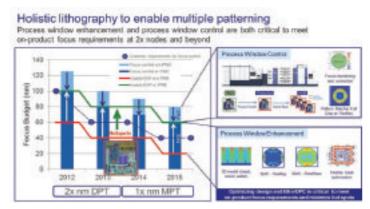

In summary, a full suite of design and manufacturing solutions are required to address the new challenges in multiplepatterning lithography. ASML has taken a holistic approach and worked in close collaboration with the chipmakers to optimize design, scanner, mask and process control altogether for the best manufacturability and yield. **FIGURE 4** gives an

**FIGURE 3.** On-product overlay roadmap showing the ever tighter specification from 28 nm node to 14 and 10 nm nodes and the requirement of advanced scanner correction capabilities (such as dynamic and high-order).Two different production scenarios are considered, namely scanner/chuck dedication and mix and match of different scanners. Source: ASML.

example on how holistic lithography enables focus roadmap down to 1x nm node. In the design phase, process window enhancement solutions such as SMO, OPC and LMC are used to eliminate the design hot spots and maximize the full chip process window. In the wafer manufacturing phase, process window control solutions such as scanner matching and high order corrections are implemented to optimize CD, overlay and focus control dynamically from tool to tool, field to field, wafer to wafer and lot to lot. A combination of the largest process window and the tightest

**FIGURE 4.** An example of how holistic lithography enables focus roadmap down to 1x nm node (DPT: double patterning; MPT: multiple patterning). A combination of process window enhancement and process window control solutions delivers robust manufacturability and yield in volume production. Source: ASML. associated with imaging and processing multiple patterns within the same design layer. From the exposure tool point of view, we need to ensure that the overall cost of ownership is maintained

and the tool can enable

further scaling. We are

concentrating on many aspects of the technology. One of the most critical is overlay. This must be as low as possible such that the ensemble overlay of all the exposures within a layer is equal or better than a single exposure. Simultaneously, we need to increase the throughput of the tools to ensure that cost per wafer per hour is also continuously improved. Both of these aspects drive a huge amount of innovation and technology development.

#### 2. How do you deal with color assignment?

**Abercrombie:** The answer to that depends on the foundry and layer being discussed. Colorless, partial coloring and full coloring flows exist. In colorless flows the designer does not assign colors. There are specialized checks (like odd cycle checks in double patterning) that make sure the layout can be decomposed into multiple masks later once the design is taped-out to the foundry. In a partial coloring flow most of the layout follows the colorless flow, but the designer can manually assigns some parts of the layout to a particular color to manage subtle variation concerns. For instance, making sure matched circuitry also has matched coloring. In a fully colored flow the designer is responsible for producing the final mask assignments for all polygons in the layer. A GDS layer is

dedicated to each mask. To assign a polygon to a given mask a copy of it is placed on the appropriate mask color layer. EDA companies provide various automation capabilities to assist with color assignment in custom, P&R and batch full chip applications.

It is best to use an EDA solution like Calibre that not only can address all different coloring flows but also provides the same checks/algorithms for all phases a design goes through from initial IP blocks to final full chip signoff.

**Zhang:** Layout decomposition or coloring has to deliver split patterns on separate masks which are free of any process rule violations and can then be patterned in single exposure with sufficient process

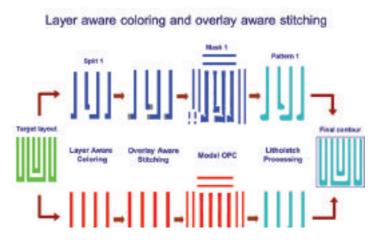

window. A double patterning (DPT) using a litho-etch-litho-etch process is shown as an example (FIGURE 5). In the DPT coloring step, any non-native color conflicts are resolved in a layer aware implementation with stitches that are properly located away from the overlap region between layers (such as a metal line contacting a via) and have the least impact on the device performance and manufacturing

**FIGURE 5.** An example of design to manufacturing work flow for a litho-etch-litho-etch double patterning (DPT) process, from layer aware coloring to overlay aware stitching, to model based OPC, to the final contour after litho and etch processes. Source: ASML.

yield. Process robust stitching must have sufficient overlap margin to tolerate misalignment between the exposures of the split masks. This is the concept of overlay aware stitching.

Color balancing is another critical care-about in layout decomposition. MPT coloring not only needs to deliver split layouts free of MPT conflicts but also has to ensure the pattern density is balanced between the split masks. Color balancing is beneficial for litho and etch process control so that robust and uniform patterning qualities can be achieved.

Coloring can also be optimized for best process window using a model based approach, as described

above in the "Design hot spots" section. Model-based coloring is not suitable for full chip application. It can be either used in source-mask optimization for MPT rule development or applied in local hot spot fix during the mask data preparation.

## 3. How does design rule check change? How is it the same?

**Abercrombie:** In a fully colored flow the design rules change slightly. First for every traditional spacing check there are essentially two checks for double patterning (DP): a minimum spacing for different colored polygons, and a larger minimum spacing for same colored polygons. In addition, there are usually

> additional density checks making sure the ratio between the colors is reasonably equal. In colorless flows specialized new checks have been developed to verify if a valid coloring exists for a given layout construct. In double patterning these specialized checks include odd cycle checks. For triple patterning (TP) and quadruple patterning (QP) new types of checks are required.

**Zhang:** Triple patterning (TPT) coloring is a lot more difficult and complex than DPT coloring. It is extremely hard to determine if a layout is TPT compatible, known as NP-complete problem in graph theory. There is no efficient way to find a solution on the full chip level. There are no existing methods for determining the number of conflicts and their locations.

Stitches are color-dependent in TPT and candidate stitch locations can be determined only after or during coloring.

Therefore it is important to ensure TPT compliance by design construct.

LITHOGRAPHY

Depending on the technology used, double exposure

results in much more of an optimization problem to

determine the best alignment strategy. Sometimes,

the previous layer alignment mark may have a poor

signal depending on the number of films involved in

the number of patterning steps increases some of the

complexity, the solutions become more of an optimi-

5. What issues in IC design and verification

the multiple-patterning schemes. While increasing

Mask alignment is usually based on the previous layer mark. However, moving to triple exposure often

from a tool perspective is more or less straightforward.

## 4. What are the complexities and issues in transitioning from double-patterning to triple-patterning?

Abercrombie: Although checking and decomposing a layout for two colors is complex, the algorithmic processing scales reasonably by design size. However, the generalized solution for triple and quadruple patterning has exponentially increasing run time as the number of polygons processed increases. This is, of course, is not a practical solution. So the problem must be constrained such that reasonable heuristic algorithmic approaches can be applied that provide reasonably scalable run times. So the complete set of design rules and design methodology need to be properly tuned to constrain the graph-complexity of the layouts produced so these checking and decomposition heuristic tools can be utilized. In addition, specialized checks may be needed so that layout constructs that do not meet the complexity constraints can be diverted from processing (to keep run time from exploding) and flagged to the user for modification until they can be properly processed.

The other challenge in moving from DP to TP and QP is colorless error visualization. If you are doing a colorless flow and need to check if the design can legally be colored, you need a way to highlight constructs for which no valid coloring solution exists in a way that the designer can understand so he/she can make changes in the layout to fix it. For DP this was odd cycle error visualization. An even-numbered cycle of interacting polygons can be colored and an odd numbered cycle of interacting polygons cannot. For TP and QP this is not the case. Any simple even or odd cycle can be colored. The constructs which cannot be colored are much more complex than in DP. In addition, narrowing down the implicated constructs to the "root" of the problem is more difficult. To address these issues Mentor Calibre is developing a new array of error visualization layers to help inform and guide the user to appropriate and productive fixes.

**Flagello:** Years ago many industry observers did not believe that double patterning was viable. Today double and triple patterning is being done. However, there are some key differences between the two.

Abercrombie:The designer should expect to seennew design rules, more parasitic variation, morehatcomplexity in design and methodology constraints,ityincreased wafer cost, and the need for new EDA toolskeepand additional CPU hardware to process their designs.er forThis is really not new as this increased complexity anded.cost has existed between every node transition. The

zation and controls challenge.

emerge with multi-patterning?

cost has existed between every node transition. The difference is that the delta may be more than between previous nodes. It is important that design teams educate themselves early on the impacts of moving to multi-patterned process nodes. That includes getting information from the foundry and EDA partners as well as reading available material on the subject.

**Zhang:** In addition to the power, performance and area metrics, designers now have to ensure their IC designs are MPT compliant and free of design hot spots so that they can be manufactured cost effectively with the best yield using multiple-patterning lithography. From lithography point of view, design hot spots are the major yield detractor. Device performance such as RC timing delay, cross talk, leakage (such as IDDQ), breakdown voltage and final yield is heavily influenced by MPT process variations. Brion's LMC has been used to evaluate the impact of realistic dose, focus, mask and overlay variations on MPT hot spots both intra-layer and interlayer. Identification of such MPT hot spots helps drive design and OPC improvements so that they can be eliminated in wafer manufacturing. 🚸

# Supplier Hub answers the needs of a changing semiconductor industry

#### LUC VAN DEN HOVE, imec, Leuven, Belgium

#### Supplier Hub answers the needs of a changing semiconductor industry

ur semiconductor industry is a cyclical business, with regular ups and downs. But we have always successfully rebounded, with new technologies that have brought on the next generation of electronic products. Now however, the industry stands at an inflection point. Some of the challenges to introduce next generation technologies are larger than ever before. Overcoming this point will require, in our opinion, a tighter collaboration than ever. To accommodate that collaboration, we have set up a new Supplier Hub, a neutral platform where researchers, IC producers, and suppliers work on solutions for technical challenges. This collaboration will allow the industry to overcome the inflection point and to move on to the next cycle of success, driven by the many exciting application domains that appear on the horizon.

#### Call for a new collaboration model

The formulas for the industry's success have changed. Device structures are pushing the limits of physics, making it challenging to continue progressing according to Moore's Law. Intricate manufacturing requirements make process control ever more difficult. Also chip design is more complex than ever before, requiring more scrutiny, analysis and testing before manufacturing can even begin. And the cost of manufacturing equipment and setting up a fab has risen exponentially, shutting out many smaller companies and forcing equipment and material suppliers to merge.

In that context, more and more innovation is coming from the supplier community, both from equipment and material suppliers. But as processes are approaching some fundamental limits, such as material limits, chemical, physical limits, it is also for suppliers becoming

more difficult to operate and develop next-generation process steps in an isolated way. An earlier and stronger interaction among suppliers is needed.

All this makes a central and neutral platform more important than ever. That insight and the requests we got from partners set imec on the path to organizing a supplier hub. A hub that is structured as a neutral, open innovation R&D platform, a platform for which we make a substantial part of our 300mm cleanroom floor space available, even extending our facilities. It is a platform where suppliers and manufacturers collaborate side-toside with the researchers developing next-generation technology nodes.

Organizing the supplier hub is a logical evolution in the way we have always set up collaborations with and between companies that are involved in semiconductor manufacturing. Collaborations that have proven very successful in the previous decade and that have resulted in a number of key innovations.

Supplier Hub off to a promising start

Today, both in logic and in memory, we are developing solutions to enable 7nm and 5nm technology nodes. These will involve new materials, new transistor architectures, and ever shrinking dimensions of structures and layers. At imec, the bulk of scaling efforts like these used to be done in collaborative programs involving IDMs and foundries, but also the fabless and fablite companies. All of these programs were strongly supported by our partnerships with the supplier community.

But today, to work out the various innovations in process steps needed for future nodes, we simply need this stronger and more strategic engagement from the supplier community, involving experimenting on the latest tools, even if they are still under development. And vice-versa, the tool and material suppliers can no longer only develop tools based on specs documents. To fabricate their products successfully and on time, they need to develop and test in a real process flow, and be involved in the development of new device concepts, to be able to fabricate tools and design process steps that match the requirements of the new devices.

A case in point: it is no longer possible now to develop and asses the latest generation of advanced litho without matching materials and etch processes. And reversely, the other tool suppliers need the result of the latest litho developments. So today, all process steps have to be optimized concurrently with other process steps, integrating material innovations at the same time. And this is absolutely necessary for success.

So that's where the Supplier Hub enters.

In 2013, imec announced an extended collaboration with ASML, involving the set up an advanced patterning center, which will grow to 100 engineers. In 2014, the new center was started as the cornerstone of the supplier hub. Mid 2014, Lam Research agreed to partake in the hub. And since then a growing number of suppliers has been joining, among them the big names in the industry. Some of more recent collaborations that we announced e.g. were Hitachi (CD-SEM metrology equipment) and SCREEN Semiconductor Solutions (cleaning and surface preparation tools).

End of 2014, ASML started installing its latest EUV-tool, the NXE:3300. In the meantime, we have initiated building a new cleanroom next to our existing 300mm infrastructure. The extra floor space will be needed to accommodate all the additional equipment that will come in in the frame of the tighter collaboration among suppliers. Finally, during our October 2014 Internal Partner Conference, we organized a first Supplier Collaboration Forum where the suppliers discussed and evaluated their projects with all partners, representing a large share of the semiconductor community.

We have also been expanding the supplier hub concept through a deeper involvement of material suppliers. These will prove a cornerstone of the hub, as many advances we need for scaling to the next nodes will be based on material innovations.

#### **Enabling the Internet-Of-Everything**

I hold great optimism for the industry. The last years, the success of mobile devices has fueled the demand for semiconductor-based products. These mobile applications will continue to stimulate data consumption, going from 4G to 5G as consumers clamor for greater data availability, immediacy, and access. Beyond the traditional computing and communications applications loom new markets, collectively called the 'Internet of Everything.'

In addition, nanoelectronics will enable disruptive innovations in healthcare to monitor, measure, analyze, predict and prevent illnesses. Wearable devices have already proven themselves in encouraging healthier lifestyles. The industry's challenge is now to ensure that the data delivered via personal devices meet medical quality standards. In that frame, our R&D efforts will continue to focus on ultra-low-power multi-sensor platforms.

While there are many facets to the inflection point puzzle, the answers of the industry begin to take shape. The cost of finding new solutions will keep on rising. Individual companies carry ever larger risks if their choices prove wrong. But through closer collaboration, companies can share that risk while developing solutions, exploring and creating new technologies, shorten times to market, and be ready to bring a new generation of products to a waiting world. The industry may indeed stand at an inflection point, but the future is bright. Innovation cannot be stifled. And collaboration remains the consensus of an industry focused on the next new thing. Today, IC does not just stand for Integrated Circuit, it indeed calls for Innovation and Collaboration. ◆

# Advanced analytics for yield improvement and zero defect in semiconductors

ANIL GANDHI, PH. D. and JOY GANDHI, Qualicent Analytics, Inc., Santa Clara, CA

Machine learning based advanced analytics for anomaly detection offers powerful techniques that can be used to achieve breakthroughs in yield and field defect rates.

n the last few decades, the volume of data collected in semiconductor manufacturing has grown steadily. Today, with the rapid rise in the number of sensors in the fab, the industry is facing a huge torrent of data that presents major challenges for analysis. Data by itself isn't useful; for it to be useful it must be converted into actionable information to drive improvements in factory performance and product quality. At the same time, product and process complexities have grown exponentially requiring new ways to analyze huge datasets with thousands of variables to discover patterns that are otherwise undetected by conventional means.

In other industries such as retail, finance, telecom and healthcare where big data analytics is becoming routine, there is widespread evidence of huge dollar savings from application of these techniques. These advanced analytics techniques have evolved through computer science to provide more powerful computing that complements conventional statistics. These techniques are revolutionizing the way we solve process and product problems in the semiconductor supply chain and throughout the product lifecycle. In this paper, we provide an overview of the application of these advanced analytics techniques

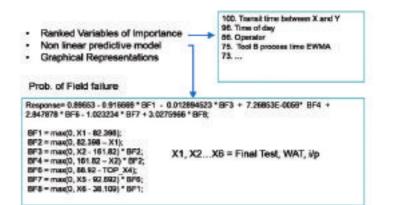

FIGURE 1. Predictive model example.

towards solving yield issues and preventing field failures in semiconductors and electronics.

Advanced data analytics boosts prior methods in achieving breakthrough yields, zero defect and optimizing product and process performance. The techniques can be used as early as product development and all the way through high volume manufacturing. It provides a cost effective observational supplement to expensive DOEs. The techniques include machine learning algorithms that can handle hundreds to thousands of variables in big or small datasets. This capability is indispensable at advanced nodes with complex fab process

**ANIL GANDHI, PH. D.** is President and Data Scientist and **JOY GANDHI** is chief marketing officer at Qualicent Analytics, Inc., Santa Clara, CA.

technologies and product functionalities where defects become intractable.

#### **Modeling target parameters**

Machine learning based models provide a predictive model of targets such as yield and field defect rates as functions of process, PCM, sort or final test variables as predictors. In the development phase, the challenge is to eliminate major systematic defect mechanisms and optimize new processes or products

to ensure high yields during production ramp. Machine learning algorithms reduce the number of variables from hundreds to thousands to the few key variables of importance; this reduction is just sufficient to allow nonlinear models to be built without over fitting. Using the model, a set of rules involving these key variables are derived. These rules provide the best operating conditions

to achieve the target yield or defect rate. **FIGURE 1** shows an example non-linear predictive model.

**FIGURE 2** is another example of rules extracted from a model, showing that when all conditions of the rule are valid across the three predictors simultaneously, then this results in lower yield. Discovering this signal with standard regression techniques failed because of the influence of a large number of manufacturing variables. Each of these large number of variables has a small and negligible influence individually, however they all combine to create noise and thus masking the signal. Standard regression techniques, available in commercial software, therefore are unable to detect the signal in these instances and therefore are not of practical use for process control. So how do we discover the rules such as the ones shown in Fig. 2?

#### **Rules discovery**

Conventionally, a parametric hypothesis is made based on prior knowledge (process domain

knowledge) and then the hypothesis is tested. For example to improve an etest metric such as threshold voltage one could start with a hypothesis that connects this backend parameter with RF power on an etch process in the frontend. However many times it is impossible to make a hypothesis based on domain knowledge because of the complexity of the processes and the variety of possible interactions, especially across several steps. So alternatively, a generalized model with cross terms is proposed and

Variables M, & and T taken together exert significant initiance on yield

**FIGURE 2.** Individual parameters M, Q and T do not exert influence while collectively they create conditions that destroy yield. Machine learning methods help discover these conditions.

then significant coefficients are picked and the rest are discarded. This works if the number of variables is small but fails with large number of variables. With 1100 variables (a very conservative number for fabs) there are 221 million possible 3-way interactions, and 60 million 2-way cross terms on top of the linear coefficients!

Fitting these coefficients would require a number of samples or records that are clearly not available in the fab. Recognizing that most of the variables and interactions have no bearing on yield, we must then reduce the feature set size (i.e. number of predictors) within a healthy manageable limit (< 15) before we apply any model to it; several machine learning techniques based on derivatives of decision trees are available for feature reduction. Once the feature set is reduced then exact models are developed using a palette of techniques such as those based on advanced variants of piece-wise regression.

In essence, what we have described above is discovery of the hypothesis, while more traditionally one starts with a hypothesis...to be tested. The example in Fig. 2 had 1100 variables most of which had no influence, six of them have measurable influence (three of them are shown), all of these were hard to detect because of dimensional noise.

The above type of technique is part of a group of methods classified as supervised learning. In

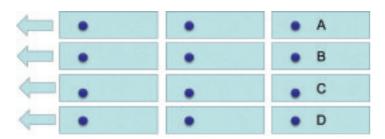

**FIGURE 3.** Solar manufacturing line conveyor, sampled at four points for colorimetry.

this type of machine learning, one defines the predictors and target variables and the technique finds the complex relationships or rules governing how the predictors influence the target. In the next example we include the use of unsupervised learning which allows us to discover clusters that reveal patterns and relationships

YIELD

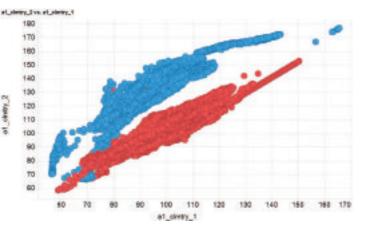

**FIGURE 4.** The ratios between 1, 2, 3 and 4 colorimetry were found to have clusters and the clusters corresponded to date separation.

led to DATE as the determining variable for the clusters.

Ultimately the goal was to create a model for cell efficiency. Feature reduction described earlier is performed followed by advanced piecewise regression and the resulting model based on 10 fold cross validation (build model on 80% of data and test against rest 20% and do this 10 times with a different random sample each time) results in a

> complex non-linear model with key element that includes a 3 way interaction as shown in **FIGURE 5**, where the dark green area represents the condition that drops the median efficiency by 30% from best case levels. This condition Colorimetry < 81, Date > X and N2 < 23.5 creates the exclusion zone that should be avoided to improve cell efficiency.

#### Advanced anomaly

between predictors which can then be connected to the target variables.

**FIGURE 3** shows a solar manufacturing line with four panels moving on a conveyor. The end measure of interest that needed improvement was cell efficiency. Measurements are made at the anneal step for each panel as shown at locations 1, 2, 3, 4 in **FIGURE 4**. The ratio between measurement sites with respect to a key metric called Colorimetry, was discovered to important; the way this was discovered was by employing clustering algorithms, which are part unsupervised learning. This ratio was found in subsequent supervised model to influence PV solar efficiency as part of a 3-way interaction.

In this case, without the use of unsupervised machine learning methods, it would have been impossible to identify the ratio between two predictors as an important variable affecting the target because this relationship was not known and therefore no hypothesis could be made for testing it among the large number of metrics and associated statistics that were gathered. Further investigation