OCTOBER 2014

# Sold State TECHNOLOGY

Insights for Electronics Manufacturing

Threshold Voltage Tuning for 10nm P. 23

Managing Oxide Growth

P. 31

Understanding Reed Relay Specs P. 34

# SEMICON Europa Heads to Grenoble P. 14

MEDIA

MAY 19-22, 2015 the Encore at the Wynn Las Vegas Meet face-to-face with an exclusive group of influential executives representing the top semiconductor manufacturing companies from around the globe.

# THE POWER OF ONE EVENT

Hear market insights, technology forecasts and strategic assessments of the challenges & opportunities facing the semiconductor manufacturing industry

Network with the people that matter

Engage in strategic business meetings with senior-level purchasing decision makers & influencers

For more information, please contact: Sabrina Straub, Sales Manager 603.770.6569 sstraub@extensionmedia.com

Owned and Produced by:

www.theconfab.com

Presented by:

OCTOBER 2014 VOL. 57 NO.7

The iconic "bubble" cable cars in Grenoble, home to SEMICON Europa 2014.

#### FEATURES

#### BUSINESS | SEMICON Europa heads to Grenoble

All parts of the semiconductor supply chain will come together at the ALPEXPO center in Grenoble, France. *Pete Singer, Editor-in-Chief*

TRANSISTORS | Threshold voltage tuning for 10nm and beyond CMOS integration

A novel metal gate integration scheme to achieve precise threshold voltage (VT) control for multiple VTs is described. *Naomi Yoshida, et al, Applied Materials, Santa Clara, CA*

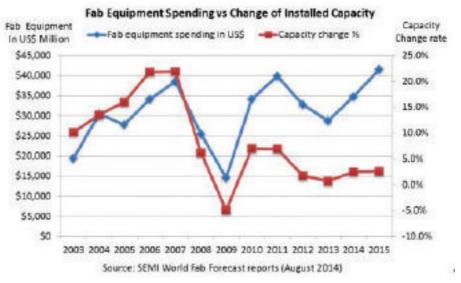

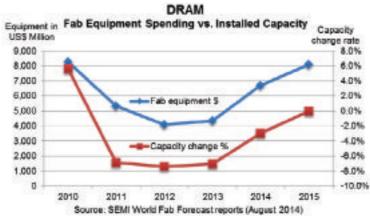

#### BUSINESS | Outlook: Healthy equipment spending into 2015

Equipment spending shows strong growth for 2014 and 2015; slow capacity additions. *Christian Gregor Dieseldorff, SEMI, San Jose, CA*

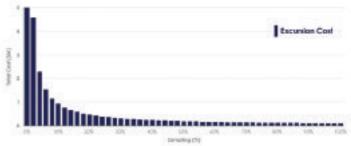

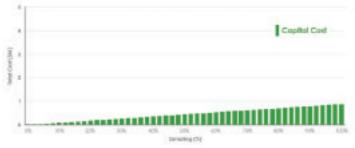

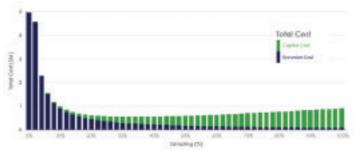

#### **INSPECTION** | Process Watch: Sampling matters

An optimum sampling strategy comes down to weighing the cost of process control against the benefit of capturing the defect or other excursion in a timely manner. David W. Price And Douglas G. Sutherland, KLA-Tencor, Milpitas, CA

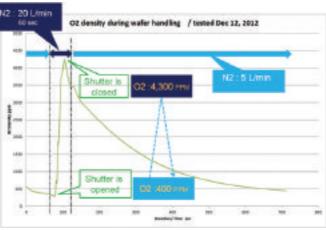

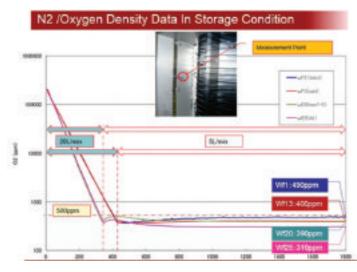

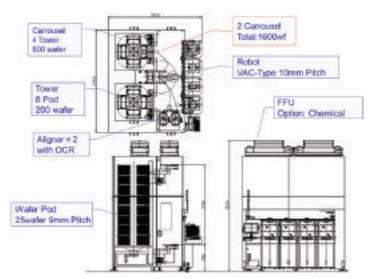

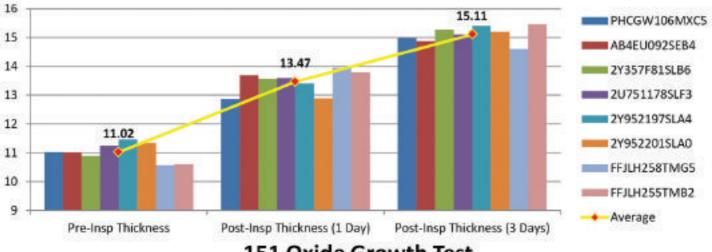

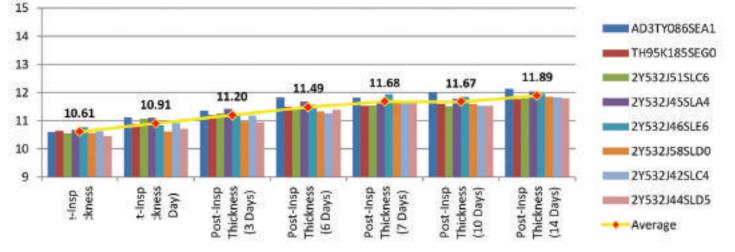

WAFERS | Managing oxide growth on in-process storage wafers for cost and yield impact

A system is described that mitigates unintended oxide growth for bare wafers while in-process storage and potentially post process at tools using nitrogen purge. *Suresh Biligiri, Rorze Automation, Fremont, CA*

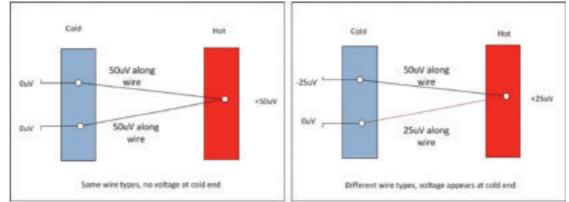

#### TESTING | The mystery of reed relays: Understanding specifications

Specifications of reed relays, which are used for current switching in ATE and other applications are explained, including carry current, lifetime, minimum switch capacity, hot switching, operating speed and thermoelectric switching. *Kevin Mallett, Pickering Electronics, Clacton-on-Sea, Essex, U.K.*

#### COLUMNS

- 3 Editorial A salute to European technology, Pete Singer, Editor-in-Chief

- 11 Packaging Intel announces EMIB, Phil Garrou, Contributing Editor

- 12 Semiconductors EUV and mask complexity, Jeff Dorsch, Contributing Editor

- **41** Industry Forum Foundry, EDA partnership eases move to advanced process nodes, *Dr. Lianfeng Yang, ProPlus Design Solutions, Inc.*

#### DEPARTMENTS

- 2 Web Exclusives

- 4 News

- **38** Europa New Products

- 40 Ad Index

# online@www.solid-state.com

### Web Exclusives

# Insights from the Leading Edge: ECTC Coverage

The advent of 2.5 and 3DIC has caused revisions in the way area array bump interconnect is carried out. Dr. Phil Garrou reviews presentations from ECTC on thermo-compression bonding, breaking down sessions hosted by Qualcomm, STATSChipPAC and Toray.

http://bit.ly/XoPlBi

### Leti integrates everything

Ed Korczynski knows how wafers feel when moving through a fab. From SemiMD, part of the Solid State Technology network.

http://bit.ly/1qhwUp8

# Monolithic 3D breakthrough at IEEE S3S 2014

In the upcoming 2014 IEEE S3S conference (October 6-9), MonolithIC 3D will unveil a breakthrough flow that is game-changing for 3D IC. For the first time ever monolithic 3D ("M3DI") could be built using the existing fab and the existing transistor flow. From SemiMD, part of the Solid State Technology network.

http://bit.ly/1toHkta

### Internet of Things infographic

The global IoT market is poised for explosive growth. By 2020, the market is expected to soar to \$7.1 trillion. This infographic, courtesy of Jabil, gives an good overview of what will be connected (even garbage bins!). http://bit.ly/1wsXh17

### Design and manufacturing technology

The fabless-foundry relationship in commercial IC manufacturing was established during an era of fab technology predictability—clear litho roadmaps for smaller and cheaper devices—but the future of fab technology seems unpredictable. The complexity which must be managed by a fabless company has already increased to justify leaders such as Apple or Qualcomm investing in technology R&D with foundries and with EDAand OEM-companies. To gain some insight into these issues, we recently asked leading industry visionaries to answer a few questions. http://bit.ly/1meaaLx

#### **Sensory Shanghai**

Stephen Whalley was in Shanghai to cohost the inaugural MEMS Industry Group (MIG) Conference Shanghai, September 11-12th, with local partners, the Shanghai Industrial Technology Research Institute (SITRI) and the Shanghai Institute of Microsystem and Information Technology (SIMIT). The theme was the Internet of Things and how the MEMS and Sensors supply chain needs to evolve to address the explosive growth in China. http://bit.ly/1miQdn2

#### Intel releases new packaging, test technologies for 14nm foundries

Intel Corporation announced two new technologies for Intel Custom Foundry customers that need cost-effective advanced packaging and test technologies. http://bit.ly/1tpbEnk

#### Scientists craft a semiconductor only three atoms thick

Scientists have developed what they believe is the thinnest-possible semiconductor, a new class of nanoscale materials made in sheets only three atoms thick. http://bit.ly/1wlJLcC

### What's in a name? Innovation for humanity

The project names Gooru, Nanoly, and Sanergy are intriguing. The fact these names represent efforts all over the world, from India to Latin America to Africa, peaks curiosity. And, the actual work of the 2014 Tech Laureates is absolutely amazing. From SemiMD, part of the Solid State Technology network. http://bit.ly/1svTRqp

## A salute to European technology

I'm looking forward to SEMICON Europa this month, which will be held for the first time in France, in Grenoble. There's not a big airport, so I'm flying into Geneva and hopping on a bus for a 2 hour ride (the other choice is Lyon, which is closer but a bit more expensive to fly into). I suspect this might also be the first SEMICON that is not close to a major airport,

### "I hope to see you in Grenoble!"

but Heinz Kundert, president of SEMI Europe, tells me that the show will be 40% larger than it was last year in Dresden. It also has an impressive 70 sessions with 300 speakers.

Europe has always been a powerhouse when it comes to semiconductor research. The work at imec, CEA-Leti and Fraunhoffer alone is truly amazing and world class. The challenge has always been taking that research and commercializing it. Part of that challenge is that the bulk of the world's semiconductor manufacturing is not in Europe, but in Asia and the U.S.

Yet there are significant manufacturing operations in Europe, notably fabs run by Infineon,

STMicroelectronics, GlobalFoundries, Bosch, TI, NxP, Altis, LFoundry, Philiips Lumileds, XFAB, AMS, Analog Devices and Freescale.

Like Europe itself, these fabs are diverse. There's a large variety in the products they produce, volume, wafer size, technology and even the level of automation.

What's promising is that this diversity could actually work to Europe's advantage when it comes to the booming application in IoT and biomedical. As Kundert notes in this month's cover story, "It's a big challenge, but we believe if somebody can manage it successfully, it's Europe. We are very experienced in those types of applications," he said.

Supporting all of this is the "10-100-20" program announced last year. It's an ambitious strategy to double the economic value of semiconductor production in Europe in the 2020-2025 timeframe. This goal is to achieve this by an unprecedented public/ private investment partnership with 10 billion Euros in public/private funding and 100 billion Euros from the industry. I believe the research and desire is there, so it will be interesting to see how that unfolds. I hope to see you in Grenoble!

-Pete Singer, Editor-in-Chief

# Solid Stat

Pete Singer, Editor-in-Chief Ph: 978.470.1806 psinger@extensionmedia.com Shannon Davis, Editor, Digital Media

Ph: 603.547.5309 sdavis@extensionmedia.com

Phil Garrou, Contributing Editor Ed Korczynski, Senior Technical Editor,

edk@extensionmedia.com Jeff Dorsch, Contributing Editor

Dick James, Contributing Editor

Vivek Bakshi, Contributing Editor

Sara Ver-Bruggen, Contributing Editor, Semiconductor Manufacturing & Design

#### CREATIVE/PRODUCTION/ONLINE

Spryte Heithecker, Production Manager Yishian Yao. Media Coordinator

Nicky Jacobson, Senior Graphic Designer Caldin Seides, Graphic Designer

Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION Jenna Johnson. jjohnson@extensionmedia.com

2343. (8 am - 5 pm, PST).

#### **CORPORATE OFFICERS**

Extension Media, LLC Vince Ridley, President and Publisher vridley@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, **Business Development** msterling@extensionmedia.com

October 2014, Volume 57, Number 7 • **Solid State Technology** ©2014 (ISSN 0038-111X) **Subscriptions:** Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 elsewhere. Digital distribution: \$130.00, You will continue to receive your subscription free of charge. This fee is only for airmail delivery. Address correspondence regarding subscriptions (including change of address) to: *Solid State Technology, 1786 18th Street, San Francisco, CA 94107-*274.09 m. 5 m. PST.

#### For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2014 by Extension Media LLC. All rights reserved. Printed in the U.S.

#### Extension

MEDIA

1786 18th Street San Francisco, CA 94107

SOLID STATE TECHNOLOGY **OCTOBER 2014** 3

Please send news articles to sdavis@extensionmedia.com

#### worldnews

**USA** | David Bell joined **Triad Semiconductor's** board of directors.

ASIA Oxford Instruments launched its third annual Indian nanotechnology seminars in Kolkata and Delhi.

USA GLOBALFOUNDRIES and the Semiconductor Research Corporation announced a new research scholarship program for undergraduate engineering students.

**EUROPE** | **Element Six** was selected by the European Commission's Seventh Framework Programme for Research and Technological Development to help develop a new ultrafast pulse disk laser.

**USA** | **NVIDIA** filed complaints against Samsung and Qualcomm for allegedly infringing NVIDIA GPU patents.

ASIA Samsung adopted ProPlus Designs' 14nm FinFET process.

**USA** | **SEMI** successfully appealed to the U.S. government to review the validity of current export controls on semiconductor etch equipment.

ASIA | SEMICON Taiwan was held in Taipei.

#### USA | GLOBALFOUNDRIES

announced that Louis "Lou" Lupin joined the company as senior vice president and chief legal officer.

ASIA | United Microelectronics Corporation (UMC) will join Fujitsu's new foundry company.

USA UC Santa Barbara researchers developed ultra sensitive biosensor from molybdenite semiconductor.

# news

# For electronics beyond silicon, a new contender emerges

Silicon has few serious competitors as the material of choice in the electronics industry. Yet transistors, the switchable valves that control the flow of electrons in a circuit, cannot simply keep shrinking to meet the needs of powerful, compact devices; physical limitations like energy consumption and heat dissipation are too significant.

Now, using a quantum material called a correlated oxide, Harvard researchers have achieved a reversible change in electrical resistance of eight orders of magnitude, a result the researchers are calling "colossal." In short, they have engineered this material to perform comparably with the best silicon switches.

The finding arose in what may seem an unlikely spot: a laboratory usually devoted to studying fuel cells—the kind that run on methane or hydrogen—led by Shriram Ramanathan, Associate Professor of Materials Science at the Harvard School of Engineering and Applied Sciences (SEAS). The researchers' familiarity with thin films and ionic transport enabled them to exploit chemistry, rather than temperature, to achieve the dramatic result.

Because the correlated oxides can function equally well at room temperature or a few hundred degrees above it, it would be easy to integrate them into existing electronic devices and fabrication methods. The discovery, published in Nature Communications, therefore firmly establishes correlated oxides as promising semiconductors for future three-dimensional integrated circuits as well as for adaptive, tunable photonic devices.

#### **Challenging silicon**

Although electronics manufacturers continue to pack greater speed and functionality into smaller packages, the performance of silicon-based components will soon hit a wall.

"Traditional silicon transistors have fundamental scaling limitations," says Ramanathan. "If you shrink them beyond a certain minimum feature size, they

Continued on page 7

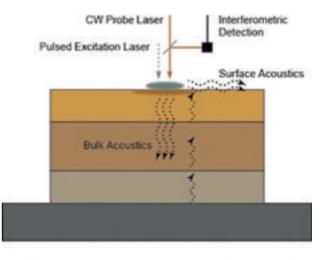

#### Rudolph introduces new acoustic metrology and defect inspection technology for 3DIC and advanced packaging applications

Rudolph Technologies has introduced its new SONUS Technology for measuring thick films and film stacks used in copper pillar bumps and for detecting defects, such as voids, in through silicon vias (TSVs). Copper pillar bumps are a critical component of many advanced packaging technologies and TSVs provide a means for signals to pass through multiple vertically stacked chips in three dimensional integrated circuits

Continued on page 6

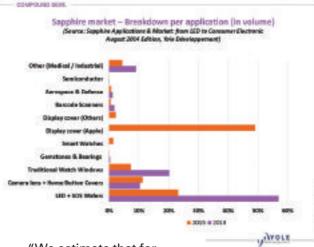

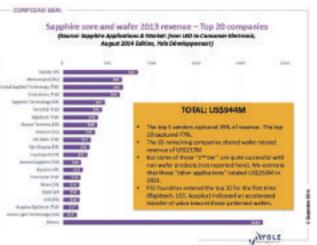

### Sapphire display covers featured in Apple smart watches but not in iPhone 6

The long wait is finally over. From a sapphire industry standpoint, Apple killed the suspense within the first 10 minutes by announcing that its new 4.7" and 5.5" iPhone 6 and iPhone 6 plus will both feature a traditional ion-exchange strengthened glass display cover. Sapphire remains in the camera lens cover and the touch ID sensor, features that were already present on the iPhone5 S.

In its recent report on the sapphire industry, Yole Développement analysts wrote that they believe that technical and manufacturing issues at various levels of the supply chain have prevented Apple from using

Continued on page 8

## Fairchild Semiconductor to close two facilities, cutting 15% of workforce

Fairchild Semiconductor announced it will eliminate its internal five-inch and significantly reduce six-inch wafer fabrication lines, resulting in the closure of its manufacturing and assembly facilities in West Jordan, Utah and Penang, Malaysia, as well as the remaining fiveinch wafer fabrication lines in Bucheon, South Korea.

Following the moves, Fairchild will operate production lines using eight-inch wafers in Maine and Pennsylvania, and retain one six-inch factory in Bucheon.

"Fairchild will also continue operating assembly and test facilities in Cebu, Philippines and Suzhou, China," said Mark Thompson, Fairchild's chairman and CEO.

Continued on page 10

# **news**cont

#### Continued from page 4

(3DIC). The new SONUS Technology is non-contact and non-destructive, and is designed to provide faster, less costly measurements and greater sensitivity to smaller defects than existing alternatives such as X-ray tomography and acoustic microscopy.

"SONUS Technology meets a critical need for measuring and inspecting the structures used to connect chips to each other and to the outside world," said Tim Kryman, Rudolph's director of metrology product management. "Copper pillar bumps and TSVs are critical interconnect technologies enabling 2.5D and 3D packaging. The mechanical integrity of the interconnect and final device performance are directly dependent on tight control of the plating processes used to create copper pillar bumps. Likewise, the quality of the TSV fill is critical to the electrical performance of stacked devices. This new technology allows us to measure individual films and film stacks with thicknesses up to 100µm, and detect voids as small as 0.5µm in TSVs with aspect ratios of 10:1 or greater."

Kryman added, "SONUS Technology builds on the expertise we developed in acoustic metrology for our industry-standard MetaPULSE systems, which are widely used for front-end metal film metrology. By offering similar improvements in yield and time-to-profitability in high volume manufacturing (HVM), SONUS offers a compelling value proposition to advanced packaging customers."

Both MetaPULSE and SONUS systems use a laser to initiate an acoustic disturbance at the surface of the sample. As the acoustic wave travels down through the film stack, it is partially reflected at interfaces between different materials. Although the detection schemes are different, the reflected waves are detected when they return to the surface and the elapsed time is used to calculate the thickness of each layer. In the case of SONUS Technology, two lasers are used. The first laser excites the sample and the second probes for the returning acoustics. This decouples excitation and detection allowing SONUS to continuously probe the sample resulting in a much larger film thickness range. So, where MetaPULSE can measure metal films and stacks to ~10 microns, SONUS can measure films in excess of 100 microns. In addition, SONUS Technology's use of interferometry to characterize the surface displacement provides a rich data set that can be analyzed to not only characterize film thickness, but perform defect detection.

15V V0105

The primary alternatives for such measurements are X-ray based tomographic analysis and acoustic microscopy. SONUS Technology's ability to detect voids as small as half a micrometer is approximately twice as good as current X-ray techniques, which have a spatial resolution of about 1 micrometer. Acoustic microscopy can make similar measurements, but the sample must be immersed in water, which, though not strictly destructive, does effectively preclude the return of the sample to production. SONUS is both non-contact and non-destructive and is designed for R&D and high-volume manufacturing.

In the run up to the product introduction, Rudolph worked closely with TEL NEXX to develop SONUS-based process control for pillar bump and TSV plating processes. Arthur Keigler, chief technology officer of TEL NEXX, said, "We are attracted by the opportunity SONUS Technology offers our mutual customers in the advanced packaging market. The ability to measure multi-metal film stacks for Cu pillar, and then continue to use the same tool for TSV void detection offers immediate productivity and cost benefits to manufacturing and development groups alike."

While Rudolph is initially focused on using the technology for copper pillar bump process metrology and TSV inspection, they are also investigating other applications, ranging from detecting film delamination to metrology and process control for MEMS fabrication processes.

# **NEWS**cont

#### Continued from page 4

don't quite behave as they should."

Yet silicon transistors are hard to beat. with an on/off ratio of at least 104 required for practical use. "It's a pretty high bar to cross," Ramanathan explains, adding that until now, experiments using correlated oxides have produced changes of only about a factor of 10, or 100 at most, near room temperature. But Ramanathan and his team have crafted a new transistor, made primarily of an oxide called samarium nickelate, that in practical operation achieves an on/off ratio of greater than 105-that is, comparable to state-of-the-art silicon transistors. In future work the researchers will investigate the device's switching dynamics and power dissipation; meanwhile, this advance represents an important proof of concept. "Our orbital transistor could really push the frontiers of this field and say, you know what? This is a material that can challenge silicon," Ramanathan says.

#### Solid-state chemical doping

Materials scientists have been studying the family of correlated oxides for years, but the field is still in its infancy, with most research aimed at establishing the materials' basic physical properties.

"We have just discovered how to dope these materials, which is a foundational step in the use of any semiconductor," says Ramanathan.

Doping is the process of introducing different atoms into the crystal structure of a material, and it affects how easily electrons can move through it—that is, to what extent it resists or conducts electricity. Doping typically effects this change by increasing the number of available electrons, but this study was different. The Harvard team manipu-

A new type of correlated transistor where the transistor action is gated by an ionic field. Image courtesy of Jian Shi.

lated the band gap, the energy barrier to electron flow.

"By a certain choice of dopants—in this case, hydrogen or lithium—we can widen or narrow the band gap in this material, deterministically moving electrons in and out of their orbitals," Ramanathan says. That's a fundamentally different approach than is used in other semiconductors. The traditional method changes the energy level to meet the target; the new method moves the target itself.

In this orbital transistor, protons and electrons move in or out of the samarium nickelate when an electric field is applied, regardless of temperature, so the device can be operated in the same conditions as conventional electronics. It is solid-state, meaning it involves no liquids, gases, or moving mechanical parts. And, in the absence of power, the material remembers its present state—an important feature for energy efficiency.

"That's the beauty of this work," says Ramanathan. "It's an exotic effect, but in principle it's highly compatible with traditional electronic devices."

#### **Quantum materials**

Unlike silicon, samarium nickelate and other correlated oxides are quantum materials, meaning that quantum-

Continued on page 10

A PASSION FOR PERFECTION

Energy efficient dry multi-stage process pumps for all applications in semiconductor industry

- Low energy consumption

Improved temperature management to optimize the pump

- according to your process

Protection of the pump against precursor cracking or condensable deposition

- Corrosion resistant and high particle tolerance

- Extended monitoring functionalities

### Are you looking for a perfect vacuum solution? Please contact us:

Pfeiffer Vacuum Headquarters/Germany T +49 6441 802-0 F +49 6441 802-1202 info@pfeiffer-vacuum.de

www.pfeiffer-vacuum.com

# **NEWS**cont

Continued from page 5

sapphire as the display cover in this year iteration of its iPhone. An important feature of the design of the new iPhone is that the case doesn't wrap around the display cover. To protect the edges and, more specifically the corners, the part features a complex shape with smooth curves. This design resulted in fairly low finishing yields with sapphire which drove the cost to above \$40 per part.

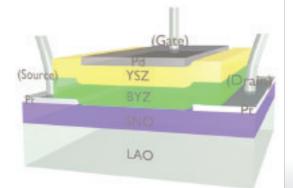

Apple focused the show on the long anticipated smart watch, announced in three customizable versions named "Apple Watch", "Apple Watch Sport" and "Apple Watch Edition". Both the "Watch" and "Edition" versions feature a sapphire display cover on the front. On the back, a zirconia ceramic cover with four sapphire lenses protects a heart rate sensor. The "Sport" model however relies on strengthened ion-exchange glass for the display cover and the lenses. The watches come in 2 case sizes of 38 and 42 mm. The sapphire display cover is a 2.5D design with a surface curved toward the edges that blends in smoothly with the watch case.

"We estimate that for the largest model,

those covers are manufactured from long sapphire bars of 40 x 34 mm cross section sliced at a pitch of about 1.8 mm," said Dr Eric Virey, Senior Analyst at Yole Développement. "The 4 lenses on the back appear to have dimensions fairly similar to the one featured on the iPhone camera lens cover," he adds. The watches however won't be available until "early 2015."

This raises the question of the status of GTAT mega-sapphire plant in Mesa, Arizona. The company might have to wait another year for an opportunity of a design win in the next iPhone. On a positive side, the company and the downstream supply chain might use this additional time to debottleneck

their process and possibly take the "Hyperion" lamination technology from advanced R&D to a manufacturingready level that could bring a real disruption in the way to use sapphire in displays.

But for now, smart watches won't provide enough upside to hit initial revenue targets. Apple currently sources

sapphire for this product from multiple suppliers, most located in China. "Even if GTAT was supplying a significant fraction of Apple smart watches, we estimate that total revenue derived from this opportunity wouldn't exceed \$45m in 2014, far from the company's initial revenue guidance for its sapphire business," said Eric Virey. "If Apple wants to help GTAT, it could also shift more of its other sapphire needs away from its current suppli-

ers. Under those circumstances, it will also be interesting to see if GTAT revises guidance for 2014 and if it receives the last US\$139M installment of the \$578M of prepayment promised by Apple before the end of the year. If so, this would show that Apple still supports GTAT and the overall project. GTAT was initially expected to start paying back this sum over quarterly installments starting in 2015 and we'll also see if Apple tries to enforce this," he commented.

Apple has nevertheless generated a lot of excitement in the sapphire industry since the announcement of its partnership with GTAT. It remains to be seen if, after adopting sapphire for the camera lens cover in 2012 and in the home button in 2013, the Apple Watch announcement is the last stop or just another step of the journey. Various OEMs have recently introduced smartphones featuring sapphire display covers. Kyocera introduced its sapphire Brigadier to the US Market in August and on September 4th, Huawei announced its "P7 Sapphire edition."

Xiaomi, a fast growing Apple competitor on the Chinese market also plans a limited edition featuring sapphire.

# **news**cont.

Continued from page 5

operating assembly and test facilities in Cebu, Philippines and Suzhou, China," said Mark Thompson, Fairchild's chairman and CEO.

In its official release, Fairchild said these cuts are a part of Fairchild's ongoing initiative to enhance manufacturing capabilities, improve product quality, and lower costs resulting in greater supply chain flexibility and responsiveness for our customers.

Closures of both facilities and Fairchild's remaining five-inch wafer fabrication lines in Bucheon, South Korea, are planned to occur from Q2 to Q4 2015.

"An adaptive supply chain must be the foundation of any global manufacturer's operations in the increasingly dynamic semiconductor solutions market," said Mr. Thompson. "The realignment we are announcing will maximize the utilization of eight-inch factories and reduce the complexity of our manufacturing footprint, while creating the flexibility to support ongoing customer demand through a greater use of external manufacturing sources. Fairchild will continue operating eight-inch wafer fabrication lines in South Portland, Maine and Mountain Top, Pennsylvania, as well as the Bucheon six- and eight-inch fabrication lines."

Through the combined actions, Fairchild expects to incur approximately \$36 million in cash restructuring and other costs. The company also plans to record during the closure process non-cash charges of approximately \$25 million for accelerated depreciation. Once completed, the company expects to realize annual savings of approximately \$45 to \$55 million from a second quarter of 2014 financial baseline. Of these estimated savings, approximately 75 percent are expected to be cash savings, with the balance attributable to lower depreciation costs. ◆

To the exception of Kyocera's Brigadier, which specifically targets the market of rugged smartphone, most of those announcements were intended at testing the market and showing capabilities ahead of a possible Apple announcement. None will come anywhere close to the iPhone in term of volume potential.

This September 9th event might therefore signals the death of sapphire as a display cover in smartphones. But after the tremendous buzz generated by the Apple and GTAT partnership, and following the positive reviews received by the first sapphire smartphones, the lack of a "sapphire iPhone" announcement might instead create a vacuum that Apple competitors will be eager to fill before Apple potentially enters the market.

"In any case, 2015 will be a pivotal year: the idea of using the material for smartphones display covers will either materialize in multiple devices and transform the industry, or just crash and burn," Eric Virey concluded.

#### INTRODUCING THE PE-25-JW

The Plasma Etch, Inc. PE-25-JW is a fully automated plasma cleaning system.

Surface energy modification with plasma treatment yields improved markability, adhesion and ease of assembly with a low environmental impact.

Removes organics and improves bonds.

#### LOW STARTING PRICE \$ 5,900 USD

TO LEARN MORE, VISIT WWW.PLASMAETCH.COM OR GALL US TODAY AT 775-883-1336

# **news**cont

Continued from page 5

In its official release, Fairchild said these cuts are a part of Fairchild's ongoing initiative to enhance manufacturing capabilities, improve product quality, and lower costs resulting in greater supply chain flexibility and responsiveness for our customers.

Closures of both facilities and Fairchild's remaining five-inch wafer fabrication lines in Bucheon, South Korea, are planned to occur from Q2 to Q4 2015. foundation of any global manufacturer's operations in the increasingly dynamic semiconductor solutions market," said Mr. Thompson. "The realignment we are announcing will maximize the utilization of eight-inch factories and reduce the complexity of our manufacturing footprint, while creating the flexibility to support ongoing customer demand through a greater use of external manufacturing sources. Fairchild will continue operating eight-inch wafer fabrication lines in South Portland, Maine and Mountain Top, Pennsylvania, as well as the Bucheon six- and eight-inch fabrication lines."

Through the combined actions, Fairchild expects to incur approximately \$36 million in cash restructuring and other costs. The company also plans to record during the closure process non-cash charges of approximately \$25 million for accelerated depreciation. Once completed, the company expects to realize annual savings of approximately \$45 to \$55 million from a second quarter of 2014 financial baseline. Of these estimated savings, approximately 75 percent are expected to be cash savings, with the balance attributable to lower depreciation costs.

"An adaptive supply chain must be the

#### Continued from page 7

mechanical interactions have a dominant influence over the material properties—and not just at small scales.

"If you have two electrons in adjacent orbitals, and the orbitals are not completely filled, in a traditional material the electrons can move from one orbital to another. But in the correlated oxides, the electrons repulse each other so much that they cannot move," Ramanathan explains. "The occupancy of the orbitals and the ability of electrons to move in the crystal are very closely tied together—or 'correlated.' Fundamentally, that's what dictates whether the material behaves as an insulator or a metal."

Ramanathan and others at SEAS have successfully manipulated the metal-insulator transition in vanadium oxide, too. In 2012, they demonstrated a tunable device that can absorb 99.75% of infrared light, appearing black to infrared cameras.

Similarly, samarium nickelate is likely to catch the attention of applied physicists developing photonic and optoelectronic devices.

"Opening and closing the band gap means you can now manipulate the ways in which electromagnetic radiation interacts with your material," says Jian Shi, lead author of the paper in Nature Communications. He completed the research as a postdoctoral fellow in Ramanathan's lab at Harvard SEAS and joined the faculty of Rensselaer Polytechnic Institute this fall. "Just by applying an electric field, you're dynamically controlling how light interacts with this material."

Further ahead, researchers at the Center for Integrated Quantum Materials, established at Harvard in 2013 through a grant from the National Science Foundation, aim to develop an entirely new class of quantum electronic devices and systems that will transform signal processing and computation.

Ramanathan compares the current state of quantum materials research to the 1950s, when transistors were newly invented and physicists were still making sense of them. "We are basically in that era for these new quantum materials," he says. "This is an exciting time to think about establishing the basic, fundamental properties. In the coming decade or so, this could really mature into a very exciting device platform."

You Zhou, a graduate student at Harvard SEAS, was co-lead author of the paper in Nature Communications. The research was supported by grants from the National Science Foundation (NSF) (CCF-0926148) and the National Academy of Sciences, as well as an NSF Faculty Early Career Development (CAREER) Award to Prof. Ramanathan (DMR-0952794). <>

## Intel Announces EMIB

Intel recently announced that a new technology "Embedded Multi-die Interconnect Bridge" or EMIB will be available to 14nm foundry customers.

They claim it is a "... lower cost and simpler 2.5D packaging approach for very high density interconnects between heterogeneous dies on a single package." While neither Intel nor any initial press reports gave any indication of exactly what this means, it is highly likely that this is tied to the issuance of patent application publication US 2014/0070380 A1 published March 13 2014.

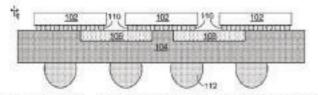

In simplified form interconnect bridges ("silicon glass or ceramic") are embedded in a laminate substrate and connected with flip chip as shown in **FIGURE 1**:

102 – chips; 104 – laminate substrate; 108 – interconnect bridge; 110 – c4 bumps; 112 BGA balls

**FIGURE 1.** Bridge interconnect as described in recent Intel patent.

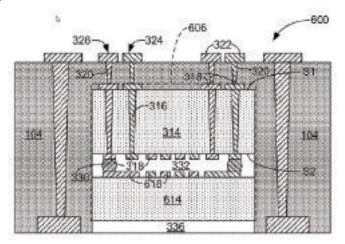

FIGURE 2. Intel EMIB Module in cross-section

### Packaging

A cross section of the package (**FIGURE 2**) is more revealing showing connections through the laminate and connections through the bridge substrate (316) which would be TSV in the case of a silicon bridge substrate. The underside of the bridge substrate (314) may be

**Dr. Phil Garrou,** Contributing Editor

connected to another bridge substrate for further interconnect routing as shown below.

While there is no silicon interposer, there do appear to be TSV in the embedded interconnect substrate as shown below. While removing complexity from the IC fabrication by eliminating TSV from the foundry process, the packaging operation becomes much more complex.

Since the 2.5D interposer has been reduced in size to the interconnect bridges, this may reduce cost, but will increase signal length vs a true 3D stack or a silicon interposer 2.5D.

While Intel released the following description: "Instead of an expensive silicon interposer with TSV (through silicon via), a small silicon bridge chip is embedded in the package, enabling very high density die-to-die connections only where needed." I think this is somewhat misleading.

The packaging analogy to what they have done is as follows: A high density bumped chip could be put down on to a high density build up PWB, but in most cases the high density bumped chip is placed on a smaller BGA substrate which is then put onto a lower density, lower cost PWB. The latter is the lower cost solution. In this case, large expensive high density interposers are avoided, and the much smaller EMIB are used for the high density interconnect. It will be interesting to see what if any the cost differential will be here.

Intel also announced the availability of its High Density Modular Test (HDMT) platform. HDMT, a combination of hardware and software modules, is Intel's test technology platform that, until now, was only available internally for Intel products. It is now available to customers of Intel Custom Foundry.  $\blacklozenge$

# EUV and mask complexity

EUV and mask complexity were the hot topics at this year's SPIE Photomask Technology conference in Monterey, Calif.

Extreme-ultraviolet lithography systems will be available to pattern critical layers of semiconductors at the 10-nanometer process node, and EUV will completely take over from 193nm immersion lithography equipment at 7nm, according to Martin van den Brink, president and chief technology officer of ASML Holding.

Giving the keynote presentation, Martin offered a lengthy update on his company's progress with EUV technology.

Sources for the next-generation lithography systems are now able to produce 77 watts of power, and ASML is shooting for 81W by the end of 2014, Martin said.

The power figure is significant since it indicates how many wafers the litho system can process, a key milestone in EUV's progress toward becoming a volume manufacturing technology. With an 80W power source, ASML's EUV systems could turn out 800 wafers a day, he noted.

The goal is to get to 1,000 wafers per day. ASML has lately taken to specifying throughput rates in daily production, not wafers per hour, since many wafer fabs are running nearly all the time at present.

ASML's overarching goal is providing "affordable scaling," Martin asserted, through what he called "holistic lithography." This involves both immersion litho scanners and EUV machines, he said.

Martin offered a product roadmap over the next four years, concluding with manufacturing of semiconductors with 7nm features in 2018.

The ASML president acknowledged that the development of EUV has been halting over the years, while asserting that his company has made "major progress" with EUV. He said the EUV program represented "a grinding project, going on for 10 years."

### Semiconductors

For all of EUV's complications and travails, "nothing is impossible," Martin told a packed auditorium at the Monterey Conference Center.

With many producers of photomasks in attendance at the conference, Martin promised, "We are not planning to make a significant change in mask infrastructure" for EUV. He added, "What you are investing today will be useful next year, and the year after that."

**Jeff Dorsch,** Contributing Editor

### SPIE panel tackles mask complexity

Photomasks that take two-and-a-half days to write. Mask data preparation that enters into Big Data territory. And what happens when extreme-ultraviolet lithography really, truly arrives?

These were among the issues addressed by eight panelists in a session "Mask Complexity: How to Solve the Issues?" The panelists were generally optimistic on prospects for resolving the various issues in question. Dong-Hoon Chung of Samsung Electronics said solutions to the thorny challenges in designing, preparing, and manufacturing masks were "not impossible."

Bala Thumma of Synopsys said he was "going to take the optimistic view" regarding mask-making challenges. "Scaling is going to continue," he added.

"We are not at the breaking point yet," Thumma said. "Far from it!" Electronic design automation companies like Synopsys will continue to improve their software tools, he asserted. Mask manufacturers will also benefit from "strong partnerships" with vendors of semiconductor manufacturing equipment, and "strong support from semiconductor companies," he said.

To resolve the issue of burgeoning data volumes in mask design and manufacture, Suichiro Ohara of Nippon Control System proposed the solution of a unified data format – specifically MALY and OASIS.MASK software. Shusuke Yoshitake of NuFlare Technology later said, "OASIS is gaining, but GDSII still predominates."

Several panelists took the long-term view and looked beyond the coming era of EUV lithography to when multiple-beam mask writers and actinic inspection of masks will be required. EUV and actinic technology, it was generally agreed, will arrive at the 7-nanometer process node, possibly in 2017 or 2018. ◆

#### 2015 MRS<sup>®</sup> SPRING MEETING & EXHIBIT April 6–10, 2015 | San Francisco, California

### CALL FOR PAPERS Abstract Submission Opens September 23, 2014 Abstract Submission Deadline October 23, 2014

#### Energy

- A Emerging Silicon Science and Technology

- B Thin-Film Compound Semiconductor Photovoltaics

- C Perovskite Solar Cells

- D Organic-Based Photovoltaics

- E Advanced Solar Cells—Components to Systems

- F Biohybrid Solar Cells—Photosynthesis-Based Photovoltaics and Photocatalytic Solar Cells

- G Next-Generation Electrochemical Energy Storage and Conversion Systems—Synthesis, Processing, Characterization and Manufacturing

- H Mechanics of Energy Storage and Conversion— Batteries, Thermoelectrics and Fuel Cells

- I High Capacity Anode Materials for Lithium Ion Batteries

- J Latest Advances in Solar Water Splitting

- K The Development of Oxygen Reduction Reaction (ORR) and Oxygen Evolution Reaction (OER) Materials in Energy Storage and Conversion Systems

#### **Nanomaterials**

- L Bioinspired Micro- and Nano-Machines—Challenges and Perspectives

- M Nanoscale Heat Transport—From Fundamentals to Devices

- N From Molecules to Colloidal Compound Semiconductor Nanocrystals— Advances in Mechanism-Enabled Design and Syntheses

- 0 Emerging Non-Graphene 2D Materials

- P Nanogenerators and Piezotronics

- Q Externally Actuated Responsive Nanomaterials— Design, Synthesis, Applications and Challenges

- R Photoactive Nanoparticles and Nanostructures

- S Semiconductor Nanowires and Devices for Advanced Applications

- T Graphene and Carbon Nanotubes

#### **Electronics and Photonics**

- U The Interplay of Structure and Carrier Dynamics in Energy-Relevant Nanomaterials

- V Resonant Optics—Fundamentals and Applications

- W Light-Matter Processes in Molecular Systems and Devices

- Y Phase-Change Materials for Data Storage, Cognitive Processing and Photonics Applications

Z Plasmonics and Metamaterials—

- Synthesis, Characterization and Integration

- AA Materials for Beyond the Roadmap Devices in Logic, Power and Memory

- BB Innovative Interconnects/Electrodes for Advanced Devices, Flexible and Green-Energy Electronics

- CC Reliability and Materials Issues of Semiconductors— Optical and Electron Devices and Materials III

- DD Tailored Disorder-Novel Materials for Advanced Optics and Photonics

- EE Quantum Photonics, Information Technology and Sensing

- FF Defects in Semiconductors—Relationship to Optoelectronic Properties

#### **Soft and Biomaterials**

- GG Foundations of Bio/Nano Interfaces— Synthesis, Modeling, Design Principles and Applications

- HH Supramolecular Materials—Assembly and Dynamics

- II Organic Bioelectronics—Materials, Processes and Applications

- JJ Exploiting Bioinspired Self-Assembly for the Design of Functional and Responsive Materials

- KK Nanomaterials in Translational Medicine

- LL Soft Electronics—From Electronic Skin to Reliable Neural Interfaces

- MM Crystal Engineering—Design, New Materials and Applications

#### **General**—Fabrication and Characterization

- NN Adaptive Architecture and Programmable Matter— Next-Generation Building Skins and Systems from Nano to Macro

- 00 Metal-Assisted Chemical Etching of Silicon and Other Semiconductors

- PP Gold-Based Materials and Applications

- QQ Plasma-Based Materials Science and Engineering

- RR Solution Syntheses of Inorganic Functional/Multifunctional Materials SS Oxide Thin Films and Nanostructures for Advanced Electrical, Optical

- and Magnetic Applications

- TT Metal Oxides—From Advanced Fabrication and Interfaces to Energy and Sensing Applications

- UU Titanium Oxides—From Fundamental Understanding to Applications

- VV Science and Technology of Superconducting Materials

- WW Ultrafast Dynamics in Complex Functional Materials

- XX Multiscale Modeling and Experiments on Microstructural Evolution in Nuclear Materials

- YY Insights for Energy Materials Using In-Situ Characterization

- ZZ Materials Information Using Novel Techniques in Electron Microscopy

#### www.mrs.org/spring2015

#### **Meeting Chairs**

Artur Braun

Swiss Federal Laboratories

for Materials

Science and Technology

Hongyou Fan

Sandia National Laboratories

Ken Haenen

Hasselt University and IMEC vzw

Lia Stanciu

Purdue University

Jeremy A. Theil

Quantumscape, Inc.

#### **Don't Miss These Future MRS Meetings!**

#### 2015 MRS Fall Meeting & Exhibit November 29 – December 4, 2015

Hynes Convention Center & Sheraton Boston Hotel Boston, Massachusetts

#### 2016 MRS Spring Meeting & Exhibit March 28 – April 1, 2016

March 28 – April 1, 2016 Phoenix Convention Center Phoenix, Arizona

#### MRS MATERIALS RESEARCH SOCIETY® Advancing materials. Improving the quality of life.

506 Keystone Drive • Warrendale, PA 15086-7573 Tel 724.779.3003 • Fax 724.779.8313 info@mrs.org • www.mrs.org

# SEMICON Europa heads to Grenoble

#### PETE SINGER, Editor-in-Chief

All parts of the semiconductor supply chain will come together at the ALPEXPO center in Grenoble, France.

EMICON Europa will be held in France for the first time, on October 7-9, in Grenoble. Located in southeastern France, at the foot of the French Alps, Grenoble is one of the most important scientific centers in Europa, home to CEA-Leti, Soitec and the GIANT innovation campus (Grenoble Innovation for Advanced New Technologies). It's also home to the iconic "bubble" cable cars shown on this issue's cover.

Heinz Kundert, president of SEMI Europe, said the show has evolved from just being a place for buyers and sellers of equipment and materials to

meet. "We have adapted the entire SEMICON format to allow the entire supply chain to come together in different ways. It's a rebirth of SEMICON in Europe," he said. "We are trying to really understand the supply chain as a total concept and what needs to be changed to be successful in the future."

The show will feature an expanded exhibition (40 percent larger) and a conference of more than 70 sessions with 300 speakers.

In addition to a new "Innovation Village" that will showcase 35 European start-ups, the event host the 18th Fab Managers Forum, which is themed "Improving Productivity for Mature Fabs." Speakers from imec, Infineon AG and Bosch will present on Internet of Things, Automation Level in Fabs, and Smart Connected Sensor Devices.

The prospect for future 450mm wafer processing,

Heinz Kundert hands a 450mm wafer to European Commission vice president Neelie Kroes.

as well other technical and business challenges in semiconductor and related micro and nano-electronics industries, will also be addressed. In a two-day special program, "450mm Innovations and Synergies for Smaller Diameters," leaders will present on progress, research, and collaboration on the future of the semiconductor manufacturing. The session includes presentations from Global 450 Consortium, European Commission, ASM Europe BV, and RECIF Technologies.

In addition, a Secondary Equipment Session, themed "Fundamental to European Competitiveness?" will feature presentations from Infineon Technologies AG, STMicroelectronics, and Robert Bosch GmbH.

Other conference programs at SEMICON Europa will explore critical issues in Fab Management, Advanced Packaging, 3DIC, Test and MEMS.

#### **Growth in Europe**

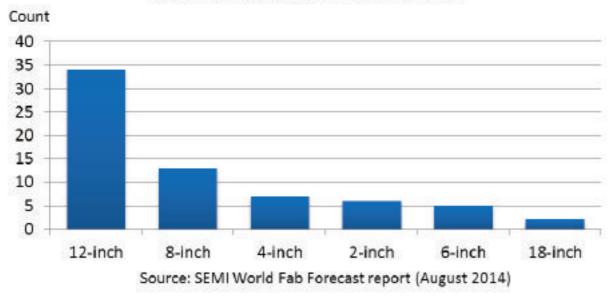

The European semiconductor equipment market is expected to grow along with the world market. Global capital spending on semiconductor equipment is projected to grow 21.1 percent in 2014 and 21.0 percent in 2015. According to the August edition of the SEMI World Fab Forecast, semiconductor equipment spending will increase from \$29 billion in 2013 to \$42 billion in 2015.

SEMI projects back-to-back years of double-digit growth in Europe and Mid-East semiconductor equipment sales. The SEMI outlook forecasts that the European/Mid-East semiconductor equipment market will grow 11 percent in 2014 (reaching \$1.9 billion) and 100 percent in 2015 (reaching \$3.8 billion). In terms of percentage of worldwide sales, the Europe/MidEast region's share is expected to increase from 5.9 percent in 2013 to 9.0 percent in 2015.

Kundert notes that Europe is home to a diverse set of semiconductor manufacturing companies, including Intel (in Ireland), Infineon (which is in the process of buying International Rectifier), GlobalFoundries (in Dresden), STMicroelectronics and Bosch. This diversity makes Europe well-suited to tackle the Internet of Things and More-than-Moore. "It's a big challenge, but we believe if somebody can manage it successfully, it's Europe. We are very experienced in those types of applications," Kundert said.

Europe is home to many leading semiconductor research groups, including imec, CEA-Leti and Fraunhoffer. These groups are supported by a variety of government efforts, including the "10-100-20" effort announced last year by European Commission vice president Neelie Kroes (see photo) and supported by SEMI.

10-100-20 is an ambitious strategy to double the economic value of semiconductor production in Europe in the 2020-2025 timeframe. This will be achieved by an unprecedented public/private investment partnership with 10 billion Euros in public/private funding and 100 billion Euros from the industry.

The roadmap, published on 14 February 2014, was drafted by the Electronic Leaders Group (ELG), that was set up by the European Commission and consists of: ARM, ASML, CEA, Fraunhofer, Globalfoundries, imec, Infineon, Intel, NXP, SOITEC, STMicroelectronics (A copy can be downloaded from http://www.semi.org/eu/ node/8506). There's been good progress, but Kundert cautioned that "such an initiative takes time."

Another notable effort is the new Industry 4.0 (or "industrie 4.0") out of Germany, which aims to define the fourth industrial revolution. The first industrial revolution was the mechanization of production using water and steam power, it was followed by the second industrial revolution which introduced mass production with the help of electric power, followed by the digital revolution, which was the use of electronics and IT to further automate production. "In the project, semiconductor technology plays an important role. Industry 4.0 or the fourth industrial revolution could be a reality in about 10 to 20 years," Kundert explained. "Germany is pushing extremely strong right now to build on semiconductors," he added.

"All in all, we see increased activity in national and local government initiatives," Kundert said.

#### **SEMICON Power**

For the first time, SEMICON Europa 2014 will offer two new power-related technical forums: Power Electronics Conference and Low Power Conference. Energy efficiency is a key challenge and advances in power microelectronics, batteries, mobility, and energy harvesting systems are making power management smarter to reduce energy consumption. The two new power conferences focus on how innovators and their technologies are building energy-optimized applications.

The theme of the Low Power Conference is "Highly Energy Efficient Nanotechnologies and Applications." The number of connected electronics devices is

#### **35 European start-ups showcased at Innovation Village**

At SEMICON Europa, attendees and exhibitors will delve into the technologies that shape the future of the microtech, nanotech, medtech and cleantech industries. Representing the entire supply chain from materials to electronic systems and services, 35 major European start-ups will participate in the Innovation Village and present their new technologies.

Innovation Village consists of a start-up exhibition (7-9 October), Silicon Innovation Forum (7 October) and Innovation Conference (8 October). As part of the Silicon Innovation Forum, all selected start-ups will have the opportunity to "pitch" to investors and SEMICON Europa visitors. The pitch session will be followed by a start-up panel discussion "Fundraising for the Future Champions of European Electronics," led by Jean-Pascal Bost of SATT-GIFT with panelists: Jacques Husser (Sigfox), Eric Baissus (Kalray), Serguei Okhonin (ActLight) and Mike Thompson (Hotblock Onboard).

The Innovation Conference, sponsored by Fidal Innovation, will feature keynote speakers such as Nicolas Leterrier (Schneider Electric) on Innovation Practices and Dan Armbrust (Silicon Catalyst) on Lean Innovation. Christine Vaca (Gate1) will act as the conference chair.

"For the inaugural SEMICON Europa in Grenoble, our team was intent on developing a program that would highlight the strength of the local and the European ecosystems in innovation and new technology," explains Anne-Marie Dutron, director of the SEMI Grenoble office. "At Innovation Village, visitors will discover the creativity of 35 European start-up companies, presenting their products, partnership and investment opportunities."

Participating start-ups were chosen by a selection committee which included ten of the most recognizable venture firms in the industry: Applied Ventures LLC, Robert Bosch Venture GmbH, TEL Venture, 3M Ventures, CEA Investissement, Samsung Ventures, Air Liquid Electronics, ASTER Capital), VTT Ventures, and Capital-E.

Start-ups include ActLight (Switzerland), BlinkSight (France), BluWireless Technology (UK), Calao-Systems (France) and Silicon Line (Germany). For more information about Innovation Village, participating start-ups or about the Innovation Conference, please visit the SEMICON Europa website: www.semiconeuropa.org/Segments/InnovationVillage

All events in Innovation Village, including the three-day start-up exhibition, Silicon Innovation Forum and Innovation Conference will be available at no charge for all SEMICON Europa guests and visitors.

#### **Silicon Line**

The company is a provider of ultra-low power optical link technology for mobile and consumer electronics markets. Silicon Line products enable power-efficient optical transportation of video, images, voice and data at the multi - gigabit speeds demanded by both today and tomorrows digital consumer lifestyles. The company is VC founded since 2007.

#### **Nessos Information Technologies SA**

Nessos is a software development company that targets custom integrated solutions with advanced software engineering requirements. Nessos' self-financed research and development department is focused on Big Data/ Big Computation applications and mobile services. The company's paiRing is its latest research and development product. It is a smart ring that enables you to instantly share your feelings, your mood and words of love with your significant other. The paiRing is described as an "elegant ring" which connects wirelessly with paiRing apps-enabled smartphone, offering various ways of communication.

#### **eVaderis**

The company offers energy efficient, low power mixed-signal data-centric control processors combining silicon technologies and disruptive non volatile resistive memories (NVRM).

The company will sell these products to wireless Machine to Machine (M2M) system integrators, serving the long - term battery volume - intensive smart sensors, data loggers, wearable computers markets, and more generally, the exploding market of the Internet of Things (IoT).

#### Wavelens

Wavelens is developing disruptive optical MEMS solutions aimed at improving cameras image quality by making easier the integration of optical functions such as autofocus, image stabilization and zoom.

#### **ActLight SA**

The company is focused on the field of CMOS photonics, developing new type photodetectors and improving photovoltaic energy harvesting technology. ActLight is a fabless company, specializing in the Intellectual Property (IP) of these areas. It also provides supporting services like design and technology advice for its customers.

#### Irlynx

Irlynx is a French start-up based in Grenoble that develops and commercializes infrared sensors to detect and characterize human being activity at lower cost while respecting private life. Thanks to a unique infrared detection technology, the Irlynx optoelectronic modules, which embed pre-processing image algorithms, speed up time to market of more innovative and interactive products.

#### Pollen Technology

POLLEN Technology is a software company that provides a product portfolio dedicated to easy and safe nanomaterials production and integration. Its products integrate the latest ISO regulations to ensure traceability and environmental/health security. Adaptative technology is covering a large scope from semiconductor industry, cosmetics, chemistry and automotive.

#### Exagan

Exagan is a supplier of GaN-based transistor devices for power supply, electrical automotive, solar panel and industrial application. With a unique and proprietary technology, Exagan is accelerating transition of power electronics industry towards more efficient production and conversion systems to reduce CO2 emission, by enabling large scale adoption of GaN-on-Silicon power technology.

#### **AVALUN SAS**

Created in 2013, the company currently offers the LabPad, a mobile point -of-care (POC) device. As rapid In Vitro Diagnostic (IVD) is a fast-growing market, LapPad technology responds to a demand for a tool designed to carry out multiple tests. LapPad allows for patients to be monitored at home or during an emergency and more generally, assists healthcare professionals (doctors, pharmacists, nurses), whom practice would be clearly incompatible with a plethora of different instruments. Using the same imaging components as a smartphone to create a fully integrated miniature microscope, LabPad is a portable minilab that can perform many tests on the same device, such as blood coagulation, glucose or cholesterol. A patient or a healthcare professional just needs to insert the appropriate micro-cuvette in the device, draw a droplet of blood from the patient's finger and deposit it on the micro-cuvette. It allows for a number of medical tests to be taken by one single instrument. The development of this technology is the result of over 10 years of research at CEA-Léti.

#### Noivion

Noivion developed and patented a new thin film deposition technique named Ionized Jet Deposition (IJD). JD is an electron ablation technology that offers advantages in terms of film quality and stoichiometry conservation combined with high productivity, competitive cost and industrial scalability. IJD sources and equipment have the unique capability to enable mass production of complex compounds coatings by a quick and single deposition step opening new opportunities for the semiconductor manufacturing industry. Successful applications include CIGS and YBCO deposition. IJD is also an ideal solution for the deposition of high melting point metals, TCOs, hard oxides, nitrides, carbides that are feasible by non reactive or reactive process with high target utilization. IJD sources are available now as prototypes to selected users. The release of a commercial version is expected within 2014. The company says that it believes in 5 years IJD can become a mature thin film industrial manufacturing solution.

#### CALAO Systems

CALAO Systems is the specialist of onboard connected computers based on ARM processor architecture and Linux open source software, integrating electronic technologies and telecommunications. Calao system offers an easy access for electronic specialist - or not - of high-tech products, to customers that operate in the industrial market, M2M and the Internet of Things. The company is headquartered in Grenoble.

#### Heyday

Heyday Integrated Circuits concepts and develops semiconductor ICs for the power conversion market. Heyday IC products increase integration, reduce component count and improve performance of AC-DC and DC-DC power conversion products.

#### Smoltek AB

Smoltek offers a proprietary conductive nano - scale carbon technology tailored to support the future needs of the semiconductor industry.

#### PETsys Electronics - Medical PET Detectors, S.A.

HPETsys Electronics SA developed new PET detectors for next generation of medical PET scanners, enabling high resolution images and increased sensitivity, at lower cost, for early cancer detection and monitoring. This is a major step in the fight against cancer. The company is now selling our patent pending ASIC's evaluation kit. The company has already secured 1 million Euros, and says another 1 million Euros is needed for the next 18 months phase (starting in May2015), after which is will be self-sufficient.

#### Scint-X

The company develops structured scintillators. Partnering with leading manufacturers of x-ray detection systems, it is in the process of transforming digital x-ray detection systems so as to produce images with unprecedented levels of resolution and contrast. The technology is primarily used in markets such as Medical (Mammography, General Medical & Dental), Security (Non Destructive Test) and Industrial applications. Currently scintillators are so called needle scintillators which are grown from a CsI material base. Scint-X has developed a structured scintillator using MEMS deep Si DRIE technologies to create a honeycombed structured scintillator combined with a highly reflective mirror finish on the sidewalls thereby increasing the x - ray absorption for significantly better DQE and MTF. This gives up to 4x improvement in contrast and 2x improvement in resolution.

#### Grapheat

Grapheat is a young startup specialized in the production and integration of monolayer high quality of graphene on wafers and substrates for specific applications. We especially target production of transparent, conducting and flexible electrodes. The company also offers customized solutions for integration of graphene in prefabricated structures by innovative lamination techniques.

#### **Gridbee Communications**

Gridbee Communications is developing innovative long range mesh network solution for connected objects. The solution is fully standard, auto-configurable, auto-scalable and auto-manageable.

#### Enerstone

Enerstone works with rechargeable battery manufacturers and integrators to improve the charge quality of their batteries, providing a considerable competitive advantage on the commodity battery market. Its battery management technology and proven expertise in battery optimization can help rechargeable battery manufacturers and integrators preserve the initial factory capacity of their batteries charge after charge, for better performance and lower overdesign costs.

#### **Nocilis Materials**

Nocilis Materials AB offers various silicon based semiconductor materials, including SiGeSnC alloys for various photonic applications and silicon photonic integrated circuits. Nocilis also offers bandgap enginered material SGOI and GOI as substrates or for RF&MW applications. growing exponentially. According to Jean-Marc Chery, COO STMicroelectronics, to sustain this growth, the semiconductor industry needs a real breakthrough in energy efficiency — both for connected devices and for the communication infrastructure. At the same time, the traditional planar bulk CMOS technology is plateauing in power consumption and performance beyond 28nm, so breakthrough solutions for energy efficient systems are mandatory to continue the growth.

Sessions include: Market Analysis; Technology Energy Efficiency; Processors; Energy Efficient Design; Energy Efficient EDA Tools; and Applications. Speaker highlights include:

- STMicroelectronics: Jean-Marc Chery, COO

- GLOBALFOUNDRIES: Manfred Horstmann, director, Products and Integration

- Qualcomm Technologies: Mustafa Badaroglu, senior program manager

- Cadence Design Systems, Inc.: Marcus Binning, senior AE manager

- IBS, Inc.: Handel Jones, CEO,

- Hewlett-Packard: Rémi Barbarin, CTO

- Schneider Electric: Gilles Chabanis, manager, Pervasive Sensing

The Power Electronics Conference is themed "The Ultimate Path to CO<sub>2</sub> Reduction." Modern power semiconductors play an essential role in energy conservation and worldwide CO<sub>2</sub> reduction. Philippe Roussel, business unit manager at Yole Developpement, will present the keynote on market and technology overview of the Power Electronics industry, including a look at the impact of Wide BandGap (WBG) Devices. He believes that the emergence of new WBG technologies such as SiC and GaN will reshape the established power electronics industry, especially on the high-voltage side. SiC and GaN offer benefits (higher frequency switching, power density, and more) that may dramatically help improve the power conversion efficiency. Yole believes that this could lead to lower CO2 emission if both SiC and GaN can emerge from labs to mass production. SiC transitioned a few years ago and GaN is starting the commercialization curve. By 2020, WBD devices are expected to generate more than \$1 billion according to Yole.

The session highlights include:

• Applications session — speakers from CEA/LETI,

EpiGaN, European Center for Power Electronics e.V. (ECPE), Infineon, European Commission, Renault, and Supergrid Institute.

Technology and Materials session — presenters from Fairchild, Infineon Technologies AG, SiCrystal AG, Siltronic AG, Soitec, ST Catania, and Yole Developpement.

#### **Imaging without limits**

The Imaging Without Limits Conference will address the rising demands of imaging systems in mobile, medical, automotive and other technology applications. Until recently, the imaging market was based primarily on mobile phone based applications. However, new technologies for imaging-based applications are now being introduced — including wearable electronics (e.g. smart watches), automotive, tablets, machine vision, security and surveillance, and medical applications.

Covering a broad range of imaging systems, the two-day conference will explore the promise of imaging-related systems, existing applications and new applications and technologies now on the horizon. Keynote speakers include Eric Fossum, Dartmouth University and the father of CIS, and Pascal Brosset, chief innovation officer of Schneider Electric. The first day will address applications (mobile, automotive, industrial, medical) and technologies (sensors, optics, processing and packaging) while the second day will delve into specific implementation techniques.

According to Yole Developpement, the CMOS Image Sensor (CIS) market is expected to grow at a 10 percent CAGR in revenue in the five-year period from 2013 to 2018, growing from US\$ 7.8 billion in 2013 to \$12.8 billion in 2018. While many applications drive the integration of CMOS image sensors, mobile phones accounted for approximately 66 percent of total shipments in 2013. But other new applications including tablets and automotive — are set to drive the future growth of this industry. Tablets also significantly contribute to the market growth with a 17 percent CAGR over 2013-2018.

The next wave of imaging will likely focus on automotive applications because additional image sensors are necessary for many of the safety improvements required by new government regulations. CAGR for CIS automotive applications is expected to **Sem** | Global Expositions

# without limits.

# EXPAND YOUR BUSINESS WORLDWIDE

Whether you are looking to explore new regions, technologies, or markets, SEMI Expositions are the ideal platform to showcase your brand, connect to customers, and grow your business worldwide. Let SEMI help you build an exhibition and marketing program that gains maximum exposure and takes your business to the next level!

#### Visit www.semiexpos.org

### **SEMI®** Expositions Calendar

NEW VENUE

#### SEMICON Europa 2014

October 7–9 Grenoble, France www.semiconeuropa.org

**PE 2014 Exhibition** and Conference October 7–9 Grenoble, France www.plastic-electronics.org

**PV Taiwan 2014** October 22–24

Taipei, Taiwan www.pvtaiwan.com SEMICON Japan 2014 December 3–5 Tokyo Big Sight, Japan www.semiconjapan.org

SEMICON Korea 2015 February 4–6 Seoul, Korea www.semiconkorea.org

**LED Korea 2015** February 4–6 Seoul, Korea www.led-korea.org SEMICON China 2015 March 17–19 Shanghai, China www.semiconchina.org

**FPD China 2015** March 17–19 Shanghai, China www.fpdchina.org

**LED Taiwan 2015** March 25–28 Taipei, Taiwan www.ledtaiwan.com

SEMICON Southeast Asia 2015 April 22–24 Penang, Malaysia www.semiconsea.org SEMICON Russia 2015 June 17–18 Moscow, Russia www.semiconrussia.org

**SEMICON West 2015** July 14–16 San Francisco, USA www.semiconwest.org

**SEMICON Taiwan 2015** September 2–4 Taipei, Taiwan www.semicontaiwan.org increase 36 percent between 2013 and 2018. Yole states that the market is "expected to reach about \$700 million in 2018, and will drive the need for high-performance sensors: global shutter, high dynamic range, and high sensitivity. The requirements of the automotive market are hence completely different from the mobile phone market, which is still in the race for higher resolution and smaller pixels."

In addition, Yole also sees several other applications with a high CAGR, including wearable devices (103

percent), machine vision (33 percent), and camera pills (32 percent).

Key companies involved in the imaging conference and exposition include: ARM, Asia Optical-EtherO, Audi, European Space Agency, French Institute of Vision, Hamamatsu, Heptagon, Microsoft, Schneider, Sofradir and STM. Many

research centers are also involved — CEA-LETI, CSEM, Fondazion Bruno Kezler, Fraunhofer Institut, Grenoble University Hospital, and more. Start-up and SMEs involved in the conference include: Aldebaran, Awaiba, CMOSIS, Caeleste, Mesa, Blue Eye Video, ISD, Kaleido, Multix, NikkoIA, NIT, Pyxalis, Yole, and Wavelens.

#### **Plastic electronics**

The Plastics Electronics Conference and Exposition, focusing on the latest developments in printed, organic and large area electronics, will co-locate with SEMICON Europa. Plastic Electronics 2014 (PE 2014) is themed "Enabling Applications beyond Limits in Electronics."

According to analysts, the plastics electronics market is growing rapidly and is expected to reach \$13 billion by 2020 driven by increasing applications in the semiconductor and electronics market. Applications like large area displays, solar panels and printed electronics are now responsible for a substantial portion of the PE market, and emerging applications like OLED, thin-film batteries, and sensors are emerging growth opportunities.

Manufacturability of plastic electronics has made major steps in the last year, moving from research level

to industrial relevance. Still, numerous barriers to commercialization must be overcome — from material development to integration, manufacturing, processing, and assembly issues.

Plastic electronics' imminent transition from the R&D phase to the industrialization stage is highlighted by several keynote presentations at the PE2014. Fiddian Warman, founder and managing director, SODA, will present on, "How design type approaches can be effective in facilitating innovative

> technological development and open up new markets and opportunities," and John Heitzinger, president, Soligie, Inc., will delve into "Advances in Additive Manufacturing of Electronics."

The exposition and conference cover the entire span of Plastic Electronics — Hybrid and Heterogeneous Integration; Organic

Electronics; OLEDs, Displays, and Lighting; and Flexible Photovoltaics — offering the latest developments for engineers, material experts, manufacturing professionals and industry strategists. Highlights are:

- Business Case session speakers from imec, ISORG, Nokia, Philips Research, Plastic Logic, SODA, STMicroelectronics, Valeo, and Yole Developpement.

- Manufacturing Panel Discussion on "Building a Leadership Position in PE" — panelists from Bosch, Cambridge, CEA, Joanneum Research, and Ynvisible.

- Manufacturing Session presenters from Applied Materials, Beneque, CEA Tech, Dupont Teijin Films UK Ltd, Joanneum Research, NovaCentrix, Roth and Rau B.V., Soligie, Universal Laser Systems, Ynvisible — as well as Cambridge University, the European Commission, and VTT (Finland).

- Technologies/Materials Session features speakers from Arkema, Arizona State University, CEA-LITEN, Corning, Fraunhofer, imec, and Sunchon National University. ◆

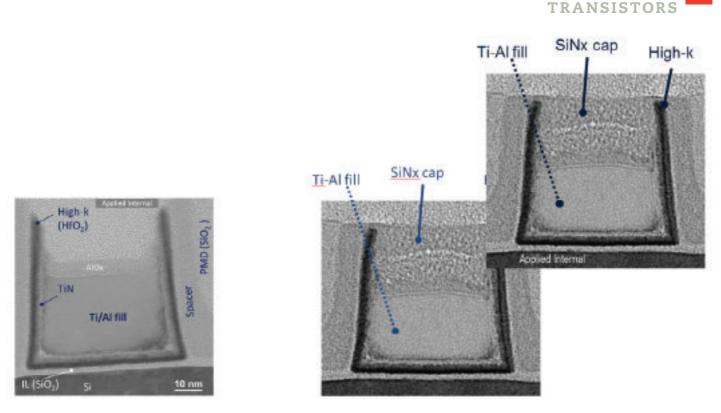

# Threshold voltage tuning for 10nm and beyond CMOS integration

NAOMI YOSHIDA, KEPING HAN, MATTHEW BEACH, XINLIANG LU, RAYMOND HUNG, HAO CHEN, WEI TANG, YU LEI, JING ZHOU, MIAO JIN, KUN XU, ANUP PHATAK, SHIYU SUN, SAJJAD HASSAN, SRINIVAS GANDIKOTA, CHORNG-PING CHANG and ADAM BRAN, Applied Materials, Santa Clara, CA

#### A novel metal gate integration scheme to achieve precise threshold voltage (VT) control for multiple VTs is described.

t very small process geometries, precise control of electrical conductivity is difficult to maintain. The industry requires a viable replacement-gate FinFET architecture to continue scaling high performance CMOS

[1, 2] technology and designs. Furthermore, cost-effective and precise VT control to achieve multiple VTs is essential for future ULSI fabrication to achieve optimal power consumption and performance.

In this study, using WFM full fill and combining two techniques — the novel metal composition and ion implantation into the WFM process, we successfully realized three critical aspects for the metal gate

gate trench, and 3) compatibility to the self-aligned contact (SAC).

A metal oxide semiconductor capacitor (MOSCAP) was used to evaluate the impact of the metal composition and beam line ion implantation on eWF. Ion

> implantation was performed for some of the samples after high-k dielectric and work function metal deposition on blanket wafers. High frequency capacitance voltage (HFCV) and current voltage (IV) measurements were recorded for the MOSCAP samples. A single damascene structure was used to measure sub-20 nanometer line resistance. A planar MOSFET was also used for evaluating impact on VT and variability.

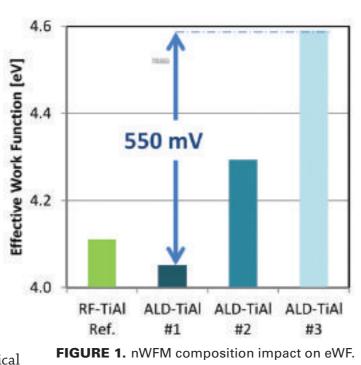

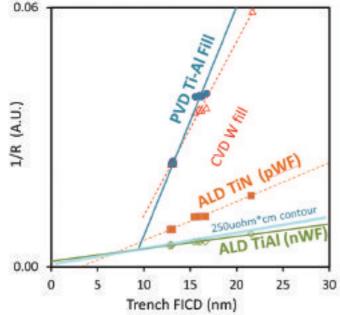

Work function modulation FIGURE 1 shows eWF with three compositions of NMOS WF metals (nWFM) compared

for 10 nanometer and beyond. These are: 1) precise effective work function (eWF) control over a 600 millivolt (mV) tuning range to achieve multiple VT, 2) maintaining conductivity for a sub-15 nanometer with RF-PVD titanium aluminum (TiAl) that was used as the nWFM reference metal. Results demonstrated that the difference between the highest and lowest WF was 550 mV and is attributed to the ALD

**NAOMI YOSHIDA** is a distinguished member of technical staff in the Advanced Product and Technology Development group of the Silicon Systems Group at Applied Materials. She earned her M.S. in physics from the International Christian University, Japan.

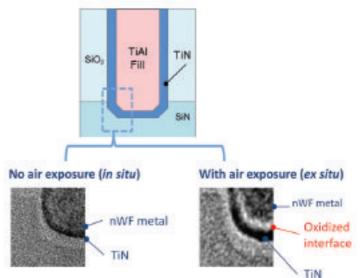

TRANSISTORS

TiAl composition. Nitrogen ion implantation into the ALD TiAl enabled further WF tuning by 100-150 mV steps. This made possible a WF range from near the Si conduction band edge of 4.1 electron volts (eV) for NMOS low VT to above mid-gap 4.7 eV. The WF shift corresponded well to the different dose levels; therefore we demonstrated that ion implantation can be used to pinpoint the target WF. In addition, we found that ion implantation into ALD TiAl does not degrade the gate leakage current and effective oxide thickness (EOT) performance.

#### Maintaining metal gate conductance for 10nm node

According to the ITRS roadmap, a gate length of 17 nanometers is expected for the 10 nanometer technology node [3]. The problem is that after the high-k cap and etch stop depositions, the gate will

1.6-02

0.E+00

in situ

10

Trench Width (nm)

Conductance, 1/R (A.U.)

have limited space left for the metal fill process [4]. One solution is to fully or mostly fill the trench with WF metal. Using an advanced ALD TiAl deposition process, we were able to fill 13 nanometer wide trenches without any gapfill voids. **FIGURE 2** shows the

extendible conductance

extendible conductance and nWF metal on conductance below 30 nanometers.

**FIGURE 2.** Conductance curves of various metals filling small trenches.

**FIGURE 4.** TEM images at interface of TiN barrier and nWFM. The ex situ sample shows oxidized interface by air exposure.

TIAL

Hi k cap TiN

air exposure

ex situ