# Solid State TECHNOLOCY Insights for Electronics Manufacturing

Managing Dis-aggregated Data for SiP Yield P. 19

Sapphire in Mobile Devices and LEDs

P. 21

NAND Architecture Comparison

P. 24

# Why Lithography Alternatives Are Essential R14

MEDIA

# BETTER TECHNOLOGY STRONGER TOGETHER

## JCET Completes Acquisition of STATS ChipPAC to Ascend to a Leading OSAT Player Globally

China's leading semiconductor packaging and testing company, Jiangsu Changjiang Electronics Technology (JCET, SHE: 600584), successfully completed the acquisition on Aug 5 2015 of STATS ChipPAC, a leading provider of advanced semiconductor packaging and test services headquartered in Singapore. This USD 780 mn transaction was originally announced on Dec 30 2014, and was conducted through JCET-SC (Singapore) Pte. Ltd., a subsidiary of JCET.

This acquisition will escalate the combined entities to one of the world's top outsourced semiconductor assembly and test (OSAT) players. As a combined group of companies, JCET and STATS ChipPAC offer a broader technology portfolio with significant manufacturing scale in key semiconductor geographies. The acquisition will also improve the competitiveness of the Chinese semiconductor packaging and test industry with a strong intellectual property (IP) and innovation portfolio built around advanced technologies acquired by JCET.

"The completion of our acquisition of STATS ChipPAC is an important step for us, and it presents an exciting win-win opportunity for both companies, supporting our long-term success," said Xinchao Wang, Chairman of JCET. "Post acquisition, the combined entities will provide one of the most extensive product/service portfolios to a highly diversified customer base with wide geographical coverage. Our leadership position in advanced packaging technologies will be further strengthened through the acquisition. JCET and STATS ChipPAC are working together to deliver the substantial revenue and cost synergies for our investors."

For more information, visit www.cj-elec.com or www.statschippac.com.

## Solid State TECHNOLOGY.

SEPTEMBER 2015 VOL. 58 NO.6

The MAPPER FLX-1200 litho tool in the Leti cleanroom interfaced with a SCREEN DUO track.

#### FEATURES

SOVER

#### **LITHOGRAPHY** Lithography alternatives: Why are they essential? The availability of patterning alternatives in the lithography landscape represents a big opportunity to properly

address the coming needs generated by the IoT. Laurent Pain, Raluca Tiron, Ludovic Lattard, Stefan Landis and Cyrille Laviron, CEA-Leti, Grenoble, France

#### **PACKAGING** Managing dis-aggregated data for SiP yield ramp

New ways are needed to feed data back and forth between designers, chip fabs, and Out-Sourced Assembly and Test (OSAT) companies.

Ed Korczynski, Senior Technical Editor

#### **MATERIALS** The use of sapphire in mobile device and LED industries Sapphire is hard, strong, optically transparent and chemically inert. *Winthrop E. Baylies and Christopher JL Moore, BayTech-Resor LLC, Maynard, MA*

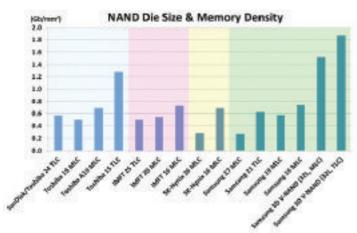

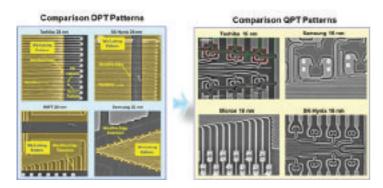

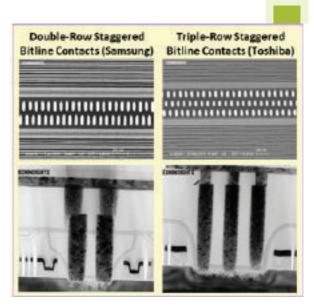

#### **MEMORIES** Comparison of 1Ynm NAND architecture and beyond

Expect at least two more next generation 2D planar NAND products having 12nm and less than 12nm technology. *Jeongdong Choe, PhD., TechInsights, Ottawa, Canada.*

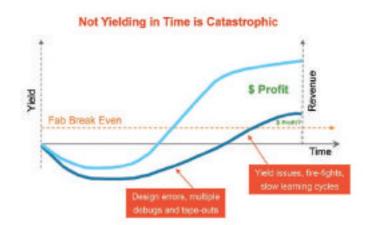

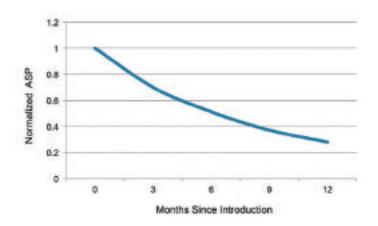

#### PROCESS WATCH | Time is the enemy of profitability

Time is a critical element in all phases of semiconductor manufacturing. Douglas G. Sutherland and David W. Price, KLA-Tencor, Milpitas, CA

#### **BUSINESS** Cut costs: Improve Your Competitive Advantage Systematic – and predictive – cost reduction in semiconductor equipment manufacturing

Systematic – and predictive – cost reduction in semiconductor equipment manura Tom Mariano, Foliage, Burlington, MA

#### COLUMNS

- 2 Editorial IoT Surveys Indicate Optimism, Confusion, Pete Singer, Editor-in-Chief

- 12 Packaging Advances in thermo-compression bonding, Phil Garrou, Contributing Editor

- 13 Semiconductors The IoT and the next 50 years of Moore's Law, Shannon Davis, Web Editor

- **32** Industry Forum Update for exporters: Trade wins and delays, *Taylor Sholler, SEMI*

#### DEPARTMENTS

- 4 Web Exclusives

- 6 News

- 30 Ad Index

## editorial

## IoT Surveys Indicate Optimism, Confusion

Solid State Technology recently conducted a survey of our readers on how the Internet of Things (IoT) is driving the demand for semiconductor technology. A total of 303 people responded to the survey. A majority of the respondents were in management roles.

Survey questions focused on their expectations for growth in the Internet of Things (IoT), drivers, potential roadblocks, opportunities and impact on semiconductor technology, including manufacturing and packaging.

"A majority of the respondents said the existing supply chain and industry infrastructure was not equipped to handle the needs of the IoT."

There is little agreement on how strongly the IoT device market will grow. About a quarter of the respondents said, by 2020, 30-50 billion devices would be connected to internet with unique urls. Almost as many were much more optimistic, saying more than 90 billion.

A sizable majority of the respondents (59.41%) believe new companies will emerge to benefit from the growth in IoT. Existing companies will also benefit, with MEMS companies benefitting the most.

A majority of the respondents said the existing supply chain and industry infrastructure was not equipped to handle the needs of the IoT or said they weren't sure. Similarly, most said new manufacturing equipment and new materials will be needed for IoT device manufacturing.

My take on this is that while the market potential for companies involved in IoT devices is large, there is little agreement on exactly how large it might become.

I believe it's also likely that new companies will emerge focused specifically on manufacturing IoT devices. Existing companies across the supply chain will also benefit.

Clearly, IoT devices will create new challenges, especially in the area of packaging. Form-factor, security and reliability are the most important characteristics of IoT devices.

Another recently completed survey on the IoT by McKinsey & Company and the Global Semiconductor Alliance (GSA) revealed some ambiguity about whether the IoT would be the top growth driver for the semiconductor industry or just one of several important forces.

The survey of executives from GSA member companies showed that they had mixed opinions about the IoT's potential, with 48 percent stating that it would be one of the top three growth drivers for the semiconductor industry and 17 percent ranking it first. 🚸

#### -Pete Singer, Editor-in-Chief

Pete Singer, Editor-in-Chief Ph: 978.470.1806 psinger@extensionmedia.com Shannon Davis, Editor, Digital Media Ph: 603.547.5309 sdavis@extensionmedia.com Ed Korczvnski, Senior Technical Editor. edk@extensionmedia.com Jeff Dorsch, Contributing Editor Phil Garrou, Contributing Editor Dick James, Contributing Editor Vivek Bakshi, Contributing Editor

2

CREATIVE/PRODUCTION/ONLINE Stephanie Bradbury, Production Manager Kyle Barreca, Media Coordinator Nicky Jacobson, Senior Graphic Designer Simone Bradley, Graphic Designer Slava Dotsenko, Senior Web Developer

#### MARKETING/CIRCULATION Jenna Johnson

2343. (8 am - 5 pm, PST)

jjohnson@extensionmedia.com

#### CORPORATE OFFICERS

Extension Media, LLC Vince Ridley, President and Publisher vridlev@extensionmedia.com

Clair Bright, Vice President and Publisher Embedded Electronics Media Group cbright@extensionmedia.com

Melissa Sterling, Vice President, **Business Development** msterling@extensionmedia.com

Septmber 2015, Volume 58, Number 6 • Solid State Technology ©2015 (ISSN 0038-111X) Subscriptions: Domestic: one year: \$258.00, two years: \$413.00; one year Canada/Mexico: \$360.00, two years: \$573.00; one-year international airmail: \$434.00, two years: \$691.00; Single copy price: \$15.00 in the US, and \$20.00 Beswhere. Digital distribution: \$130.00. You will continue to receive your subscription free of charge. This fee is only for airmail delivery. Address correspondence regarding subscriptions (including change of address) to: Solid State Technology, 1786 18th Street, San Francisco, CA 94107-erad to be a content of the subscription free of the subscription free

#### For subscription inquiries:

Tel: 847.559.7500; Fax: 847.291.4816; Customer Service e-mail: sst@omeda.com; Subscribe: www.sst-subscribe.com

Solid State Technology is published eight times a year by Extension Media LLC, 1786 Street, San Francisco, CA 94107. Copyright © 2015 by Extension Media LLC. All rights reserved. Printed in the U.S.

1786 18th Street San Francisco, CA 94107

**Conference & Networking Event** JUNE 12-15, 2016 Encore at the Wynn Las Vegas Make plans to attend the semiconductor manufacturing industry's premier conference and networking event.

#### 2015 EVENT HIGHLIGHTS

98% of Attendees responded that the NETWORKING OPPORTUNITIES met or exceeded their expectations

91% of Attendees responded that they would RECOMMEND The ConFab to their colleagues

92% of Attendees responded the QUALITY OF THE CONFERENCE met or exceeded their expectations

MAKE PLANS TO ATTEND THE CONFAB 2016

For more information, please contact: Sabrina Straub 603.770.6569 sstraub@extensionmedia.com

Owned and Produced by:

www.theconfab.com

Presented by:

# Online@www.solid-state.com

### Web Exclusives

### What chipmakers will need to address growing complexity, cost of IC design and yield ramps

As these early days of the Internet of Things show the network's promise and reveal technological challenges that could threaten its ability to meet user expectations in the years ahead, technology providers will be charged with supplying the solutions that will meet those challenges. http://bit.ly/1E3NImR

## Process Watch: The most expensive defect – Part 2

The December 2014 edition of Process Watch suggested that the most expensive defect is the one that goes undetected until the end of line. Indeed, undetected excursions typically result in the scrap of millions of dollars per year of defective semiconductor chips. But many electronics suppliers and OEMs would argue that the consequences of field failures (reliability defects) are much worse than those of non-functioning devices detected at electrical test (killer defects).

http://bit.ly/1lsQWGN

# Tackling advanced litho challenges on the path to node 5

If you attended just about any mask making conference in the last five to seven years, you would have heard the lament about exploding data volumes and their impact on mask writing time and, by extension, mask costs. The industry is still concerned with data volumes, whether 193nm immersion or EUVL.

#### http://bit.ly/1FW02u4

# Move over, 16nm – here comes 10nm chips

Those 16-nanometer chips with FinFETs? Yesterday's news. Taiwan Semiconductor Manufacturing wants you to know that they're ready, willing, and able to help you design chips with 10-nanometer features.

http://bit.ly/1FF31Z0

## Apple Watch and ASE start new era in SiP

Back in April, the Apple Watch appeared in Chipworks' labs, and of course, they pulled it apart to see its contents.

http://bit.ly/1WCRpAs

#### Insights from the Leading Edge: News from Toshiba, UMC, and Nvidia

In his 250th blog post, Phil Garrou reports on Toshiba extending TSV Memory stacking to NAND, UMC entering HVM on SI interposers for AMD FIJI, and Nvidia's Pascal coming in 2016.

http://bit.ly/1J2iELl

#### **Cross-point ReRAM Integration Claimed by Intel/Micron**

The Intel/Micron joint-venture now claims to have successfully integrated a Resistive-RAM (ReRAM) made with an unannounced material in a crosspoint architecture, switching using an undisclosed mechanism. http://bit.ly/1MVhWCR

## SEMICON West: The road forward is 3DIC

SEMICON West 2015 had a strong and rich undercurrent – the roadmap forward is most certainly 3DIC. Yes, the industry can and we will keep pushing dimensions down, but for most designs the path forward would be "More than Moore." As Global-Foundries' CEO Jha recently voiced: It's clear that More-than-Moore is now mainstream rather than niche. http://bit.ly/1KLYPLn

2016 MRS<sup>®</sup> SPRING MEETING & EXHIBIT March 28–April 1, 2016 | Phoenix, Arizona

# **CALL FOR PAPERS**

#### CHARACTERIZATION AND MODELING OF MATERIALS

- CM1 New Frontiers in Aberration Corrected Transmission Electron Microscopy

- CM2 Quantitative Tomography for Materials Research CM3 Mechanics and Tribology at the Nanoscale—

- In Situ and In Silico Investigations CM4 Verification, Validation and Uncertainty Quantification in Multiscale

- Materials Simulation

#### **ENERGY AND ENVIRONMENT**

- EE1 Emerging Materials and Phenomena for Solar Energy Conversion

- EE2 Advancements in Solar Fuels Generation— Materials, Devices and Systems

- EE3 Materials and Devices for Full Spectrum Solar Energy Harvesting

- EE4 Electrode Materials and Electrolytes for Lithium and Sodium Ion Batteries

- EE5 Next-Generation Electrical Energy Storage Chemistries

- EE6 Research Frontiers on Liquid-Solid Interfaces in Electrochemical Energy Storage and Conversion Systems

- EE7 Mechanics of Energy Storage and Conversion— Batteries, Thermoelectrics and Fuel Cells

- EE8 Grid-Scale Energy Storage

- EE9 Hydrogen and Fuel Cell Technologies for Transportation-Materials, Systems and Infrastructure

- EE10 Recent Advances in Materials for Carbon Capture

- EE11 Caloric Materials for Renewable Energy Applications

- EE12 Radiation Damage in Materials—A Grand Multiscale Challenge

- EE13 Actinides—Fundamental Science, Applications and Technology

- EE14 Titanium Oxides—From Fundamental Understanding to Applications

- EE15 Materials for Sustainable Development—Integrated Approaches

#### www.mrs.org/spring2016

#### **Meeting Chairs**

Christopher A. Bower X-Celeprint Ltd.

Andrew M. Minor University of California, Berkeley Lawrence Berkeley National Laboratory

**Roger Narayan** UNC/NCSU Joint Department of Biomedical Engineering

Izabela Szlufarska University of Wisconsin-Madison Osamu Ueda Kanazawa Institute of Technology

#### **Don't Miss These Future MRS Meetings!**

2016 MRS Fall Meeting & Exhibit November 27 – December 2, 2016 Boston, Massachusetts

**2017 MRS Spring Meeting & Exhibit** April 17 – 21, 2017 Phoenix, Arizona

#### MRS MATERIALS RESEARCH SOCIETY

506 Keystone Drive • Warrendale, PA 15086-7573 Tel 724.779.3003 • Fax 724.779.8313 info@mrs.org • www.mrs.org

#### **ELECTRONICS AND PHOTONICS**

- EP1 Organic Excitonic Systems and Devices

- EP2 Silicon Carbide—Substrates, Epitaxy, Devices, Circuits and Graphene

Abstract Submission Opens September 15, 2015

Abstract Submission Deadline

October 15, 2015

- EP3 Perovskite-Based Photovoltaics and Optoelectronic Devices

- EP4 Emerging Silicon Science and Technology

- EP5 Metal Oxide Hetero-Interfaces in Hybrid Electronic Platforms

- EP6 Integration of Heterovalent Semiconductors and Devices

- EP7 Material and Device Frontiers for Integrated Photonics

- EP8 Resonant Optics—Fundamentals and Applications

- EP9 Materials and Processes for Nonlinear Optics

- EP10 Optoelectronic Devices of Two-Dimensional (2D) Materials

- EP11 Novel Materials for End-of-Roadmap Devices in Logic, Power and Memory

- EP12 Materials Frontiers in Semiconductor Advanced Packaging

- EP13 Tailoring Superconductors—

- Materials and Devices from Basic Science to Applications

- EP14 Materials for Next-Generation DisplaysEP15 Diamond Power Electronic Devices

#### **MATERIALS DESIGN**

- MD1 Materials, Interfaces and Devices by Design

- MD2 Tuning Properties by Elastic Strain Engineering from Modeling to Making and Measuring

- MD3 Functional Oxide Heterostructures by Design

- MD4 Phase-Change Materials and Applications

- MD5 Fundamentals of Organic Semiconductors—

- Synthesis, Morphology, Devices and Theory MD6 Electronic Textiles

- ND6 Electronic Textiles

- MD7 Advances in Lanthanide Materials for Imaging, Sensing, Optoelectronics and Recovery/Recycling

- MD8 Multiscale Behavior of Materials in Extreme Environments

- MD9 Magnetic Materials—From Fundamentals to Applications

- MD10 Micro-Assembly Technologies

#### NANOTECHNOLOGY

- NT1 Functional Nanostructures and Metamaterials for Solar Energy and Novel Optical Phenomena

- NT2 Oxide and Chalcogenide-Based Thin Films and Nanostructures for Electronics and Energy Applications

- NT3 Carbon Nanofluidics

- NT4 Emerging Non-Graphene 2D Materials

- NT5 Nanodiamonds—Fundamentals and Applications

- NT6 Colloidal Nanoparticles—From Synthesis to Applications

- NT7 Nanoparticle Characterization and Removal

- NT8 Silicon Nanostructures—Doping, Interface Effects and Sensing

#### SOFT MATERIALS AND BIOMATERIALS

- SM1 Liquid Crystalline Materials—Displays and Beyond

- SM2 Bioinspired Dynamic Materials—Synthesis, Engineering and Applications

- SM3 Soft Materials for Compliant and Bioinspired Electronics

- SM4 Engineering Biointerfaces with Nanomaterials

- SM5 Surfaces and Interfaces for Biomaterials

- SM6 Transient and Biologically-Inspired Electronics

- SM7 Future Healthcare Needs through Biomaterials, Bioengineering and the Cellular Building Block

- SM8 Bioinspired Metal Nanoparticles—Synthesis, Properties and Application

- SM9 Structure and Properties of Biological Materials and Bioinspired Designs

- SM10 Biofabrication-Based Biomaterials and Tissues

Please send news articles to sdavis@extensionmedia.com

#### worldnews

**USA – FSUSS MicroTec** announced new competence-center for nanoimprint in North America.

**USA – Qualcomm** completed its \$2.4B acquisition of **CSR**.

**EUROPE – imec** announced plans to extend its GaN-on-Si R&D program, and is now offering joint research on GaN-on-Si 200mm epitaxy and enhancement mode device technology.

ASIA – MagnaChip will host its first Foundry Technology Symposium in Shanghai, China.

USA – Microchip Technology completed its acquisition of Micrel.

ASIA – Toshiba launched 16MP CMOS image sensors targeting smartphones and tablets.

**EUROPE – CEA-Leti** and **EV Group** launched a new program in nanoimprint lithography called INSPIRE.

ASIA – STATS ChipPAC announced the promotion and appointment of Dr. Han Byung Joon as Co-President and CEO for the company.

**USA-Applied Materials** unveiled the Applied Olympia ALD system.

**EUROPE- CEA-Leti** reported FinFET feasibility and circuit design with its CoolCube technology.

**USA – Intel** announced it will invest \$5 million in its engineering partnership with **Georgia Tech** over the next five years.

## Chinese chipmaker Tsinghua prepares \$23B bid for Micron Technology

By Shannon Davis, Web Editor

China's state-owned Tsinghua Unigroup Ltd. is preparing a \$23 billion bid for chipmaker Micron Technology, in what analysts say would be the biggest Chinese takeover of a U.S. company.

Tsinghua, China's largest state-owned chip design company, is prepared to bid \$21 per share for Micron, according to Dow Jones.

As of Tuesday, a Micron spokesman told Reuters that the company had not yet received an offer, while Tsinghua chairman Zhao Weiguo told Bloomberg that the Chinese company was "very interested in cooperation" with Micron.

Tsinghua's potential purchase of Micron is regarded as a strategic move to help the advancement of China's own chip sector. The country currently has no major home-grown memory makers, according to Reuters.

Micron is the last remaining U.S. producer of DRAM memory chips, and any foreign

takeover would still have to pass a review by the Committee on Foreign Investment in the United States, to examine the national security implications of the deal. The deal would also need to be examined by the Chinese National Development and Reform Commission.

This would not be the first significant consolidation in the memory sector this year. In May, Hewlett-Packard sold a 51 percent stake in its data-networking business to Tsinghua for approximately \$2.3 billion.

"Valuation appears low as a potential \$21 a share bid is 8.3 times fiscal year PE or low end of the historic range of 7 to 15 whereas Micron was at \$32 just 5 months ago," UBS analyst Stephen Chin told MarketWatch.

MarketWatch speculated that a cheap valuation could encourage other companies to launch their own bids.  $\clubsuit$

# Intel and Micron produce breakthrough memory technology

Intel Corporation and Micron Technology, Inc. unveiled 3D XPoint technology, a non-volatile memory that has the potential to revolutionize any device, application or service that benefits from fast access to large sets of data. Now in production, 3D XPoint technology is a major breakthrough in memory process technology and the first new memory category since the introduction of NAND flash in 1989.

The explosion of connected devices and digital services is generating massive amounts of new data. To make this data useful, it must be stored and analyzed very quickly, creating challenges for service providers and system builders who must balance cost, power and performance trade-offs when they design memory and storage solutions. 3D XPoint technology combines the performance, density, power, non-volatility and cost advantages of all available memory technologies on the market today. The technology is up to 1,000 times faster and has up to 1,000 times greater endurance3 than NAND, and is 10 times denser than conventional memory.

"For decades, the industry has searched for ways to reduce the lag time between the

Continued on page 8

## **GLOBALFOUNDRIES** completes acquisition of IBM Microelectronics business

GLOBALFOUNDRIES announced that it has completed its acquisition of IBM's Microelectronics business.

With the acquisition, GLOBALFOUNDRIES gains differentiated technologies to enhance its product offerings in key growth markets, from mobility and Internet of Things (IoT) to Big Data and high-performance computing. The deal strengthens the company's workforce, adding decades of experience and expertise in semiconductor development, device expertise, design, and manufacturing. And the addition of more than 16,000 patents and applications makes GLOBALFOUNDRIES the holder of one of the largest semiconductor patent portfolios in the world.

"Today we have significantly enhanced our technology development capabilities and reinforce our long-term commitment to investing in R&D for technology leadership," said Sanjay Jha, chief executive officer of GLOBALFOUNDRIES. "We have added world-class technologists and differentiated technologies, such as RF and ASIC, to meet our customers' needs and accelerate our progress toward becoming a foundry powerhouse."

Through the addition of some of the brightest and most innovative scientists and engineers in the semiconductor industry, GLOBALFOUNDRIES solidifies its path to advanced process technologies at 10nm, 7nm, and beyond.

In RF, GLOBALFOUNDRIES now has technology leadership in wireless front-end module solutions. IBM has developed world-class capabilities in both RF silicon-on-insulator (RFSOI) and high-performance silicon-germanium (SiGe) technologies, which are highly complementary to GLOBALFOUNDRIES' existing mainstream technology offerings. The company will continue to invest to deliver the next generation of its RFSOI roadmap and looks to capture opportunities in the automotive and home markets.

In ASICs, GLOBALFOUNDRIES now has technology leadership in wired communications. This enables the company to provide the design capabilities and IP necessary to develop these high-performance customized products and solutions. With increased investments, the company plans to develop additional ASIC solutions in areas of storage, printers and networking. The most recent ASIC family, announced in January and built on GLOBALFOUNDRIES' 14nm-LPP technology, has been well accepted in the marketplace with several design wins.

GLOBALFOUNDRIES increases its manufacturing scale with fabs in East Fishkill, NY and Essex Junction, VT. These facilities will operate as part of the company's growing global operations, adding capacity and top-notch engineers to better meet the needs of its existing and new customers.

Moreover, the transaction builds on significant investments in the burgeoning Northeast Technology Corridor, which includes GLOBALFOUNDRIES' leading-edge Fab 8 facility in Saratoga County, NY and joint R&D activities at SUNY Polytechnic Institute's College of Nanoscale Science and Engineering in Albany, NY. The company's presence in the northeast now exceeds 8,000 direct employees.

The acquisition includes an exclusive commitment to supply IBM with advanced semiconductor processor solutions for the next 10 years. GLOBALFOUNDRIES also gets direct access to IBM's continued investment in semiconductor research, solidifying its path to advanced process geometries at 10nm and beyond.

# THE POWER of TWO.

## two lasers | one station the IX-280-ML Multi-laser Micromachining System

higher efficiency

greater flexibility

lower cost of ownership

+1 (603) 518-3200 www.ipgphotonics.com sales.ipgm@ipgphotonics.com

PHOTONICS

# newscont.

#### IBM Research alliance produces industry's first 7nm node test chips

IBM Research announced that working with alliance partners at SUNY Polytechnic Institute's Colleges of Nanoscale Science and Engineering (SUNY Poly CNSE) it has produced the semiconductor industry's first 7nm (nanometer) node test chips with functional transistors. The breakthrough underscores IBM's continued leadership and long-term commitment to semiconductor technology research.

The accomplishment, made possible through IBM's unique public-private partnership with New York State and joint development alliance with GLOBALFOUNDRIES, Samsung and equipment suppliers, is driven by the company's \$3 billion, five-year investment in chip R&D announced in 2014. Under that program, IBM researchers based at SUNY Poly's NanoTech Complex in Albany are pushing the limits of chip technology to 7nm node and beyond to meet the demands of cloud computing and Big Data systems, cognitive computing and mobile products.

Developing a viable 7nm node technology has been one of the grand challenges of the semiconductor industry. Pursuing such small dimensions through conventional processes has degraded chip performance and negated the expected benefits of scaling — higher performance, less cost and lower power requirements. Microprocessors utilizing 22nm and 14nm technology power today's servers, cloud data centers and mobile devices, and 10nm technology is well on the way to becoming a mature technology, but 7nm node has remained out of reach due to a number of fundamental technology barriers. In fact, many have questioned whether the traditional benefits of such small chip dimensions could ever be achieved.

The IBM 7nm node test chip with functioning transistors was achieved using new semiconductor processes and techniques

pioneered by IBM Research. Developing it required a number of first-in-the-industry innovations, most notably silicon germanium (SiGe) channel transistors and extreme ultraviolet (EUV) lithography integration at multiple levels.

By introducing SiGe channel material for transistor performance enhancement at 7nm node geometries, process innovations to stack them below 30nm pitch and full integration of EUV lithography at multiple levels, IBM was able to achieve close to 50 percent area scaling improvements over today's most advanced 10nm technology. These efforts could result in at least a 50 percent power/performance improvement for the next generation of systems that will power the Big Data, cloud and mobile era.

The 7nm node milestone continues IBM's legacy of historic contributions to silicon and semiconductor innovation. They include the invention or first implementation of the single cell DRAM, the Dennard Scaling Laws, chemically amplified photoresists, copper interconnect wiring, Silicon on Insulator, strained engineering, multi core microprocessors, immersion lithography, high speed SiGe, High-k gate dielectrics, embedded DRAM, 3D chip stacking and Air gap insulators.

IBM and SUNY Poly have built a highly successful, globally recognized partnership at the multi-billion dollar Albany NanoTech Complex, highlighted by the institution's Center for Semiconductor Research (CSR), a \$500 million program that also includes the world's leading nanoelectronics companies. The CSR is a long-term, multi-phase, joint R&D cooperative program on future computer chip technology. It continues to provide student scholarships and fellow-ships at the university to help prepare the next generation of nanotechnology scientists, researchers and engineers.

#### Intel and Micron, Continued from page 6

processor and data to allow much faster analysis," said Rob Crooke, senior vice president and general manager of Intel's Non-Volatile Memory Solutions Group. "This new class of non-volatile memory achieves this goal and brings gamechanging performance to memory and storage solutions."

"One of the most significant hurdles in modern computing is the time it takes the processor to reach data on long-term storage," said Mark Adams, president of Micron. "This new class of non-volatile memory is a revolutionary technology that allows for quick access to enormous data sets and enables entirely new applications."

As the digital world quickly grows – from 4.4 zettabytes of digital data created in 2013 to an expected 44 zettabytes by 20204

- 3D XPoint technology can turn this immense amount of data into valuable information in nanoseconds. For example, retailers may use 3D XPoint technology to more quickly identify fraud detection patterns in financial transactions; healthcare researchers could process and analyze larger data sets in real time, accelerating complex tasks such as genetic analysis and disease tracking.

The performance benefits of 3D XPoint technology could also enhance the PC experience, allowing consumers to enjoy faster interactive social media and collaboration as well as more immersive gaming experiences. The non-volatile nature of the technology also makes it a great choice for a variety of low-latency storage applications since data is not erased when the device is powered off.

#### New recipe, architecture for breakthrough memory technology

Following more than a decade of research and development, 3D XPoint technology was built from the ground up to address the need for non-volatile, high-performance, high-endurance and high-capacity storage and memory at an affordable cost. It ushers in a new class of non-volatile memory that significantly reduces latencies, allowing much more data to be stored close to the processor and accessed at speeds previously impossible for non-volatile storage.

The innovative, transistor-less cross point architecture creates a three-dimensional checkerboard where memory cells sit at the intersection of word lines and bit lines, allowing the cells to be addressed individually. As a result, data can be written and read in small sizes, leading to faster and more efficient read/write processes.

3D XPoint technology will sample later this year with select customers, and Intel and Micron are developing individual products based on the technology.

# **ATH-M**

#### Magnetically levitated turbopumps from 500 l/s to 3200 l/s

- Very high gas throughput for all process gases

- Low lifetime costs due to maintenance-free technology

- Standard, heated and corrosion resistant coating versions available

- Available with integrated or external controller

Are you looking for a perfect vacuum solution? Please contact us: **Pfeiffer Vacuum, Inc.** · USA · T 800-248-8254 · F 603-578-6550 · contact@pfeiffer-vacuum.com www.pfeiffer-vacuum.com

# **news**cont

## New AMS Fab Going to Marcy NY

Austria-based ams AG, formerly known as Austriamicrosystem, announced plans to locate a new 360,000 ft2 fab in upstate New York at the Nano Utica site in Marcy, NY. The fab will be used to manufacture analog devices on 200/300mm wafers. Total buildout at the site, including support buildings and office space, will be close to 600,000ft2.

This will be the first fab going into the 428 acre Marcy site, which is large enough to accommodate three fabs and an R&D or packaging facility.

Construction of the ams fab is scheduled to begin in spring 2016, with first wafer ramp in the last quarter of 2017.

In what might become the new business model for fabs, the building itself will be publicly owned and leased to ams, which will assume operating costs and most of the costs of the capital equipment. Capital purchases, operating expenses and other investments in the facility over the first 20 years are estimated at more than \$2 billion. ams will create and retain more than 700 full time jobs and anticipates the creation of at least 500 additional support jobs from contractors, subcontractors, suppliers, and partners necessary to establish the full ecosystem necessary to enable advanced manufacturing operations.

Fort Schuyler Management (FSMC) will handle the construction, with the goal of turning the fab over to ams in Q2 2017. A key part of N.Y. Mario Governor Cuomo's START-UP NY initiative, FSMC is a State University of New York (SUNY Polytechnic Institute) affiliated, private, not-for-profit, 501c(3) corporation that facilitates research and economic development opportunities in support of New York's emerging nanotechnology and semiconductor clusters.

"If jobs are being created, everything else will take care of itself," Cuomo said.

Mohawk Valley EDGE President Steve DiMeo said site work has already started. "We're putting roads in, storm drainage, utilities and we just approved the change order for clearing the land where ams will be located. We'll be doing some additional site development this fall, and work closely with Fort Schuyler so that they will be in a position to begin construction the early part of next year."

In a related announcement, GE Global Research said it will expand its New York global operations to the Mohawk Valley, serving as the anchor tenant of the Computer Chip Commercialization Center (QUAD C) on the campus of SUNY Polytechnic Institute's Colleges of Nanoscale Science and Engineering in Utica. Nearly 500 jobs are expected to be created in the Mohawk Valley in the next five years from SUNY Poly, GE and affiliated corporations and another 350 in the subsequent five years.

These public-private partnerships represent the launch of the next phase of the Governor's Nano Utica initiative, which now exceeds more than 4,000 projected jobs over the next ten years. Designed to replicate the dramatic success of SUNY Poly's Nanotech Megaplex

An artist's rendering of what a fab would look like at the Marcy site.

in Albany, NANO Utica further cements New York's international recognition as the preeminent hub for 21st century nanotechnology innovation, education, and economic development.

"This is a transformative moment that will make a difference in peoples' lives in the Mohawk Valley for generations to come," said Governor Cuomo. "Over the past few years, we have worked to reverse the negative and invest in Upstate NY – and today we're taking another huge step forward. With GE and ams joining the Nano Utica initiative, we're seeing the region's economy gathering momentum unlike ever before. The Mohawk Valley is beginning an economic revolution around nanotechnology, and I am excited to see the region take off and thrive, both today and in the years ahead."

Dr. Alain Kaloyeros, President and Chief Executive Officer of SUNY Polytechnic Institute, said, "Today's announcement by Governor Andrew Cuomo represents a major expansion for Quad-C and the Nano Utica initiative and is a tremendous victory for the Mohawk Valley and the entire State of New York. World renowned partners such as GE Global Research and AMS raise the level of prestige for the entire region and accelerate the development of this international hub for technology and innovation. Governor Cuomo's pioneering economic development model, coupled with SUNY Poly CNSE's world class expertise and resources, continues to generate historic investment and job creation throughout the state. We welcome GE and AMS and their leadership teams and look forward to their partnership in the continued growth of Nano Utica."

ams Chief Operating Officer Dr. Thomas Stockmeier said, "Building a new wafer fab will help us achieve our growth plans and meet the increasing demand for our advanced manufacturing nodes. Our decision to locate the facility in New York was motivated by the highly-skilled workforce, the proximity to esteemed education and research institutions, and the favorable business environment provided by Governor Cuomo and all the public and private partners we are working with on this important project."

Additionally, ams will collaborate with FSMC and SUNY Poly on a joint development program to support complimentary research, commercialization and workforce training opportunities at SUNY Poly facilities throughout New York State.

# SEMICON<sup>®</sup> Europa 2015 PE 2015

6 – 8 October • Messe Dresden, Germany www.semiconeuropa.org

SEMICON Europa technology and business programs address the critical issues and challenges facing the microelectronics industry and provide the information, education, and guidance that you need to move your innovations and products to market.

#### **EXHIBITION AREAS**

- Semiconductor Manufacturing Equipment for Front-End and Back-End, Materials and Services

- Allée des Clusters

- Applications and Components Industry 4.0, Medtech, Automotive, Imaging, Power Electronics, Plastic Electronics, IoT, Cool Silicon

- Innovation Village

- Science Park

### **PROGRAM TOPICS**

- Semiconductor Technology including Fab Management, Automation, Advanced Technology Nodes, Lithography, Metrology, New Materials, MEMS

- Advanced Packaging and Test

- Imaging Conference

- Low Power Conference

- Power Electronics Conference

- Plastic Electronics Conference

- Executive and Market Programs

- Silicon Innovation Forum

**Register now online:**

without

limits.

#### WbQtv

Use promotion code and save 25 Euro! Free access to SEMICON Europa 2015. www.semiconeuropa.org

Supported by:

# Advances in thermocompression bonding

## At the 65th IEEE ECTC, several companies presented advances in thermos-compression bonding.

Jie Fu of Qualcomm discussed "Thermal Compression Bonding for Fine Pitch Solder Interconnects." Mass reflow-based interconnects, using either solder bump or Cu-column on bond on lead are the typical low-cost flip chip assembly approaches used by industry. These interconnects face challenges related to shorting and non-wets at sub 100 $\mu$ m pitches. Transitioning below 100 $\mu$ m pitch requires a new approach, such as thermoscompression flip chip (TCFC). While TCFC provides higher accuracy bonding and allows for use of smaller solder cap which enables tighter FC pitch, it also presents new challenges. The major challenges for TCFC bonding include lower throughput and control of non-conductive paste (NCP) voids.

Overall, bond head ramp rate, temperature uniformity, peak temperature and dwell time must be fine-tuned in tandem to compensate for manufacturing tolerances and to get the desired end of line solder joint structure. In addition, controlling the temp exposure for the NCP material before NCP cure is critical to enable a robust TCFC solder joint. Too much thermal exposure and the NCP begins to cure prior to solder melting, which can leading to NCP entrapment and unreliable TCFC solder joints. Laminate surface finish is also an important variable.

In a similar study Cho and co-workers at GlobalFoundries presented "Chip Package Interaction Analysis for 20-nm Technology with Thermo-Compression Bonding with Non-Conductive Paste." Strong market demand for finer pitch interconnects to enable higher I/O counts in a smaller form factor is driving another transition from conventional MR bonding process to thermo-compression bonding using non-conductive paste (TC-NCP). FEA simulation results for TC-NCP vs mass reflow show that TCNCP has significantly reduced thermomechanical stress at the ULK level and the bump level.

Horst Clauberg of K&S discussed "High Productivity Thermocompression Flip Chip Bonding." There is tremendous effort by IDMs, OSATs, materials suppliers and equipment suppliers to bring thermos-compression bonding to commercial reality. The most significant technical challenges have for the most part

## Packaging

production is taking place. However, relatively low throughput and high equipment cost create adoption resis-

been solved and limited commercial

tance, especially in the all-important consumer market.

Thermocompression bonding can be segmented into two different processes. The first process differentiation is whether the underfill is pre-applied before the semiconductor chip is mounted or not. Pre-applied underfill comes either as a film applied to the die or as a paste applied to the substrate. In both cases the underfill must not only create a void-free bond, but also provide flux to remove oxide on the solder caps. The alternative process is thermocompression – capillary underfill (TC-CUF) where the die is underfilled in the same way as standard flip chip, except that the underfill process is much more challenging because of the more narrow bondline of a typical thermocompression bonded device. In TC-CUF, flux can be applied either by dipping the die into flux before bonding, or applying flux to the substrate.

Doug Hiner in a joint presentation between Qualcomm and Amkor presented "Multi-Die Chip on Wafer Thermo-Compression Bonding Using Non-Conductive Film." Non-conductive films have been in development as a replacement to the liquid preapplied underfill materials used in fine pitch copper pillar assembly.

Several assembly methods are available for chip on wafer assembly including: (1) traditional chip attach with mass reflow (MR) and capillary underfill (CUF), (2) thermo-compression bonding (TCB) of copper pillar interconnects using nonconductive paste (NCP) underfill (TCB+NCP), and thermocompression bonding of copper pillar with non-conductive film (NCF) underfill (TCB+NCF).

The TCB+NCP process carries concerns with the underfill time on stage which prevents the dispensing of the NCP material across the wafer prior to the chip bonding process. This constraint effects process costs significantly. The TCB+NCF process to date have not met the cost/benefit needs of the industry. NCF assembly provides significant improvements in the design rules associated with die to package edge, die to die, and fillet size. The NCF process also resolves the time on stage concerns associated with the NCP process by laminating the NCF material to the bonded die instead of to the interposer or receiving wafer surface. ◆

# The IoT and the next 50 years of Moore's Law

Fifty years of technological developments following Moore's Law has changed our world in some phenomenal ways, but Intel's Doug Davis believes the time has come to change the way we think about developing new solutions.

At SEMICON West 2015, Intel's Internet of Things Senior Vice President and General Manager challenged attendees to broaden their thinking on the potential of the IoT and examine their own roles in bringing about global change through new, innovative technology.

"The question is not how do we make these devices smart? The question becomes what are the problems that we can work together to solve?" Davis said.

Davis' presentation addressed four complex issues the world is currently facing: an aging population, climate change, the urban boom, and how we feed the planet, offering real IoT solutions that could impact these growing concerns.

#### loT and an aging population

Since 1950, the average lifespan has increase by more than 20 years. By the year 2050, more people on the planet will be over the age of 60 than under the age of 14.

"As we're all living healthier, longer lives, we also have to reflect that as a society we're unprepared to provide care for these kinds of numbers," said Davis.

Even if the infrastructure were available, if you talk to seniors, they'd rather live out their lives at home, Davis pointed out. How can the IoT help us with this challenge?

#### IoT and climate change

No matter where you stand on global warming, there's no arguing that air quality is becoming a serious issue in an increasing number of cities in the world, Davis said.

He challenged his audience to also think about this problem differently, posing the question, "What if we

#### Semiconductors

reduced emissions at every point in the supply chain?"

Davis cited Intel's own predictive analytics solutions, which have been used in a number of their fabs around the world.

"Engineers at one Intel fab have used this data to reduce mainte-

nance time by 50%, parts replacement by 20%," Davis said. "They were able to reduce non-genuine yield loss by as much as 20%."

With this kind of increase in efficiencies, Davis said Intel believes this also helps to reduce their carbon footprint.

#### loT and the urban boom

"We're undergoing the fastest rural to urban migration in human history," Davis explained. "City populations are growing by 65 million people per year – that's seven new Chicagos every year."

And there are a lot of growing concerns that go along with this boom, from traffic problems to pollution. To address these issues, Davis said Intel has pilot programs now in the UK that are beginning to capture data on traffic patterns, air quality, water supply and more, and overlaying that data with public service agencies, which would allow these agencies and eventually citizens to make real-time decisions and changes.

#### loT and how we feed the planet

Davis argued that the real problem the world is facing isn't how to feed the planet, but the amount of food wasted while so many people go hungry.

"The World Bank says that we're currently wasting ¼ to 1/3 of the food that's being produced on the planet today," said Davis. "We have to get better at distributing food."

Davis shared one example of improved agricultural performance through IoT solutions installed in rice fields in Malaysia, where farmers used ground water and weather forecasting analytics to monitor and make decisions about crop management. In the end, Davis said, farmers were able to see water savings of up to 10% and rice production increase of 50%.

"The genius of Moore's Law showed us what was possible and set the pace for us," Davis said. "Over the next 50 years, think about what's possible – think beyond just the device and into the end-to-end solutions we can create, and we can tackle these huge challenges worldwide." ◆ LITHOGRAPHY

# Lithography alternatives: Why are they essential?

LAURENT PAIN, RALUCA TIRON, LUDOVIC LATTARD, STEFAN LANDIS and CYRILLE LAVIRON,

CEA-Leti, Grenoble, France

The availability of patterning alternatives in the lithography landscape represents a big opportunity to properly address the coming needs generated by the IoT.

he Internet of Things (IoT) is expected to fuel significant growth opportunities for the semiconductor industry, as demand increases for wireless components and more and more embedded functionalities such as memory and sensors. This growth will affect almost all integrated circuit (IC) sectors (**FIGURE 1**). The chip industry will continue to need advanced technologies to provide the most powerful functionalized ICs with lower power consumption for the IoT, but manufacturing costs remain a key challenge. Lithography and related patterning technologies can represent up to 50 percent of total IC production costs, and significant efforts have to be made in the coming years to slow and even reverse this trend.

In the lithography landscape for the development of advanced technology nodes, extreme-UV (EUV) lithography technology recovered some credibility

FIGURE 1. Impact of the IoT on semiconductor industry revenue from 2000 to 2020.

at the beginning of 2015 with the release and installation of the first 80W power sources[1]. However, its adoption by the industry remains uncertain, because its infrastructure still requires significant development. Also, the recurrent questions about the real cost of ownership associated with the ability of the 0.33NA platform to address sub-7nm technology nodes continue to dominate the debate in the semiconductor community, especially since 3D-stacking strategies are being seriously investigated. This potentially could slow demand for high-resolution and therefore delay the new advanced lithography solutions.

Meanwhile, 193nm immersion lithography, with double- or quadruple-patterning strategies, supports the industry preference for advanced-node developments, despite the tremendous effort required for process controls (alignment, mask manufacturing etc.). In this landscape, lithography alternatives maintain promise for continued R&D because they may present competitive compromises for the industry. Massively parallel electron-beam and nano-imprint lithography techniques remain highly attractive, as they can provide noteworthy cost-of-ownership benefits for IC manufacturers. In addition, directed self-assembly (DSA) lithography with block copolymer shows promising resolution capabilities and appears to be an option to reduce multipatterning strategies, and therefore the associated mask-set budgets. But what is the current status of these technologies? Are they really able to meet

**LAURENT PAIN** is lithography program manager at Leti, **RALUCA TIRON** is head of the IDEAL program, **LUDOVIC LATTARD** is head of the IMAGINE program, **STEFAN LANDIS** is head of the INSPIRE program and **CYRILLE LAVIRON** is lithography laboratory manager at Leti.

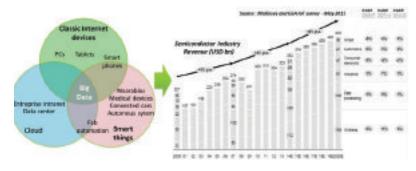

**FIGURE 2.** CEA-Leti schematic on DSA process environment validation

industry expectations for advanced technology nodes? Are they indeed able to reduce manufacturing costs? What are their introduction points into the production environment?

CEA-Leti is working to answer these questions and has initiated collaborative R&D programs to assess and boost the development of these alternative technologies through strategic partnerships. Three programs have been launched with the primary goals of demonstrating that these lithography options can meet industry needs, assessing industrial use of them and proposing to Leti's IDM partners real turn-key integrated process-flow solutions.

- **IMAGINE:** launched in 2009 with MAPPER Lithography, this program is pushing for the insertion of massively parallel direct-write electron-beam technology. Other participants include TSMC, STMicroelectronics, Nissan Chemical, Mentor Graphics, SCREEN, Tokyo Electron and Aselta Nanographics.

- **IDEAL:** DSA lithography represents a promising solution for advanced patterning. Leti has worked with Arkema since 2011 on the qualification and demonstration of materials for insertion into industrial production flow. Other partners include ST, Tokyo Electron, SCREEN, Mentor Graphics and CNRS-LCPO.

- **INSPIRE:** established in 2015 with the EV Group, this program will focus on the assessment of imprint technology on large-scale patterning.

## Directed self assembly: the resolution is in polymer matrix

Since 2010, DSA has steadily attracted attention of R&D laboratories and the IDM industry. The natural highresolution capability of the block copolymer (sub-10nm) may meet the requirements of future technology nodes. Significant work in this area is underway at R&D consortia such as imec, IBM Research in Albany, N.Y., and Leti, as well as directly in the fab[2,3]. For example, Leti and its partners put in place a full infrastructure to qualify the new material developed by the chemical company Arkema (FIGURE 2). A full 300mm line is operational at Leti using a Tokyo Electron track and a customized SCREEN DUO track able to handle the latest process possibilities. This type of infrastructure is required to validate in fab-like conditions the new materials (PS-PMMA and high chi platforms) and their associated integration flows. Those operating conditions give industry the capability to quickly evaluate the full process-flow performances with all the required classic statistical data for final validation.

### Looking for a perfect packaging process? YES has the answer!

YES polyimide cure ovens offer consistent, quality:

Polyimide cure BCB cure Low temp polymers cure Low-k dielectric cure Copper anneal

Uniform solvent evaporation Optimal temperature control Oxygen-free environment Cleaner process

For more information, visit <u>www.yieldengineering.com</u> or call 925-373-8353

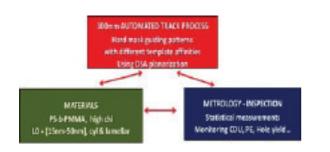

**FIGURE 3.** DSA defectivity trend on lamellar. Courtesy T Younkins (Intel) - Private communication.

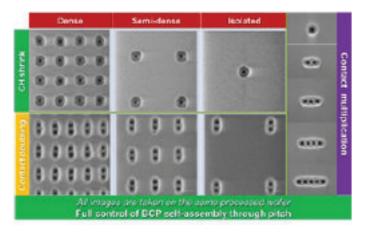

FIGURE 4. Control of iso-dense bias density in Leti DSA

Focusing on defectivity Intel showed convincing data at 1def/cm<sup>2</sup> on line-and-space structures, confirming the potential of DSA to reach the ITRS target and therefore to be used for manufacturing in the near future (**FIGURE 3**). As well, Leti results on grapho-epitaxy process are also very encouraging with zero visual-defect process flow for contact/via application measured with low statistical level[4]. Those results are the first positive key trends in the DSA technology. Evaluating the compatibility of DSA with semiconductor process flows is the next important step. The control of the iso-dense configuration focused

**FIGURE 6.** Example of MAPPER Lithography patterning capability on the pre-alpha platform[5]

a lot of attention on the grapho-epitaxy process, in which block copolymer film-filling uniformity is affected by the topography effects of the guide patterns. Leti developed and patented a flow allowing a proper control of CD and CDU in all density configurations. (**FIGURE 4**) This solution preserves the interest of DSA as it is integrated in the process flow itself and because it does not imply a need for any additional design-rule restriction[4].

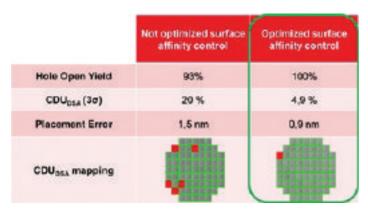

Nevertheless, some hurdles remain to be overcome before its final adoption. The control of the surface affinity is one key aspect. It can greatly affect the final defectivity level and impact the complexity of the integration flow (FIGURE 5). Any non-uniform control of the bottom residual polymer thickness in the bottom of the guide cavity may lead to post-etch opening issues and final circuit-yield drop. Moreover, to be fully adopted, DSA technology also must be aligned with the compatible design rule manuals. Insertion in the DRM is essential and it implies adding new specific constraints due to the nature of the block copolymer and to the lithography guide realization. All these R&D efforts must be pushed to value the advantages of DSA technology: the natural high resolution of this solution and its cost effectiveness from reducing multiexposure strategy. In addition to ensuring DSA's ability to extend 193nm immersion lithography, it also supports the use of the EUV 0.33NA tool for the development of 7nm nodes and below.

#### Massively parallel electron-beam writing

Despite recurrent delays in new developments, parallel electron-beam lithography remains an attractive alternative option. The massively parallel writing solutions developed by MAPPER Lithography and IMS Nanofabrication for wafer and mask writing, respectively, offer good compromises: a significant alliance of resolution and advantageous manufacturing costs. But this technology also benefits from additional advantages, such as writing flexibility and a significant throughput improvement due to the parallel exposure concept that can boost the throughput in the future up to 100 wafers per hour in a cluster-tool configuration. First pre-industrial units are today installed in pilot-line environments, foreshadowing their introduction into production lines in coming years.

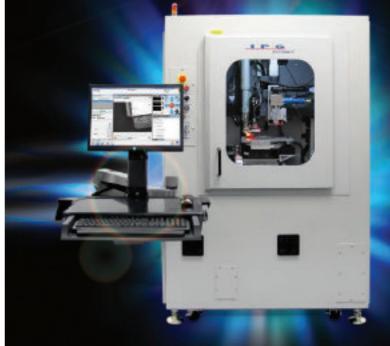

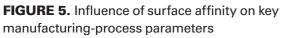

MAPPER and Leti's collaboration is focused on introducing this technology for direct-write application. This joint program started in 2009 around the MAPPER's pre-alpha tool that validated the key concept of the MAPPER technology in terms of parallel writing and resolution capabilities (**FIGURE 6**). The partnership entered in a new phase in 2014 with the installation of the first FLX-1200 pre-production platform, (**FIGURE 7**), operating 1,300 beam lines for a targeted throughput of 1 wph and then scalable to 10 wph by increasing the beam line count up to 13,000.

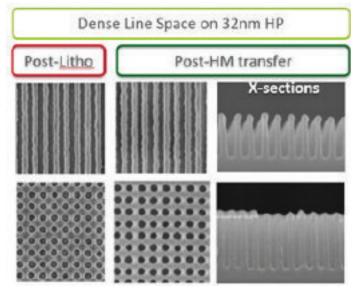

This FLX-1200, which is being ramped up now, already has shown imaging performances that match its specifications. Full 300mm wafers can be printed in one hour with 32nm half-pitch resolution (**FIGURE 8**). In the IMAGINE program, Leti and its partners are also working to validate a complete turn-key integrated solution allowing fast and secure wafer processing from design to silicon. Such infrastructure developments around data treatment, materials, process, etch and metrology will be required to speed-up the insertion of the MAPPER technology into future production lines.

Leti and MAPPER will demonstrate the operational

**FIGURE 7.** MAPPER FLX-1200 in Leti cleanroom interfaced with a SCREEN DUO track. Key figures of the tool: Acceleration voltage 5kV; throughput: 1wph with 1,300 beamlines; resolution/alignment specs:  $32nmhp / 10nm 3\sigma$ .

**FIGURE 8.** First imaging performance of the FLX-1200 on full 300mm wafer

capability of the FLX-1200 in its final configuration, including mix-and-match alignment performances. The achievement of this key demonstration milestone is essential to launching this technology. Then, after final ramp-up, the MAPPER platform is expected to be aligned in terms of specifications with 14nm technology (32nm hp). A wide range of potential applications based on its mask-less concept and throughput potential already have been clearly identified: CMOS prototyping and low-volume production, complementary lithography concept for high-end patterning[6], new industry segments (photonics, low-cost circuit functionalization, large field exposure, etc.).

#### Nano-imprint lithography

Nano-imprint lithography (NIL) stands out from the other conventional lithography processes (photolithography, electronic lithography, EUV lithography) because of the fundamental mechanism of creating the final structures. In the case of nano-imprint, the flow of the resist directly shapes the pattern through the stamp cavities, eliminating the need for chemical contrast, as is the case for optical lithography resists. In recent decades, significant efforts have been made to extend the distance between the photomask and the resist-coated wafer to reduce defectivity and enhance resolution. Therefore, for many scientists, NIL technology appeared to be a UFO, since the process is based on the intimate contact between the working stamp and the resist to be embossed.

In the past 20 years, significant progress has been made to make the technology more mature and ready for high-volume manufacturing. Among the several existing

Full-wafer imprint

Step-and-flash imprint

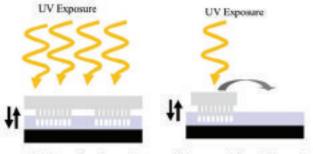

**FIGURE 9.** Schematic description of the full-wafer and step-and-flash imprint options.

NIL technology alternatives, the UV-based imprint, using transparent stamp, is today the standard one. Two wellestablished options are now available on the market: the full-wafer imprint (the size of the stamp corresponds to the size of the wafer to be printed) and the step-and-flash imprint in which a small stamp (i.e. die size) is stepped, as in optical lithography across the wafer to be processed (**FIGURE 9**).

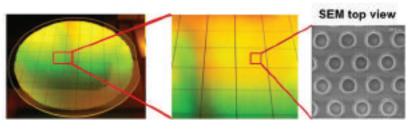

If the step-and-flash NIL technology is better suited to address the semiconductor markets (NAND flash memory, DRAM and logic) with its high level-alignment capability and its good control of defectivity density[7], the full-wafer NIL option could quickly become the reference manufacturing option for the emerging and growing markets such as LED and photonics-based devices (**FIGURE 10**).

However, this wafer-scale imprint solution still lacks quantitative data regarding its technology assessment for high-volume manufacturing. Commercial equipment[8] and resists, the cornerstones of this technology, are already available. But some links in the industrial supply chain (design rules, master manufacturing and repair, in-line defectivity and metrology controls, fully integrated process flows) still must be established and qualified to make this technology more mature.

To accelerate adoption of this technology, Leti and EV Group launched in June 2015 a new collaborative industrial program called INSPIRE, aimed at demonstrating the benefits of this full-wafer NIL technology and spreading its use for applications beyond the traditional semiconductor industry. Much more than a classic industrial partnership, the program is designed to support development of new applications from the feasibility-study stage up to the first manufacturing steps,

**FIGURE 10.** Full wafer scale imprinted wafer for photonic crystal application.

including the prototyping phase in Leti's clean room. INSPIRE is also designed to demonstrate the technology's cost-of-ownership benefits for a wide range of application domains. The final objective of this program is to facilitate the transfer of the developed integrated process solutions to industrial partners. The steps should significantly lower the entry barrier for NIL technology and speed up its use in production lines.

#### Conclusion

The availability of patterning alternatives in the lithography landscape represents a big opportunity to properly address the coming needs generated by the IoT. Besides conventional optical lithography, they offer industry new and/or complementary advantages: innovation capability and opportunities to better manage cost of ownership. But not only that! The high-resolution potential, the ability to facilitate design-innovation validation, and the complementarity of these alternatives with other patterning solutions also highlight their strengths. The step now is to finalize the evaluation of these technologies with respect to industry standards and establish them as real and credible lithography alternatives.

#### References

- A. Schafgans et al, Proc SPIE, Extreme Ultraviolet Lithography VI, Vol. 9422, 2015

- 2. S. Sayan et al, Proc. SPIE, Advances in Patterning Materials and Processes XXXII, Vol. 9425, 2015

- 3. H. Tsai et al, ACS nano, vol 8 (5), pp. 5227-5232, 2014

- R. Tiron et al, Alternative Lithographic Technologies II, Vol. 9423, 2015

- 5. L. Pain et al, SEMICON Europa symposium, Dresden, Oct 2013

- 6. D. Lam et al, Proc SPIE, Photomask Technology, Vol. 7823, 2010

- 7. H. Takeishi et al, Proc SPIE

- 8. EVG product flyer, EVG HERCULES NIL platform, web site: http://www.evgroup.com/en/products/lithog raphy/nanoimprint\_systems/uv\_nil/hercules\_nil

# Managing dis-aggregated data for SiP yield ramp

ED KORCZYNSKI, Senior Technical Editor

## New ways are needed to feed data back and forth between designers, chip fabs, and Out-Sourced Assembly and Test (OSAT) companies.

In general, there is an accelerating trend toward System-in-Package (SiP) chip designs including Package-On-Package (POP) and 3D/2.5D-stacks where complex mechanical forces -- primarily driven by the many Coefficient of Thermal Expansion (CTE) mismatches within and between chips and packages -- influence the electrical properties of ICs. In this era, the industry needs to be able to model and control the mechanical and thermal properties of the combined chip-package, and so we need ways to feed data back and forth between designers, chip fabs, and Out-Sourced Assembly and Test (OSAT) companies. With accelerated yield ramps needed for High Volume Manufacturing (HVM) of consumer mobile products, to minimize risk of expensive Work In Progress (WIP) moving through the supply chain a lot of data needs to feed-forward and feedback.

Calvin Cheung, ASE Group Vice President of Business Development & Engineering, discussed these trends in the "Scaling the Walls of Sub-14nm Manufacturing" keynote panel discussion during the recent SEMICON West 2015. "In the old days it used to take 12-18 months to ramp yield, but the product lifetime for mobile chips today can be only 9 months," reminded Cheung. "In the old days we used to talk about ramping a few thousand chips, while today working with Qualcomm they want to ramp millions of chips quickly. From an OSAT point of view, we pride ourselves on being a virtual arm of the manufacturers and designers," said Cheung, "but as technology gets more complex and 'knowledge-basecentric" we see less release of information from foundries. We used to have larger teams in foundries." Dick James of ChipWorks details the complexity of the SiP used in the Apple Watch in his recent blog post at SemiMD, and documents the details behind the assumption that ASE is the OSAT.

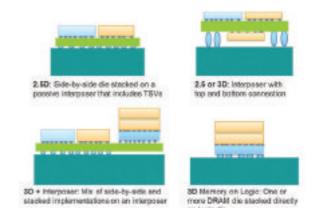

With single-chip System-on-Chip (SoC) designs the 'final test' can be at the wafer-level, but with SiP based on chips from multiple vendors the 'final test' now must happen at the package-level, and this changes the Design For Test (DFT) work flows. DRAM in a 3D stack (**FIGURE 1**) will have an interconnect test and memory Built-In Self-Test (BIST) applied from BIST resident on the logic die connected to the memory stack using Through-Silicon Vias (TSV).

**FIGURE 1.** Schematic cross-sections of different 3D Systemin-Package (SiP) design types (Source: Mentor Graphics).

"The test of dice in a package can mostly be just re-used die-level tests based on hierarchical pattern re-targeting which is used in many very large designs today," said Ron Press, technical marketing director of Silicon Test Solutions, Mentor Graphics, in discussion with SemiMD. "Additional interconnect tests between die would be added using boundary scans at die inputs and outputs, or an equivalent method. We put together 2.5D and 3D methodologies that are in some of the foundry reference flows. It still isn't certain if specialized tests will be required to monitor for TSV partial failures."

"Many fabless semiconductor companies today use solutions like scan test diagnosis to identify productspecific yield problems, and these solutions require a combination of test fail data and design data," explained Geir Edie, Mentor Graphics' product marketing manager of Silicon Test Solutions. "Getting data from one part of

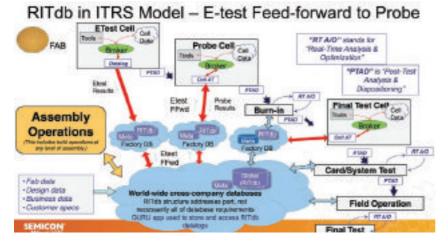

**FIGURE 2.** Structure of the Rich Interactive Test Database (RITdb) industry standard, showing how data can move through the supply chain (Source: Texas Instruments).

the fabless organization to another can often be more challenging than what one should expect. So, what's often needed is a set of 'best practices' that covers the entire yield learning flow across organizations."

"We do need a standard for structuring and transmitting test and operations meta-data in a timely fashion between companies in this relatively new dis-aggregated semiconductor world across Fabless, Foundry, OSAT, and OEM," asserted John Carulli, GLOBALFOUNDRIES' deputy director of Test Development & Diagnosis, in an exclusive discussion with SemiMD. "Presently the databases are still proprietary - either internal to the company or as part of third-party vendors' applications." Most of the test-related vendors and users are supporting development of the new Rich Interactive Test Database (RITdb) data format to replace the Standard Test Data Format (STDF) originally developed by Teradyne.

"The collaboration across the semiconductor ecosystem placed features in RITdb that understand the end-to-end data needs including security/provenance," explained Carulli. FIGURE 2 shows that since RITdb is a structured data construct, any data from anywhere in the supply chain could be easily communicated, supported, and scaled regardless of OSAT or Fabless customer test program infrastructure. "If RITdb is truly adopted and some certification system can be placed around it to keep it from diverging, then it provides a standard core to transmit data with known meaning across our dis-aggregated semiconductor world. Another key part is the Test Cell Communication Standard Working Group; when integrated with RITdb, the improved automation and control path would greatly reduce manually communicated understanding of operational practices/issues across companies that impact yield and quality."

Phil Nigh, GLOBALFOUNDRIES Senior Technical Staff, explained to SemiMD that for heterogeneous integration of different chip types the industry has on-chip temperature measurement circuits which can monitor temperature at a given time, but not necessarily identify issues cause by thermal/ mechanical stresses. "During production testing, we should detect mechanical/ thermal stress 'failures' using product testing methods such as IO leakage, chip leakage, and other chip performance measurements such as FMAX," reminded Nigh.

#### **Model but verify**

Metrology tool supplier Nanometrics has unique perspective on the data needs of 3D packages since the company has delivered dozens of tools for TSV metrology to the world. The company's UniFire 7900 Wafer-Scale Packaging (WSP) Metrology System uses white-light interferometry to measure critical dimensions (CD), overlay, and film thicknesses of TSV, microbumps, Re-Distribution Layer (RDL) structures, as well as the co-planarity of Cu bumps/pillars. Robert Fiordalice, Nanometrics' Vice President of UniFire business group, mentioned to SemiMD in an exclusive interview that new TSV structures certainly bring about new yield loss mechanisms, even if electrical tests show standard results such as 'partial open.' Fiordalice said that, "we've had a lot of pull to take our TSV metrology tool, and develop a TSV inspection tool to check every via on every wafer." TSV inspection tools are now in beta-tests at customers.

As reported at 3Dincites, Mentor Graphics showed results at DAC2015 of the use of Calibre 3DSTACK by an OSAT to create a rule file for their Fan-Out Wafer-Level Package (FOWLP) process. This rule file can be used by any designer targeting this package technology at this assembly house, and checks the manufacturing constraints of the package RDL and the connectivity through the package from die-to-die and die-to-BGA. Based on package information including die order, x/y position, rotation and orientation, Calibre 3DSTACK performs checks on the interface geometries between chips connected using bumps, pillars, and TSVs. An assembly design kit provides a standardized process both chip design companies and assembly houses can use to ensure the manufacturability and performance of 3D SiP. 🔶

# The use of sapphire in mobile device and LED industries

WINTHROP E. BAYLIES and CHRISTOPHER JL MOORE, BayTech-Resor LLC, Maynard, MA

#### Sapphire is hard, strong, optically transparent and chemically inert.

ave you ever wondered what blue gemstone earrings, an LED lightbulb and an Apple Watch have in common? The answer (at least for this article) is that all depend on sapphire as part of their manufacturing process. In part 1 of the following two part article we will discuss how sapphire is becoming an important part of the mobile device food chain. Part 2 will concentrate on how sapphire is used in LED production.

Sapphire (chemical composition  $Al_2O_3$ ) has a high melting point of 2040°C (3704°F) and is chemically resistant even at high temperatures. It is an anisotropic material meaning that its mechanical/thermal properties depend on the direction of the crystal plane that is cut and polished. An insulator with a 9.2 eV energy gap it is optically transparent. With a hardness of 9 on the Mhos scale it is almost as hard and strong as diamond (10 Mhos).

To summarize, sapphire has some good points: hard, strong, optically transparent and chemically inert (there is a reason high end watches use sapphire crystals) and some bad points: hard, strong, and chemically inert (which is why sapphire crystals are more expensive than glass). That is, the very properties that make it ideal for applications needing mechanical strength and hardness mean that it is a difficult material to grow, machine and polish.

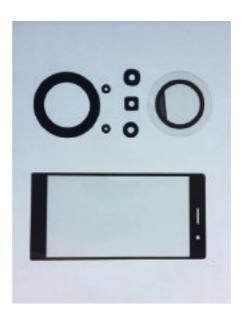

There are several places where sapphire can be (or is now) used in the manufacture of mobile devices. The most publicity in this area was generated in 2014 with significant speculation in both the trade magazines and newspapers (such as the Wall Street Journal) that the iPhone 6 would be released with a sapphire touch screen or at the very least a sapphire cover glass over the existing touchscreen. Part of this speculation was fueled by the large number (1700 to 2500 depending on source) of sapphire producing furnaces being installed at an Apple facility in Mesa Arizona. However, the sapphire iPhone 6 was not released due in part to the difficulties in growing and processing enough sapphire screens at a reasonable cost to supply the significant number of phones produced. There are now sapphire touch screen phones available from other suppliers and recently, the Apple Watch was released with a sapphire screen. In addition many fingerprint sensors and camera cover glasses are now produced using sapphire as the cover material.

Requirements for sapphire material is clear (forgive the pun). For screens and cameras it must be of good optical quality i.e. transmit light well and have low surface roughness. For fingerprint sensors it needs consistent surface quality and electrical properties.

FIGURE 1. A schematic of the process used to produce sapphire parts for a mobile device.

**WINTHROP E. BAYLIES** and **CHRISTOPHER JL MOORE** are senior partners at BayTech-Resor LLC, Maynard, MA. E-mail: win.baylies@BayTech-Resor.com and chris.moore@BayTech-Resor.com.

#### www.solid-state.com

#### **Production process**

**FIGURE 1** shows a schematic of the production process for sapphire used in a mobile device screen. The following paragraphs provide more detail on this process [1] as well as a few of problems encountered along the way.

The sapphire production process starts when a seed crystal and a mixture of aluminum oxide and crackle (un-crystallized sapphire material) is heated using a specific temperature/time profile, then cooled (this process can take two weeks depending on the amount of sapphire being produced) using a carefully controlled set of time/temperature profiles. When done correctly, the cookie sized seed grows and produces a singlecrystal sapphire boule. That at least is the theory. In reality, two weeks is a long time and any number of problems can go wrong during this process including gas bubbles, mechanical faults such as cracks and contamination. Each of these problems can affect the sapphire and its optical/electrical properties. There is a clear correlation between the time taken to grow a boule and the potential quality of the boule produced. Many of the problems encountered in the upscaling of the sapphire production process sprang from trying to grow large boules at high speeds.

It is at the next step in the process where boule size does matter. Typically, the boule will be drilled or cut to produce material near the size needed for the particular application. It makes a significant difference if the material is for a watch crystal (say 1.5 inch diameter ~ 1.7 square inches). Here you can "core-drill" a boule to produce a number of smaller cylinders. For a phone screen/cover plate (at 4 by 6 inch i.e. 24 square inches) a larger portion of the boule is needed for a box shape. The ability to grow large sized boules on a regular basis is not in question; most important is how much of that boule is bubble-, crack- and impurity-free. In some cases the boules are inspected with various metrology techniques to determine which sections of the boule can be used and which cannot. The section of the boules not used is recycled into the original growth process (unless contaminated).

Given the hardness of the sapphire, diamond wire saws or diamond core drills are used for cutting or coring the boules. The yield from any boule is a function of the original boule size, the size of the cores or slabs being produced and the volume of the boule free from imperfections. As was discussed earlier, and is typical of many processes, the larger the size of the piece the lower the yield.

The next step is to take the cylindrical cores (or rectangular slabs) and cut them into appropriate sized pieces. The thickness of the desired part and the amount the producer is willing to invest in high technology solutions determines what is done next. On one end of the technology scale the parts are cut using a wire saw or an abrasive cutoff saw. On the other end of the scale you can ion implant the surface to produce a damaged layer at a depth below the surface determined by the original ion energy. If the slab is heated after sufficient implantation is done a thin sheet will separate from the surface. Both processes result in parts of the approximate size needed for the application; a discussion of the pros and cons of each approach is beyond the scope of this article.