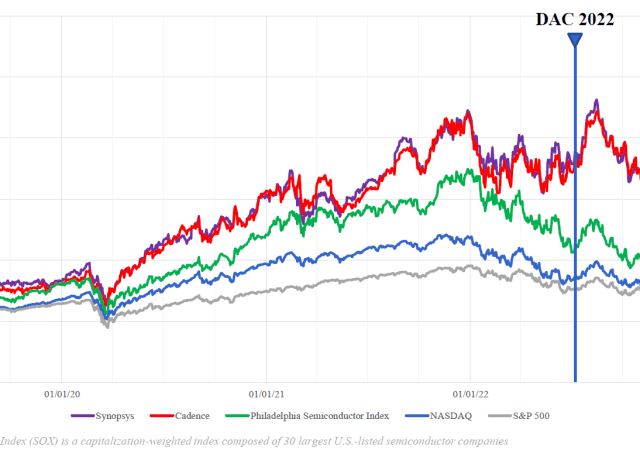

Familiar semiconductor EDA-IP trends remain but vary in impact for 2023.

System Companies Shake Up Semis with Middle Man Cuts, Vertical Shifts, and More

The economic death of Moore’s Law brings a simpler semiconductor value chain, the rise of system companies, software ownership, cuts to the middle man, vertical shifts, and IP M&As.

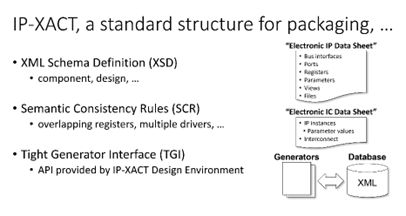

What’s New in the 2022 IEEE IP-XACT Standard? Big Reveals from the Chair

Does semiconductor IP still matter? And what does the chair of the IEEE-1685 IP-XACT standard reveal about the latest feature sets?

Three Trends Shaping the Future of EDA

As more systems companies move to design their own chips and electronic products, what are the key EDA trends impacting the pace of innovation?

The Democratization of Chip Design

The open-source silicon movement with a community-based, open-source platform of easy-to-use, easy-to-access tools is a practical and efficient way to ensure innovation and has the potential to drive exponential semiconductor industry growth.

What Trends Will Have the Biggest Impact on Semiconductor Design?

Semiconductor design has progressively improved over the decades, and that will continue for the foreseeable future. Here are some fascinating trends that will likely shape the future of engineering at all stages of product development.

Outlook for 2021: Executive Viewpoints

Each year, Semiconductor Digest turns to industry leaders and analysts to get their viewpoints on what they expect to see in the coming year in terms of critical tech and business trends.

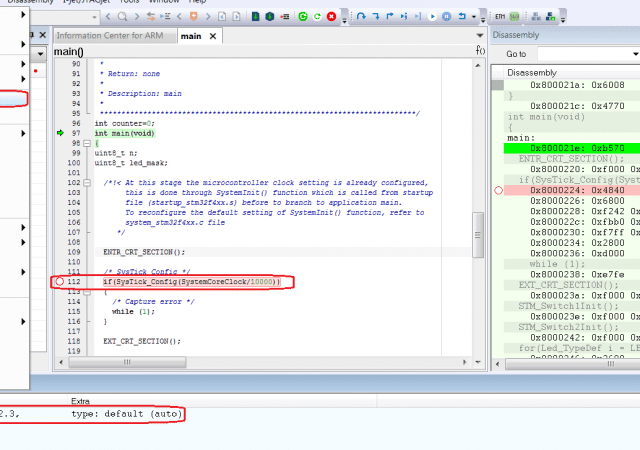

Tips on Becoming a Debugging Wizard

One reason developers spend so much time on this task is a lack of understanding of how to maximize their use of debugging tools.

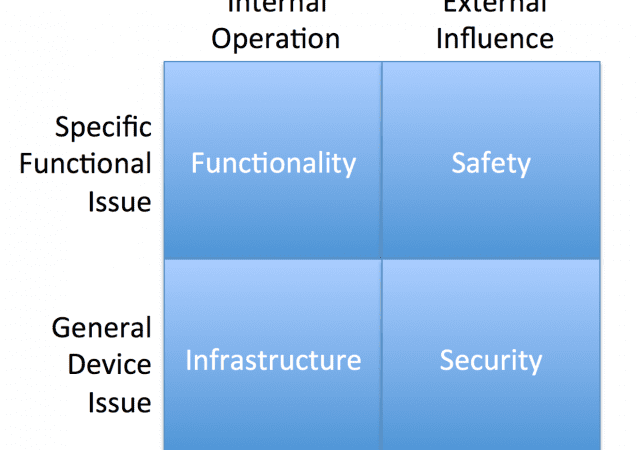

Redefining Reliability: A Game of Integrity Verification

Four factors lead to device integrity: Correct functional execution, effective infrastructure operation, safe operation in adverse conditions, and secure execution in the face of malicious attack.

VLSI Design Optimization and Validation Process Is Like Painting the Forth Bridge

Some EDA tools have introduced an innovative approach that allows designers to generate design metadata one time for certain verification flows.