Secretary of Commerce Gina Raimondo believes investments in leading-edge logic chips manufacturing will put the U.S. on track to produce roughly 20 percent of the world’s leading-edge logic chips by the end of the decade.

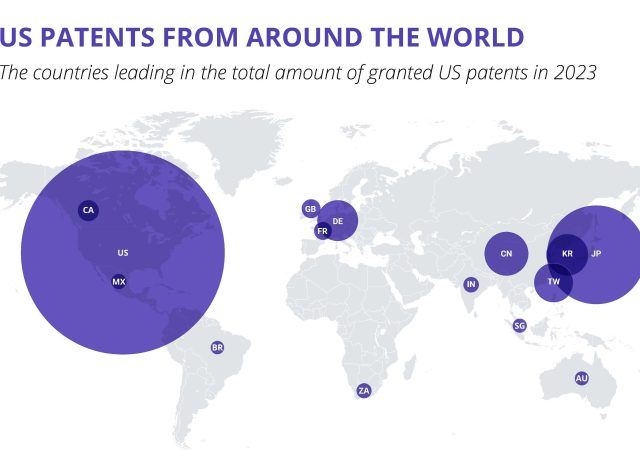

Semiconductor Tech Received Most Granted Patents in 2023

An annual analysis of publicly available patent data from IP management firm Anaqua found that semiconductor technologies received the most granted patents in the US in 2023, the second year in a row that semiconductors have topped the list.

How the CHIPs Act Changed the Chip Industry – A Year Later

One year after passing the CHIPs Act, and there are still questions about whether its influence will be positive or negative.

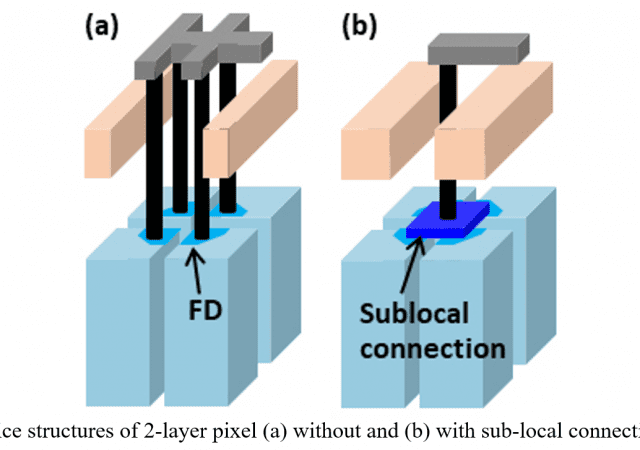

Sony, Samsung, Toshiba, Toppan Have Image Sensor/LiDAR Papers at the VLSI Symposia in June

Since the development of mobile phone camera image sensors, they have been a hot topic with continuous evolution to sub-micron pixels, and more recently the move towards self-driving cars (and other ranging needs) is pushing LiDAR systems.

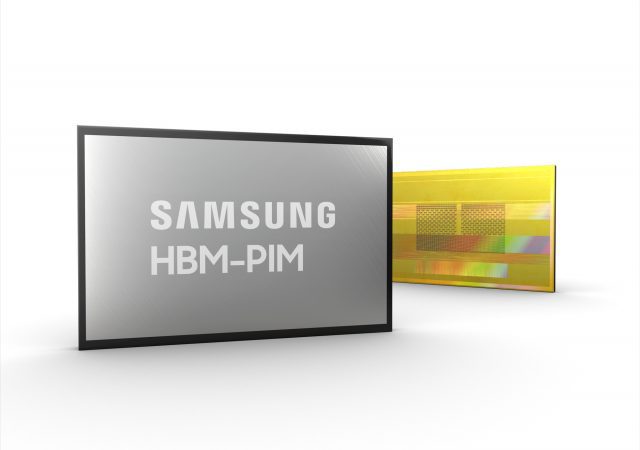

Samsung Brings In-memory Processing Power to Wider Range of Applications

Samsung’s revelations at Hot Chips include the first successful integration of its PIM-enabled High Bandwidth Memory (HBM-PIM) into a commercialized accelerator system, and broadened PIM applications to embrace DRAM modules and mobile memory.

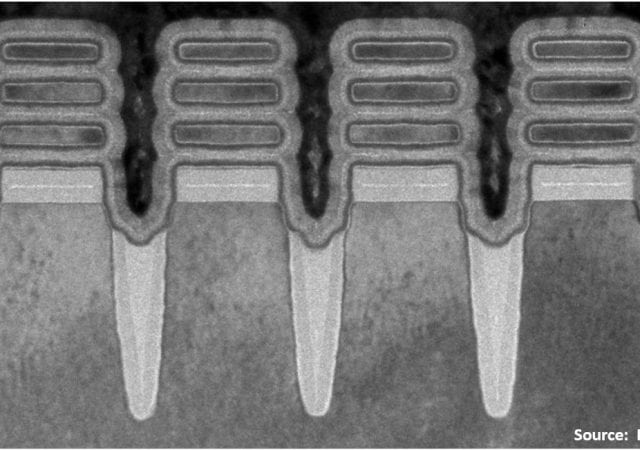

IBM Announces 2nm GAA-FET Technology – the Sum of “Aha!” Moments

IBM likes to create a stir once in awhile, and judging by the tech-press response in the last week or three, they have achieved that goal with their announcement of 2-nanometer CMOS technology, developed at their Albany research centre. This technology is expected to give a 45% performance boost or 75% power reduction, compared with a 7-nm process. Of course the question is, compared with what 7-nm process?

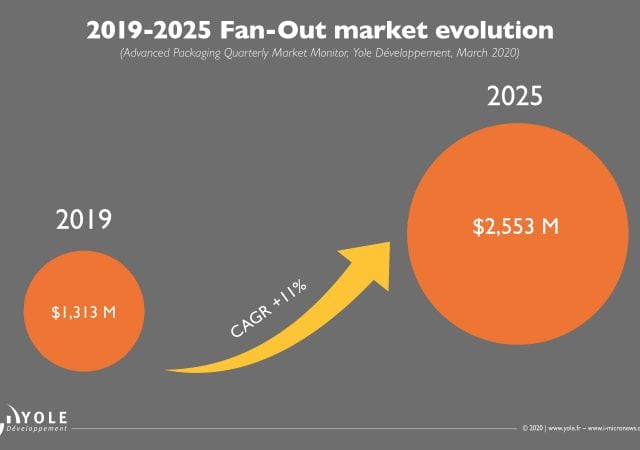

Wafer Level Packaging Reaches New Heights

Fan-out package revenue is expected to surpass $2B by 2025 and fan-in WLCSP revenue to peak to $3B by 2025 as TSMC continues to drive the fan-out market in 5G applications.

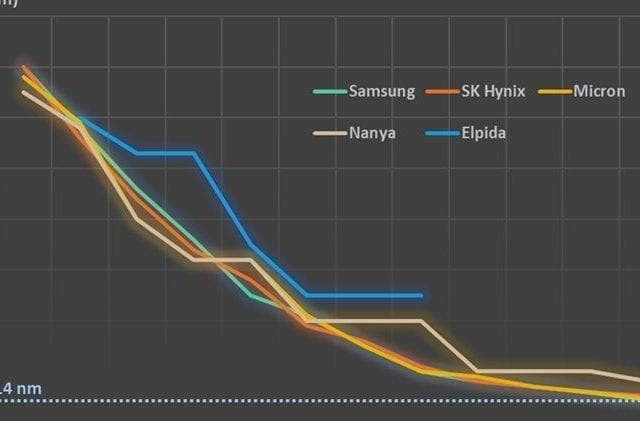

DRAM, NAND and Emerging Memory Technology Trends and Developments in 2019

Innovation in memory technology is constant. In this article, TechInsights’ Jeongdong Choe reviews the latest developments in DRAM, NAND, and emerging technology, and provide insight on the trends in this space.